产品特点

引脚配置

综述

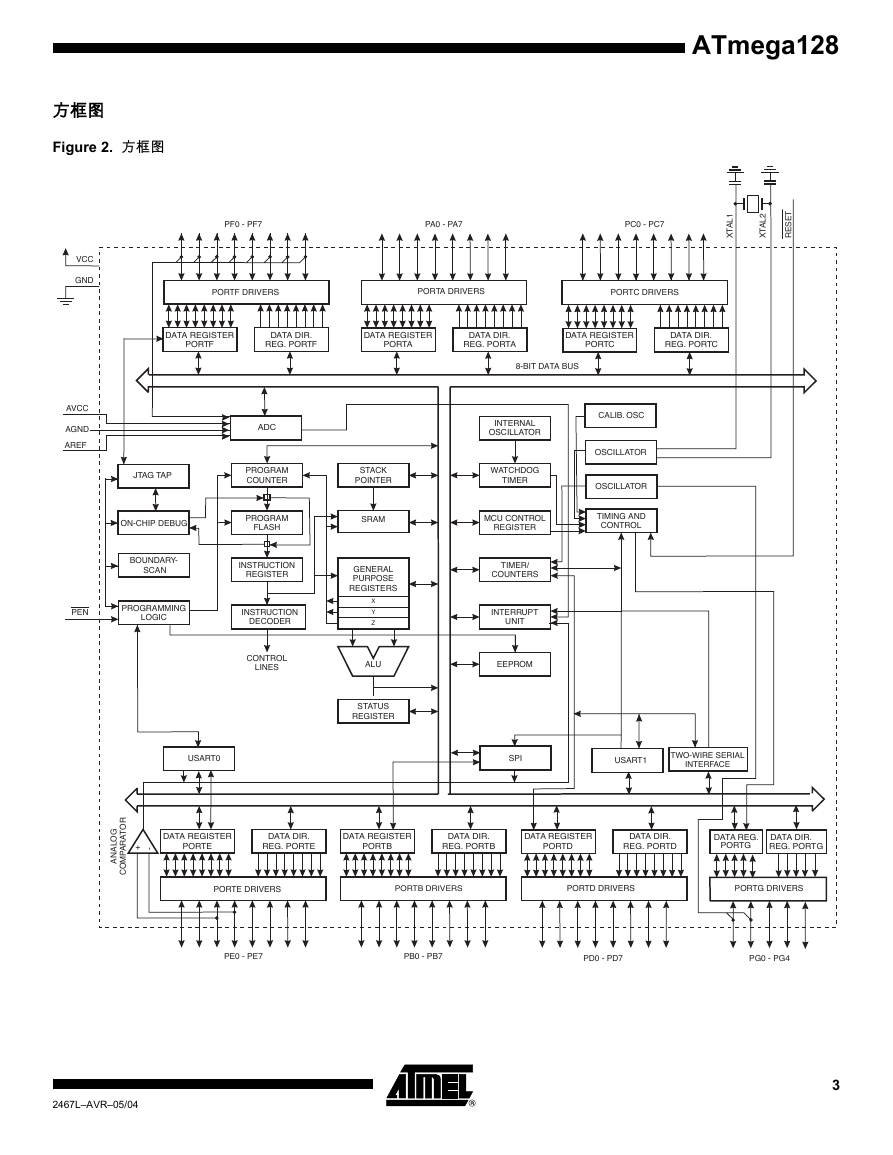

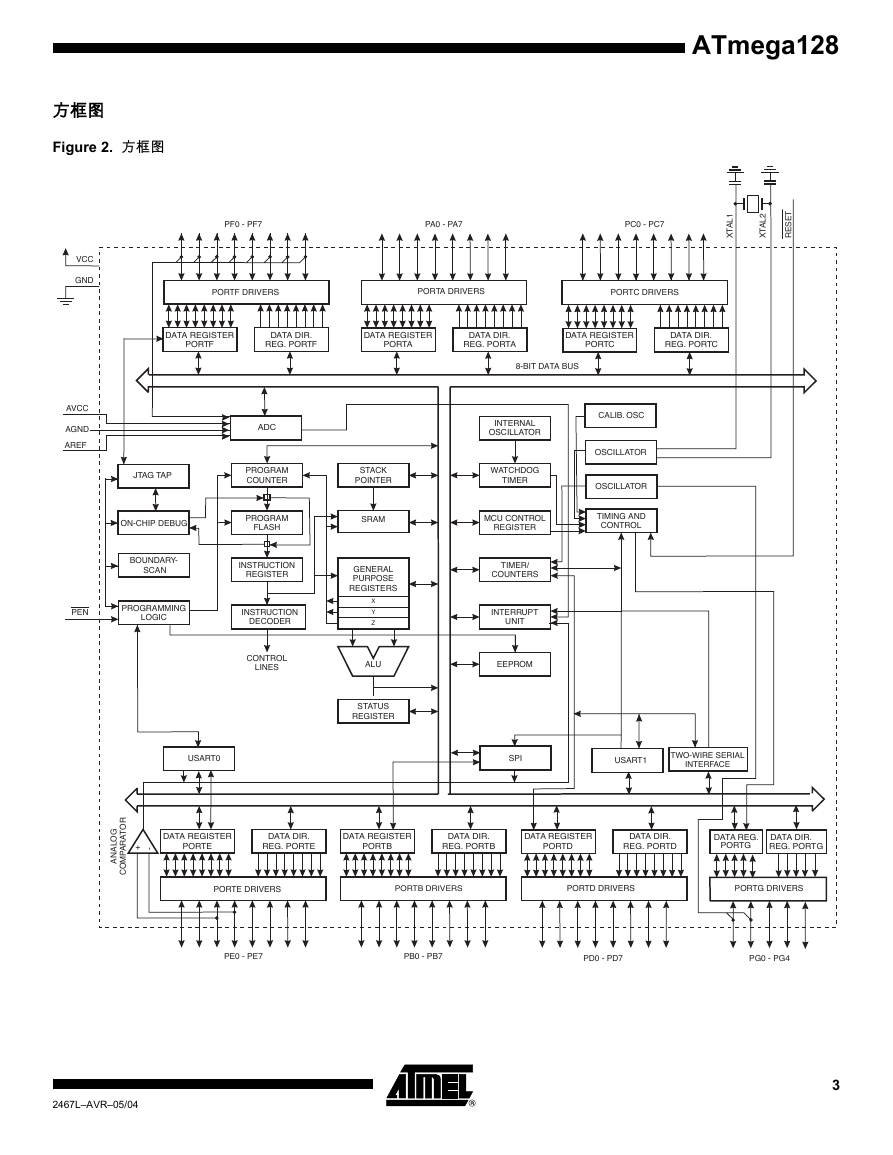

方框图

ATmega103与 ATmega128的兼容性

ATmega103兼容模式

引脚说明

VCC

GND

端口A(PA7..PA0)

端口B(PB7..PB0)

端口C(PC7..PC0)

端口D(PD7..PD0)

端口E(PE7..PE0)

端口F(PF7..PF0)

端口G(PG4..PG0)

RESET

XTAL1

XTAL2

AVCC

AREF

PEN

代码例子

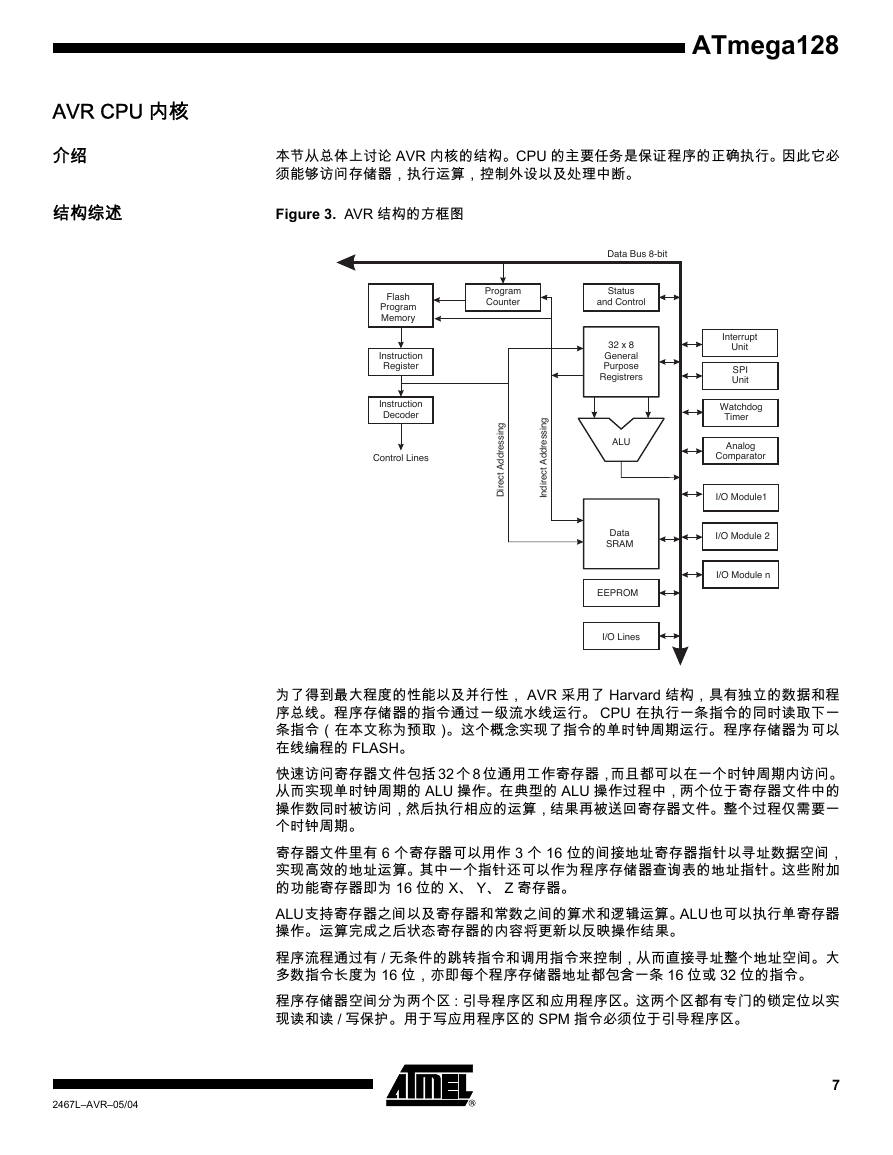

AVR CPU内核

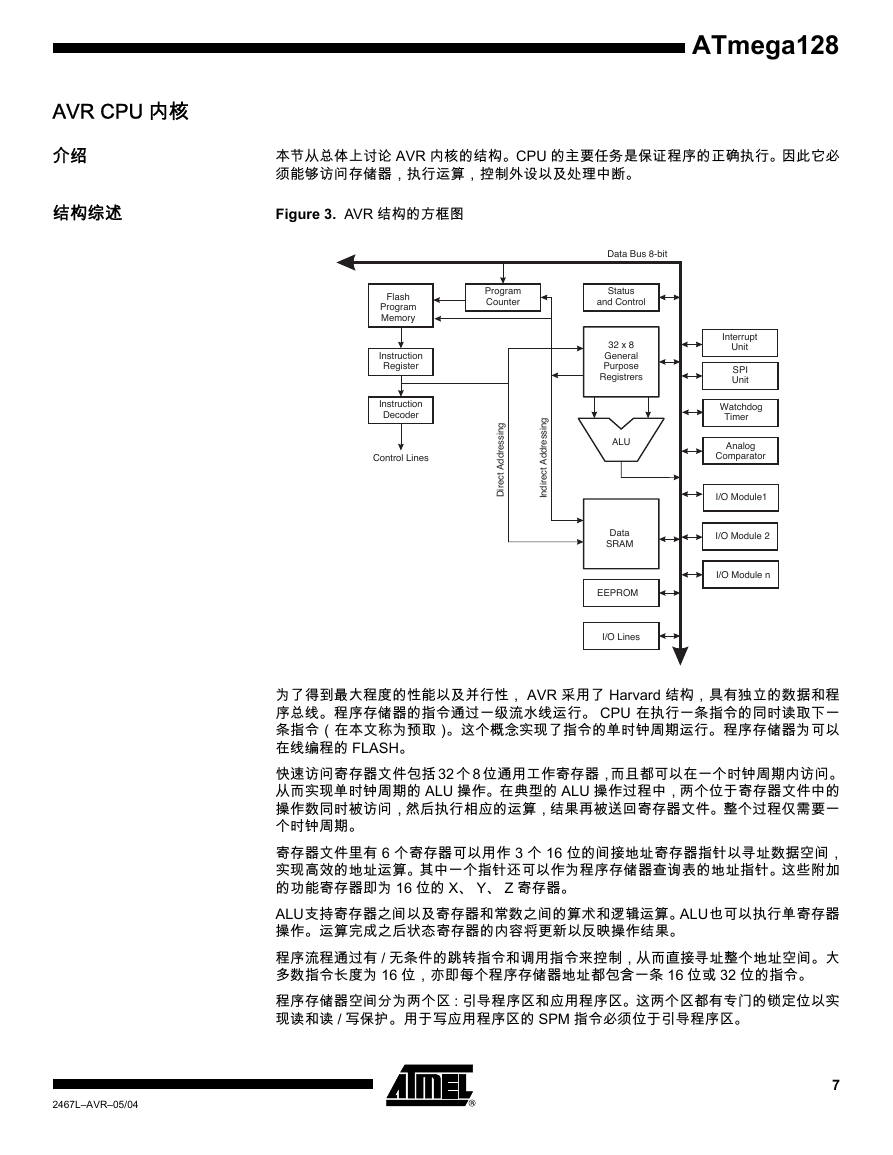

介绍

结构综述

ALU-算逻单元

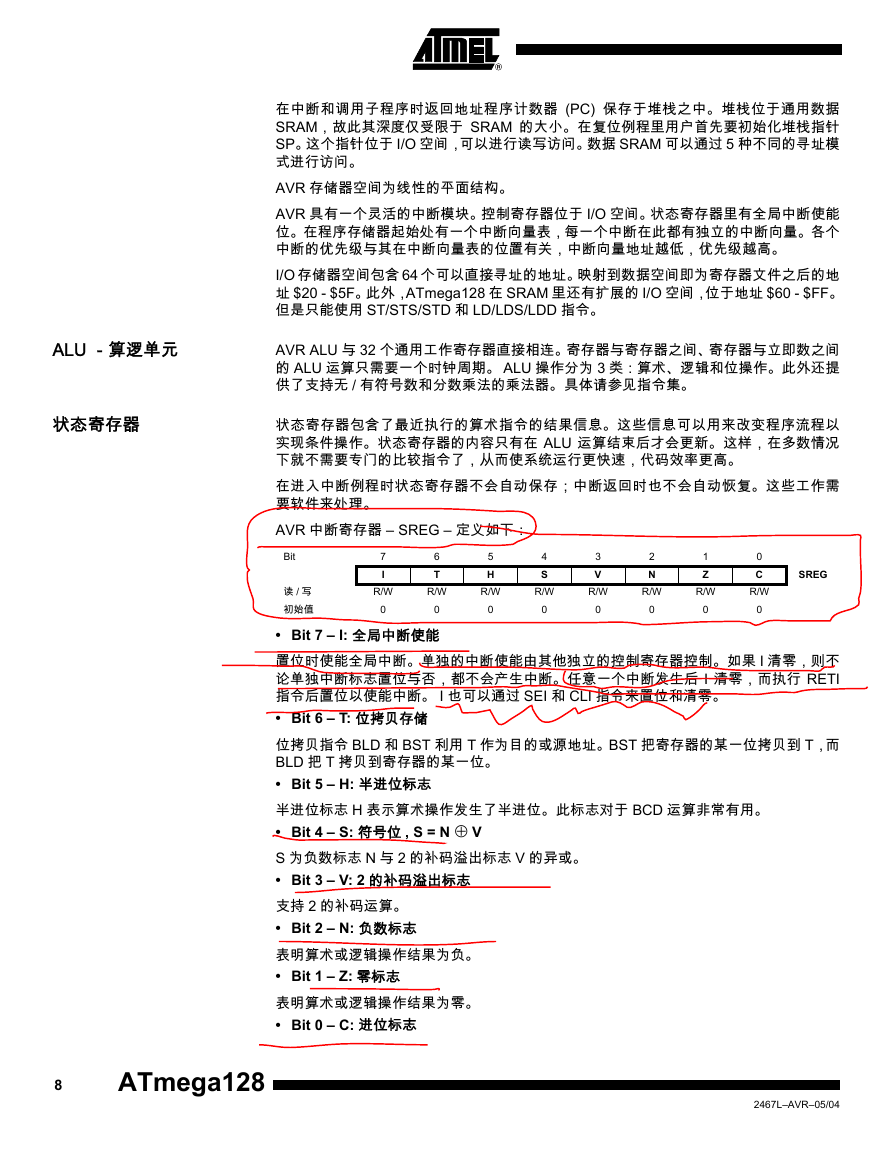

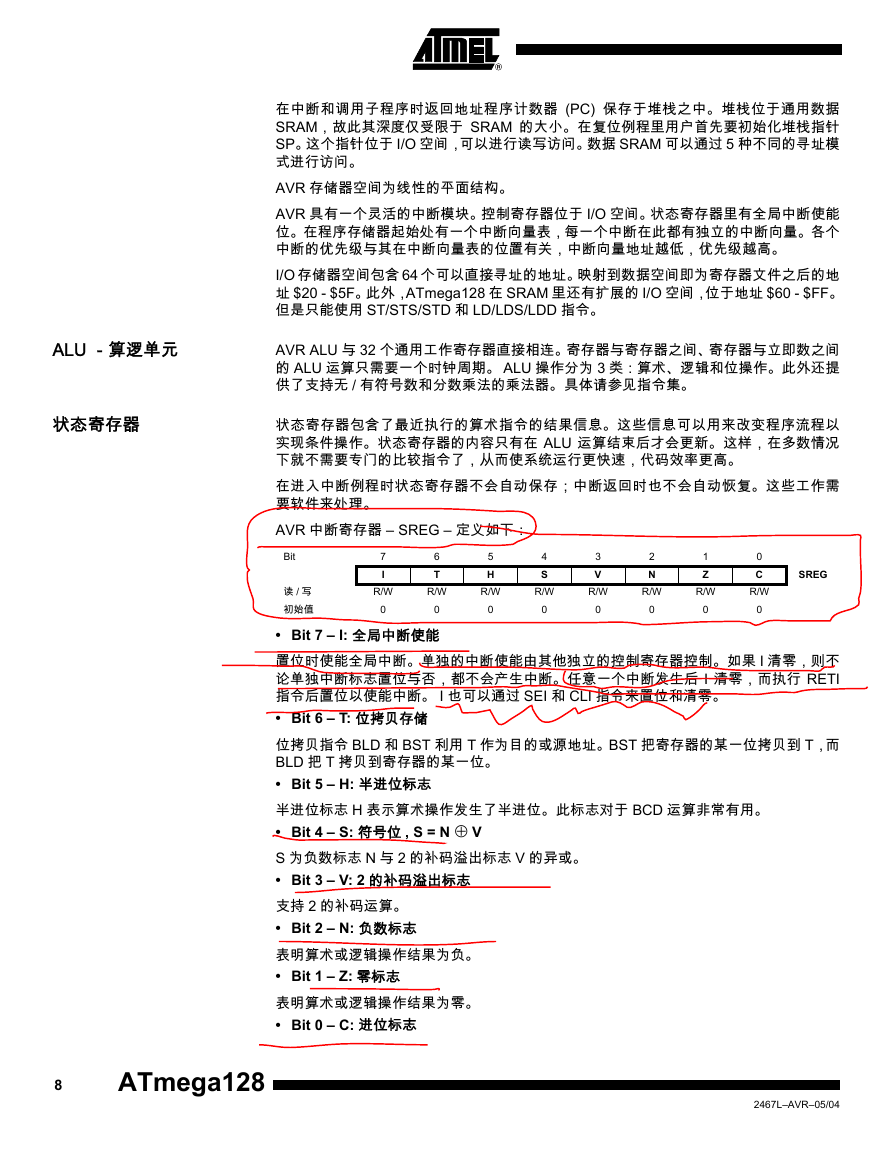

状态寄存器

通用寄存器文件

X寄存器,Y寄存器和Z寄存器

堆栈指针

RAM页面的Z选择寄存器- RAMPZ

指令执行时序

复位和中断处理

中断响应时间

AVR ATmega128存储 器

系统内可编程的Flash程序 存储器

SRAM数据存储器

数据存储器访问时间

EEPROM数据存储器

EEPROM读/写访问

EEPROM 地址寄存器-EEARH 和EEARL

EEPROM数据寄存器-EEDR

EEPROM控制寄存器-EECR

掉电休眠模式下EEPROM的写 入

防止EEPROM数据丢失

I/O存储器

外部存储器接口

综述

ATmega103兼容性

使用外部存储器接口

地址锁存要求

上拉和总线保持

时序

XMEM寄存器说明

MCU控制寄存器-MCUCR

外部存储器控制寄存器A- XMCRA

外部存储器控制寄存器B- XMCRB

使用外部的存储器(小于64KB)

完全使用外部的64KB存储器

系统时钟及其选项

时钟系统及其分布

CPU时钟-clkCPU

I/O时钟-clkI/O

Flash时钟-clkFLASH

异步定时器时钟-clkASY

ADC时钟-clkADC

时钟源

默认时钟源

晶体振荡器

低频晶体振荡器

外部RC振荡器

标定的片内RC振荡器

振荡器标定寄存器-OSCCAL

外部时钟

定时器/计时器振荡器

XTAL分频控制寄存器-XDIV

电源管理及睡眠模式

MCU控制寄存器-MCUCR

空闲模式

ADC噪声抑制模式

掉电模式

省电模式

Standby模式

扩展Standby模式

最小化功耗

模数转换器

模拟比较器

掉电检测器

片内基准电压

看门狗定时器

端口引脚

JTAG接口与片内调试系统

系统控制和复位

复位AVR

复位源

上电复位

外部复位

掉电检测复位

看门狗复位

MCU控制和状态寄存器- MCUCSR

片内基准电压

基准电压使能信号和启动时间

看门狗定时器

看门狗定时器控制寄存器- WDTCR

改变看门狗定时器配置的时间序列

安全级别0

安全级别1

安全级别2

中断

ATmega128的中断向量

在应用区和Boot区之间移动中 断

MCU控制寄存器-MCUCR

I/O端口

介绍

作为通用数字I/O的端口

配置引脚

读取引脚上的数据

数字输入使能和睡眠模式

未连接引脚的处理

端口的第二功能

特殊功能IO寄存器-SFIOR

端口A的第二功能

端口B的第二功能

端口C的第二功能

端口D的第二功能

端口E的第二功能

端口F的第二功能

端口G的第二功能

I/O端口寄存器的说明

端口A数据寄存器-PORTA

端口A数据方向寄存器-DDRA

端口A输入引脚地址-PINA

端口B数据寄存器-PORTB

端口B数据方向寄存器-DDRB

端口B输入引脚地址-PINB

端口C数据寄存器-PORTC

端口C数据方向寄存器-DDRC

端口C输入引脚地址-PINC

端口D数据寄存器-PORTD

端口D数据方向寄存器-DDRD

端口D输入引脚地址-PIND

端口E数据寄存器-PORTE

端口E数据方向寄存器-DDRE

端口E输入引脚地址-PINE

端口F数据寄存器-PORTF

端口F数据方向寄存器-DDRF

端口F输入引脚地址-PINF

端口G数据寄存器-PORTG

端口G数据方向寄存器- DDRG

端口G输入引脚地址-PING

外部中断

外部中断控制寄存器A- EICRA

外部中断控制寄存器B- EICRB

外部中断屏蔽寄存器-EIMSK

外部中断标志寄存器-EIFR

8位定时器/计时器0 - - PWM、异步操作

综述

寄存器

定义

T/C的时钟源

计数器单元

输出比较单元

强制输出比较

写TCNT0操作阻止比较匹配

使用输出比较单元

比较匹配输出单元

比较输出模式和波形产生

工作模式

普通模式

CTC(比较匹配时清除定时器) 模式

快速PWM模式

相位修正PWM模式

T/C时序图

8位T/C寄存器说明

T/C控制寄存器-TCCR0

T/C寄存器-TCNT0

输出比较寄存器-OCR0

定时器/计数器的异步操作

异步状态寄存器-ASSR

T/C0的异步操作

定时器/计数器中断屏蔽寄存器 -TIMSK

定时器/计数器中断标志寄存器 -TIFR

定时器/计数器预分频器

特殊功能IO寄存器-SFIOR

16位定时器/计数器( 定时器/计数器1和定 时器/计数器3)

ATmega103兼容模式的限制

综述

寄存器

定义

兼容性

访问16位寄存器

重复利用暂存器的高字节

定时器/计数器的时钟源

计数器单元

输入捕捉单元

输入捕捉触发源

噪声抑制器

使用输入捕捉单元

输出比较单元

强制输出比较

写TCNTn将阻止比较匹配

使用输出比较匹配单元

比较匹配输出单元

比较匹配模式和波形产生

工作模式

普通模式

CTC(比较匹配时清除定时器) 模式

快速PWM模式

相位修正PWM模式

相位和频率修正PWM模式

定时器/计数器时序图

16位定时器/计数器寄存 器说明

定时器/计数器1控制寄存器A -TCCR1A

定时器/计数器3 控制寄存器A -TCCR3A

定时器/计数器1控制寄存器B -TCCR1B

定时器/计数器3控制寄存器B -TCCR3B

定时器/计数器1控制寄存器C -TCCR1C

定时器/计数器3控制寄存器C -TCCR3C

定时器/计数器1-TCNT1H和 TCNT1L

定时器/计数器3-TCNT3H和 TCNT3L

输出比较寄存器1 A-OCR1AH 和OCR1AL

输出比较寄存器1 B-OCR1BH 和OCR1BL

输出比较寄存器1 C- OCR1CH和OCR1CL

输出比较寄存器3 A-OCR3AH 和OCR3AL

输出比较寄存器3 B-OCR3BH 和OCR3BL

输出比较寄存器3 C- OCR3CH和OCR3CL

输入捕捉寄存器1-ICR1H和 ICR1L

输入捕捉寄存器3-ICR3H和 ICR3L

定时器/计数器中断屏蔽寄存器 -TIMSK

扩展的定时器/计数器中断屏蔽 寄存器-ETIMSK

定时器/计数器中断标志寄存器 -TIFR

扩展的定时器/计数器中断标志 寄存器-ETIFR

定时器/计数器3、定 时器/计数器2和定时 器/计数器1的预分频 器

内部时钟源

预分频器复位

外部时钟源

特殊功能IO寄存器-SFIOR

具有PWM功能的8位 定时器/计数器2

综述

寄存器

定义

定时器/计数器时钟源

计数器单元

输出比较单元

强制输出比较

写TCNT2将阻止比较匹配

使用输出比较单元

比较匹配输出单元

比较输出模式和波形产生

工作模式

普通模式

CTC(比较匹配时清除定时器) 模式

快速PWM模式

相位修正PWM模式

定时器/计数器时序图

8位定时器/计数器寄 存器说明

定时器/计数器控制寄存器- TCCR2

定时器/计数器寄存器-TCNT2

输出比较寄存器-OCR2

定时器/计数器中断屏蔽寄存器 -TIMSK

定时器/计数器中断标志寄存器 -TIFR

输出比较调制器 (OCM1C2)

综述

说明

时序例子

串行通讯接口-SPI

SS引脚的功能

从机模式

主机模式

SPI控制寄存器-SPCR

SPI状态寄存器-SPSR

SPI数据寄存器-SPDR

数据模式

USART

双USART

综述

AVR USART和AVR UART- 兼容性

时钟产生

片内时钟产生-波特率发生器

倍速操作(U2X)

外部时钟

同步时钟操作

帧格式

计算奇偶校验位

USART初始化

发送数据-USART发送器

以5 到8个数据位的方式发送帧

以9个数据位的方式发送帧

发送器标志和中断

产生奇偶校验位

禁止发送器

接收数据-USART接收器

以5到8个数据位的方式接收帧

以9个数据位的方式接收帧

接收完成标志和中断

接收器错误标志

奇偶校验器

接收器禁用

刷新接收缓冲器

接收异步数据

恢复异步时钟

恢复异步数据

异步工作范围

多处理器通讯模式

使用MPCM

USART寄存器说明

USARTn I/O数据寄存器- UDRn

USART控制和状态寄存器A- UCSRnA

USARTn控制和状态寄存器B- UCSRnB

USART控制和状态寄存器C- UCSRnC

USART波特率寄存器- UBRRnL和UBRRnH

设置波特率的例子

两线串行接口TWI

特点

两线串行接口总线定义

TWI词汇

电气连接

数据传输和帧格式

传输数据(位)

START/STOP状态

地址数据包格式

数据包格式

将地址包和数据包组合为一个完 整的传输过程

多主机总线系统,仲裁和同 步

TWI模块综述

Scl和SDA引脚

比特率发生器单元

总线接口单元

地址匹配单元

控制单元

TWI寄存器说明

TWI比特率寄存器-TWBR

TWI控制寄存器-TWCR

TWI状态寄存器-TWSR

TWI数据寄存器-TWDR

TWI(从机)地址寄存器- TWAR

使用TWI

数据传输模式

主机发送模式

主机接收模式

从机接收模式

从机发送模式

其他状态

将几个TWI模式组合到一起

多主机系统和仲裁

模拟比较器

特殊功能IO寄存器-SFIOR

模拟比较器控制和状态寄存器- ACSR

模拟比较器多工输入

模数转换器

特点

操作

启动一次转换

预分频和转换时序

差分增益通道

改变通道或基准源

ADC输入通道

ADC基准电压源

ADC噪声抑制器

模拟输入电路

模拟噪声抑制技术

偏置补偿方案

ADC精度定义

ADC转换结果

ADC多工选择寄存器-ADMUX

ADC控制和状态寄存器A- ADCSRA

ADC数据寄存器-ADCL和 ADCH

ADLAR = 0:

ADLAR = 1:

JTAG接口和片上调试 系统OCD(On-chip Debug)

特点

综述

测试访问端口-TAP

TAP控制器

使用边界扫描链

利用片上调试系统OCD

OCD指定的JTAG指令

PRIVATE0; $8

PRIVATE1; $9

PRIVATE2; $A

PRIVATE3; $B

I/O存储器中与OCD相关 的寄存器

OCD寄存器-OCDR

利用JTAG的编程能力

参考书目

IEEE 1149.1 (JTAG)边界 扫描

特点

系统综述

数据寄存器

旁路寄存器

器件识别寄存器

版本

器件型号

生产商ID

复位寄存器

边界扫描链

边界扫描指定的JTAG指 令

EXTEST; $0

IDCODE; $1

SAMPLE_PRELOAD; $2

AVR_RESET; $C

BYPASS; $F

I/O存储器里与边界扫描相 关的寄存器

MCU控制和状态寄存器- MCUCSR

边界扫描链

扫描数字端口引脚

边界扫描和TWI

扫描RESET引脚

扫描时钟引脚

扫描模拟比较器

扫描ADC

ATmega128边界扫描次序

边界扫描描述语言文件

支持引导装入程序 - 在 写的同时可以读 (RWW, Read-While- Write)的自我编程能力

引导程序的特点

应用程序Flash区以及引导 程序Flash区

应用程序区

引导程序区(Boot Loader Section)-BLS

RWW Flash区及非RWW Flash区

RWW区

非RWW区-NRWW

引导程序区锁定位

进入引导程序

保存程序存储器控制寄存器- SPMCSR

在自编程时访问Flash

Flash的自编程

通过SPM执行页擦除

装载临时缓冲器(页加载)

执行页写操作

使用SPM中断

在更新BLS时需要考虑的问题

在自编程时防止读取RWW区

通过SPM设置引导程序锁定位

写EEPROM将阻止写SPMCSR

以软件方式读取熔丝位和锁定位

防止Flash的内容损毁

使用SPM时的Flash编程时间

一个简单的引导程序汇编代码

ATmega128引导程序参数

存储器编程

程序及数据存储器锁定位

熔丝位

锁存熔丝位的数据

标识字节

标定字节

并行编程的参数,引脚映射 及命令

信号名称

并行编程

进入并行编程模式

进行高效编程需要考虑的问题

芯片擦除

对Flash进行编程

对EEPROM进行编程

读取Flash

读取EEPROM

对熔丝位的低位进行编程

对熔丝位的高位进行编程

对扩展熔丝位进行编程

对锁定位进行编程

读取熔丝位和锁定位

读取标识字节

读取标定字节

并行编程特性

串行下载

SPI串行编程引脚映射

SPI串行编程算法

Flash的数据轮询

EEPROM的数据轮询

SPI串行编程特性

通过JTAG接口进行编程

与编程相关的JTAG指令

AVR_RESET ($C)

PROG_ENABLE ($4)

PROG_COMMANDS ($5)

PROG_PAGELOAD ($6)

PROG_PAGEREAD ($7)

数据寄存器

复位寄存器

编程使能寄存器

编程命令寄存器

虚拟Flash页面加载寄存器

虚拟Flash页面读取寄存器

编程算法

进入编程模式

退出编程模式

执行芯片擦除操作

对Flash进行编程

读取Flash

对EEPROM进行编程

读取EEPROM

对熔丝位进行编程

对锁定位进行编程

读取熔丝位和锁定位

读取标识字节

读取标定字节

电气特性

绝对极限值*

直流特性

外部时钟波形

外部时钟

两线串行接口特性

SPI时序特性

交流特性

外部数据存储器时序

ATmega128典型特性

工作电流

空闲电流

掉电模式电流

省电模式电流

Standby模式电流

引脚上拉电阻

引脚驱动能力

引脚阈值与迟滞

BOD阈值与模拟比较补偿

片内振荡器速度

外设单元电流消耗

复位与复位脉宽电流消耗

寄存器概述

指令集概述

定货信息

封装信息

64A

64M1

勘误表

ATmega128 Rev. I

ATmega128 Rev. H

ATmega128 Rev. G

ATmega128 Rev. F

ATmega128数据手册 修改日志

从版本Rev. 2467K-03/04 到版本Rev.2467L-05/04 的修改

从版本Rev. 2467J-12/03 到版本Rev.2467K-03/04 的修改

从版本Rev. 2467I-09/03 到版本Rev.2467J-12/03 的修改

从版本Rev. 2467H-02/03 到版本Rev. 2467I-09/03 的修改

从版本Rev. 2467G-09/02 到版本Rev. 2467H-02/03 的修改

从版本Rev. 2467F-09/02 到版本Rev. 2467G-09/02 的修改

从版本Rev. 2467E-04/02 到版本Rev. 2467F-09/02 的修改

从版本Rev. 2467D-03/02 到版本Rev. 2467E-04/02 的修改

从版本Rev. 2467C-02/02 到版本Rev. 2467D-03/02 的修改

从版本Rev. 2467B-09/01 到版本Rev. 2467C-02/02 的修改

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc