福州大学物信学院

数字集成电路课程设计报告

设计题目: 3-8 译码器(74HC138)

班级:

4 班

专业:

微电子

姓名:

学号:

组名:

指导老师:

教师评分:

日期:

1

�

褔州大学数字集成电路课设计

目 录

目 录.........................................................................................................................................................................2

第 1 章 概述...............................................................................................................................................................3

1.1 课程设计目的 ......................................................... 3

1.2 课程设计的主要内容 ................................................... 3

第 2 章 功能分析与逻辑分析 .................................................................................................................................. 4

2.1 功能分析 ............................................................. 4

第 3 章 电路设计.......................................................................................................................................................5

3.1 模块划分 ............................................................. 5

3.2 各级电路计算 ......................................................... 6

第 4 章 电路仿真.......................................................................................................................................................9

4.1 总体电路 ............................................................. 9

4.2 总体 SYMBOL VIEW ....................................................... 10

4.3 仿真图 .............................................................. 10

4.4 仿真结果 ............................................................ 11

4.5 功耗分析 ............................................................ 11

4.6 本章小结 ............................................................ 13

第 5 章 版图设计.....................................................................................................................................................14

5.1 输入级版图 .......................................................... 14

5.2 输入缓冲级版图 ...................................................... 14

5.3 三输入与非门版图 .................................................... 15

5.4 输出缓冲级版图 ...................................................... 15

5.5 输出级版图 .......................................................... 15

5.6 整体版图 ............................................................ 16

5.7 本章小结 ............................................................ 16

总体心得...................................................................................................................................................................17

附录...........................................................................................................................................................................17

2

�

褔州大学数字集成电路课设计

第 1 章 概述

1.1 课程设计目的

综合应用已掌握的知识,熟悉集成电路设计流程,熟悉集成电路设计主流工具,强化

学生的实际动手能力,培养学生的工程意识和系统观念,培养学生的团队协作能力。

1.2 课程设计的主要内容

1.2.1 课程设计题目及要求

器件名称:3-8 译码器的 74HC138 芯片

要求电路性能指标:

⑵ 驱动 10 个 LSTTL 电路(相对于 15PF 电容负载)

⑶ 于 VDD=3.3V,VOH=3V,VOL=0.3V

⑷ tTLH/tTHL=10ns;

⑷tPLH/tPHL(A1、A2、A3→Y)=15ns;

⑸ tPHL/ tPLH(S1、S2、S3→Y)=17ns

⑹ Pdis≤200mW,fwork=15MHZ

1.2.2 课程设计的内容

1. 功能分析及逻辑设计;

2. 电路设计及器件参数计算;

3. 估算功耗与延时;

4. 电路模拟与仿真;

5. 版图设计;

6. 版图检查:DRC 与 LVS;

7. 后仿真

8. 版图数据提交。

3

�

褔州大学数字集成电路课设计

第 2 章 功能分析与逻辑分析

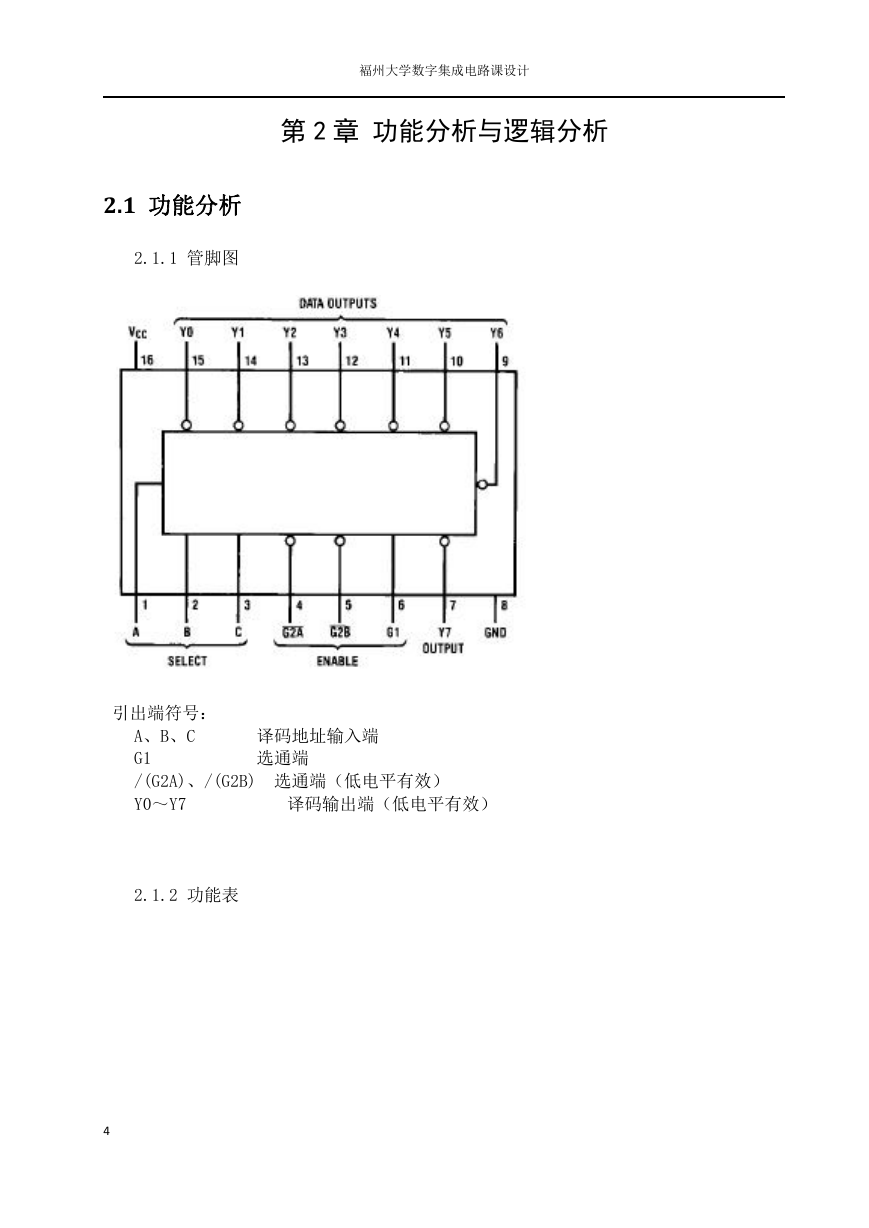

2.1 功能分析

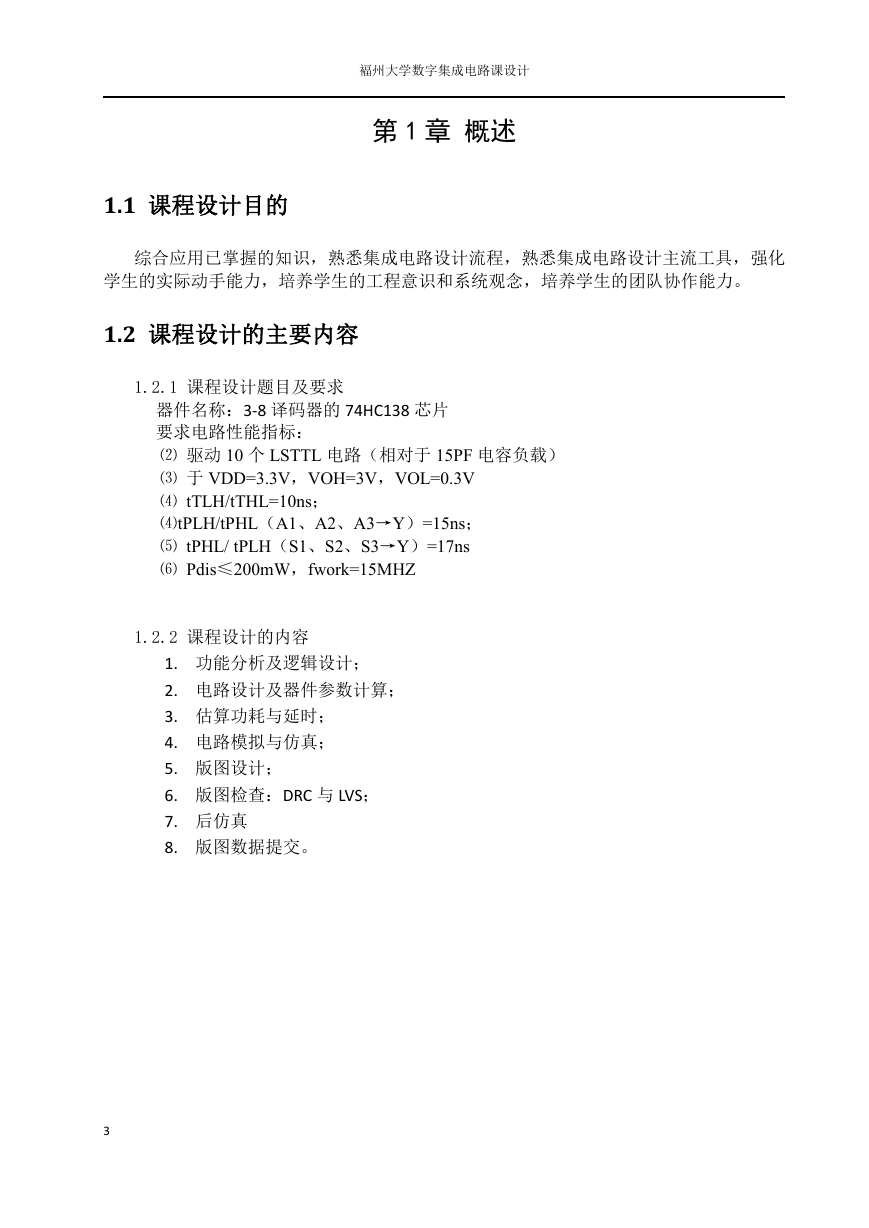

2.1.1 管脚图

引出端符号:

译码地址输入端

选通端

A、B、C

G1

/(G2A)、/(G2B) 选通端(低电平有效)

Y0~Y7

译码输出端(低电平有效)

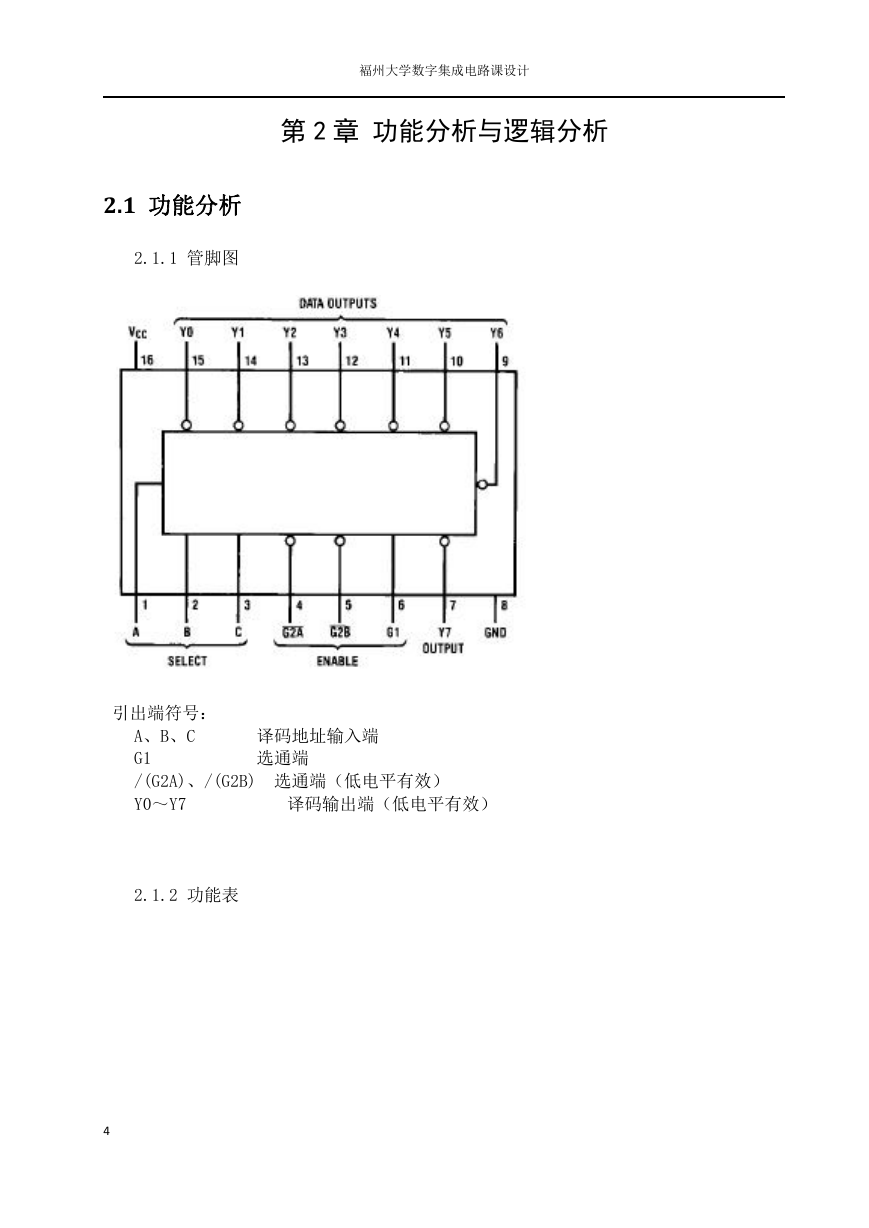

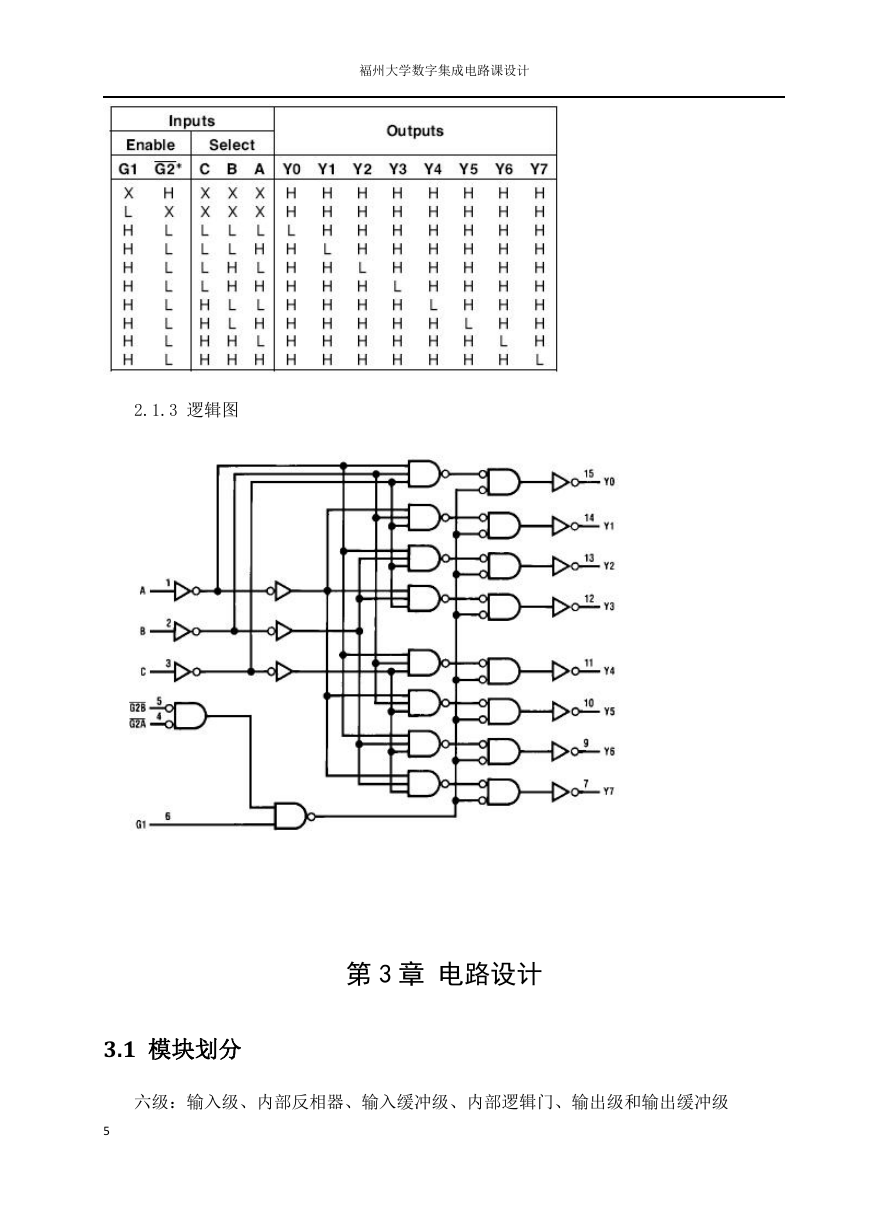

2.1.2 功能表

4

�

褔州大学数字集成电路课设计

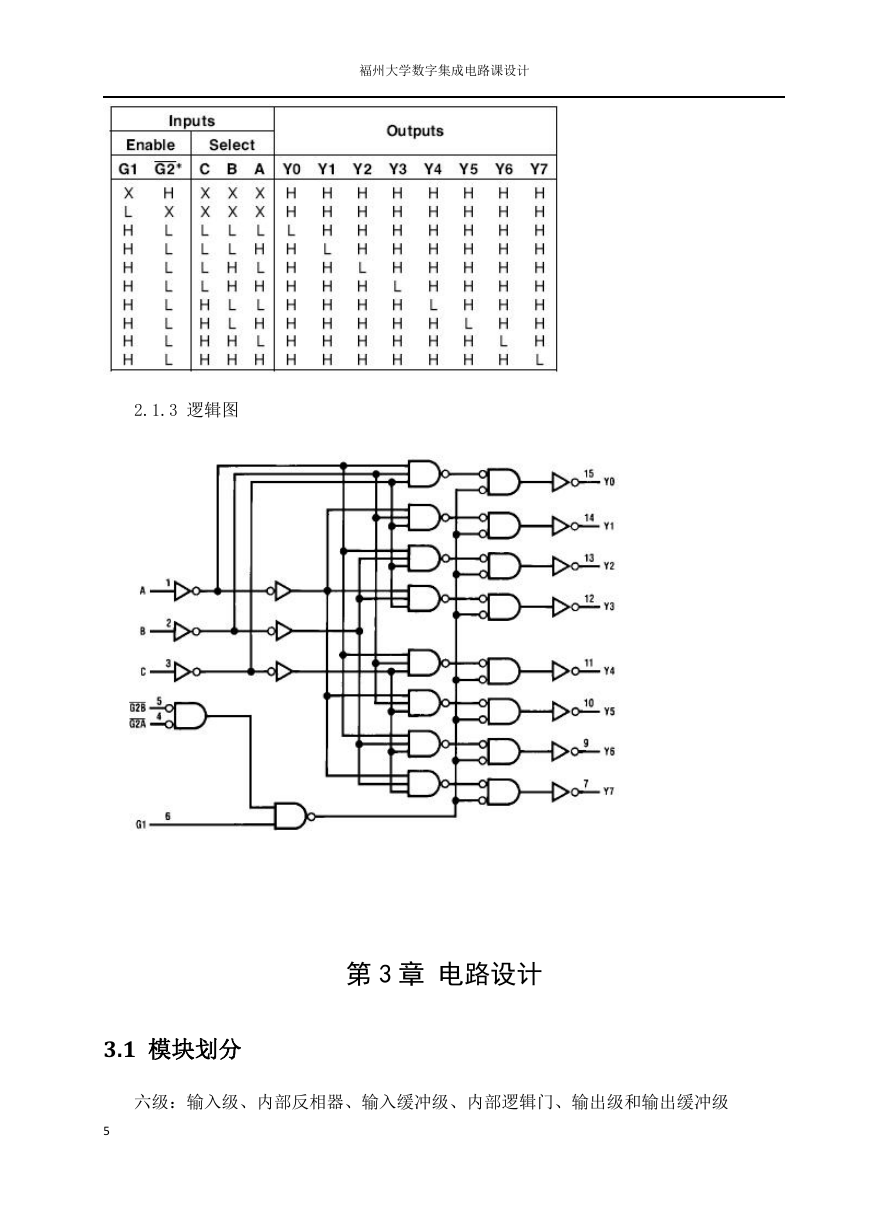

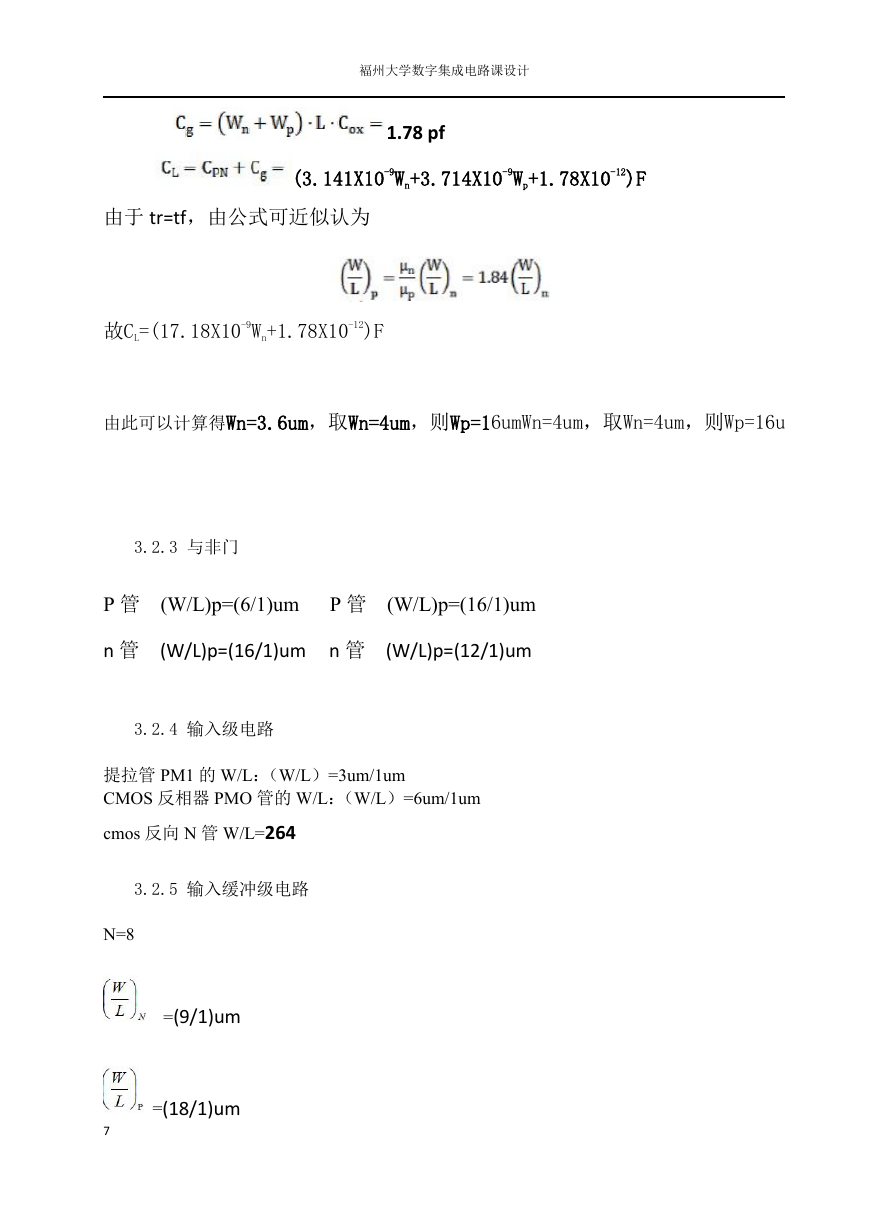

2.1.3 逻辑图

第 3 章 电路设计

3.1 模块划分

六级:输入级、内部反相器、输入缓冲级、内部逻辑门、输出级和输出缓冲级

5

�

褔州大学数字集成电路课设计

3.2 各级电路计算

3.2.1 输出级电路

C=15PF V=3V t=10ns

I=5mA

当输入为高电平时,输出为低电平,N 管导通

计算 Wn≈42u Ln 取 1u

当输入为低电平时,输出为高电平,P 管导通。

计算 Wp≈160u Lp=1u

3.2.2 内部反相器

Tr=Tf=1ns

Cpn=(3.714X10-9Wn+6.272X10-16)+(3.141X10-9Wp+6.405X10-16)

6

�

褔州大学数字集成电路课设计

1.78 pf

(3.141X10-9Wn+3.714X10-9Wp+1.78X10-12)F

由于 tr=tf,由公式可近似认为

故CL=(17.18X10-9Wn+1.78X10-12)F

由此可以计算得Wn=3.6um,取Wn=4um,则Wp=16umWn=4um,取Wn=4um,则Wp=16u

3.2.3 与非门

P 管 (W/L)p=(6/1)um P 管 (W/L)p=(16/1)um

n 管 (W/L)p=(16/1)um n 管 (W/L)p=(12/1)um

3.2.4 输入级电路

提拉管 PM1 的 W/L:(W/L)=3um/1um

CMOS 反相器 PMO 管的 W/L:(W/L)=6um/1um

cmos 反向 N 管 W/L=264

3.2.5 输入缓冲级电路

N=8

=(9/1)um

=(18/1)um

7

�

褔州大学数字集成电路课设计

3.2.6 输出缓冲级电路

N=22.6

=14

=28

故在与非门中的 NMOS 器件与 PMOS 器件

N=(42+160)/(16+16)=6.3

N1=2.6

(W/L)n=37u

(W/L)p=42u

8

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc