基于基于FPGA的高精度数字式移相正弦波信号发生器设计

的高精度数字式移相正弦波信号发生器设计

Design of an exact and digital phase shifting low frequency sine wave generator based on FPGA

Abstract:This paper present an approach of designing an exact and digital phase shifting low frequency sine wave

generator based on FPGA and DDS technology. VHDL can be programmed , then be download to a SpartanⅡseries chip

XC2S100e-6PQ208, Which is made by Xilinx Co. Ltd. This device is composed of only one FPGA chip and simple

periphery circuit ,then can generate two sin waves with preconcerted and adjusted frequency , phase difference and

amplitude.The range of phase difference has achieved 0~359°,step up 1°.

Key words:Digital Phase shifting;FPGA;VHDL; DDS

摘要 : 文章介绍了基于FPGA和数字频率合成技术,利用VHDL编制程序并下载至Xilinx公司的SpartanⅡ系列XC2S100E-

6PQ208 FPAG芯片上,加以简单的外围电路,构成了高精度数字式移相正弦波信号发生器。该装置能够产生频率、相位、幅度

均可数字式预置并可调节的两路正弦波信号,相位差范围为0~359°,步进为1°。

关键词: 数字移相 ; FPGA; VHDL; 直接数字频率合成

1.引言

在一些试验、研究中,有时需要存在相位差的两同频信号。通常采用移相网络来实现,如阻容移相,变压器移相等。采用这些

方法有许多不足之处,比如:输出波形受输入波形的影响,移相操作不方便,移相角度随信号频率和所接负载等因素的影响

等。若采用直接数字频率合成及数字移相技术,能得到频率及相位差高度稳定精确的信号且实现方便。

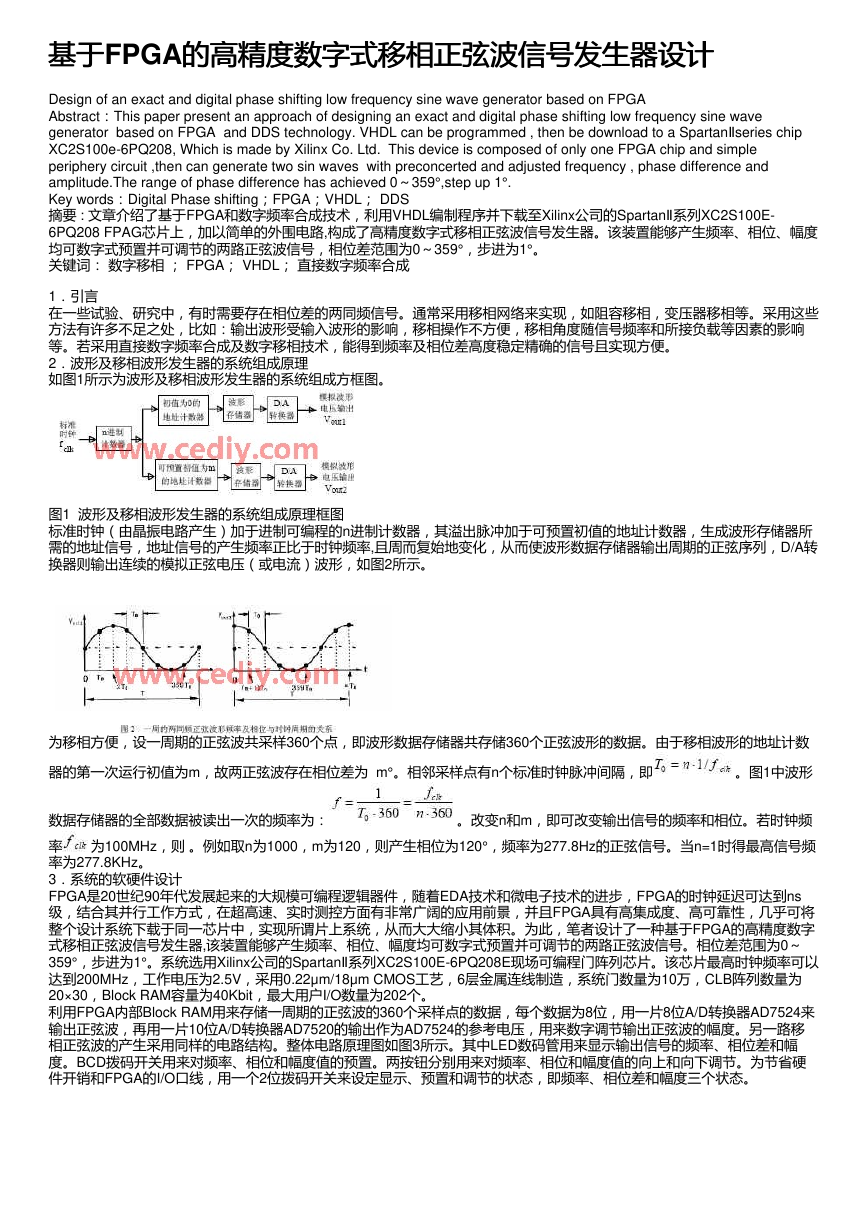

2.波形及移相波形发生器的系统组成原理

如图1所示为波形及移相波形发生器的系统组成方框图。

图1 波形及移相波形发生器的系统组成原理框图

标准时钟(由晶振电路产生)加于进制可编程的n进制计数器,其溢出脉冲加于可预置初值的地址计数器,生成波形存储器所

需的地址信号,地址信号的产生频率正比于时钟频率,且周而复始地变化,从而使波形数据存储器输出周期的正弦序列,D/A转

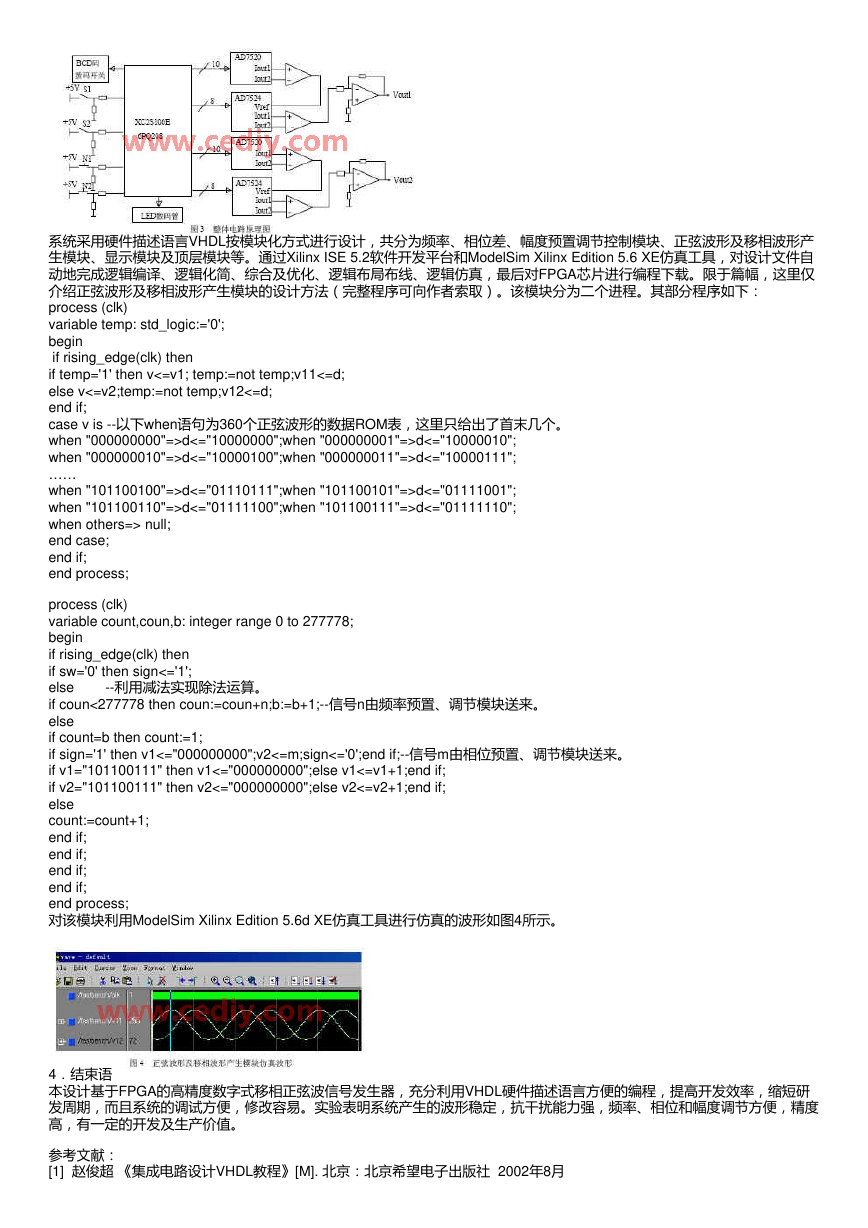

换器则输出连续的模拟正弦电压(或电流)波形,如图2所示。

为移相方便,设一周期的正弦波共采样360个点,即波形数据存储器共存储360个正弦波形的数据。由于移相波形的地址计数

器的第一次运行初值为m,故两正弦波存在相位差为 m°。相邻采样点有n个标准时钟脉冲间隔,即

。图1中波形

。改变n和m,即可改变输出信号的频率和相位。若时钟频

数据存储器的全部数据被读出一次的频率为:

率 为100MHz,则 。例如取n为1000,m为120,则产生相位为120°,频率为277.8Hz的正弦信号。当n=1时得最高信号频

率为277.8KHz。

3.系统的软硬件设计

FPGA是20世纪90年代发展起来的大规模可编程逻辑器件,随着EDA技术和微电子技术的进步,FPGA的时钟延迟可达到ns

级,结合其并行工作方式,在超高速、实时测控方面有非常广阔的应用前景,并且FPGA具有高集成度、高可靠性,几乎可将

整个设计系统下载于同一芯片中,实现所谓片上系统,从而大大缩小其体积。为此,笔者设计了一种基于FPGA的高精度数字

式移相正弦波信号发生器,该装置能够产生频率、相位、幅度均可数字式预置并可调节的两路正弦波信号。相位差范围为0~

359°,步进为1°。系统选用Xilinx公司的SpartanⅡ系列XC2S100E-6PQ208E现场可编程门阵列芯片。该芯片最高时钟频率可以

达到200MHz,工作电压为2.5V,采用0.22μm/18μm CMOS工艺,6层金属连线制造,系统门数量为10万,CLB阵列数量为

20×30,Block RAM容量为40Kbit,最大用户I/O数量为202个。

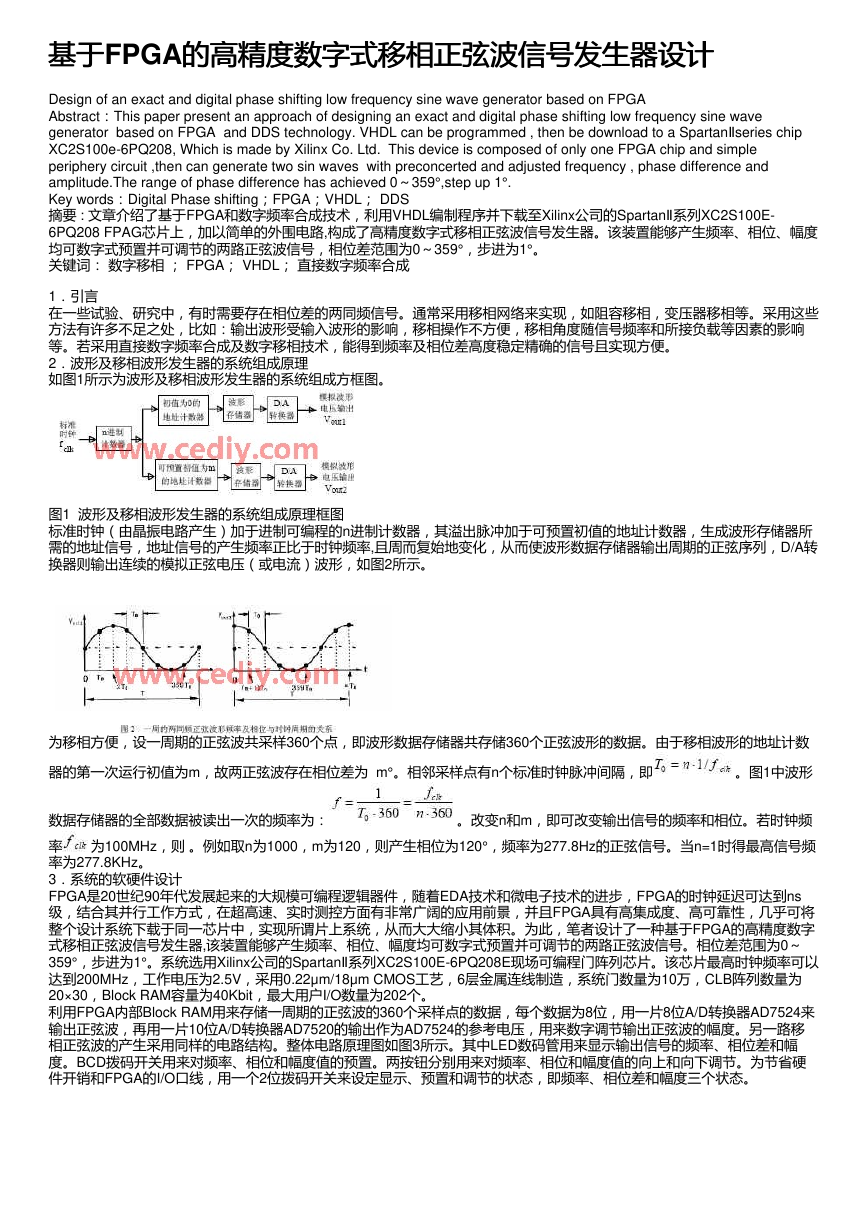

利用FPGA内部Block RAM用来存储一周期的正弦波的360个采样点的数据,每个数据为8位,用一片8位A/D转换器AD7524来

输出正弦波,再用一片10位A/D转换器AD7520的输出作为AD7524的参考电压,用来数字调节输出正弦波的幅度。另一路移

相正弦波的产生采用同样的电路结构。整体电路原理图如图3所示。其中LED数码管用来显示输出信号的频率、相位差和幅

度。BCD拨码开关用来对频率、相位和幅度值的预置。两按钮分别用来对频率、相位和幅度值的向上和向下调节。为节省硬

件开销和FPGA的I/O口线,用一个2位拨码开关来设定显示、预置和调节的状态,即频率、相位差和幅度三个状态。

�

系统采用硬件描述语言VHDL按模块化方式进行设计,共分为频率、相位差、幅度预置调节控制模块、正弦波形及移相波形产

生模块、显示模块及顶层模块等。通过Xilinx ISE 5.2软件开发平台和ModelSim Xilinx Edition 5.6 XE仿真工具,对设计文件自

动地完成逻辑编译、逻辑化简、综合及优化、逻辑布局布线、逻辑仿真,最后对FPGA芯片进行编程下载。限于篇幅,这里仅

介绍正弦波形及移相波形产生模块的设计方法(完整程序可向作者索取)。该模块分为二个进程。其部分程序如下:

process (clk)

variable temp: std_logic:='0';

begin

if rising_edge(clk) then

if temp='1' then v<=v1; temp:=not temp;v11<=d;

else v<=v2;temp:=not temp;v12<=d;

end if;

case v is --以下when语句为360个正弦波形的数据ROM表,这里只给出了首末几个。

when "000000000"=>d<="10000000";when "000000001"=>d<="10000010";

when "000000010"=>d<="10000100";when "000000011"=>d<="10000111";

……

when "101100100"=>d<="01110111";when "101100101"=>d<="01111001";

when "101100110"=>d<="01111100";when "101100111"=>d<="01111110";

when others=> null;

end case;

end if;

end process;

process (clk)

variable count,coun,b: integer range 0 to 277778;

begin

if rising_edge(clk) then

if sw='0' then sign<='1';

else --利用减法实现除法运算。

if coun<277778 then coun:=coun+n;b:=b+1;--信号n由频率预置、调节模块送来。

else

if count=b then count:=1;

if sign='1' then v1<="000000000";v2<=m;sign<='0';end if;--信号m由相位预置、调节模块送来。

if v1="101100111" then v1<="000000000";else v1<=v1+1;end if;

if v2="101100111" then v2<="000000000";else v2<=v2+1;end if;

else

count:=count+1;

end if;

end if;

end if;

end if;

end process;

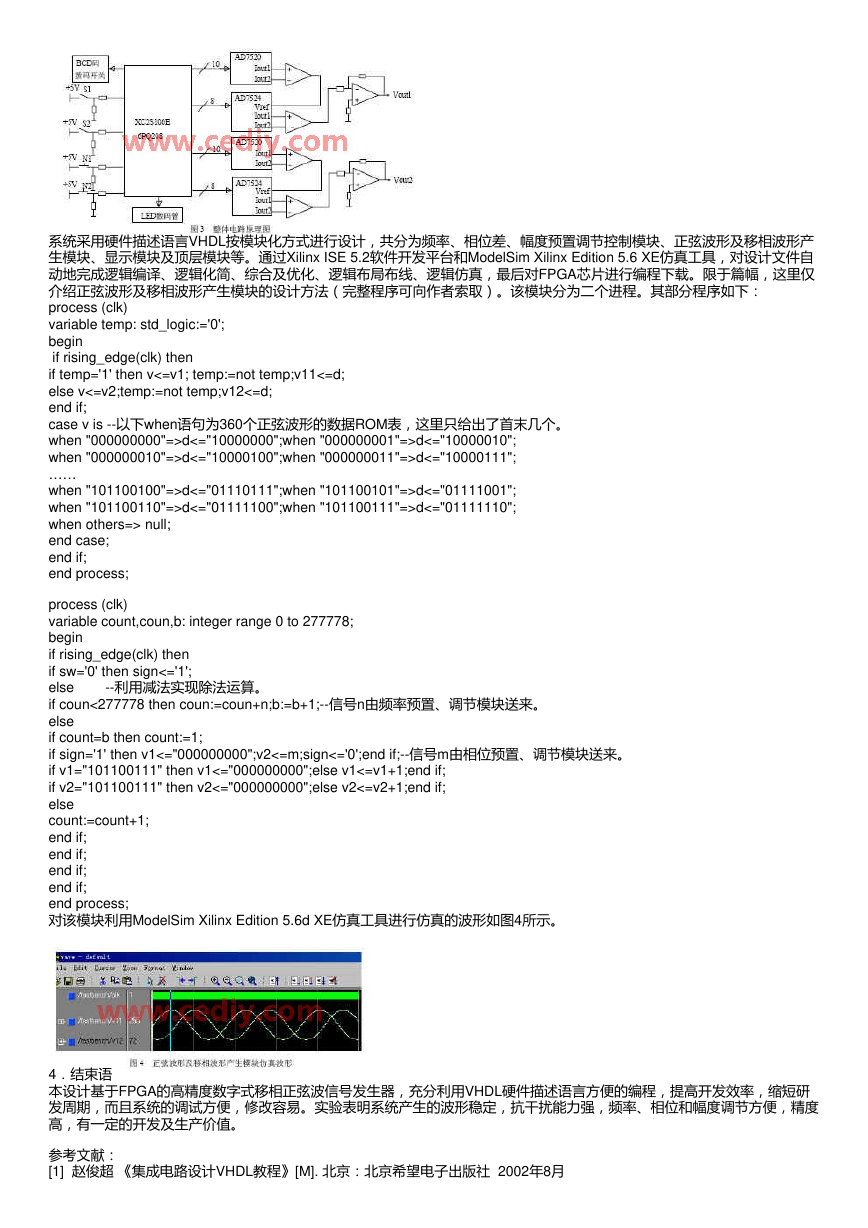

对该模块利用ModelSim Xilinx Edition 5.6d XE仿真工具进行仿真的波形如图4所示。

4.结束语

本设计基于FPGA的高精度数字式移相正弦波信号发生器,充分利用VHDL硬件描述语言方便的编程,提高开发效率,缩短研

发周期,而且系统的调试方便,修改容易。实验表明系统产生的波形稳定,抗干扰能力强,频率、相位和幅度调节方便,精度

高,有一定的开发及生产价值。

参考文献:

[1] 赵俊超 《集成电路设计VHDL教程》[M]. 北京:北京希望电子出版社 2002年8月

�

[2] 潘松、黄继业 编著 《EDA技术实用教程》[M]. 科学出版社 2002年10月

[3] 常晓明 《Verilog-HDL实践与应用系统设计》[M]. 北京:北京航空航天大学出版社 2003年1月

作者简介:朱卫华 (1964-),男,湖南省衡阳县人。南华大学电气工程学院讲师,硕士,1990年北京师范大学物理系毕业, 主

要从事计算机自动检测和仪表技术研究。

通信地址:湖南省衡阳市南华大学电气工程学院,邮编:421001

E-mail:zhuweihua64@hotmail.com

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc