REVEAL INTRODUCTION

FPGA ON-CHIP DEBUG

Lattice Confidential

�

Reveal Training

Agenda

• Highlights

• User Tool Flow

• Key Concepts

• Tool Details

• Summary

• JTAG Builder Flow

Lattice Diamond Reveal

Page: 2

© 2010 Lattice Semiconductor Corporation

�

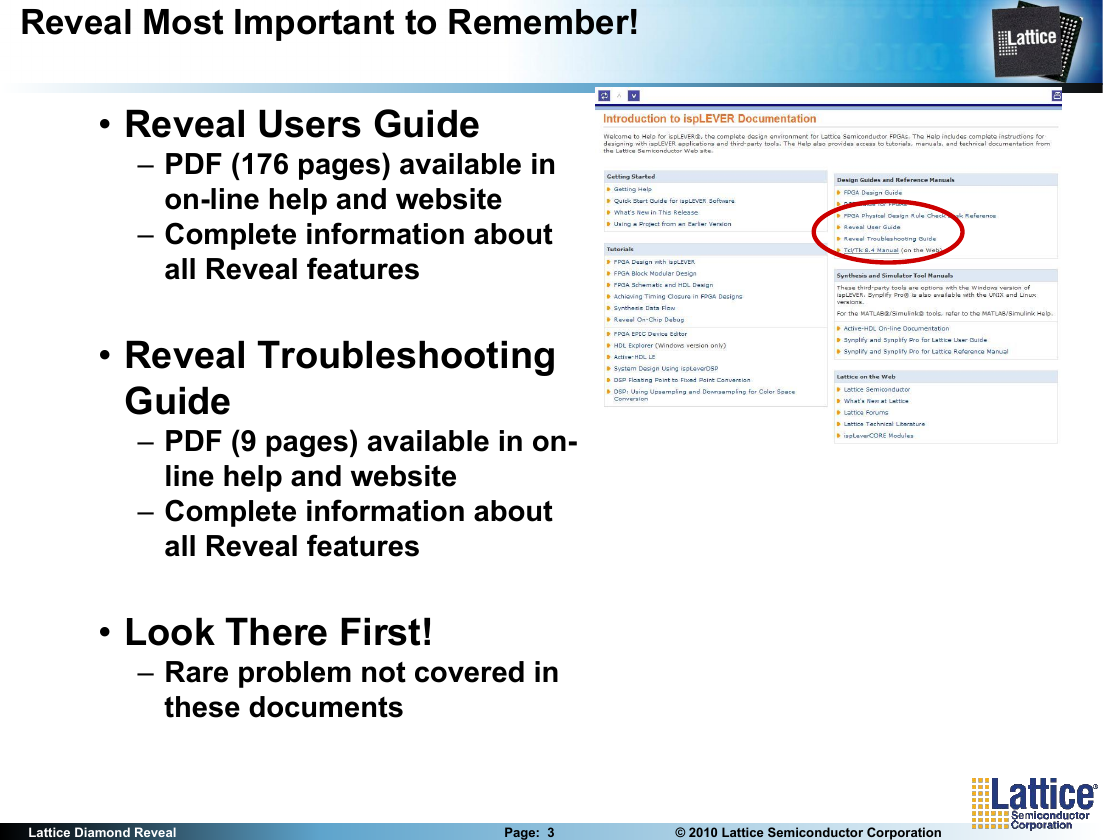

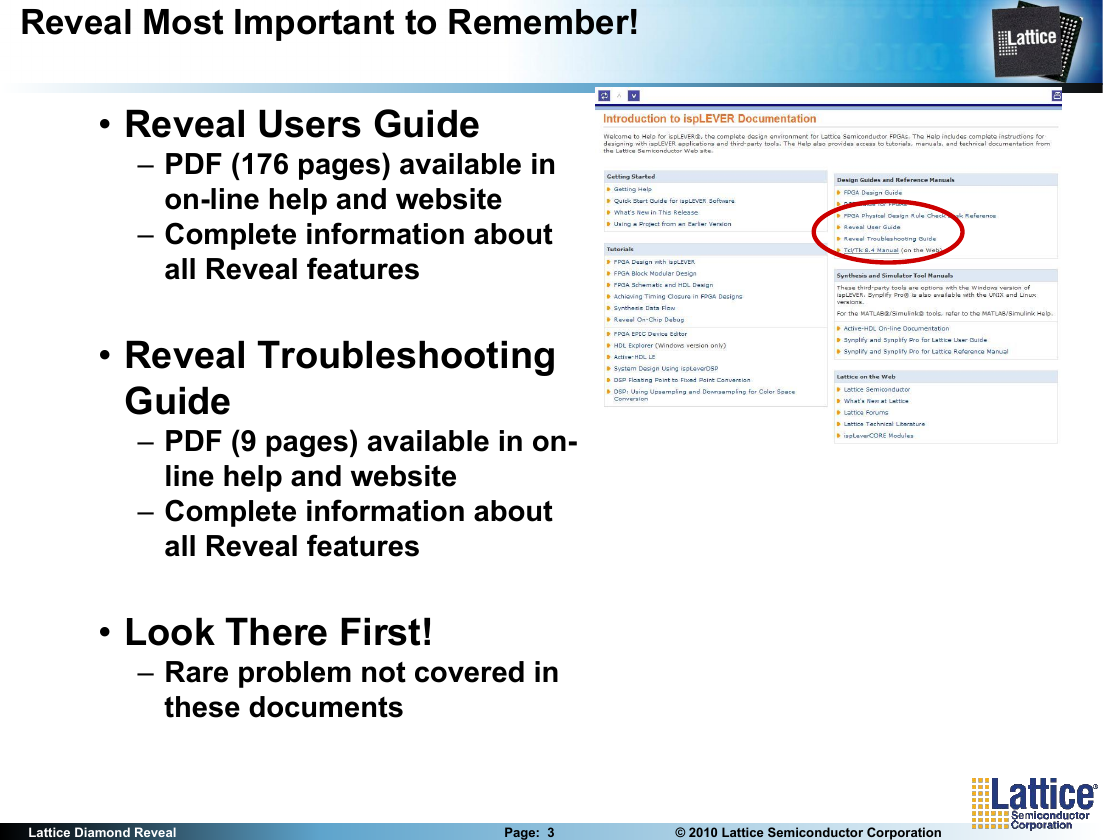

Reveal Most Important to Remember!

• Reveal Users Guide

on-line help and website

– PDF (176 pages) available in

– Complete information about

all Reveal features

• Reveal Troubleshooting

Guide

– PDF (9 pages) available in on-

line help and website

– Complete information about

all Reveal features

• Look There First!

– Rare problem not covered in

these documents

Lattice Diamond Reveal

Page: 3

© 2010 Lattice Semiconductor Corporation

�

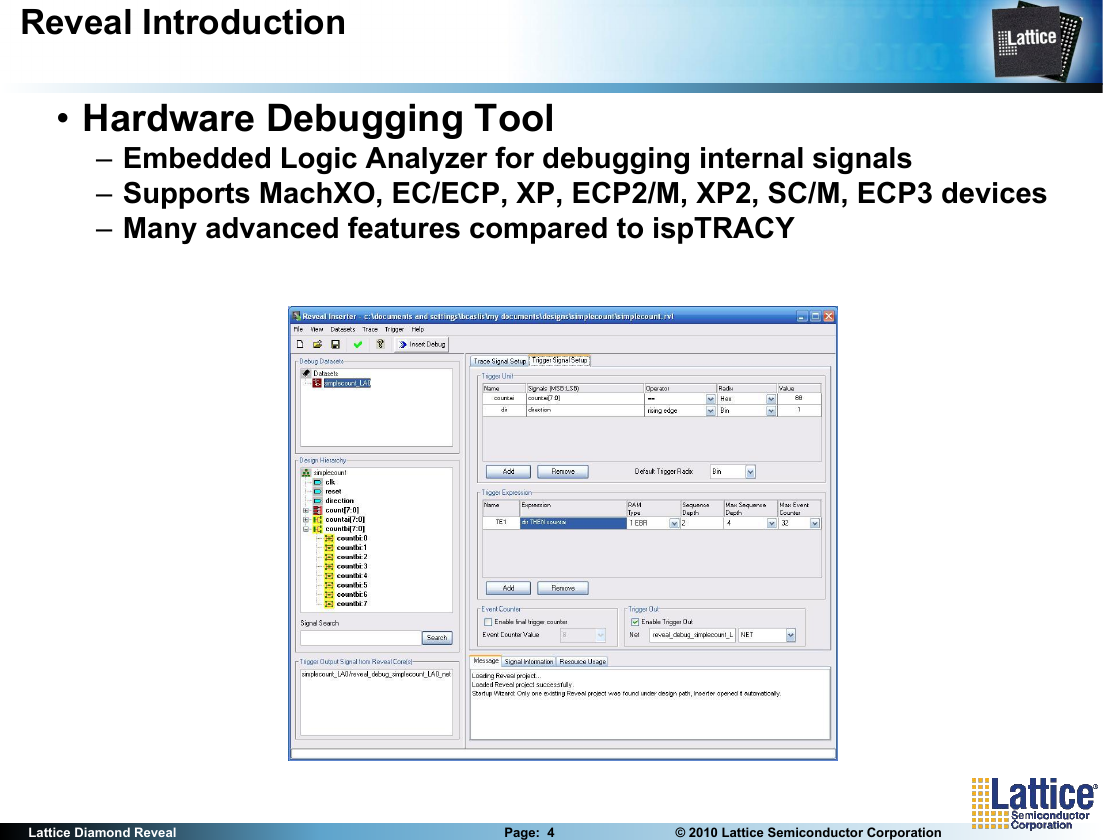

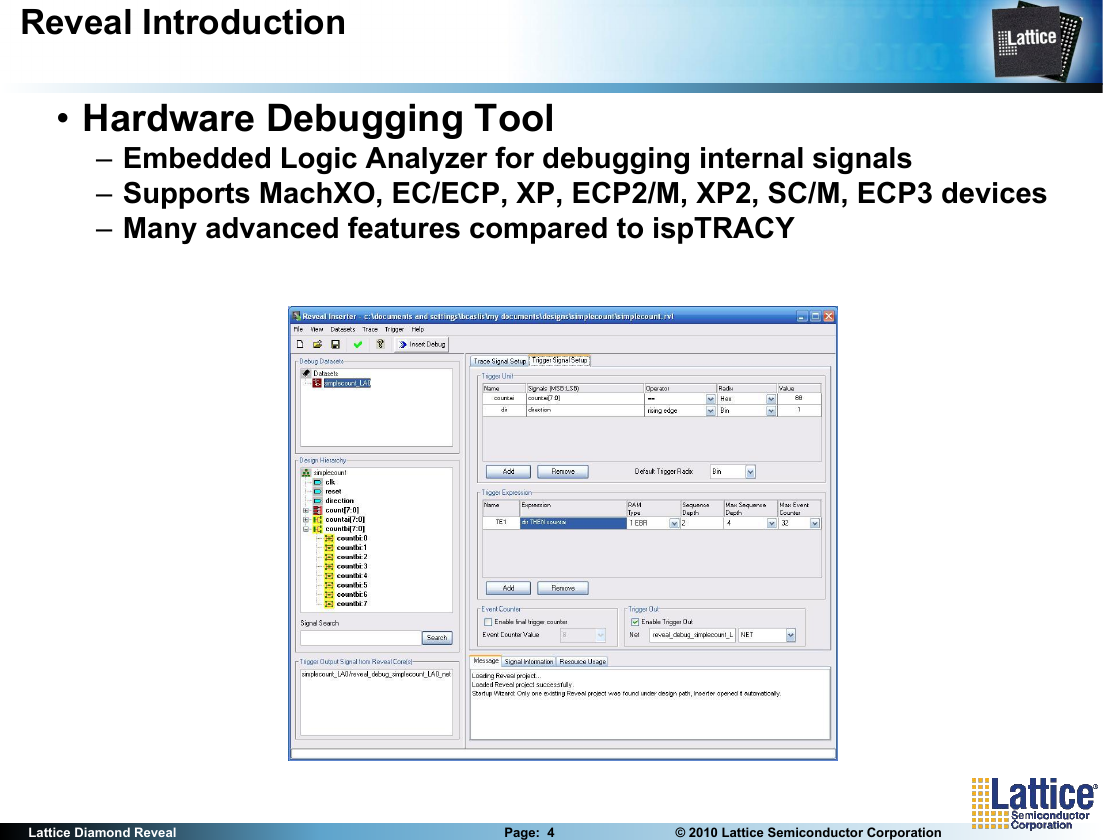

Reveal Introduction

• Hardware Debugging Tool

– Embedded Logic Analyzer for debugging internal signals

– Supports MachXO, EC/ECP, XP, ECP2/M, XP2, SC/M, ECP3 devices

– Many advanced features compared to ispTRACY

Lattice Diamond Reveal

Page: 4

© 2010 Lattice Semiconductor Corporation

�

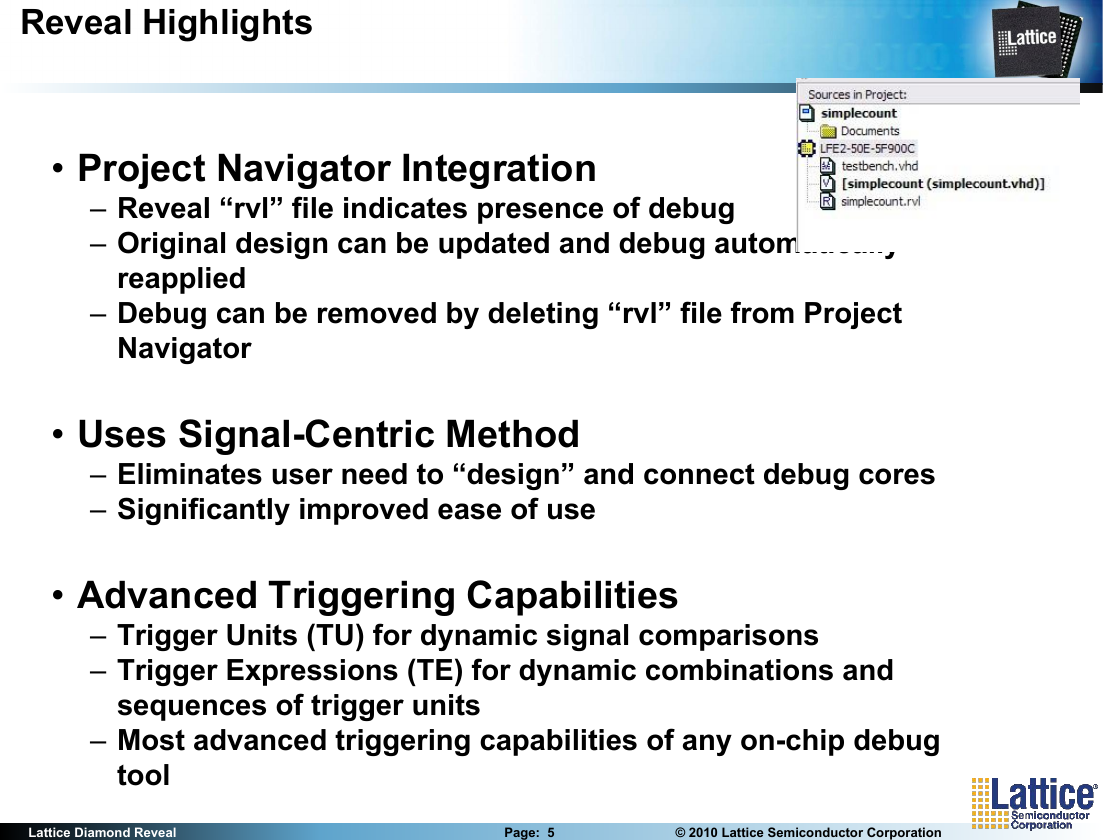

Reveal Highlights

• Project Navigator Integration

– Reveal “rvl” file indicates presence of debug

– Original design can be updated and debug automatically

– Debug can be removed by deleting “rvl” file from Project

reapplied

Navigator

• Uses Signal-Centric Method

– Eliminates user need to “design” and connect debug cores

– Significantly improved ease of use

• Advanced Triggering Capabilities

– Trigger Units (TU) for dynamic signal comparisons

– Trigger Expressions (TE) for dynamic combinations and

sequences of trigger units

– Most advanced triggering capabilities of any on-chip debug

tool

Lattice Diamond Reveal

Page: 5

© 2010 Lattice Semiconductor Corporation

�

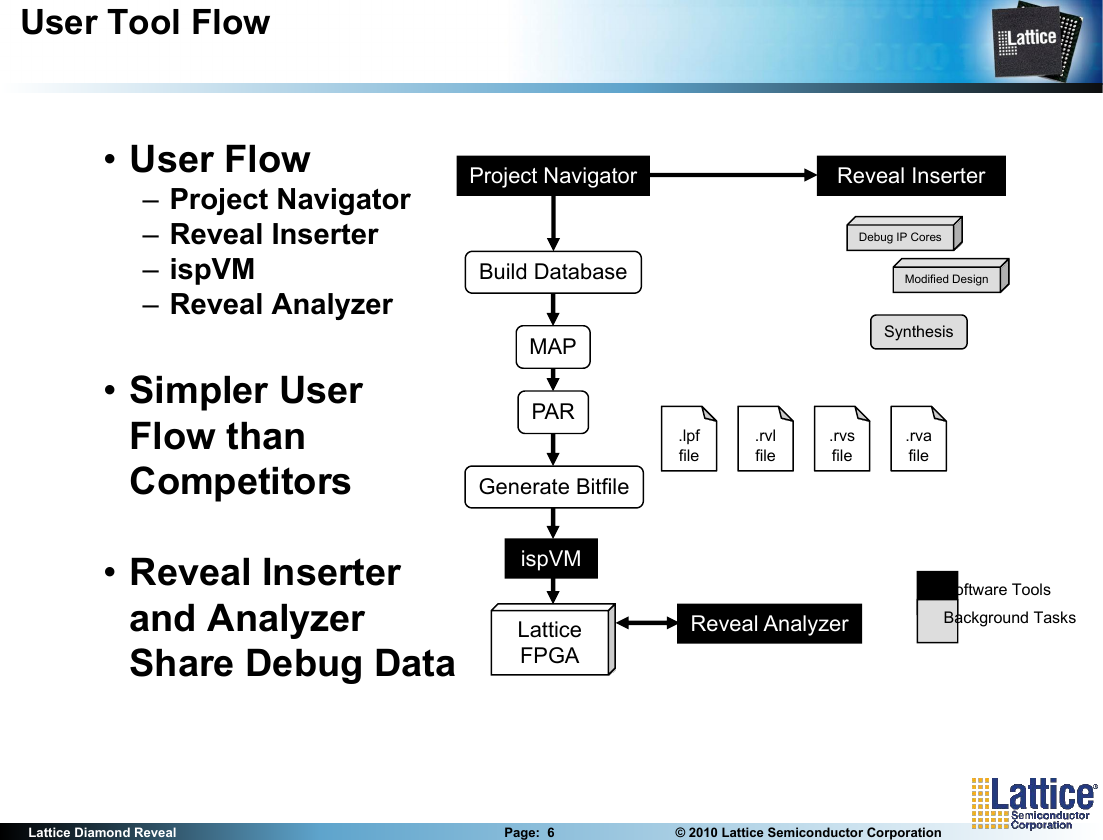

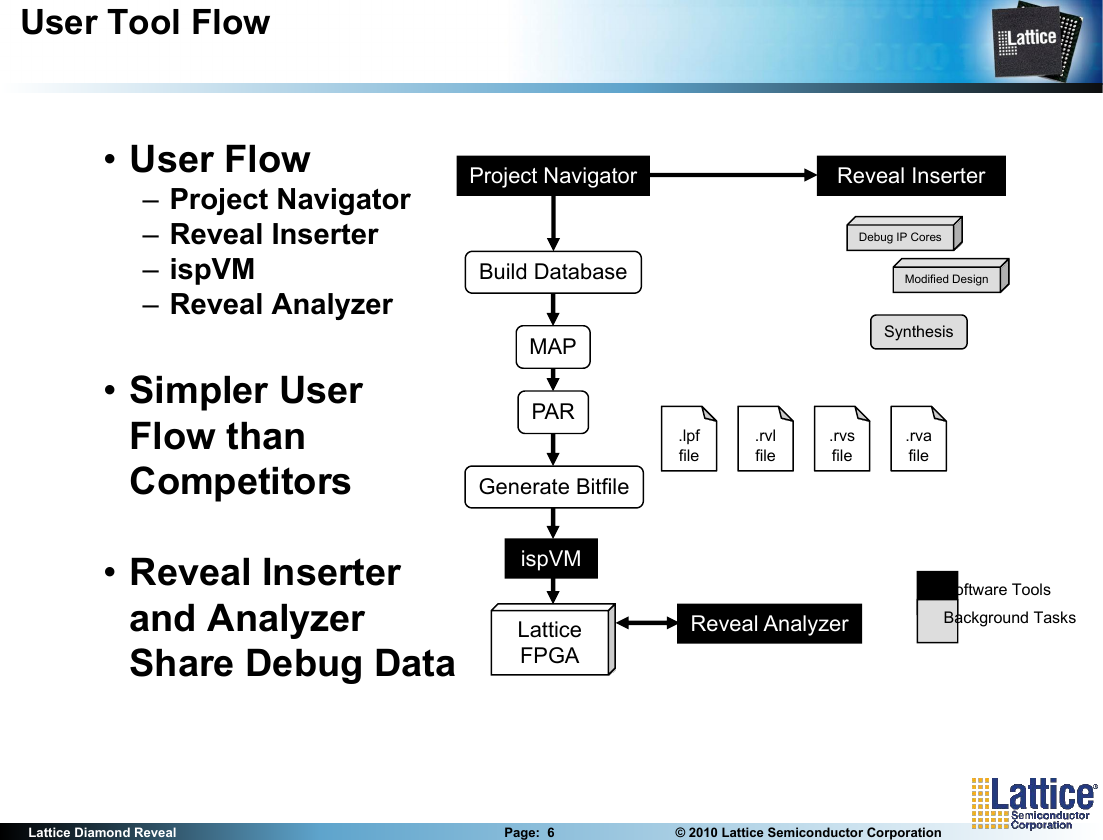

User Tool Flow

• User Flow

– Project Navigator

– Reveal Inserter

– ispVM

– Reveal Analyzer

• Simpler User

Flow than

Competitors

Project Navigator

Reveal Inserter

Build Database

MAP

PAR

Generate Bitfile

Debug IP Cores

Modified Design

Synthesis

.lpf

file

.rvl

file

.rvs

file

.rva

file

• Reveal Inserter

and Analyzer

Share Debug Data

ispVM

Lattice

FPGA

Reveal Analyzer

Software Tools

Background Tasks

Lattice Diamond Reveal

Page: 6

© 2010 Lattice Semiconductor Corporation

�

Datasets

• FPGA Being Debugged Contains

– User Design

– Debug Logic

• Dataset is a Container for Debug

Information for a Design

– Debug logic can have multiple cores

– Each core has unique sample clock

– Each core has trigger logic & storage buffer

– Each core has unique settings

• Multiple Reveal Project Files can be Saved

Lattice Diamond Reveal

Page: 7

© 2010 Lattice Semiconductor Corporation

�

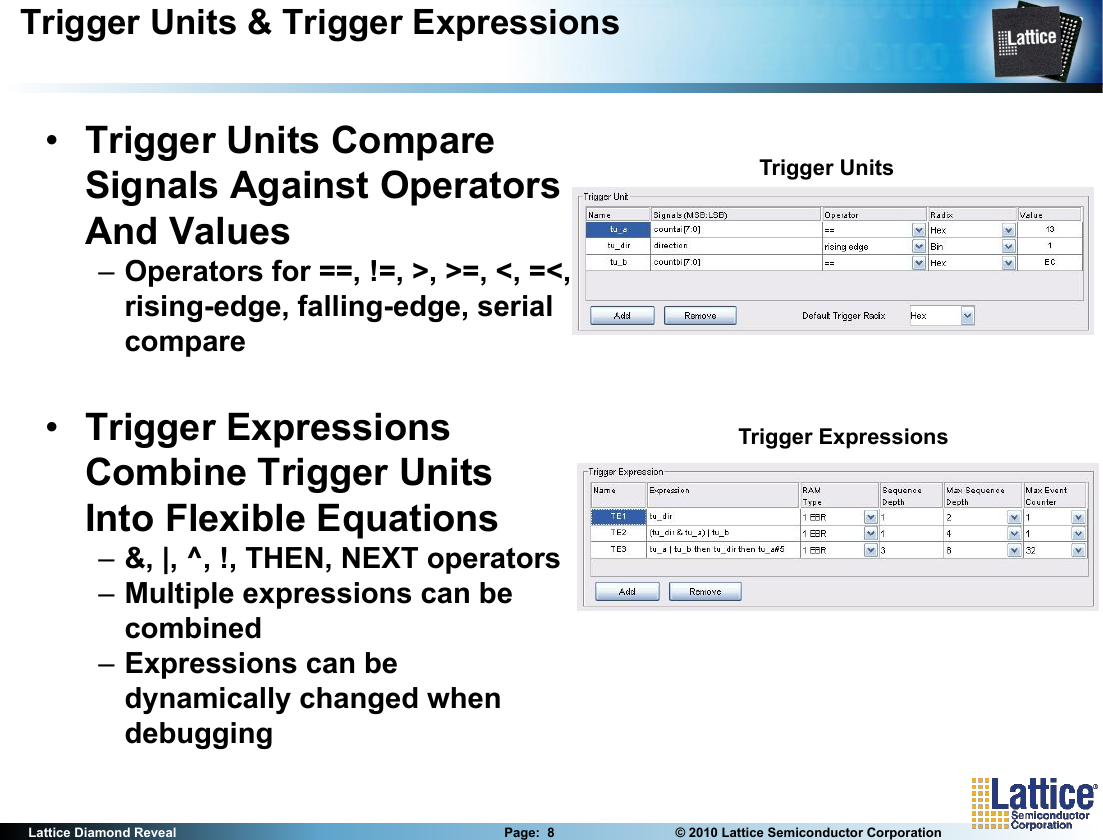

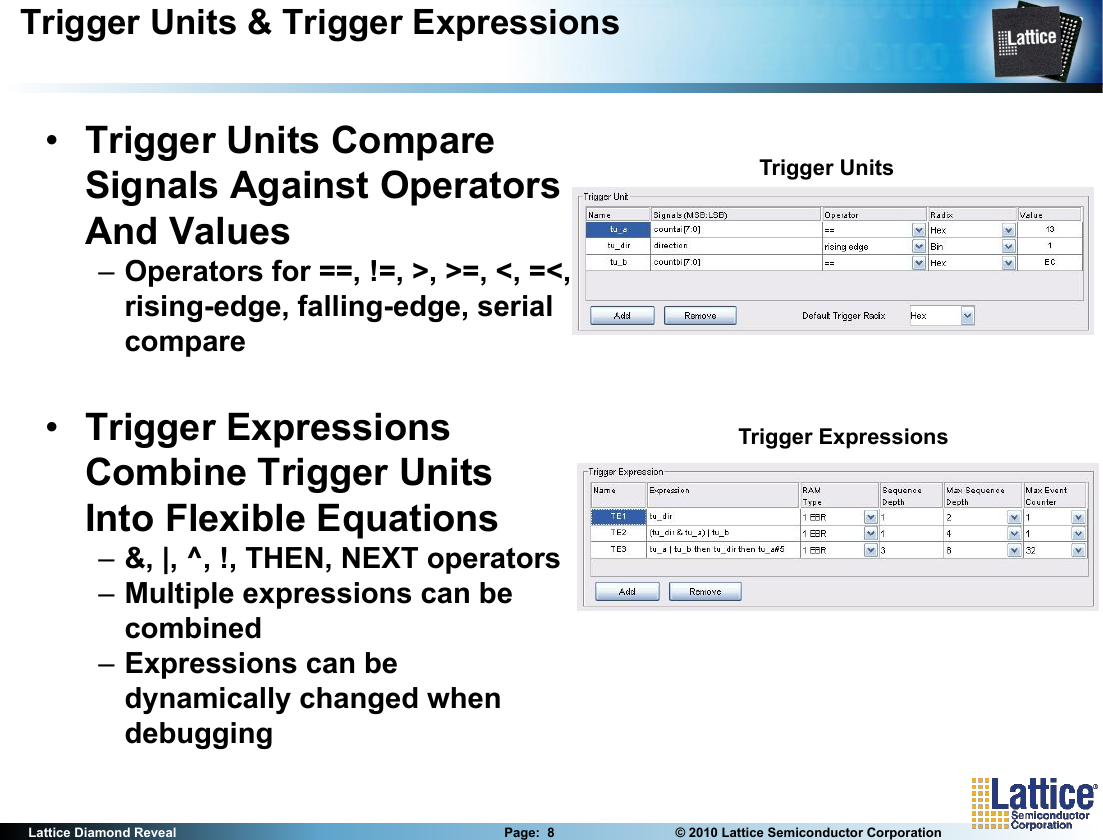

Trigger Units & Trigger Expressions

• Trigger Units Compare

Signals Against Operators

And Values

– Operators for ==, !=, >, >=, <, =<,

rising-edge, falling-edge, serial

compare

• Trigger Expressions

Combine Trigger Units

Into Flexible Equations

– &, |, ^, !, THEN, NEXT operators

– Multiple expressions can be

combined

– Expressions can be

dynamically changed when

debugging

Trigger Units

Trigger Expressions

Lattice Diamond Reveal

Page: 8

© 2010 Lattice Semiconductor Corporation

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc