一种频率稳定的低功耗振荡器电路设计

一种频率稳定的低功耗振荡器电路设计

设计了一种频率稳定的低功耗张弛振荡器电路。采用恒流源对电容两端同时充电和放电,然后将电容两端电压

送入后级比较器进行判决,使得输出频率只与恒流源电流、电容以及比较器比较窗口相关。该电路采用GSMC

0.18 μm CMOS工艺,在5 V电源电压以及室温条件下仿真,输出频率为123.6 kHz,平均电流消耗为2.67 μA;

在2 V~5.5 V电源电压和-40 ℃~+85 ℃的温度变化范围内,输出频率精度在-6.5%~1.3%范围内。

对于大多数SoC(System on a Chip)设计而言,时钟发生器模块是必不可少的组成部分。提供时钟参考源一般有两种方

式[1]:一种是使用晶体

本文设计的振荡器除了作为

1 电路设计与分析

电路设计与分析

1.1 电路结构与原理

电路结构与原理

本文设计的振荡器结构如图1所示,由

其工作原理为:由基准电流源电路产生与电源无关的电流,用该电流的镜像电流对电容进行充放电。其中,当S1为高电平

时,S2为低电平,即此时比较器的输出为低电平。从而通过PMOS管M5对C0的左端N1进行恒流充电,同时通过NMOS管M6

对C0的右端N2进行恒流放电。随着N1点的电位上升N2点电位下降,当N1与N2的电位差大于迟滞比较器的迟滞窗口时,比较

器的输出跳变为高电平,导致S1跳变为低电平,同时S2跳变为高电平。同理,通过PMOS管M5对C0的左端N1进行恒流放

电,同时通过NMOS管M6对C0的右端N2进行恒流充电。N1点电位下降,N2点电位上升,当N2与N1的电位差大于迟滞比较器

的迟滞窗口时,比较器输出反相,变为低电平。从而完成了时钟信号产生一个周期的变化过程。

由于迟滞比较器的输入级采用NMOS管,为了使电容两端的电压在迟滞比较器正常工作输入范围之内,在设计中添加M7,

使得工作时N1、N2点的电压不会低于一个NMOS管的阈值电压和两个过驱动电压之和,从而达到了迟滞比较器正常工作时对

输入电压的要求。

振荡周期公式如下:

其中,ΔV为迟滞比较器的迟滞窗口大小。由式(1)可知振荡周期与迟滞窗口、充放电电流以及电容大小有关。由于充放

电电流是由与电源无关的电流源产生,比较器迟滞窗口也与电源电压无关,因此,电路的输出频率受电源电压的影响较小。

在常见的张弛比较器[5]中,比较器的电压判决通常需要参考源模块提供参考电压用来与电容充放电极板上的电压做比较,

从而产生时钟信号。而参考源的产生需要另外消耗功耗,同时参考源的温度特性会影响输出频率的温度特性。而在本设计中,

通过对电容两端进行充放电,消除了振荡器对参考电压源的需求,从而节省了功耗。

由于S1和S2的反相对称性影响输出时钟信号的占空比,因此采用正反馈结构来提高S1和S2的反相对称性,从而提高了输

出时钟信号的占空比特性。

1.2 与电源电压无关的电流源

与电源电压无关的电流源

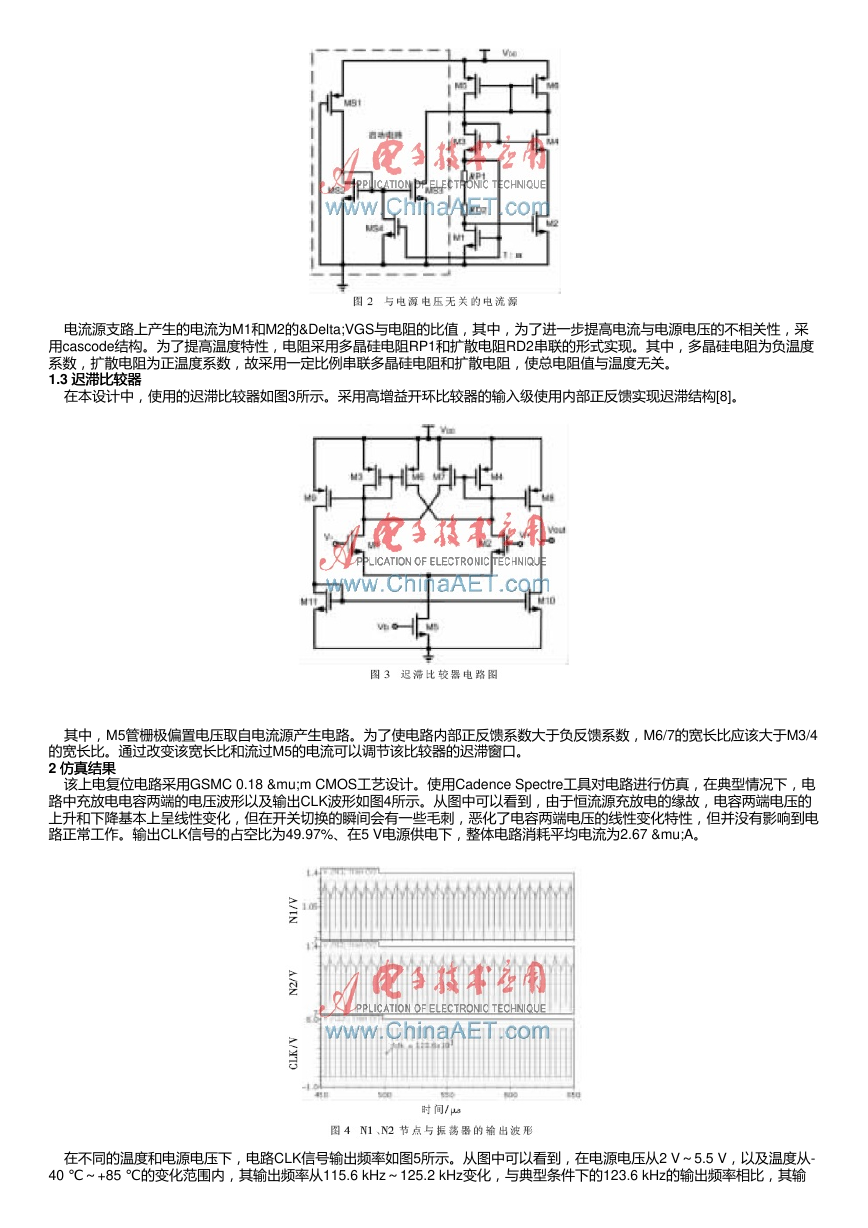

由M1~M6以及RP1和RD2组成与电源电压无关的电流源[6],如图2所示,MS1~MS3为启动电路[7]。正常工作时,MS4管

开启,将MS3管栅极电压拉低,从而MS3管关断,不影响电流源电路正常工作;当电流源处于异常零状态时,M5/6管的栅极

维持高电平,M1/2管的栅极电压保持低电平,MS4管关断,MS3管开启,从而将M5/6管的栅极拉低,使得电流源电路开启。

�

电流源支路上产生的电流为M1和M2的ΔVGS与电阻的比值,其中,为了进一步提高电流与电源电压的不相关性,采

用cascode结构。为了提高温度特性,电阻采用多晶硅电阻RP1和扩散电阻RD2串联的形式实现。其中,多晶硅电阻为负温度

系数,扩散电阻为正温度系数,故采用一定比例串联多晶硅电阻和扩散电阻,使总电阻值与温度无关。

1.3 迟滞比较器

迟滞比较器

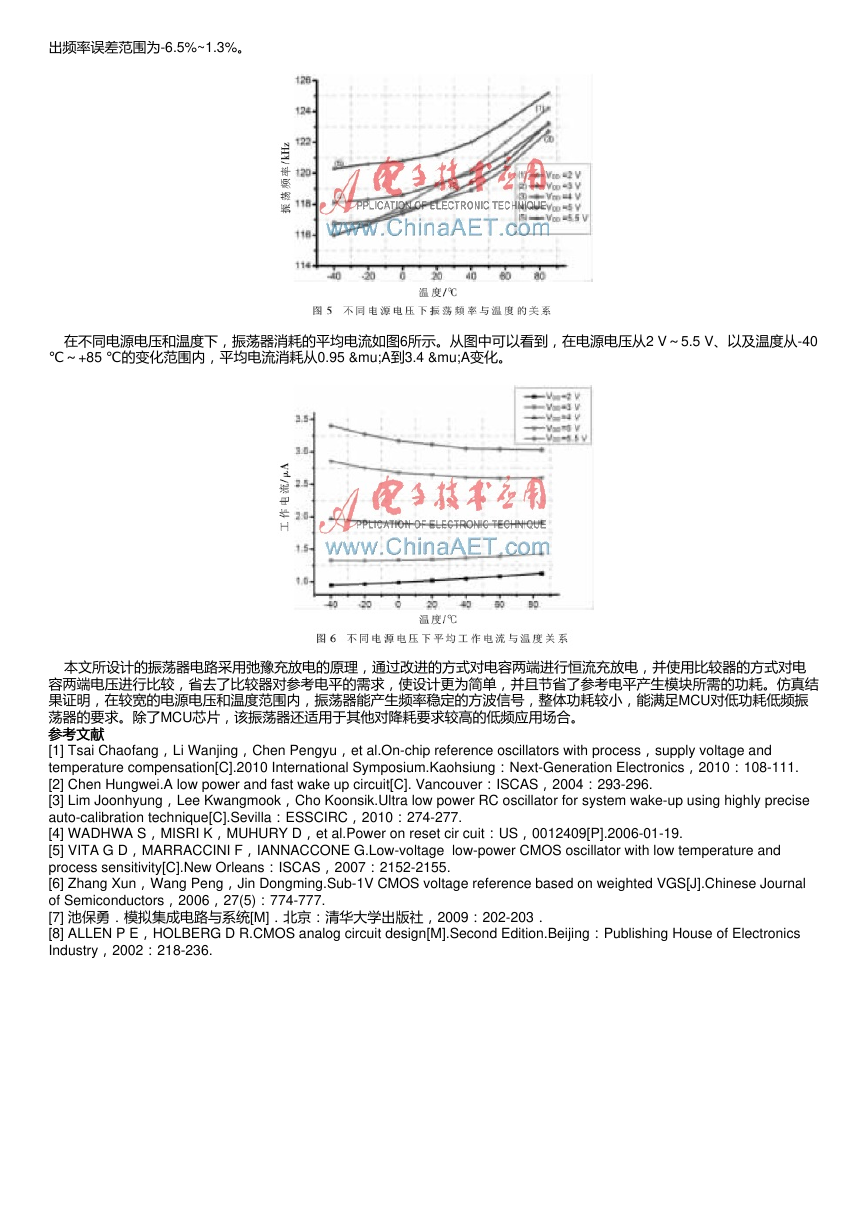

在本设计中,使用的迟滞比较器如图3所示。采用高增益开环比较器的输入级使用内部正反馈实现迟滞结构[8]。

其中,M5管栅极偏置电压取自电流源产生电路。为了使电路内部正反馈系数大于负反馈系数,M6/7的宽长比应该大于M3/4

的宽长比。通过改变该宽长比和流过M5的电流可以调节该比较器的迟滞窗口。

2 仿真结果

仿真结果

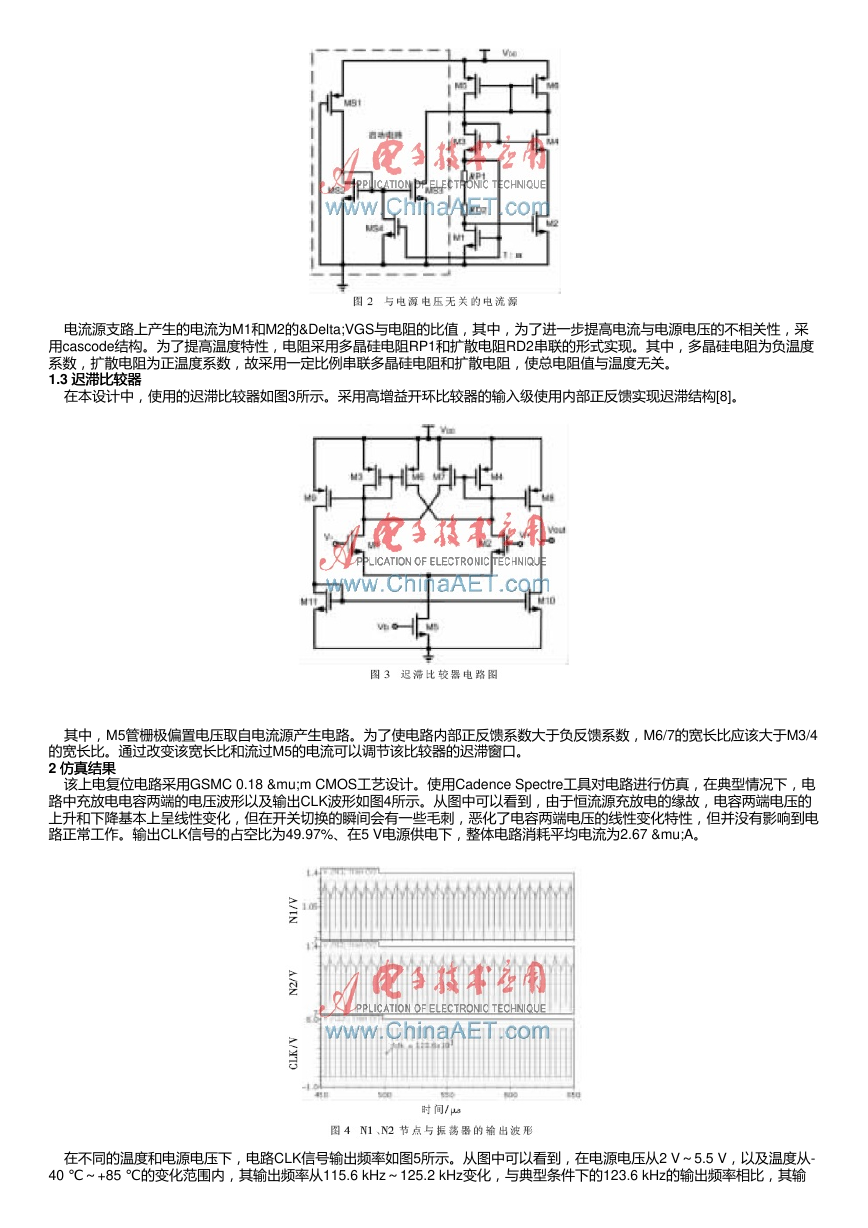

该上电复位电路采用GSMC 0.18 μm CMOS工艺设计。使用Cadence Spectre工具对电路进行仿真,在典型情况下,电

路中充放电电容两端的电压波形以及输出CLK波形如图4所示。从图中可以看到,由于恒流源充放电的缘故,电容两端电压的

上升和下降基本上呈线性变化,但在开关切换的瞬间会有一些毛刺,恶化了电容两端电压的线性变化特性,但并没有影响到电

路正常工作。输出CLK信号的占空比为49.97%、在5 V电源供电下,整体电路消耗平均电流为2.67 μA。

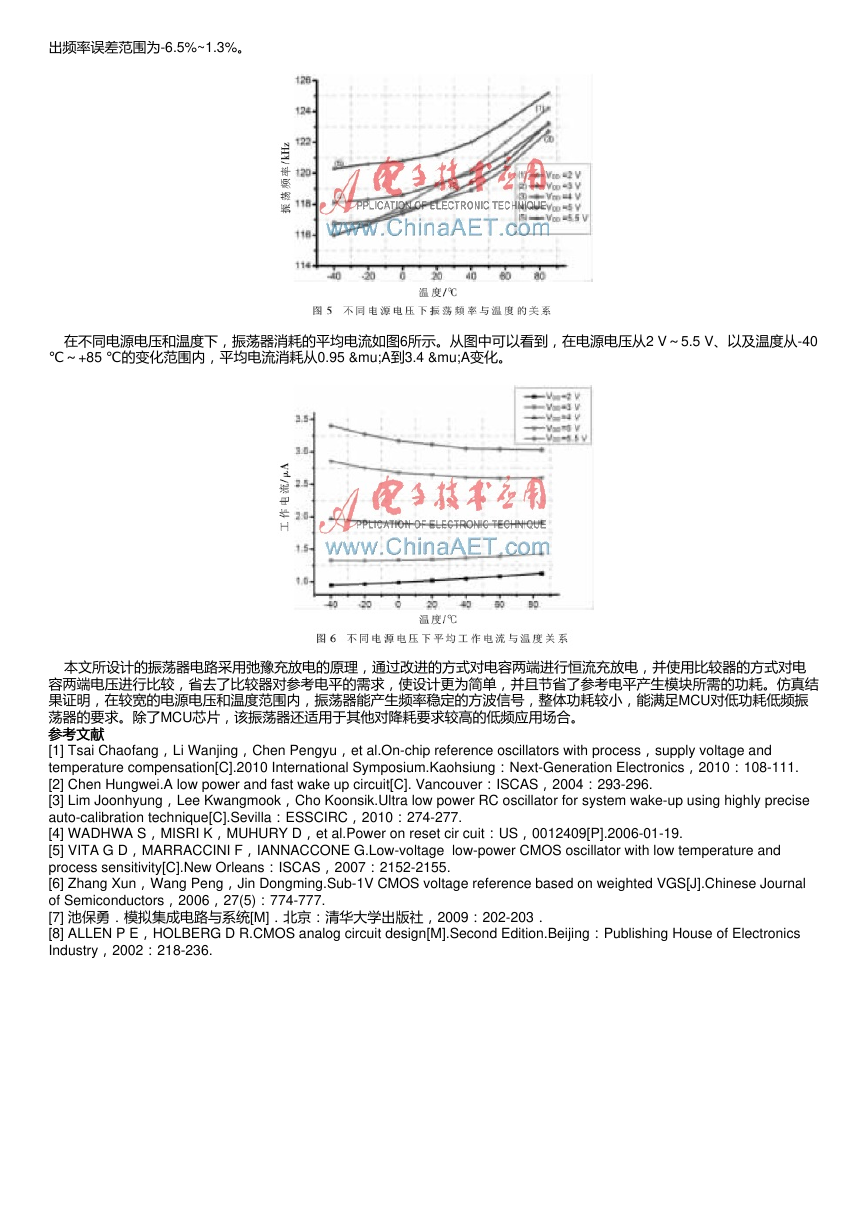

在不同的温度和电源电压下,电路CLK信号输出频率如图5所示。从图中可以看到,在电源电压从2 V~5.5 V,以及温度从-

40 ℃~+85 ℃的变化范围内,其输出频率从115.6 kHz~125.2 kHz变化,与典型条件下的123.6 kHz的输出频率相比,其输

�

出频率误差范围为-6.5%~1.3%。

在不同电源电压和温度下,振荡器消耗的平均电流如图6所示。从图中可以看到,在电源电压从2 V~5.5 V、以及温度从-40

℃~+85 ℃的变化范围内,平均电流消耗从0.95 μA到3.4 μA变化。

本文所设计的振荡器电路采用弛豫充放电的原理,通过改进的方式对电容两端进行恒流充放电,并使用比较器的方式对电

容两端电压进行比较,省去了比较器对参考电平的需求,使设计更为简单,并且节省了参考电平产生模块所需的功耗。仿真结

果证明,在较宽的电源电压和温度范围内,振荡器能产生频率稳定的方波信号,整体功耗较小,能满足MCU对低功耗低频振

荡器的要求。除了MCU芯片,该振荡器还适用于其他对降耗要求较高的低频应用场合。

参考文献

参考文献

[1] Tsai Chaofang,Li Wanjing,Chen Pengyu,et al.On-chip reference oscillators with process,supply voltage and

temperature compensation[C].2010 International Symposium.Kaohsiung:Next-Generation Electronics,2010:108-111.

[2] Chen Hungwei.A low power and fast wake up circuit[C]. Vancouver:ISCAS,2004:293-296.

[3] Lim Joonhyung,Lee Kwangmook,Cho Koonsik.Ultra low power RC oscillator for system wake-up using highly precise

auto-calibration technique[C].Sevilla:ESSCIRC,2010:274-277.

[4] WADHWA S,MISRI K,MUHURY D,et al.Power on reset cir cuit:US,0012409[P].2006-01-19.

[5] VITA G D,MARRACCINI F,IANNACCONE G.Low-voltage low-power CMOS oscillator with low temperature and

process sensitivity[C].New Orleans:ISCAS,2007:2152-2155.

[6] Zhang Xun,Wang Peng,Jin Dongming.Sub-1V CMOS voltage reference based on weighted VGS[J].Chinese Journal

of Semiconductors,2006,27(5):774-777.

[7] 池保勇.模拟集成电路与系统[M].北京:清华大学出版社,2009:202-203.

[8] ALLEN P E,HOLBERG D R.CMOS analog circuit design[M].Second Edition.Beijing:Publishing House of Electronics

Industry,2002:218-236.

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc