JESD204 v7.2

Table of Contents

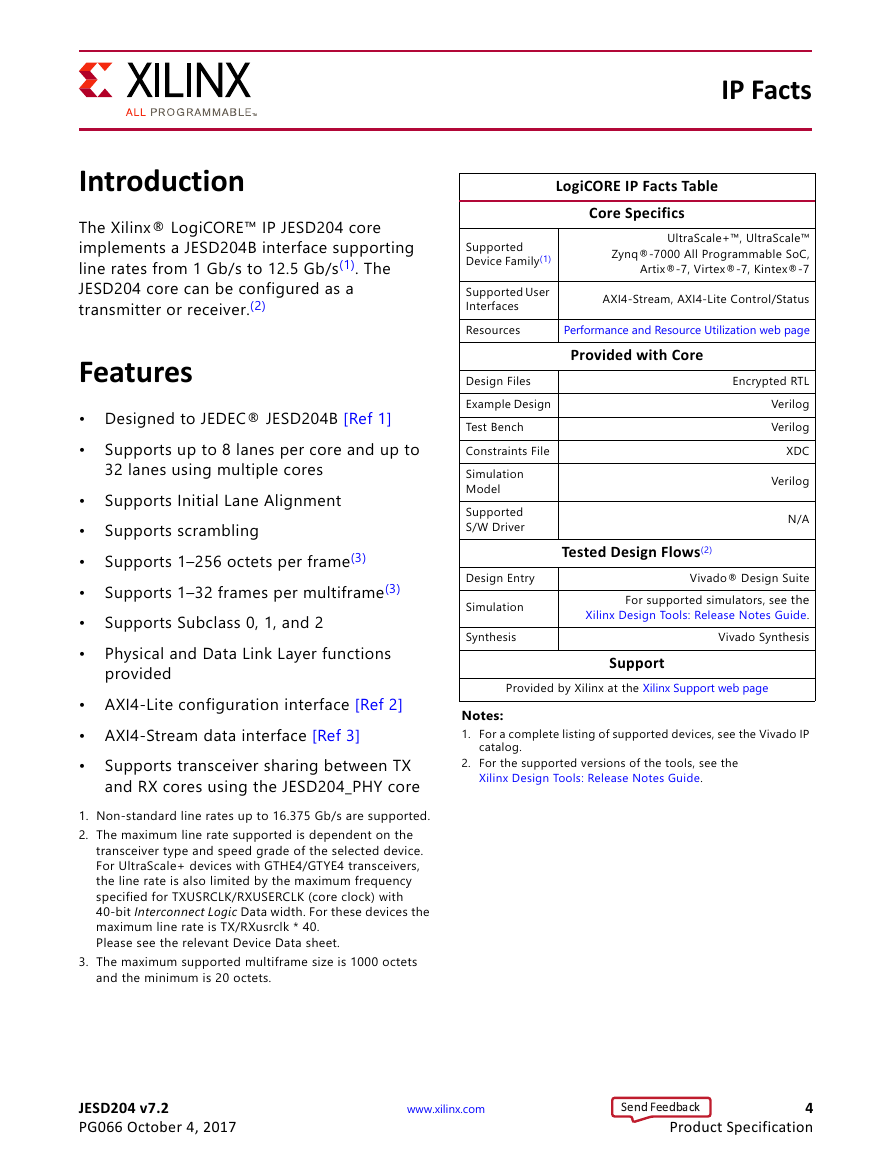

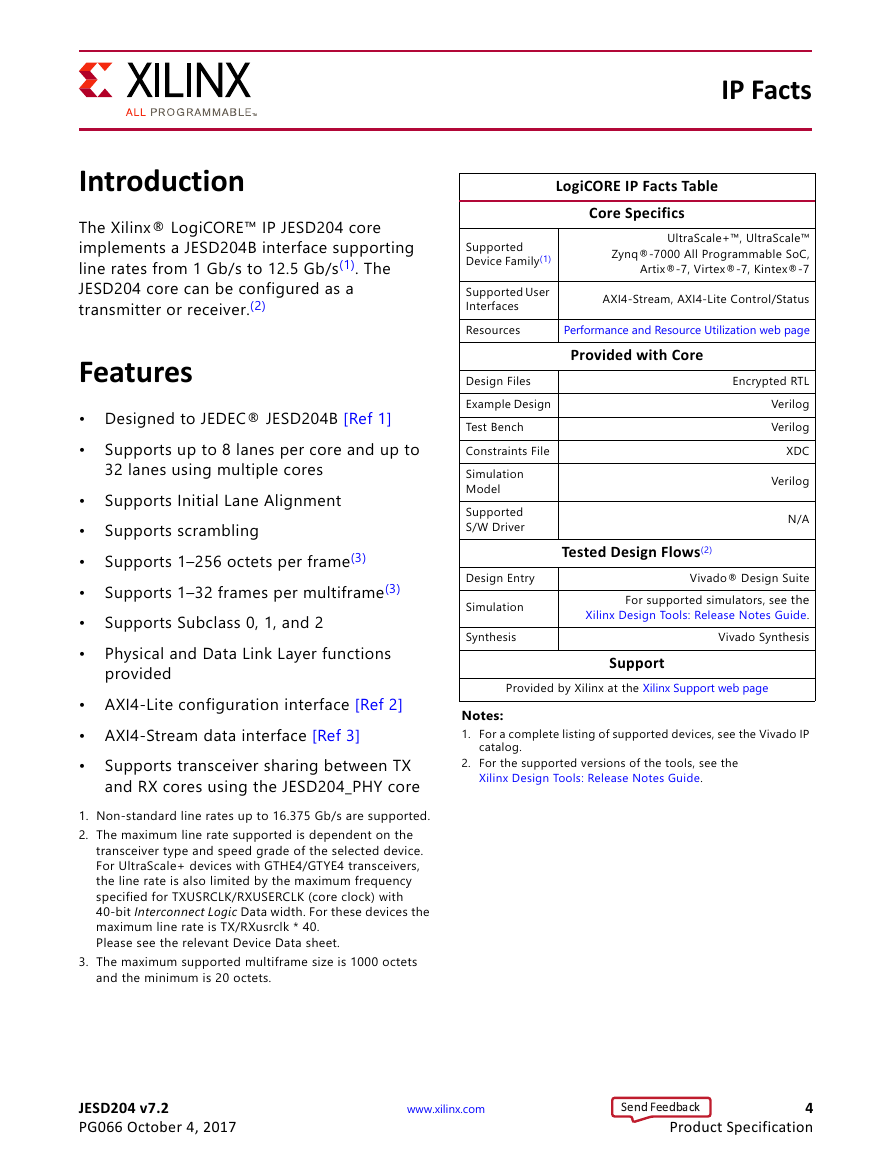

IP Facts

Ch. 1: Overview

Transmitter

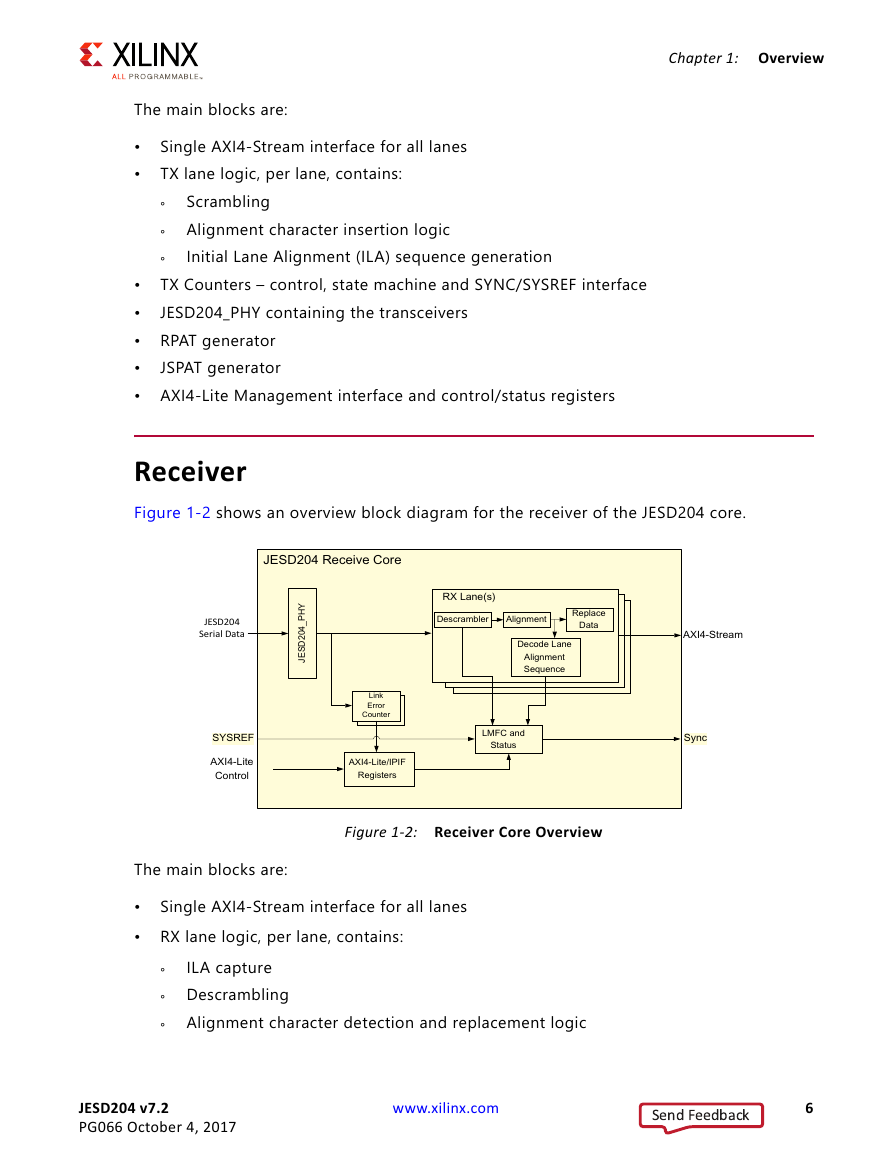

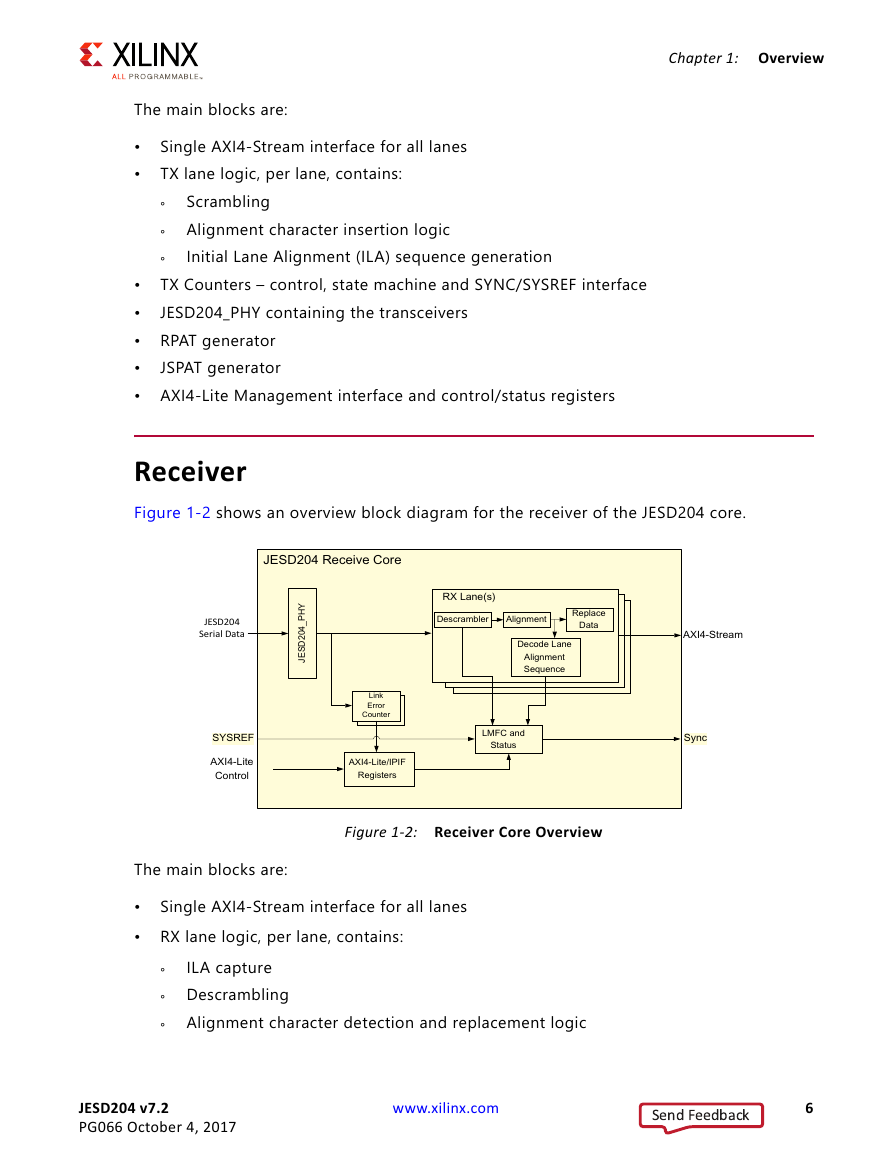

Receiver

Core Level Architecture

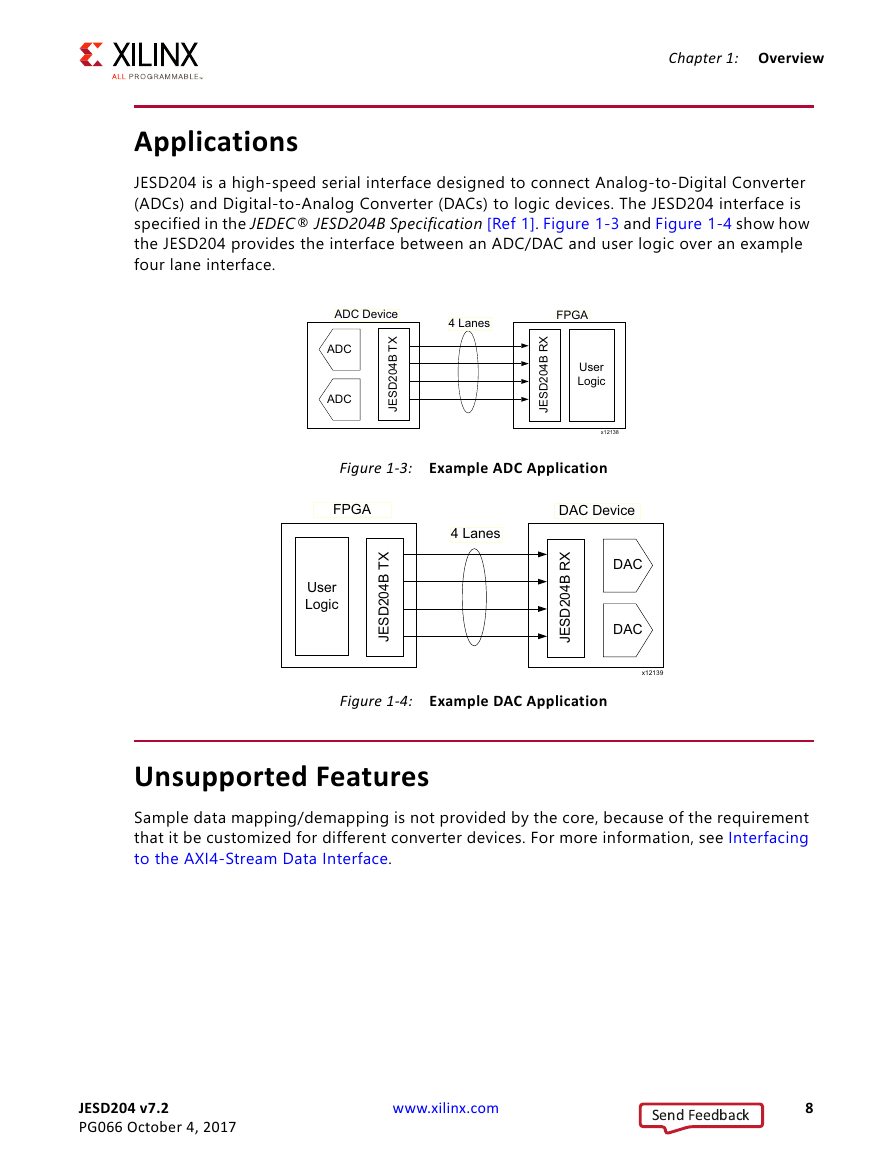

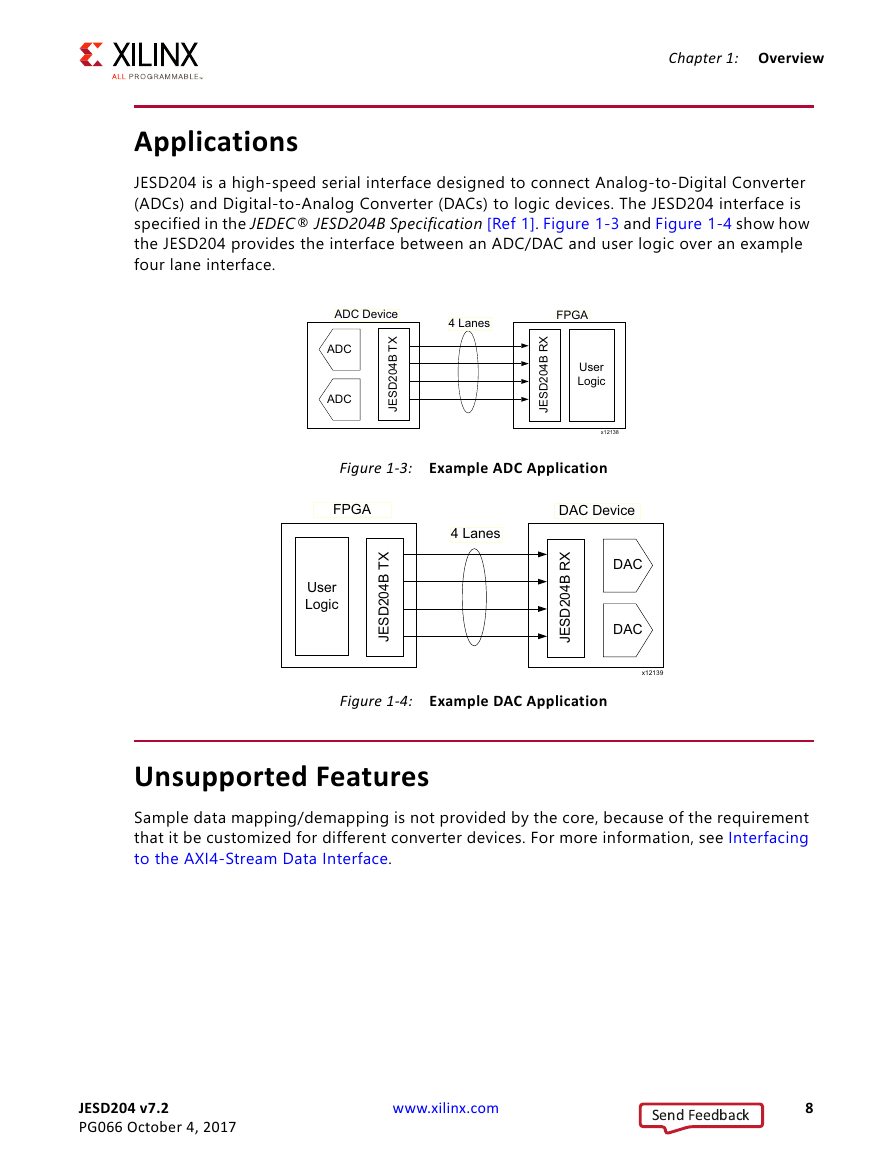

Applications

Unsupported Features

Licensing and Ordering Information

License Checkers

License Type

License Options

Simulation Only

Full System Hardware Evaluation

Full

Obtaining Your License Key

Simulation License

Full System Hardware Evaluation License

Obtaining a Full License

Installing Your License File

Ch. 2: Product Specification

Standards

Performance

Resource Utilization

Port Descriptions

Clock and Reset Ports – TX Core

Clock and Reset Ports – RX Core

JESD204 PHY and Transceiver Interface Ports – TX Core

JESD204 PHY and Transceiver Interface Ports – RX Core

Transmit Data Interface – TX Core

Receive Data Interface – RX Core

Management Interface (AXI4-Lite)

Transceiver Debug Interface

Register Space

Ch. 3: Designing with the Core

General Design Guidelines

Use the Example Design as a Starting Point

Know the Degree of Difficulty

Keep It Registered

Recognize Timing Critical Signals

Use Supported Design Flows

Make Only Allowed Modifications

Recommended Design Experience

Core Overview and Getting Started

Serial Line Rate and Clocking

Core Clock

Reference Clock

AXI4-Lite Interface Clock

Selecting the Operating Line Rate and Reference Clock

Core Delivery – Shared Logic Example Design

Transceiver Sharing

Subclass Mode

Subclass 0

Subclass 1

Subclass 2

Programming the Core

Clocking

Supporting Subclass 1 and 2 Deterministic Latency

Number of lanes per link

Basic Generic Clocking Schemes

7 Series Devices

UltraScale Devices

7 Series Devices

UltraScale and UltraScale+ Devices

Supported Clock Frequency Ranges

Detailed Clocking

Clocking for Subclass 0 Mode

Resets

System Reset

Software Reset

Watchdog Timer Reset

AXI4-Stream Reset

Interfacing to the AXI4-Stream Data Interface

Transport Layer

TI ADS42JB69 ADC 2 Converter, 4 Lane Mode

ADI AD9250 ADC 2 Converter, 2 Lane Mode

IDT ADC1443D ADC 2 Converter, 2 Lane Mode

AXI4-Lite Management Interface

Subclass 1 Operation

SYSREF Timing

SYSREF Handling

SYSREF Sampling Clock Edge

SYSREF Always

SYSREF on Initial Link Bring-Up

SYSREF on Link Resynchronization

SYSREF Delay

Subclass 2 Operation

JESD204B Receiver

Lane Skew

Elastic Buffer Implementation

Receive Latency

RX End to End Latency

ADC Timing

Core Timing

Calculating End to End Latency

Achieving Repeatable Latency

Procedure - Achieving Repeatable Latency

Minimum Deterministic Latency Support

Error Signaling Using the SYNC~ Interface

Link Re-initialization

JESD204B Transmitter

Transmit Latency

TX End to End Latency

Core Timing

DAC Timing

Calculating End to End Latency

Step 1 – Determine how many LMFC periods are required (N)

Step 2 – Calculate the end to end latency using N

Example

Transmitter Phase Adjustment for Subclass 2

Link Test Modes

Continuous D21.5 Characters

Modified RPAT

JSPAT

Transceiver PRBS test patterns

Link Re-initialization

Sharing Transceivers between Transmit and Receive

Sharing Transceivers in IP Integrator

Sharing a QPLL

Sharing Transceivers in RTL Designs

Powering down unused GT channels

Ch. 4: Design Flow Steps

Customizing and Generating the Core

Configuration Tab

Link Configuration Tab

Shared Logic Tab

JESD204 PHY Configuration Tab

User Parameters

Output Generation

Constraining the Core

Required Constraints

Device, Package, and Speed Grade Selections

Clock Frequencies

SYSREF Constraints

Clock Domains

Clock Management

Clock Placement

Banking

Transceiver Placement

I/O Standard and Placement

Simulation

Synthesis and Implementation

Ch. 5: Example Design

Common Design Elements

Transport Layer Mapping

sysref Generation

TX Block Layout

TX Transport Layer Mapping

RX Block Layout

RX Transport Layer Mapping

Ch. 6: Test Bench

Appx. A: Verification, Compliance, and Interoperability

Simulation

Hardware Testing

Appx. B: Hardware Demonstration Design

Appx. C: Migrating and Upgrading

Migrating to the Vivado Design Suite

Upgrading in the Vivado Design Suite

Device Migration

Upgrading from v7.0 to v7.1

Upgrading from JESD204 v6.2 to v7.0

Upgrading from JESD204 v6.1 to v6.2

Upgrading from JESD204 v6.0 to v6.1

Upgrading from JESD204 v5.2 to v6.0

Transmitter with Shared Logic in Example Design

Transmitter with Shared Logic in Example Design Converted to Include Shared Logic in Core

Receiver with Shared Logic in Example Design

Receiver with Shared Logic in Example Design Converted to Include Shared Logic in Core

Transmitter with Shared Logic in Core

Receiver with Shared Logic in Core

Appx. D: Debugging

Finding Help on Xilinx.com

Documentation

Answer Records

Technical Support

Debug Tools

Vivado Design Suite Debug Feature

Reference Boards

Simulation Debug

Hardware Debug

General Checks

Issues Obtaining Lane Synchronization

Issues Losing Synchronization Soon After Gaining Synchronization

Interface Debug

AXI4-Lite Interfaces

Appx. E: Additional Resources and Legal Notices

Xilinx Resources

References

Revision History

Please Read: Important Legal Notices

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc