5

4

3

2

1

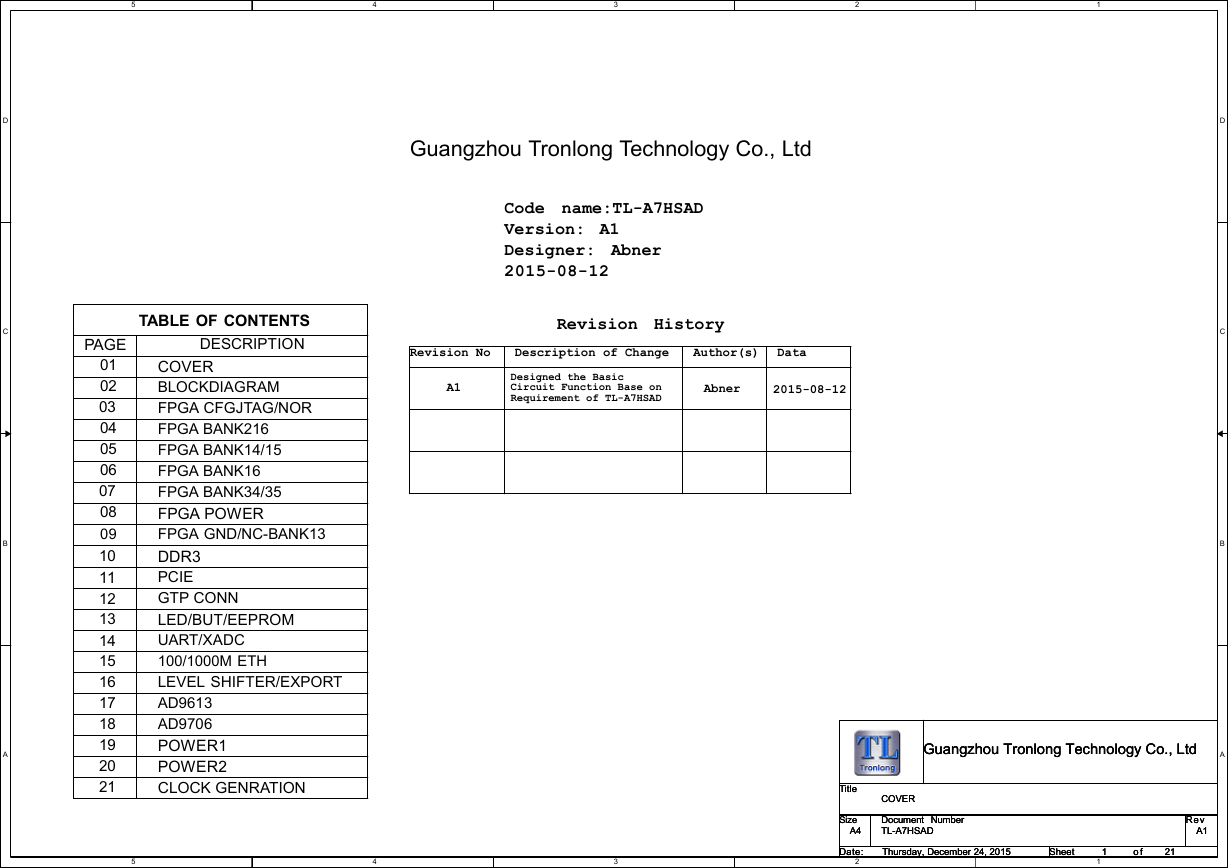

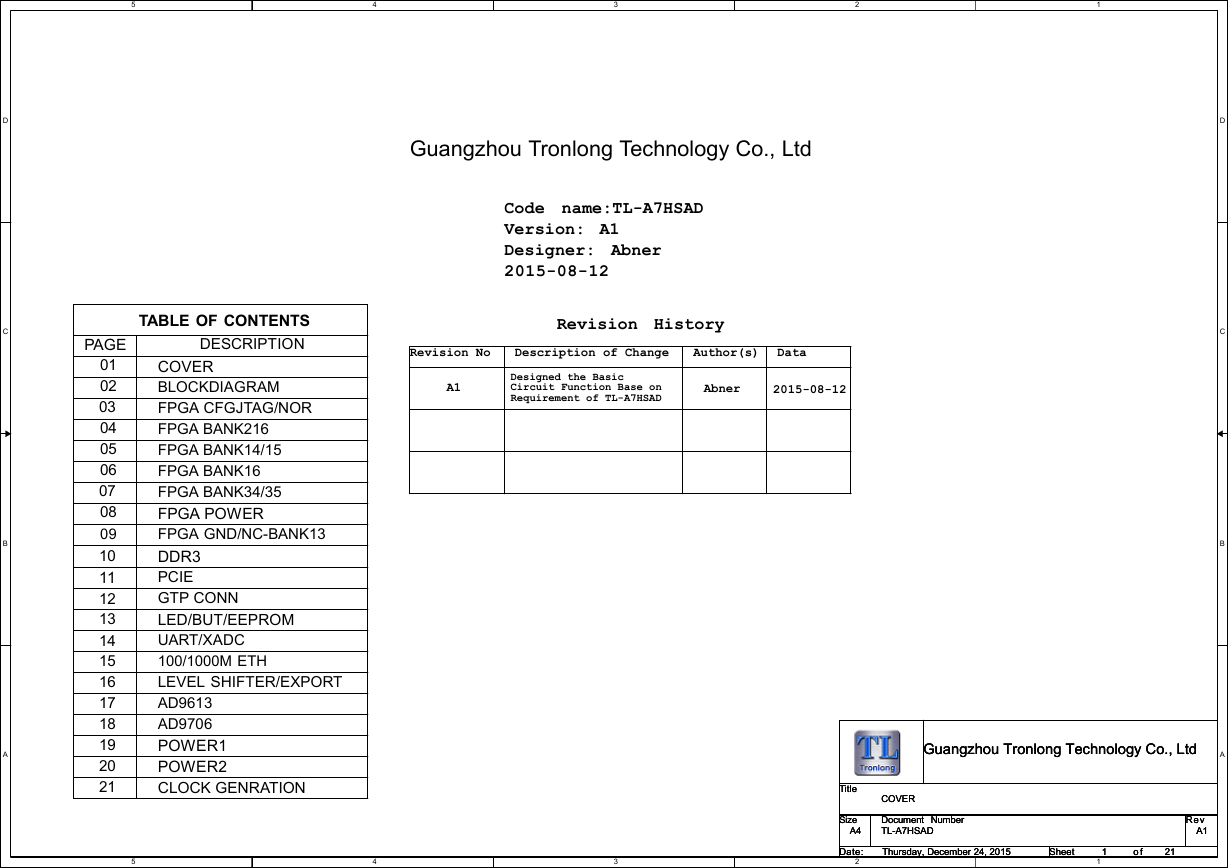

Guangzhou Tronlong Technology Co., Ltd

Code name:TL-A7HSAD

Version: A1

Designer: Abner

2015-08-12

Revision History

Revision No

Description of Change

Author(s)

Data

A1

Designed the Basic

Circuit Function Base on

Requirement of TL-A7HSAD

Abner

2015-08-12

D

C

B

D

C

B

A

TABLE OF CONTENTS

PAGE

DESCRIPTION

01

02

03

04

05

06

07

08

09

10

11

12

13

14

15

16

17

18

19

20

21

COVER

BLOCKDIAGRAM

FPGA CFGJTAG/NOR

FPGA BANK216

FPGA BANK14/15

FPGA BANK16

FPGA BANK34/35

FPGA POWER

FPGA GND/NC-BANK13

DDR3

PCIE

GTP CONN

LED/BUT/EEPROM

UART/XADC

100/1000M ETH

LEVEL SHIFTER/EXPORT

AD9613

AD9706

POWER1

POWER2

CLOCK GENRATION

5

4

3

Guangzhou Tronlong Technology Co., Ltd

Guangzhou Tronlong Technology Co., Ltd

Guangzhou Tronlong Technology Co., Ltd

A

Title

Title

Title

Size

Size

Size

A4

A4

A4

Date:

Date:

Date:

2

COVER

COVER

COVER

Document Number

Document Number

Document Number

TL-A7HSAD

TL-A7HSAD

TL-A7HSAD

R e v

R e v

R e v

A1

A1

A1

Thursday, December 24, 2015

Thursday, December 24, 2015

Thursday, December 24, 2015

Sheet

Sheet

Sheet

1

1

1

1

o f

o f

o f

21

21

21

�

D

C

B

A

5

4

3

2

1

D

C

B

5

4

3

Guangzhou Tronlong Technology Co., Ltd

Guangzhou Tronlong Technology Co., Ltd

Guangzhou Tronlong Technology Co., Ltd

A

Title

Title

Title

Size

Size

Size

A4

A4

A4

Date:

Date:

Date:

2

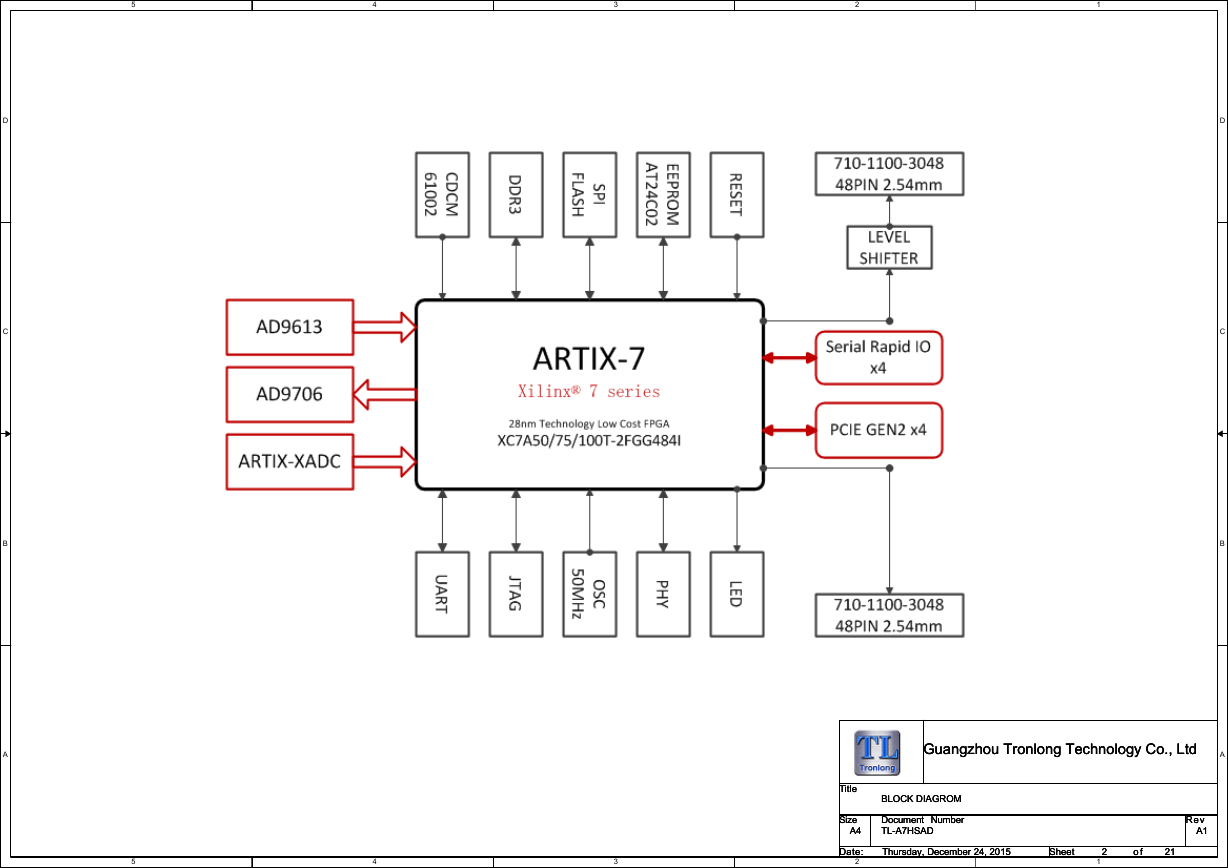

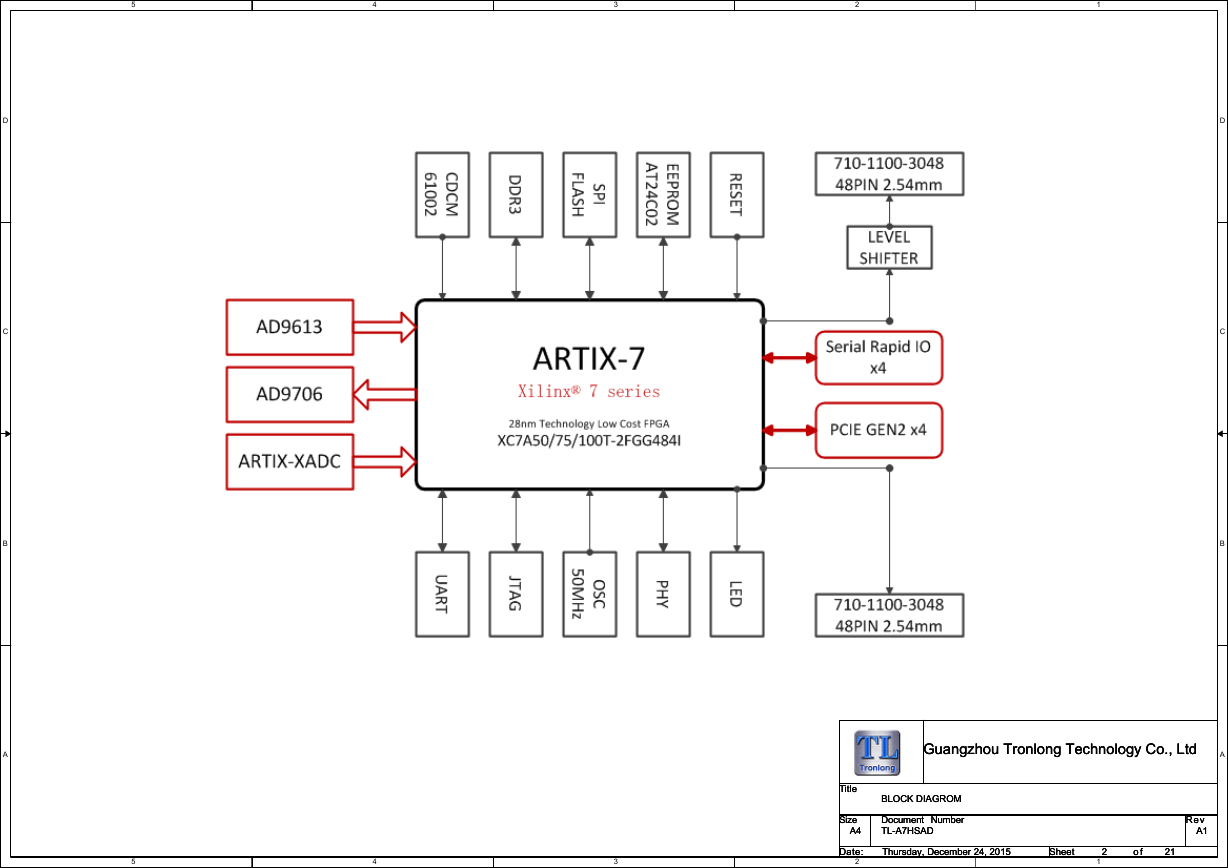

BLOCK DIAGROM

BLOCK DIAGROM

BLOCK DIAGROM

Document Number

Document Number

Document Number

TL-A7HSAD

TL-A7HSAD

TL-A7HSAD

R e v

R e v

R e v

A1

A1

A1

Thursday, December 24, 2015

Thursday, December 24, 2015

Thursday, December 24, 2015

Sheet

Sheet

Sheet

2

2

2

1

o f

o f

o f

21

21

21

�

5

4

3

2

1

VDD_3V3_FPGA

ROUTING CONSTRAINT:± 150 mil

IIC ADDR:0b1010100(0x54)

TP1

XADC_VREFP

D

U30-1

DXN_0

VCCADC_0

GNDADC_0

DXP_0

VREFN_0

VREFP_0

VP_0

VN_0

VCCBATT_0

CCLK_0

TCK_0

TMS_0

TDO_0

TDI_0

INIT_B_0

PROGRAM_B_0

CFGBVS_0

DONE_0

M0_0

M1_0

M2_0

N9

K10

K9

N10

L9

M10

L10

M9

E12

L12

V12

T13

U13

R13

U12

N12

U8

G11

U11

U10

U9

VDD_3V3_FPGA

XADC_DXN 14

VDD_XADC

XADC_DXP 14

R198

0R

VBATT_FPGA

FPGA_CCLK

XADC_VREF 14

XADC_VP 14

XADC_VN 14

TP2

R226

1K

FPGA_TCK 3

FPGA_TMS 3

FPGA_TDO 3

FPGA_TDI

3

VDD_3V3_FPGA

FPGA_INIT_B

FPGA_PROG

FPGA_DONE

FPGA_M0

FPGA_M1

FPGA_M2

DNP_10K_1%

R1

10K_1%

R2

10K_1%

R3

U2

R4

DNP_10K_1%

3,5

FPGA_SPI_D3

3,5

3,5

FPGA_SPI_CS

FPGA_SPI_D1

1

2

3

4

5

6

7

8

DQ3_HOLD_B

VCC

NC0

NC1

NC2

NC3

S_B

DQ1

C

DQ0

NC7

NC6

NC5

NC4

VSS

DQ2_VPP_WP_B

N25Q256A13ESF40G

16

15

14

13

12

11

10

9

10K_1%

R5

FPGA_CCLK

FPGA_SPI_D0

3,5

FPGA_SPI_D2

3,5

TP3

QSPI FLASH MEMORY

VDD_3V3_FPGA

C

XC7A50/75/100T-2FGG484I

100nF

C2

C3

C1

1uF

100nF

0R

R7

1K_1%

R8

1K_1%

R199

1K_1%

R6

C4

100nF

AGND

FPGA_DONE

330R

R9

LED9

LED_RED

CON1

1

2

3

4

5

6

7

8

9

FPGA_PROG

FPGA_CCLK

CON_2D54_1x9_TH

FPGA_SPI_D3

3,5

FPGA_SPI_D2

3,5

FPGA_SPI_CS 3,5

3,5

FPGA_SPI_D0

3,5

FPGA_SPI_D1

VDD_3V3_FPGA

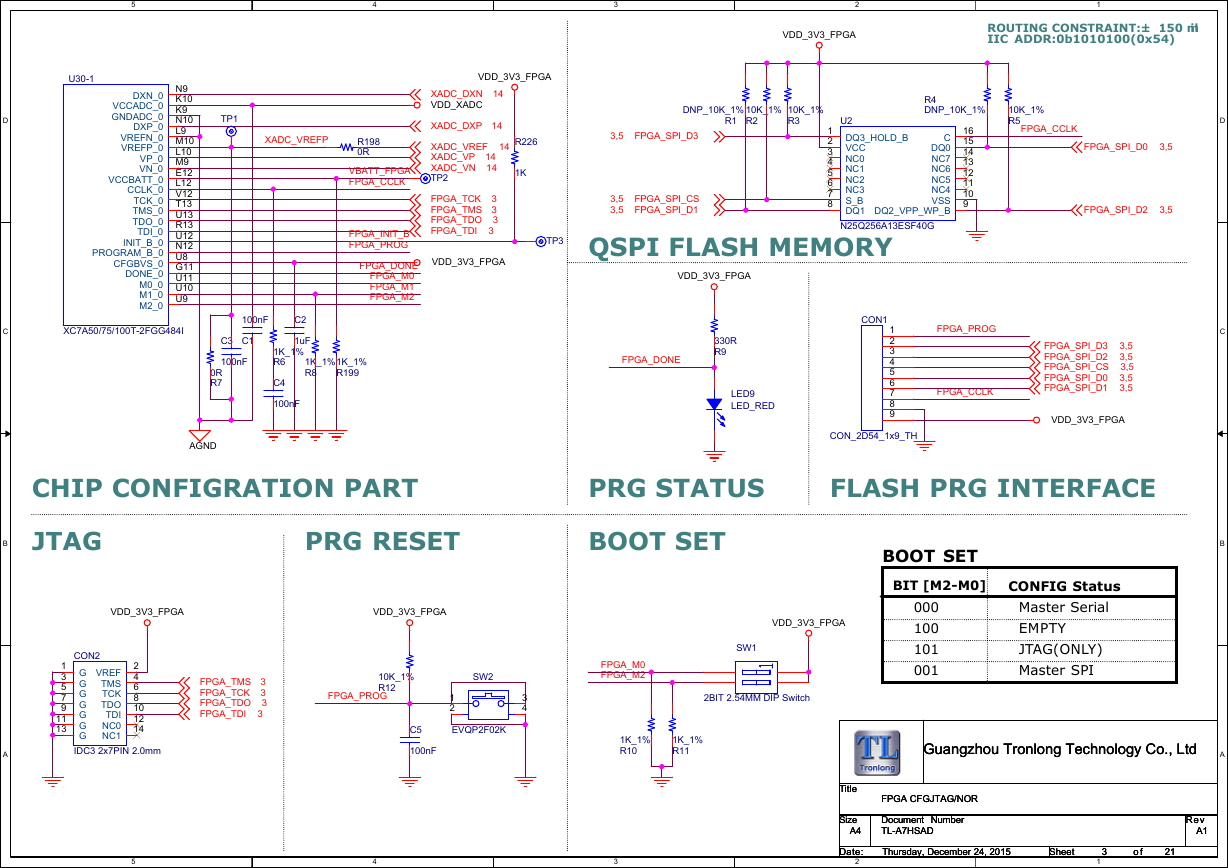

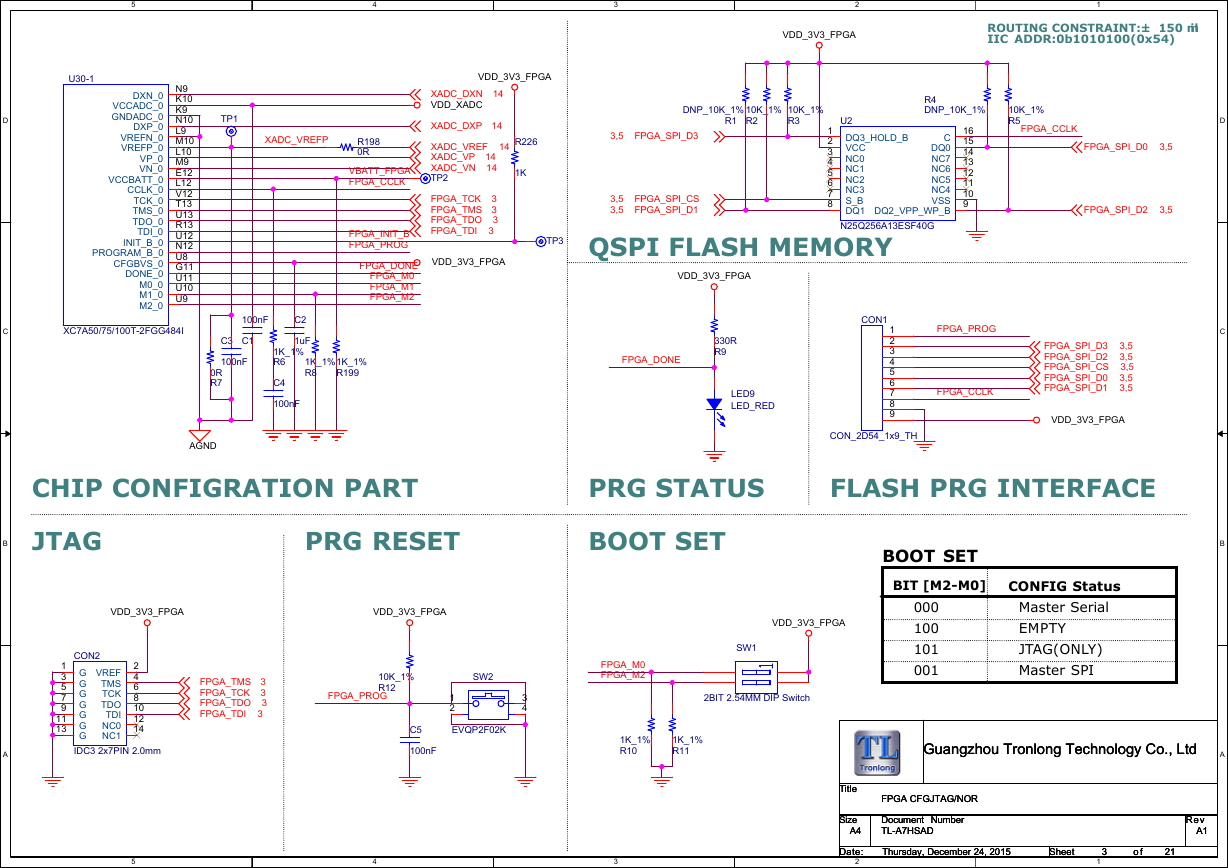

CHIP CONFIGRATION PART

PRG STATUS

FLASH PRG INTERFACE

D

C

B

BOOT SET

BIT [M2-M0]

CONFIG Status

000

100

101

001

Master Serial

EMPTY

JTAG(ONLY)

Master SPI

Guangzhou Tronlong Technology Co., Ltd

Guangzhou Tronlong Technology Co., Ltd

Guangzhou Tronlong Technology Co., Ltd

A

Title

Title

Title

Size

Size

Size

A4

A4

A4

Date:

Date:

Date:

2

FPGA CFGJTAG/NOR

FPGA CFGJTAG/NOR

FPGA CFGJTAG/NOR

Document Number

Document Number

Document Number

TL-A7HSAD

TL-A7HSAD

TL-A7HSAD

R e v

R e v

R e v

A1

A1

A1

Thursday, December 24, 2015

Thursday, December 24, 2015

Thursday, December 24, 2015

Sheet

Sheet

Sheet

3

3

3

1

o f

o f

o f

21

21

21

B

JTAG

PRG RESET

BOOT SET

VDD_3V3_FPGA

VDD_3V3_FPGA

1

3

5

7

9

11

13

CON2

G

G

G

G

G

G

G

VREF

TMS

TCK

TDO

TDI

NC0

NC1

2

4

6

8

10

12

14

A

IDC3 2x7PIN 2.0mm

FPGA_TMS 3

FPGA_TCK 3

FPGA_TDO 3

FPGA_TDI

3

10K_1%

R12

FPGA_PROG

SW2

1

2

3

4

VDD_3V3_FPGA

SW1

FPGA_M0

FPGA_M2

2BIT 2.54MM DIP Switch

C5

EVQP2F02K

100nF

1K_1%

R10

1K_1%

R11

5

4

3

�

D

C

B

A

5

4

3

2

1

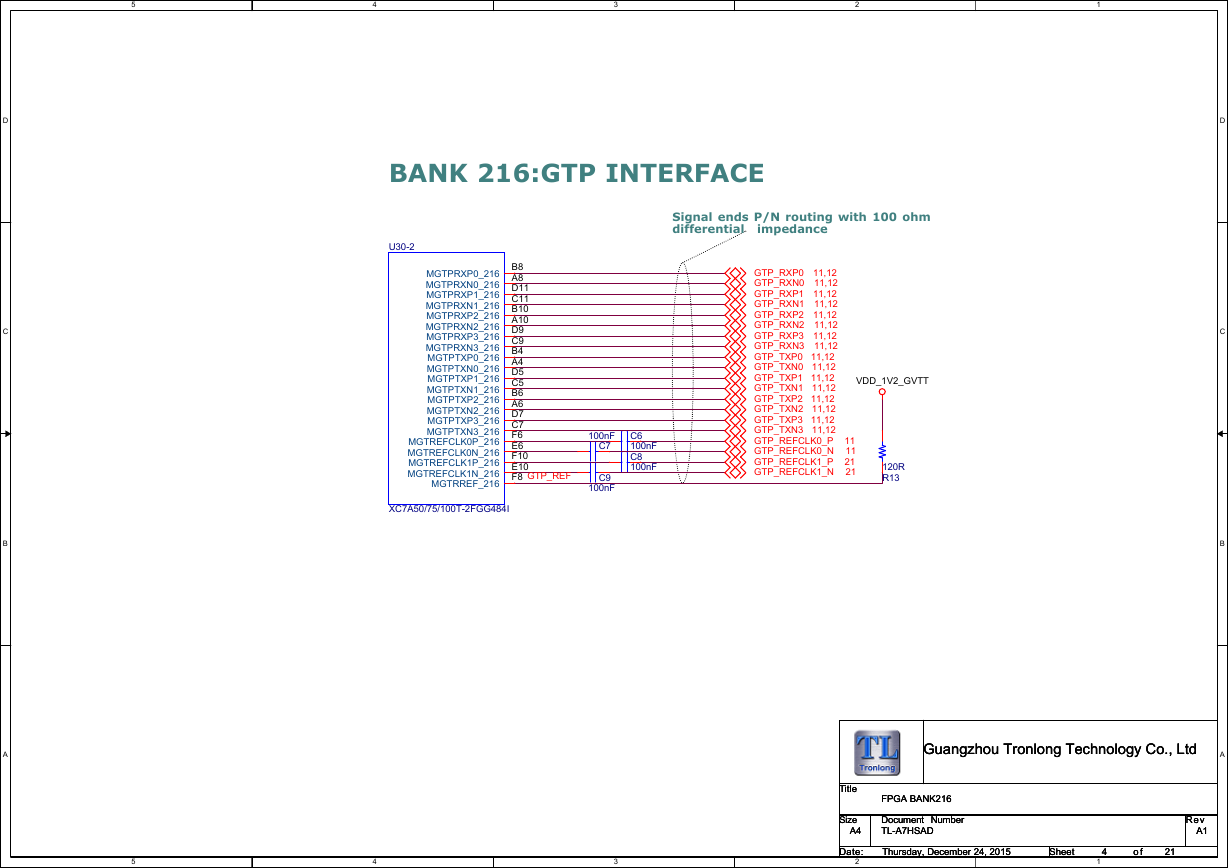

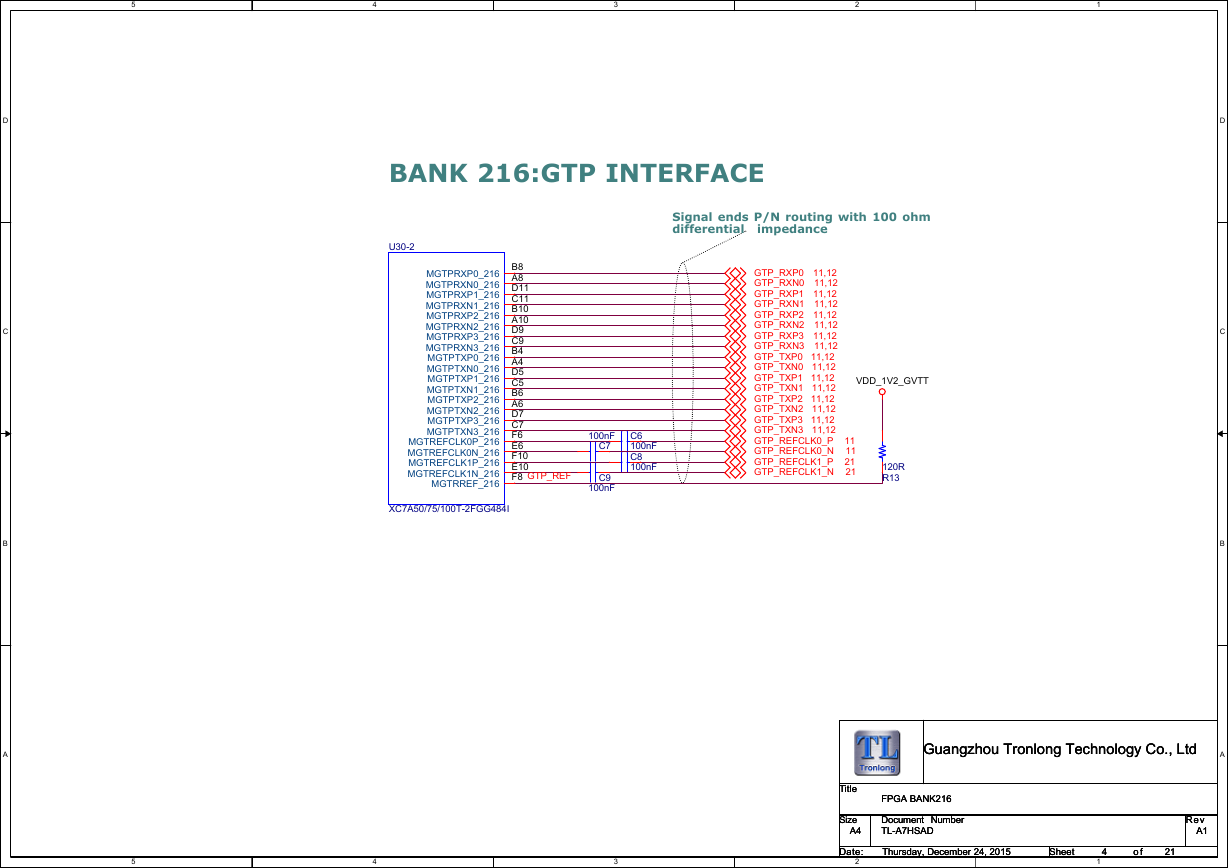

BANK 216:GTP INTERFACE

Signal ends P/N routing with 100 ohm

differential

impedance

U30-2

MGTPRXP0_216

MGTPRXN0_216

MGTPRXP1_216

MGTPRXN1_216

MGTPRXP2_216

MGTPRXN2_216

MGTPRXP3_216

MGTPRXN3_216

MGTPTXP0_216

MGTPTXN0_216

MGTPTXP1_216

MGTPTXN1_216

MGTPTXP2_216

MGTPTXN2_216

MGTPTXP3_216

MGTPTXN3_216

MGTREFCLK0P_216

MGTREFCLK0N_216

MGTREFCLK1P_216

MGTREFCLK1N_216

MGTRREF_216

XC7A50/75/100T-2FGG484I

B8

A8

D11

C11

B10

A10

D9

C9

B4

A4

D5

C5

B6

A6

D7

C7

F6

E6

F10

E10

F8

GTP_REF

C6

100nF

C8

100nF

100nF

C7

C9

100nF

GTP_RXP0 11,12

GTP_RXN0 11,12

GTP_RXP1 11,12

GTP_RXN1 11,12

GTP_RXP2 11,12

GTP_RXN2 11,12

GTP_RXP3 11,12

GTP_RXN3 11,12

GTP_TXP0 11,12

GTP_TXN0 11,12

GTP_TXP1 11,12

GTP_TXN1 11,12

GTP_TXP2 11,12

GTP_TXN2 11,12

GTP_TXP3 11,12

GTP_TXN3 11,12

GTP_REFCLK0_P 11

GTP_REFCLK0_N 11

GTP_REFCLK1_P 21

GTP_REFCLK1_N 21

VDD_1V2_GVTT

120R

R13

D

C

B

5

4

3

Guangzhou Tronlong Technology Co., Ltd

Guangzhou Tronlong Technology Co., Ltd

Guangzhou Tronlong Technology Co., Ltd

A

Title

Title

Title

Size

Size

Size

A4

A4

A4

Date:

Date:

Date:

2

FPGA BANK216

FPGA BANK216

FPGA BANK216

Document Number

Document Number

Document Number

TL-A7HSAD

TL-A7HSAD

TL-A7HSAD

R e v

R e v

R e v

A1

A1

A1

Thursday, December 24, 2015

Thursday, December 24, 2015

Thursday, December 24, 2015

Sheet

Sheet

Sheet

4

4

4

1

o f

o f

o f

21

21

21

�

5

4

3

2

1

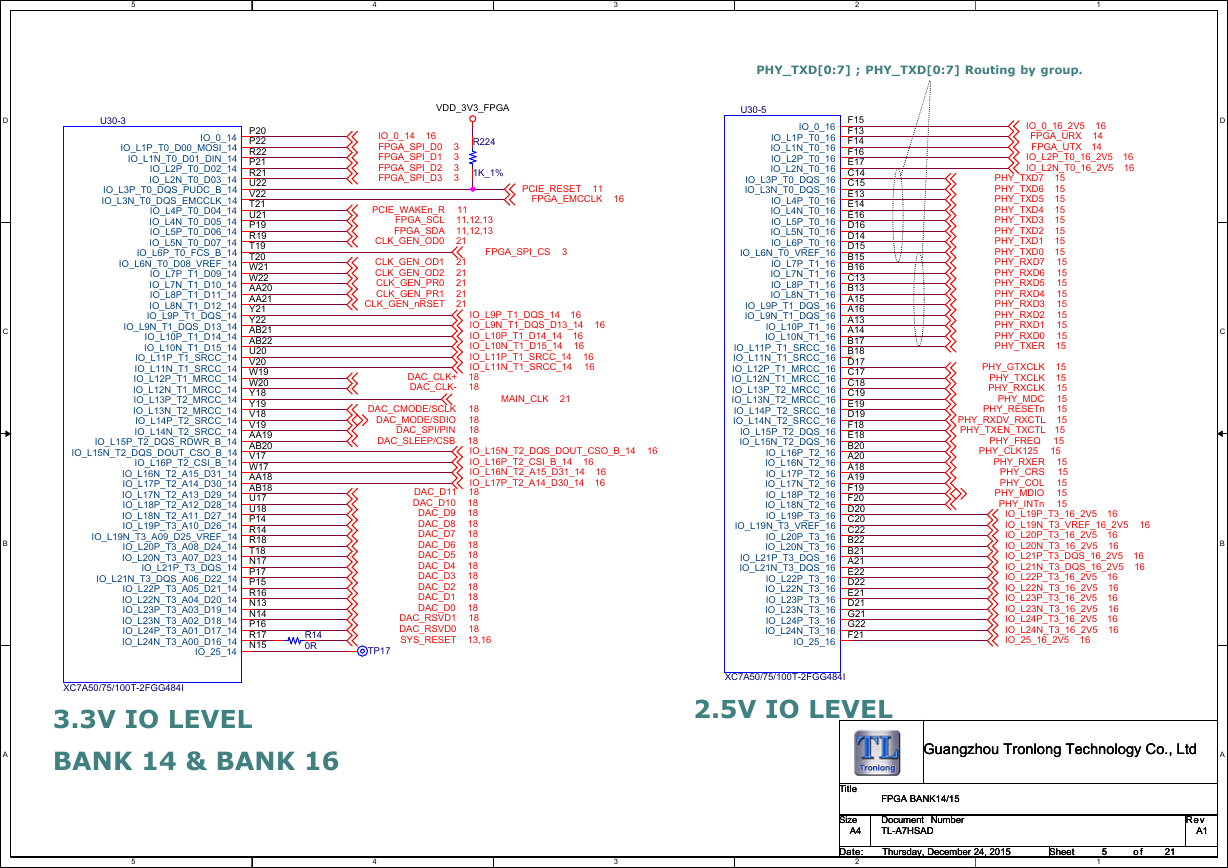

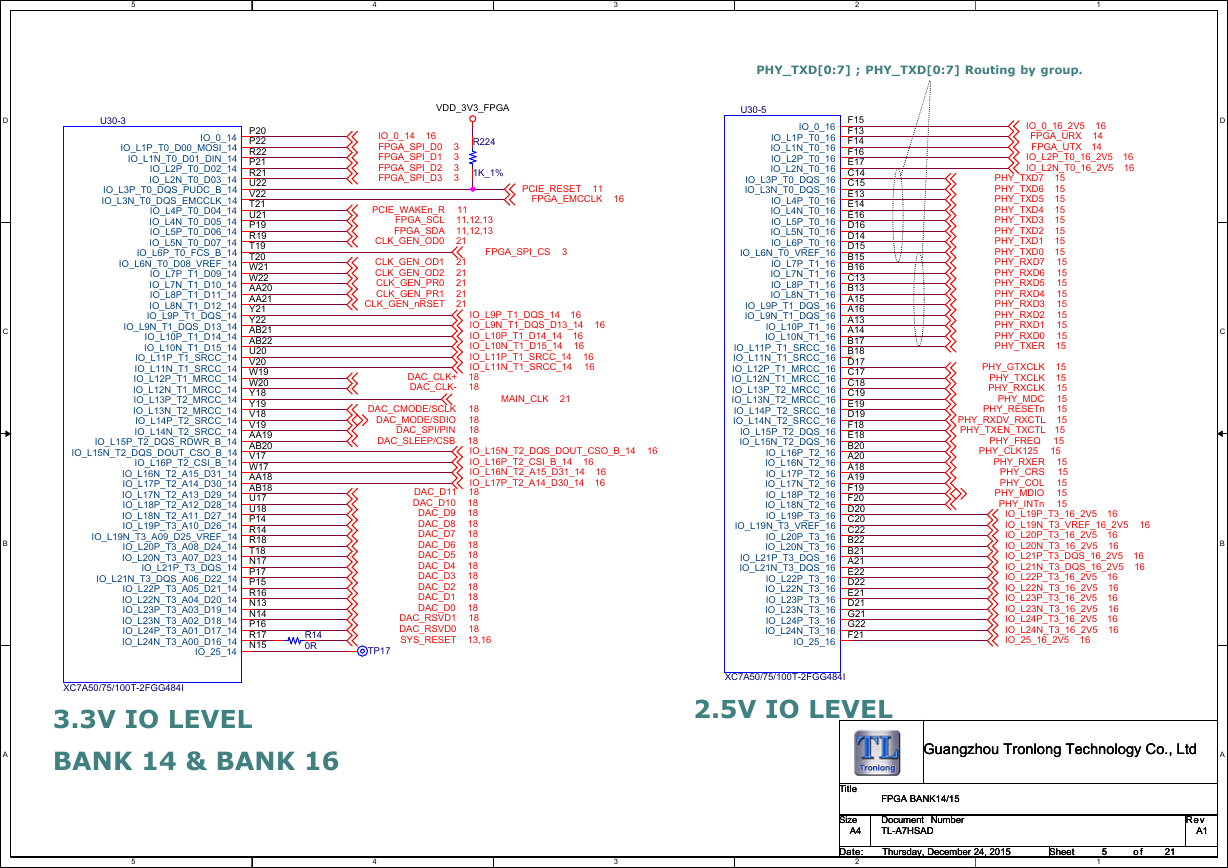

PHY_TXD[0:7] ; PHY_TXD[0:7] Routing by group.

D

U30-3

IO_0_14

IO_L1P_T0_D00_MOSI_14

IO_L1N_T0_D01_DIN_14

IO_L2P_T0_D02_14

IO_L2N_T0_D03_14

IO_L3P_T0_DQS_PUDC_B_14

IO_L3N_T0_DQS_EMCCLK_14

IO_L4P_T0_D04_14

IO_L4N_T0_D05_14

IO_L5P_T0_D06_14

IO_L5N_T0_D07_14

IO_L6P_T0_FCS_B_14

IO_L6N_T0_D08_VREF_14

IO_L7P_T1_D09_14

IO_L7N_T1_D10_14

IO_L8P_T1_D11_14

IO_L8N_T1_D12_14

IO_L9P_T1_DQS_14

IO_L9N_T1_DQS_D13_14

IO_L10P_T1_D14_14

IO_L10N_T1_D15_14

IO_L11P_T1_SRCC_14

IO_L11N_T1_SRCC_14

IO_L12P_T1_MRCC_14

IO_L12N_T1_MRCC_14

IO_L13P_T2_MRCC_14

IO_L13N_T2_MRCC_14

IO_L14P_T2_SRCC_14

IO_L14N_T2_SRCC_14

IO_L15P_T2_DQS_RDWR_B_14

IO_L15N_T2_DQS_DOUT_CSO_B_14

IO_L16P_T2_CSI_B_14

IO_L16N_T2_A15_D31_14

IO_L17P_T2_A14_D30_14

IO_L17N_T2_A13_D29_14

IO_L18P_T2_A12_D28_14

IO_L18N_T2_A11_D27_14

IO_L19P_T3_A10_D26_14

IO_L19N_T3_A09_D25_VREF_14

IO_L20P_T3_A08_D24_14

IO_L20N_T3_A07_D23_14

IO_L21P_T3_DQS_14

IO_L21N_T3_DQS_A06_D22_14

IO_L22P_T3_A05_D21_14

IO_L22N_T3_A04_D20_14

IO_L23P_T3_A03_D19_14

IO_L23N_T3_A02_D18_14

IO_L24P_T3_A01_D17_14

IO_L24N_T3_A00_D16_14

IO_25_14

P20

P22

R22

P21

R21

U22

V22

T21

U21

P19

R19

T19

T20

W21

W22

AA20

AA21

Y21

Y22

AB21

AB22

U20

V20

W19

W20

Y18

Y19

V18

V19

AA19

AB20

V17

W17

AA18

AB18

U17

U18

P14

R14

R18

T18

N17

P17

P15

R16

N13

N14

P16

R17

N15

C

B

A

VDD_3V3_FPGA

16

IO_0_14

FPGA_SPI_D0

FPGA_SPI_D1

FPGA_SPI_D2

FPGA_SPI_D3

3

3

3

3

R224

1K_1%

PCIE_WAKEn_R 11

FPGA_SCL

11,12,13

FPGA_SDA 11,12,13

CLK_GEN_OD0

21

PCIE_RESET 11

FPGA_EMCCLK 16

FPGA_SPI_CS 3

CLK_GEN_OD1

CLK_GEN_OD2

CLK_GEN_PR0

CLK_GEN_PR1

21

21

21

21

CLK_GEN_nRSET 21

16

IO_L9P_T1_DQS_14 16

IO_L9N_T1_DQS_D13_14

IO_L10P_T1_D14_14 16

IO_L10N_T1_D15_14

16

IO_L11P_T1_SRCC_14

IO_L11N_T1_SRCC_14

18

18

16

16

DAC_CLK+

DAC_CLK-

MAIN_CLK 21

DAC_CMODE/SCLK 18

DAC_MODE/SDIO 18

DAC_SPI/PIN 18

DAC_SLEEP/CSB 18

16

IO_L15N_T2_DQS_DOUT_CSO_B_14

IO_L16P_T2_CSI_B_14

16

IO_L16N_T2_A15_D31_14

IO_L17P_T2_A14_D30_14 16

18

18

18

18

18

18

18

18

18

18

18

18

18

18

DAC_D11

DAC_D10

DAC_D9

DAC_D8

DAC_D7

DAC_D6

DAC_D5

DAC_D4

DAC_D3

DAC_D2

DAC_D1

DAC_D0

DAC_RSVD1

DAC_RSVD0

SYS_RESET 13,16

R14

0R

TP17

U30-5

IO_0_16

IO_L1P_T0_16

IO_L1N_T0_16

IO_L2P_T0_16

IO_L2N_T0_16

IO_L3P_T0_DQS_16

IO_L3N_T0_DQS_16

IO_L4P_T0_16

IO_L4N_T0_16

IO_L5P_T0_16

IO_L5N_T0_16

IO_L6P_T0_16

IO_L6N_T0_VREF_16

IO_L7P_T1_16

IO_L7N_T1_16

IO_L8P_T1_16

IO_L8N_T1_16

IO_L9P_T1_DQS_16

IO_L9N_T1_DQS_16

IO_L10P_T1_16

IO_L10N_T1_16

IO_L11P_T1_SRCC_16

IO_L11N_T1_SRCC_16

IO_L12P_T1_MRCC_16

IO_L12N_T1_MRCC_16

IO_L13P_T2_MRCC_16

IO_L13N_T2_MRCC_16

IO_L14P_T2_SRCC_16

IO_L14N_T2_SRCC_16

IO_L15P_T2_DQS_16

IO_L15N_T2_DQS_16

IO_L16P_T2_16

IO_L16N_T2_16

IO_L17P_T2_16

IO_L17N_T2_16

IO_L18P_T2_16

IO_L18N_T2_16

IO_L19P_T3_16

IO_L19N_T3_VREF_16

IO_L20P_T3_16

IO_L20N_T3_16

IO_L21P_T3_DQS_16

IO_L21N_T3_DQS_16

IO_L22P_T3_16

IO_L22N_T3_16

IO_L23P_T3_16

IO_L23N_T3_16

IO_L24P_T3_16

IO_L24N_T3_16

IO_25_16

F15

F13

F14

F16

E17

C14

C15

E13

E14

E16

D16

D14

D15

B15

B16

C13

B13

A15

A16

A13

A14

B17

B18

D17

C17

C18

C19

E19

D19

F18

E18

B20

A20

A18

A19

F19

F20

D20

C20

C22

B22

B21

A21

E22

D22

E21

D21

G21

G22

F21

XC7A50/75/100T-2FGG484I

2.5V IO LEVEL

16

D

C

B

IO_0_16_2V5 16

FPGA_URX 14

FPGA_UTX 14

IO_L2P_T0_16_2V5 16

IO_L2N_T0_16_2V5 16

PHY_TXD7

15

PHY_TXD6

15

PHY_TXD5

15

PHY_TXD4

15

PHY_TXD3

15

PHY_TXD2

15

PHY_TXD1

15

15

PHY_TXD0

PHY_RXD7

15

PHY_RXD6

15

15

PHY_RXD5

15

PHY_RXD4

15

PHY_RXD3

15

PHY_RXD2

15

PHY_RXD1

PHY_RXD0

15

PHY_TXER 15

PHY_GTXCLK 15

PHY_TXCLK 15

PHY_RXCLK 15

PHY_MDC 15

15

PHY_RESETn

15

PHY_RXDV_RXCTL

PHY_TXEN_TXCTL 15

PHY_FREQ 15

15

PHY_CLK125

PHY_CRS

PHY_COL

PHY_RXER 15

15

15

PHY_MDIO 15

15

PHY_INTn

16

IO_L19P_T3_16_2V5 16

IO_L19N_T3_VREF_16_2V5

IO_L20P_T3_16_2V5 16

IO_L20N_T3_16_2V5 16

IO_L21P_T3_DQS_16_2V5 16

IO_L21N_T3_DQS_16_2V5

16

IO_L22P_T3_16_2V5 16

IO_L22N_T3_16_2V5 16

IO_L23P_T3_16_2V5 16

IO_L23N_T3_16_2V5 16

IO_L24P_T3_16_2V5 16

IO_L24N_T3_16_2V5 16

IO_25_16_2V5 16

Guangzhou Tronlong Technology Co., Ltd

Guangzhou Tronlong Technology Co., Ltd

Guangzhou Tronlong Technology Co., Ltd

A

Title

Title

Title

Size

Size

Size

A4

A4

A4

Date:

Date:

Date:

2

FPGA BANK14/15

FPGA BANK14/15

FPGA BANK14/15

Document Number

Document Number

Document Number

TL-A7HSAD

TL-A7HSAD

TL-A7HSAD

R e v

R e v

R e v

A1

A1

A1

Thursday, December 24, 2015

Thursday, December 24, 2015

Thursday, December 24, 2015

Sheet

Sheet

Sheet

5

5

5

1

o f

o f

o f

21

21

21

XC7A50/75/100T-2FGG484I

3.3V IO LEVEL

BANK 14 & BANK 16

5

4

3

�

5

4

3

2

1

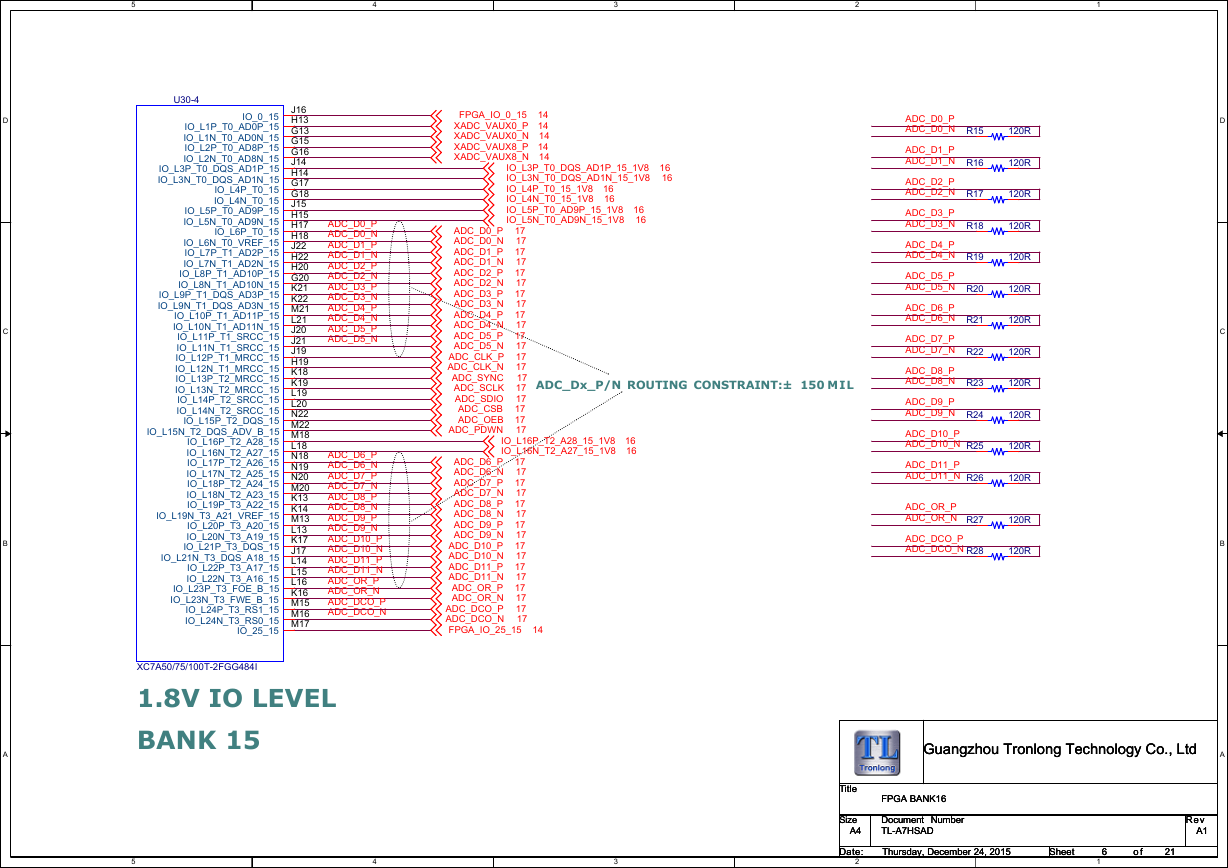

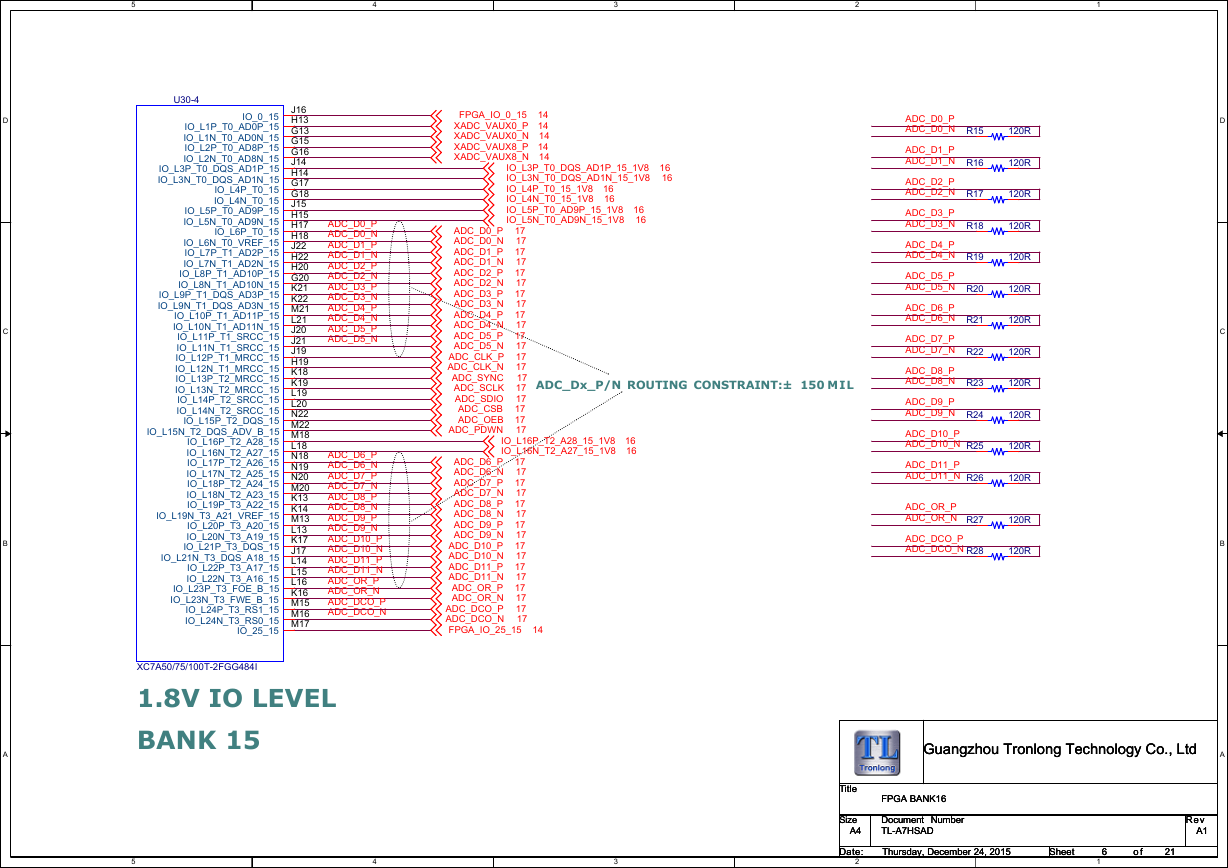

D

C

B

A

U30-4

IO_0_15

IO_L1P_T0_AD0P_15

IO_L1N_T0_AD0N_15

IO_L2P_T0_AD8P_15

IO_L2N_T0_AD8N_15

IO_L3P_T0_DQS_AD1P_15

IO_L3N_T0_DQS_AD1N_15

IO_L4P_T0_15

IO_L4N_T0_15

IO_L5P_T0_AD9P_15

IO_L5N_T0_AD9N_15

IO_L6P_T0_15

IO_L6N_T0_VREF_15

IO_L7P_T1_AD2P_15

IO_L7N_T1_AD2N_15

IO_L8P_T1_AD10P_15

IO_L8N_T1_AD10N_15

IO_L9P_T1_DQS_AD3P_15

IO_L9N_T1_DQS_AD3N_15

IO_L10P_T1_AD11P_15

IO_L10N_T1_AD11N_15

IO_L11P_T1_SRCC_15

IO_L11N_T1_SRCC_15

IO_L12P_T1_MRCC_15

IO_L12N_T1_MRCC_15

IO_L13P_T2_MRCC_15

IO_L13N_T2_MRCC_15

IO_L14P_T2_SRCC_15

IO_L14N_T2_SRCC_15

IO_L15P_T2_DQS_15

IO_L15N_T2_DQS_ADV_B_15

IO_L16P_T2_A28_15

IO_L16N_T2_A27_15

IO_L17P_T2_A26_15

IO_L17N_T2_A25_15

IO_L18P_T2_A24_15

IO_L18N_T2_A23_15

IO_L19P_T3_A22_15

IO_L19N_T3_A21_VREF_15

IO_L20P_T3_A20_15

IO_L20N_T3_A19_15

IO_L21P_T3_DQS_15

IO_L21N_T3_DQS_A18_15

IO_L22P_T3_A17_15

IO_L22N_T3_A16_15

IO_L23P_T3_FOE_B_15

IO_L23N_T3_FWE_B_15

IO_L24P_T3_RS1_15

IO_L24N_T3_RS0_15

IO_25_15

J16

H13

G13

G15

G16

J14

H14

G17

G18

J15

H15

H17

H18

J22

H22

H20

G20

K21

K22

M21

L21

J20

J21

J19

H19

K18

K19

L19

L20

N22

M22

M18

L18

N18

N19

N20

M20

K13

K14

M13

L13

K17

J17

L14

L15

L16

K16

M15

M16

M17

ADC_D0_P

ADC_D0_N

ADC_D1_P

ADC_D1_N

ADC_D2_P

ADC_D2_N

ADC_D3_P

ADC_D3_N

ADC_D4_P

ADC_D4_N

ADC_D5_P

ADC_D5_N

ADC_D6_P

ADC_D6_N

ADC_D7_P

ADC_D7_N

ADC_D8_P

ADC_D8_N

ADC_D9_P

ADC_D9_N

ADC_D10_P

ADC_D10_N

ADC_D11_P

ADC_D11_N

ADC_OR_P

ADC_OR_N

ADC_DCO_P

ADC_DCO_N

XC7A50/75/100T-2FGG484I

1.8V IO LEVEL

BANK 15

FPGA_IO_0_15

14

XADC_VAUX0_P 14

XADC_VAUX0_N 14

XADC_VAUX8_P 14

XADC_VAUX8_N 14

IO_L3P_T0_DQS_AD1P_15_1V8 16

IO_L3N_T0_DQS_AD1N_15_1V8

16

IO_L4P_T0_15_1V8 16

IO_L4N_T0_15_1V8 16

IO_L5P_T0_AD9P_15_1V8 16

IO_L5N_T0_AD9N_15_1V8

16

ADC_D0_P 17

ADC_D0_N 17

ADC_D1_P 17

ADC_D1_N 17

ADC_D2_P 17

ADC_D2_N 17

ADC_D3_P 17

ADC_D3_N 17

ADC_D4_P 17

ADC_D4_N 17

ADC_D5_P 17

ADC_D5_N 17

ADC_CLK_P 17

ADC_CLK_N 17

ADC_SYNC 17

ADC_SCLK 17

ADC_SDIO 17

ADC_CSB 17

ADC_OEB 17

ADC_PDWN 17

ADC_Dx_P/N ROUTING CONSTRAINT:± 150 M IL

IO_L16P_T2_A28_15_1V8 16

IO_L16N_T2_A27_15_1V8 16

ADC_D6_P 17

ADC_D6_N 17

ADC_D7_P 17

ADC_D7_N 17

ADC_D8_P 17

ADC_D8_N 17

ADC_D9_P 17

ADC_D9_N 17

ADC_D10_P 17

ADC_D10_N 17

ADC_D11_P 17

ADC_D11_N 17

ADC_OR_P 17

ADC_OR_N 17

ADC_DCO_P 17

ADC_DCO_N 17

FPGA_IO_25_15

14

ADC_D0_P

ADC_D0_N

ADC_D1_P

ADC_D1_N

ADC_D2_P

ADC_D2_N

ADC_D3_P

ADC_D3_N

ADC_D4_P

ADC_D4_N

ADC_D5_P

ADC_D5_N

ADC_D6_P

ADC_D6_N

ADC_D7_P

ADC_D7_N

ADC_D8_P

ADC_D8_N

ADC_D9_P

ADC_D9_N

ADC_D10_P

ADC_D10_N

ADC_D11_P

ADC_D11_N

R15

120R

R16

120R

R17

120R

R18

120R

R19

120R

R20

120R

R21

120R

R22

120R

R23

120R

R24

120R

R25

120R

R26

120R

ADC_OR_P

ADC_OR_N

ADC_DCO_P

ADC_DCO_N

R27

120R

R28

120R

D

C

B

5

4

3

Guangzhou Tronlong Technology Co., Ltd

Guangzhou Tronlong Technology Co., Ltd

Guangzhou Tronlong Technology Co., Ltd

A

Title

Title

Title

Size

Size

Size

A4

A4

A4

Date:

Date:

Date:

2

FPGA BANK16

FPGA BANK16

FPGA BANK16

Document Number

Document Number

Document Number

TL-A7HSAD

TL-A7HSAD

TL-A7HSAD

R e v

R e v

R e v

A1

A1

A1

Thursday, December 24, 2015

Thursday, December 24, 2015

Thursday, December 24, 2015

Sheet

Sheet

Sheet

6

6

6

1

o f

o f

o f

21

21

21

�

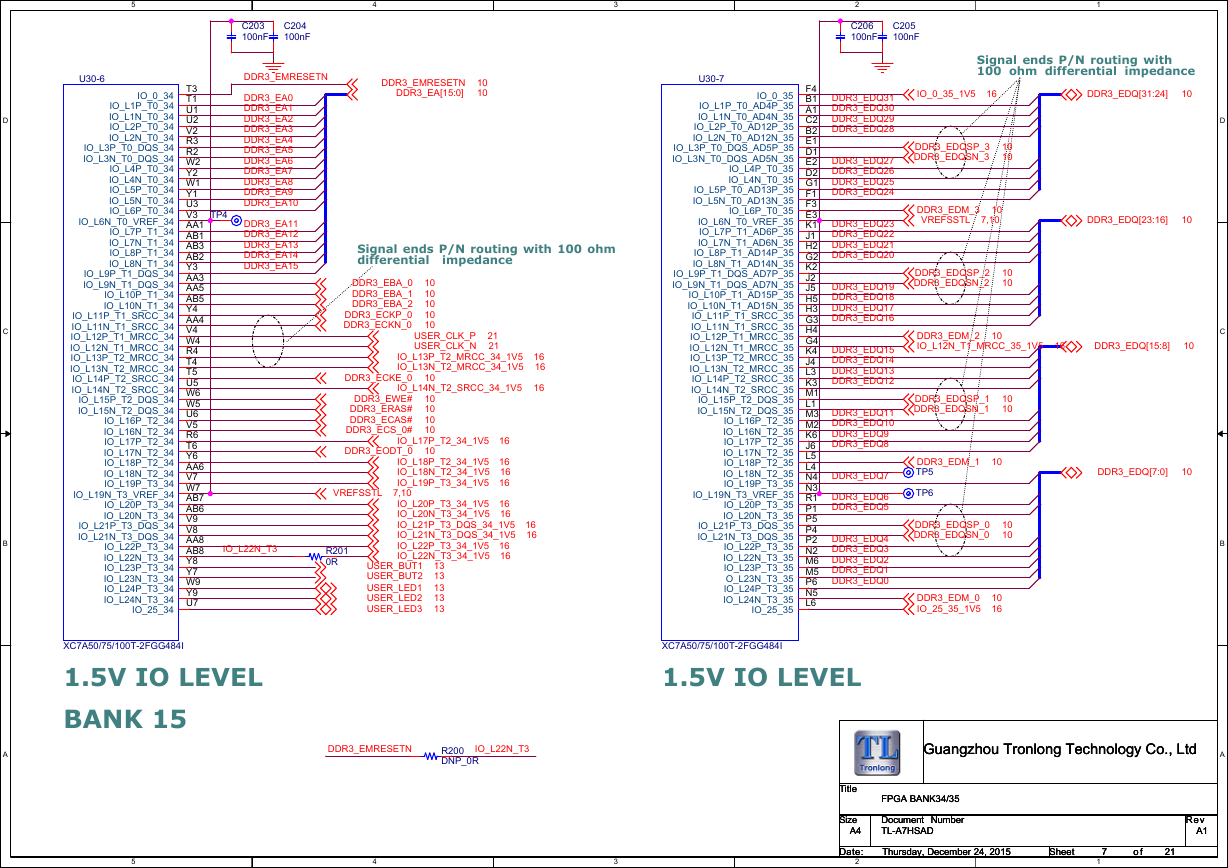

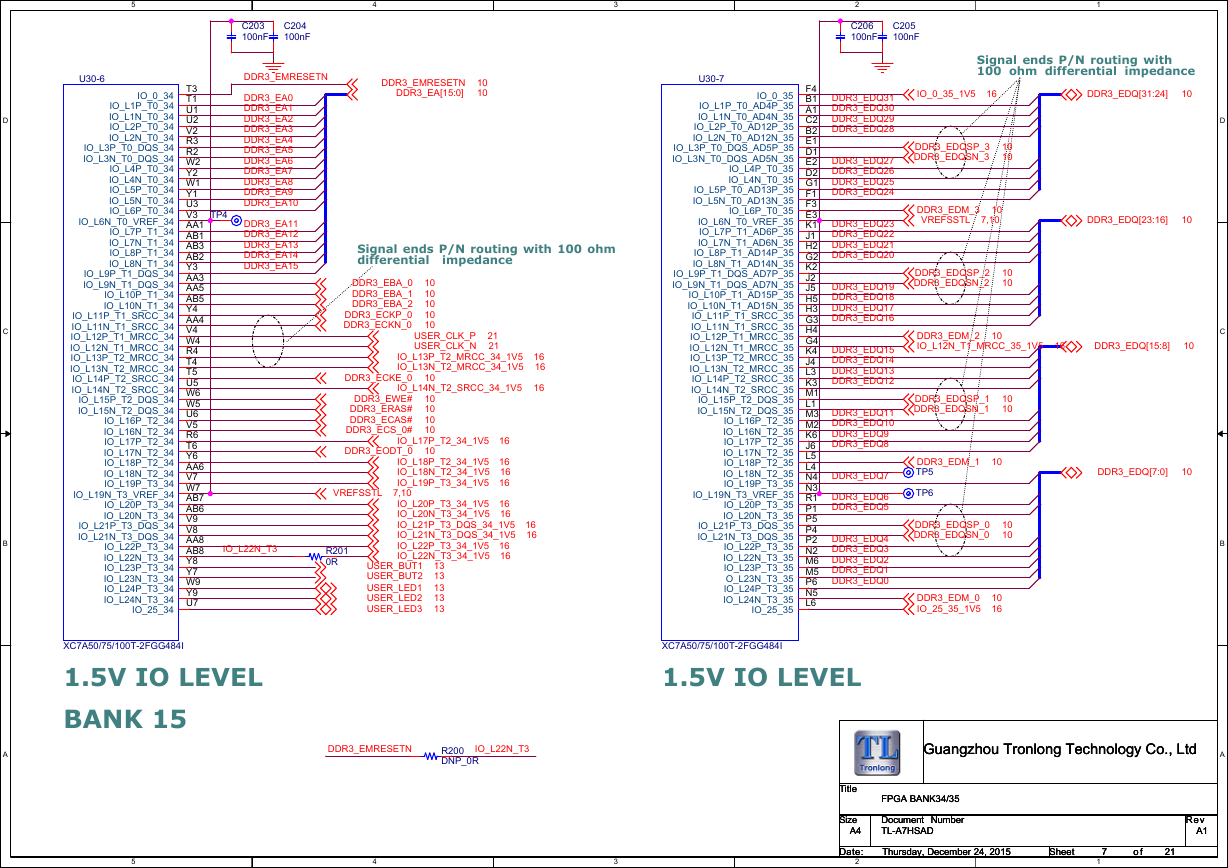

D

C

B

A

5

4

3

C203

100nF

C204

100nF

DDR3_EMRESETN

DDR3_EA0

DDR3_EA1

DDR3_EA2

DDR3_EA3

DDR3_EA4

DDR3_EA5

DDR3_EA6

DDR3_EA7

DDR3_EA8

DDR3_EA9

DDR3_EA10

DDR3_EA11

DDR3_EA12

DDR3_EA13

DDR3_EA14

DDR3_EA15

TP4

DDR3_EMRESETN 10

10

DDR3_EA[15:0]

Signal ends P/N routing with 100 ohm

differential

impedance

DDR3_EBA_0

DDR3_EBA_1

DDR3_EBA_2

DDR3_ECKP_0

DDR3_ECKN_0

10

10

10

10

10

USER_CLK_P 21

USER_CLK_N 21

IO_L13P_T2_MRCC_34_1V5

IO_L13N_T2_MRCC_34_1V5

16

16

DDR3_ECKE_0

10

IO_L14N_T2_SRCC_34_1V5

16

DDR3_EWE#

DDR3_ERAS#

DDR3_ECAS#

DDR3_ECS_0#

10

10

10

10

IO_L17P_T2_34_1V5 16

DDR3_EODT_0

10

VREFSSTL

IO_L18P_T2_34_1V5 16

IO_L18N_T2_34_1V5 16

IO_L19P_T3_34_1V5 16

7,10

IO_L20P_T3_34_1V5 16

IO_L20N_T3_34_1V5 16

IO_L21P_T3_DQS_34_1V5 16

IO_L21N_T3_DQS_34_1V5

16

IO_L22P_T3_34_1V5 16

IO_L22N_T3_34_1V5 16

IO_L22N_T3

R201

0R

USER_BUT1

USER_BUT2

USER_LED1

USER_LED2

USER_LED3

13

13

13

13

13

U30-6

IO_0_34

IO_L1P_T0_34

IO_L1N_T0_34

IO_L2P_T0_34

IO_L2N_T0_34

IO_L3P_T0_DQS_34

IO_L3N_T0_DQS_34

IO_L4P_T0_34

IO_L4N_T0_34

IO_L5P_T0_34

IO_L5N_T0_34

IO_L6P_T0_34

IO_L6N_T0_VREF_34

IO_L7P_T1_34

IO_L7N_T1_34

IO_L8P_T1_34

IO_L8N_T1_34

IO_L9P_T1_DQS_34

IO_L9N_T1_DQS_34

IO_L10P_T1_34

IO_L10N_T1_34

IO_L11P_T1_SRCC_34

IO_L11N_T1_SRCC_34

IO_L12P_T1_MRCC_34

IO_L12N_T1_MRCC_34

IO_L13P_T2_MRCC_34

IO_L13N_T2_MRCC_34

IO_L14P_T2_SRCC_34

IO_L14N_T2_SRCC_34

IO_L15P_T2_DQS_34

IO_L15N_T2_DQS_34

IO_L16P_T2_34

IO_L16N_T2_34

IO_L17P_T2_34

IO_L17N_T2_34

IO_L18P_T2_34

IO_L18N_T2_34

IO_L19P_T3_34

IO_L19N_T3_VREF_34

IO_L20P_T3_34

IO_L20N_T3_34

IO_L21P_T3_DQS_34

IO_L21N_T3_DQS_34

IO_L22P_T3_34

IO_L22N_T3_34

IO_L23P_T3_34

IO_L23N_T3_34

IO_L24P_T3_34

IO_L24N_T3_34

IO_25_34

T3

T1

U1

U2

V2

R3

R2

W2

Y2

W1

Y1

U3

V3

AA1

AB1

AB3

AB2

Y3

AA3

AA5

AB5

Y4

AA4

V4

W4

R4

T4

T5

U5

W6

W5

U6

V5

R6

T6

Y6

AA6

V7

W7

AB7

AB6

V9

V8

AA8

AB8

Y8

Y7

W9

Y9

U7

XC7A50/75/100T-2FGG484I

1.5V IO LEVEL

BANK 15

2

C206

100nF

C205

100nF

1

Signal ends P/N routing with

100 ohm differential impedance

IO_0_35_1V5 16

DDR3_EDQ[31:24]

10

DDR3_EDQSP_3

DDR3_EDQSN_3

10

10

DDR3_EDM_3

VREFSSTL

10

7,10

DDR3_EDQ[23:16]

10

DDR3_EDQSP_2

DDR3_EDQSN_2

10

10

DDR3_EDM_2

IO_L12N_T1_MRCC_35_1V5

10

16

DDR3_EDQ[15:8]

10

DDR3_EDQ[7:0]

10

DDR3_EDQSP_1

DDR3_EDQSN_1

10

10

DDR3_EDM_1

TP5

10

TP6

DDR3_EDQSP_0

DDR3_EDQSN_0

10

10

DDR3_EDM_0

10

IO_25_35_1V5 16

D

C

B

U30-7

IO_0_35

IO_L1P_T0_AD4P_35

IO_L1N_T0_AD4N_35

IO_L2P_T0_AD12P_35

IO_L2N_T0_AD12N_35

IO_L3P_T0_DQS_AD5P_35

IO_L3N_T0_DQS_AD5N_35

IO_L4P_T0_35

IO_L4N_T0_35

IO_L5P_T0_AD13P_35

IO_L5N_T0_AD13N_35

IO_L6P_T0_35

IO_L6N_T0_VREF_35

IO_L7P_T1_AD6P_35

IO_L7N_T1_AD6N_35

IO_L8P_T1_AD14P_35

IO_L8N_T1_AD14N_35

IO_L9P_T1_DQS_AD7P_35

IO_L9N_T1_DQS_AD7N_35

IO_L10P_T1_AD15P_35

IO_L10N_T1_AD15N_35

IO_L11P_T1_SRCC_35

IO_L11N_T1_SRCC_35

IO_L12P_T1_MRCC_35

IO_L12N_T1_MRCC_35

IO_L13P_T2_MRCC_35

IO_L13N_T2_MRCC_35

IO_L14P_T2_SRCC_35

IO_L14N_T2_SRCC_35

IO_L15P_T2_DQS_35

IO_L15N_T2_DQS_35

IO_L16P_T2_35

IO_L16N_T2_35

IO_L17P_T2_35

IO_L17N_T2_35

IO_L18P_T2_35

IO_L18N_T2_35

IO_L19P_T3_35

IO_L19N_T3_VREF_35

IO_L20P_T3_35

IO_L20N_T3_35

IO_L21P_T3_DQS_35

IO_L21N_T3_DQS_35

IO_L22P_T3_35

IO_L22N_T3_35

IO_L23P_T3_35

O_L23N_T3_35

IO_L24P_T3_35

IO_L24N_T3_35

IO_25_35

F4

B1

A1

C2

B2

E1

D1

E2

D2

G1

F1

F3

E3

K1

J1

H2

G2

K2

J2

J5

H5

H3

G3

H4

G4

K4

J4

L3

K3

M1

L1

M3

M2

K6

J6

L5

L4

N4

N3

R1

P1

P5

P4

P2

N2

M6

M5

P6

N5

L6

DDR3_EDQ31

DDR3_EDQ30

DDR3_EDQ29

DDR3_EDQ28

DDR3_EDQ27

DDR3_EDQ26

DDR3_EDQ25

DDR3_EDQ24

DDR3_EDQ23

DDR3_EDQ22

DDR3_EDQ21

DDR3_EDQ20

DDR3_EDQ19

DDR3_EDQ18

DDR3_EDQ17

DDR3_EDQ16

DDR3_EDQ15

DDR3_EDQ14

DDR3_EDQ13

DDR3_EDQ12

DDR3_EDQ11

DDR3_EDQ10

DDR3_EDQ9

DDR3_EDQ8

DDR3_EDQ7

DDR3_EDQ6

DDR3_EDQ5

DDR3_EDQ4

DDR3_EDQ3

DDR3_EDQ2

DDR3_EDQ1

DDR3_EDQ0

XC7A50/75/100T-2FGG484I

1.5V IO LEVEL

DDR3_EMRESETN

IO_L22N_T3

R200

DNP_0R

Guangzhou Tronlong Technology Co., Ltd

Guangzhou Tronlong Technology Co., Ltd

Guangzhou Tronlong Technology Co., Ltd

A

5

4

3

Title

Title

Title

Size

Size

Size

A4

A4

A4

Date:

Date:

Date:

2

FPGA BANK34/35

FPGA BANK34/35

FPGA BANK34/35

Document Number

Document Number

Document Number

TL-A7HSAD

TL-A7HSAD

TL-A7HSAD

R e v

R e v

R e v

A1

A1

A1

Thursday, December 24, 2015

Thursday, December 24, 2015

Thursday, December 24, 2015

Sheet

Sheet

Sheet

7

7

7

1

o f

o f

o f

21

21

21

�

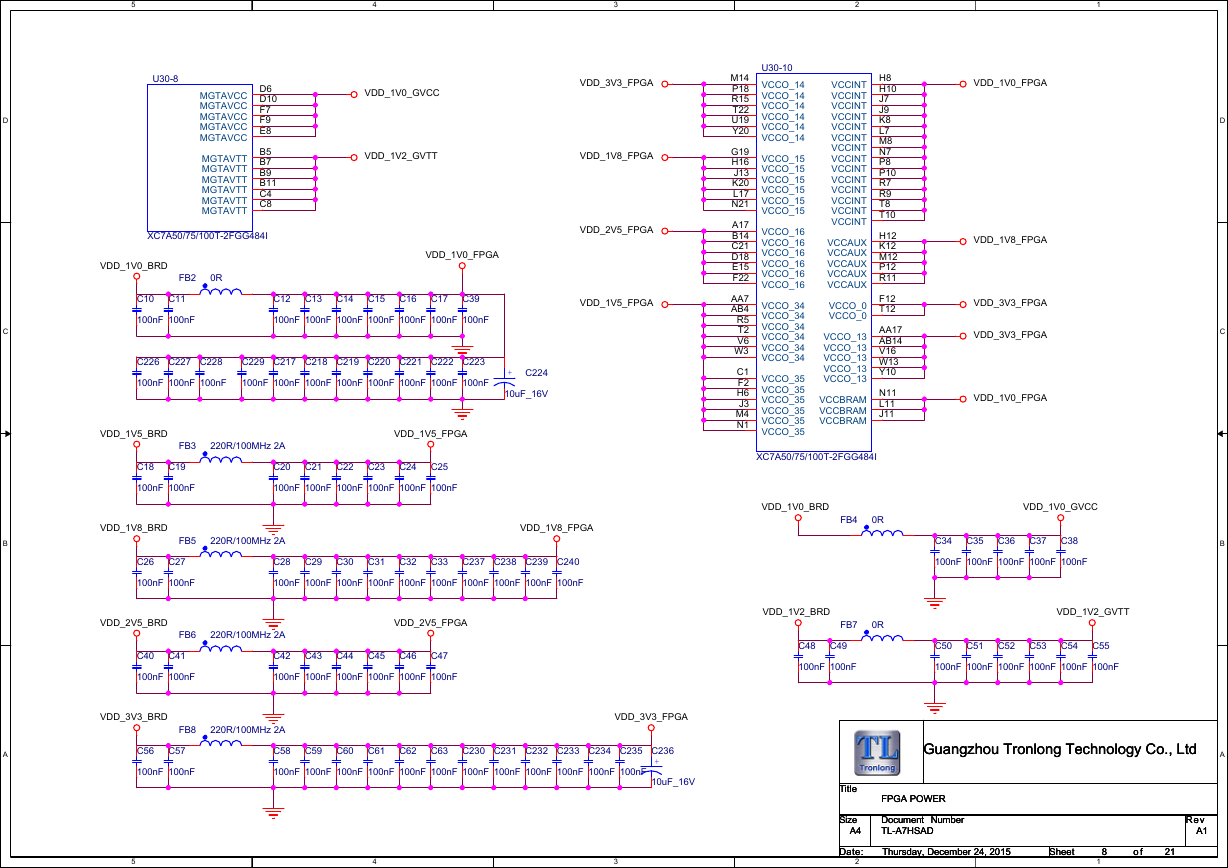

D

C

B

A

5

4

3

2

1

U30-8

MGTAVCC

MGTAVCC

MGTAVCC

MGTAVCC

MGTAVCC

MGTAVTT

MGTAVTT

MGTAVTT

MGTAVTT

MGTAVTT

MGTAVTT

D6

D10

F7

F9

E8

B5

B7

B9

B11

C4

C8

XC7A50/75/100T-2FGG484I

VDD_1V0_BRD

FB2

0R

VDD_1V0_GVCC

VDD_3V3_FPGA

VDD_1V2_GVTT

VDD_1V8_FPGA

VDD_1V0_FPGA

VDD_2V5_FPGA

C10

C11

C12

C13

C14

C15

C16

C17

C39

VDD_1V5_FPGA

100nF

100nF

100nF

100nF

100nF

100nF

100nF

100nF

100nF

C226

C227

C228

C229

C217

C218

C219

C220

C221

C222

C223

100nF

100nF

100nF

100nF

100nF

100nF

100nF

100nF

100nF

100nF

100nF

+ C224

10uF_16V

VDD_1V5_BRD

VDD_1V5_FPGA

FB3

220R/100MHz 2A

C18

C19

C20

C21

C22

C23

C24

C25

100nF

100nF

100nF

100nF

100nF

100nF

100nF

100nF

VDD_1V8_BRD

FB5

220R/100MHz 2A

VDD_1V8_FPGA

C26

C27

C28

C29

C30

C31

C32

C33

C237

C238

C239

C240

100nF

100nF

100nF

100nF

100nF

100nF

100nF

100nF

100nF

100nF

100nF

100nF

VDD_2V5_BRD

VDD_2V5_FPGA

FB6

220R/100MHz 2A

C40

C41

C42

C43

C44

C45

C46

C47

100nF

100nF

100nF

100nF

100nF

100nF

100nF

100nF

M14

P18

R15

T22

U19

Y20

G19

H16

J13

K20

L17

N21

A17

B14

C21

D18

E15

F22

AA7

AB4

R5

T2

V6

W3

C1

F2

H6

J3

M4

N1

U30-10

VCCO_14

VCCO_14

VCCO_14

VCCO_14

VCCO_14

VCCO_14

VCCO_15

VCCO_15

VCCO_15

VCCO_15

VCCO_15

VCCO_15

VCCO_16

VCCO_16

VCCO_16

VCCO_16

VCCO_16

VCCO_16

VCCO_34

VCCO_34

VCCO_34

VCCO_34

VCCO_34

VCCO_34

VCCO_35

VCCO_35

VCCO_35

VCCO_35

VCCO_35

VCCO_35

VCCINT

VCCINT

VCCINT

VCCINT

VCCINT

VCCINT

VCCINT

VCCINT

VCCINT

VCCINT

VCCINT

VCCINT

VCCINT

VCCINT

VCCAUX

VCCAUX

VCCAUX

VCCAUX

VCCAUX

VCCO_0

VCCO_0

VCCO_13

VCCO_13

VCCO_13

VCCO_13

VCCO_13

VCCBRAM

VCCBRAM

VCCBRAM

H8

H10

J7

J9

K8

L7

M8

N7

P8

P10

R7

R9

T8

T10

H12

K12

M12

P12

R11

F12

T12

AA17

AB14

V16

W13

Y10

N11

L11

J11

XC7A50/75/100T-2FGG484I

VDD_1V0_FPGA

VDD_1V8_FPGA

VDD_3V3_FPGA

VDD_3V3_FPGA

VDD_1V0_FPGA

VDD_1V0_BRD

FB4

0R

VDD_1V0_GVCC

C34

C35

C36

C37

C38

100nF

100nF

100nF

100nF

100nF

VDD_1V2_BRD

FB7

0R

VDD_1V2_GVTT

C48

C49

C50

C51

C52

C53

C54

C55

100nF

100nF

100nF

100nF

100nF

100nF

100nF

100nF

D

C

B

VDD_3V3_BRD

FB8

220R/100MHz 2A

VDD_3V3_FPGA

C56

C57

C58

C59

C60

C61

C62

C63

C230

C231

C232

C233

C234

C235

100nF

100nF

100nF

100nF

100nF

100nF

100nF

100nF

100nF

100nF

100nF

100nF

100nF

100nF

C236

+

10uF_16V

5

4

3

Guangzhou Tronlong Technology Co., Ltd

Guangzhou Tronlong Technology Co., Ltd

Guangzhou Tronlong Technology Co., Ltd

A

Title

Title

Title

Size

Size

Size

A4

A4

A4

Date:

Date:

Date:

2

FPGA POWER

FPGA POWER

FPGA POWER

Document Number

Document Number

Document Number

TL-A7HSAD

TL-A7HSAD

TL-A7HSAD

R e v

R e v

R e v

A1

A1

A1

Thursday, December 24, 2015

Thursday, December 24, 2015

Thursday, December 24, 2015

Sheet

Sheet

Sheet

8

8

8

1

o f

o f

o f

21

21

21

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc