西安电子科技大学

SV 实验一实验报告

课程名称 System Verilog 系统验证技术

学

号

姓

名

专

业

指导老师

1

�

1、 实验步骤

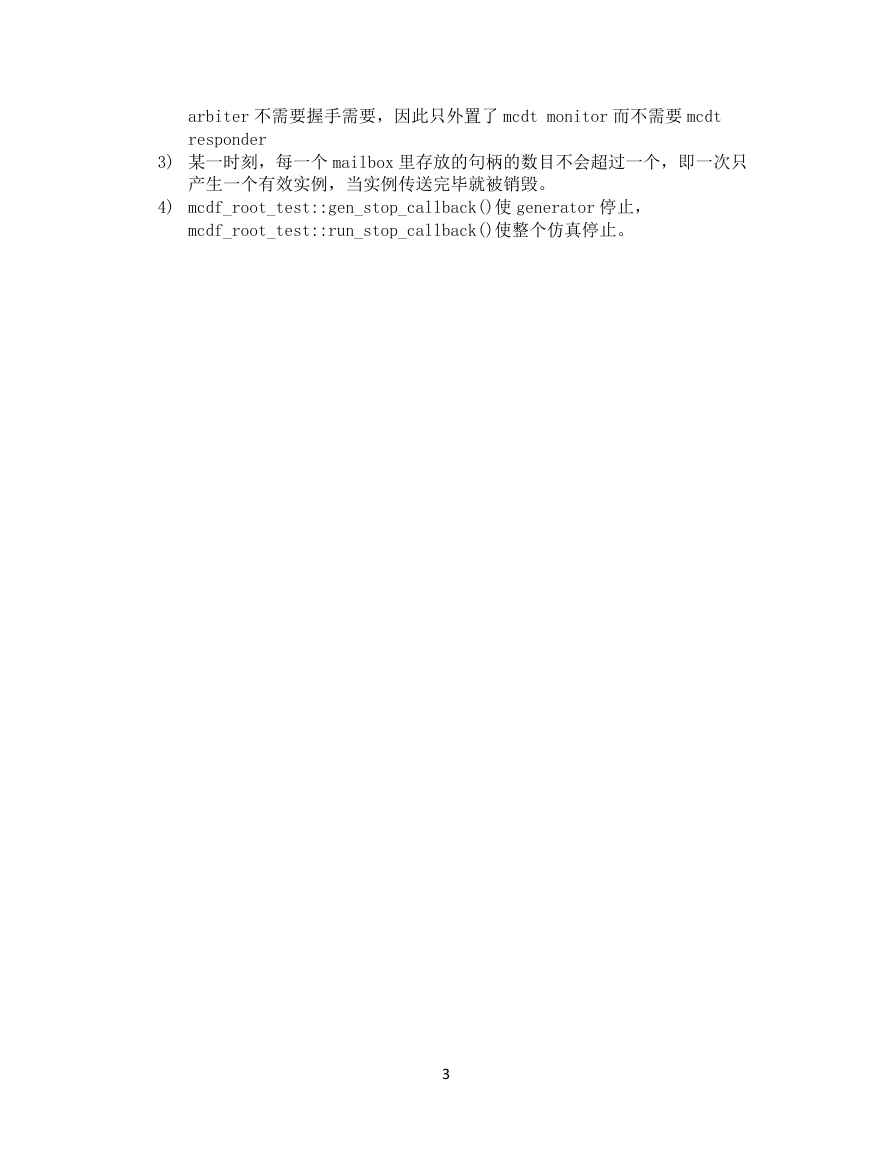

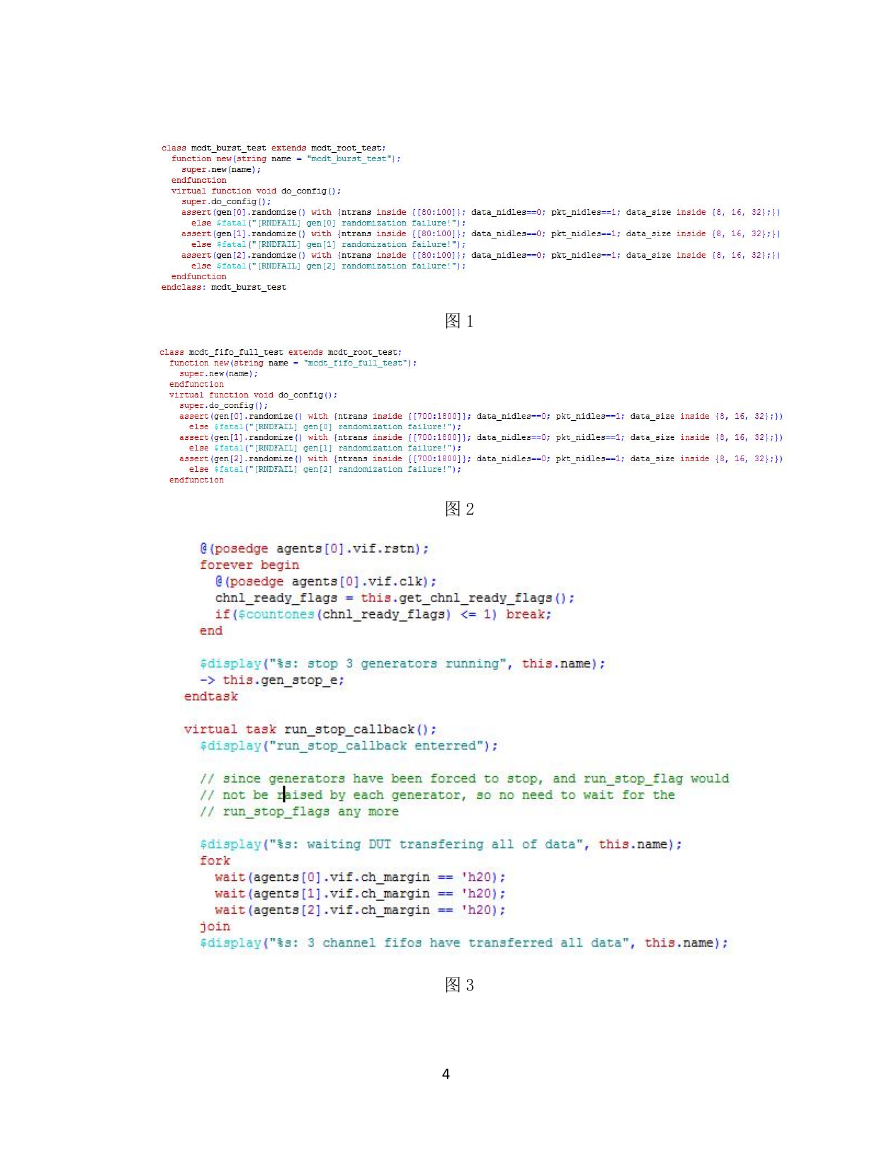

在 mcdt_burst_test 根据要求添加了:

1) 数据包的数据产生范围

2) 数据间隔

3) 数据包的间隔

4) 数据大小。

达到了实验要求中的实现测试用例 mcdt_burst_test,如图 1。

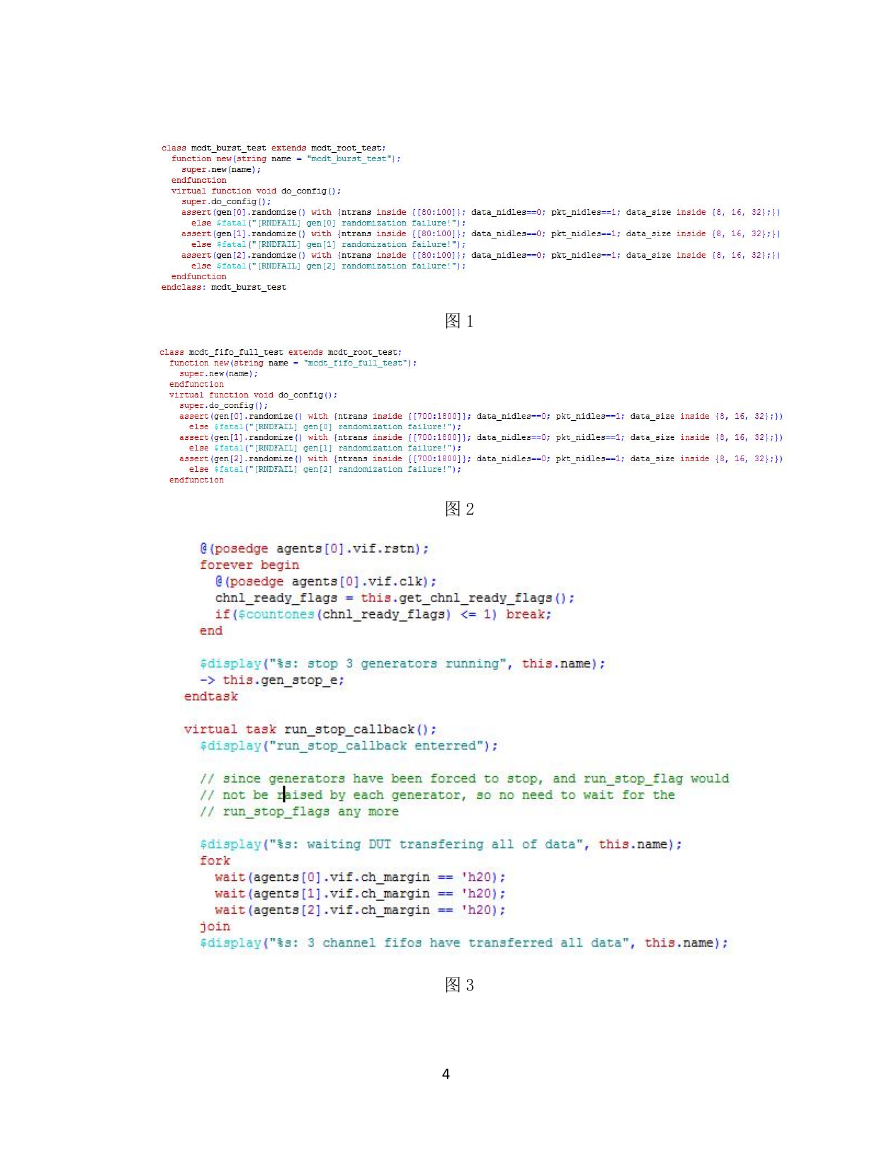

在 mcdt_fifo_full_test 根据要求添加了类似 mcdt_burst_test 的约束,达到了实

验要求中的实现测试用例 mcdt_fifo_full_test,如图 2。

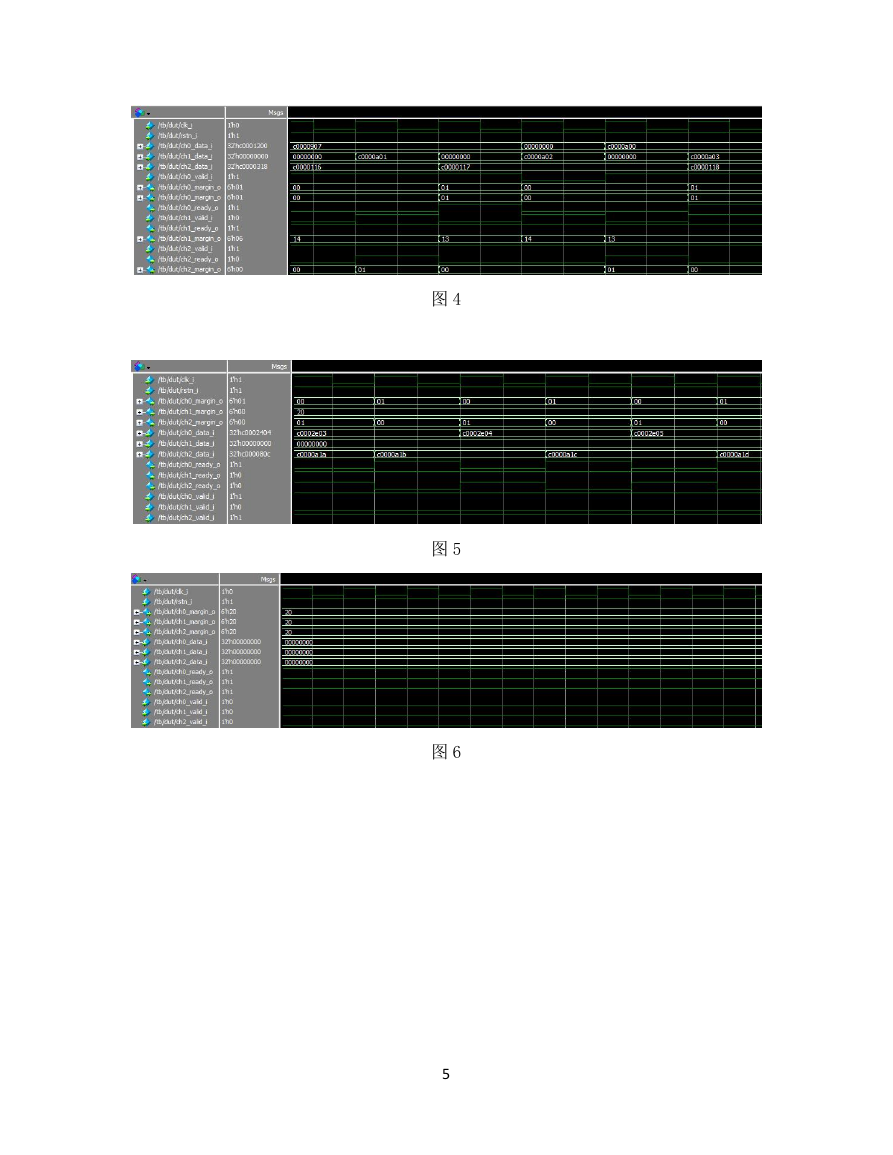

在 mcdt_fifo_full_test 根据要求添加了停止条件,使有两个或两个以上 channel

的 ready 信号同时拉低时,并且 channel FIFO 中的数据全部从 MCDT 送出时,停止

测试,如图 3。

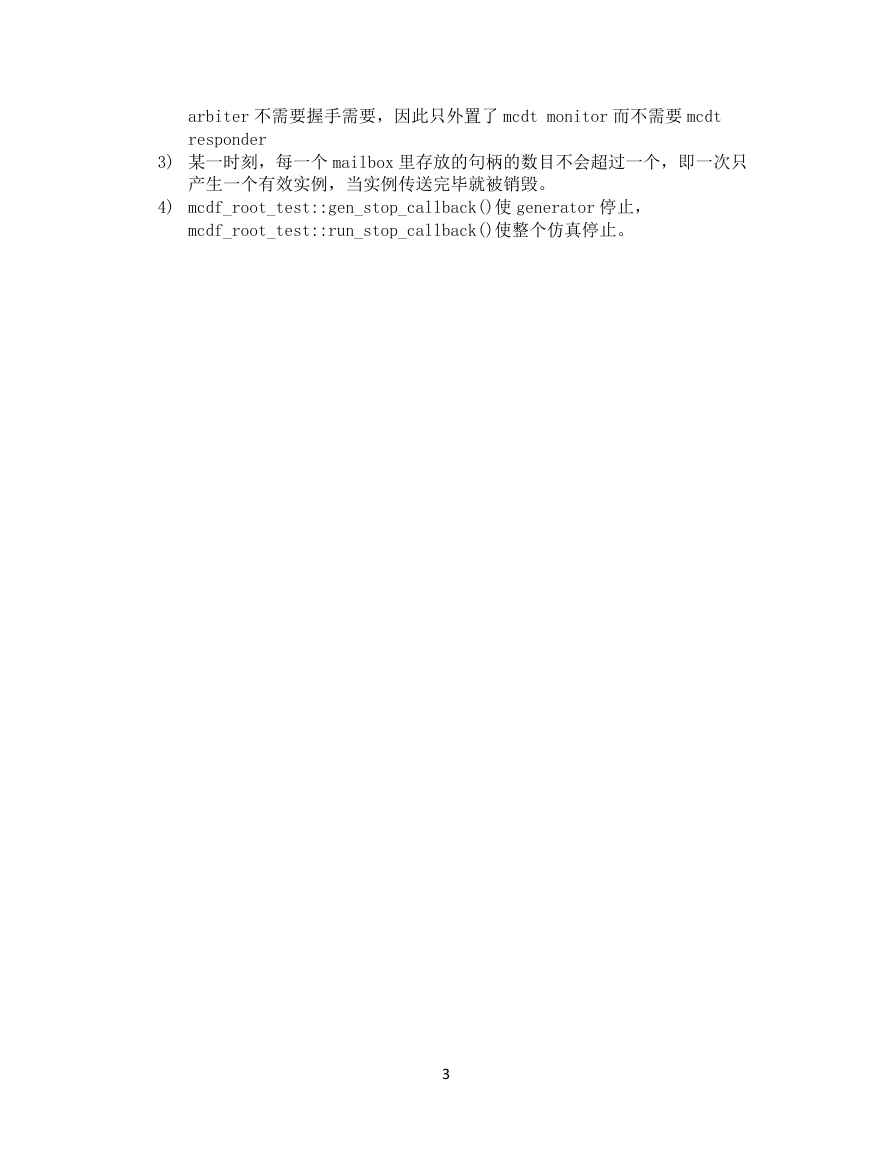

2、 实验结果

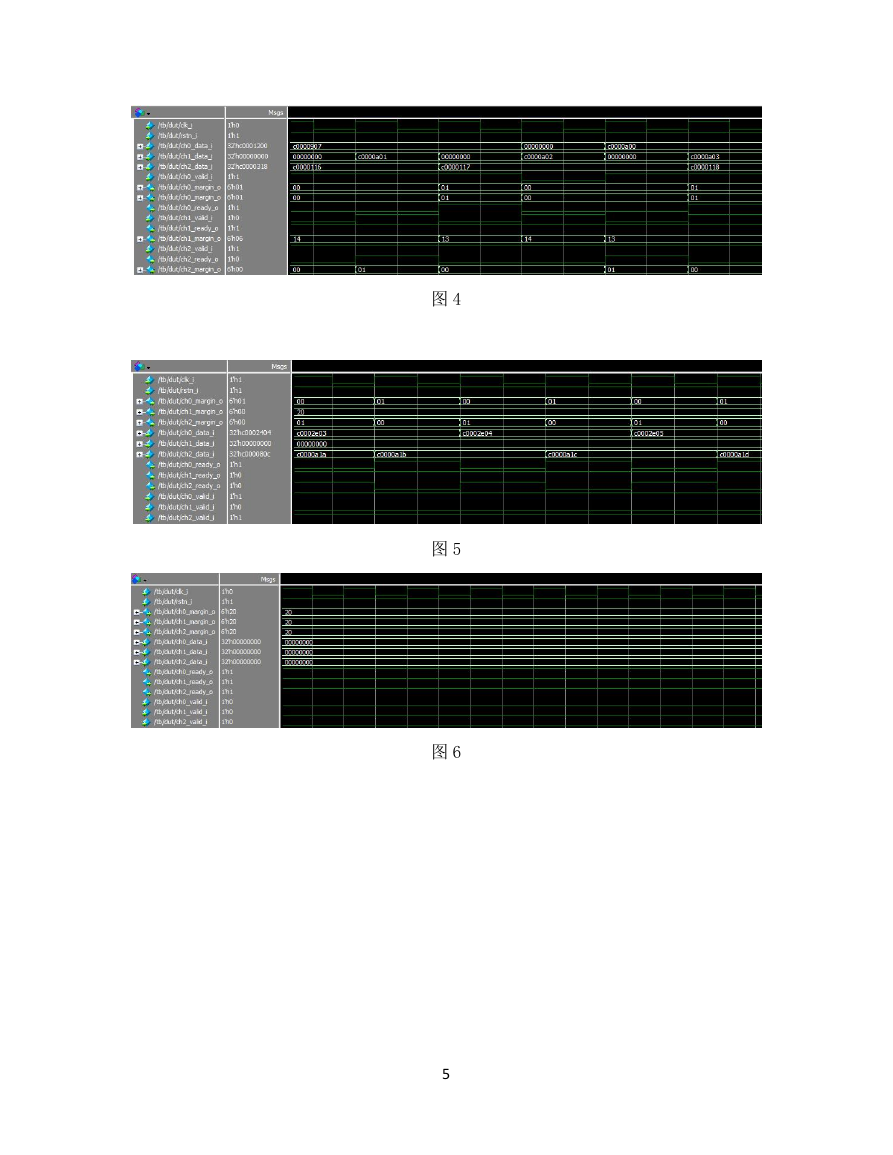

图 4 仿真波形中可见,三个通道的激励变化符合添加的约束,在波形中检查三个通

道的激励都能按照符合 BURST 发送要求。

图 5 仿真波形中可见,当没有 fifo 写满时,generator 会产生符合约束的连续数

据。

图 6 仿真波形中可见,当有或两个以上 channel 的 ready 信号同时拉低时,

generator 停止产生数据,等待将数据全部送出,当 margin 信号为 h20 即十进制

32 时,代表 fifo 清空,停止仿真,实现实验要求。

3、 实验总结

通过这次实验我学会了 QuestaSim 的基本操作流程,对 System Verilog 的基本

语法有了进一步认识,熟悉了 mcdt 测试平台结构,了解了:

1) channel stimulator 里数据的传输过程如下:

a) generator 不断产生 transaction 实例,将实例放在 mailbox 里,

b) initiator 通过 req_mb 句柄不断拿到 generator 里每一个 transaction

句柄,

c) 每拿到一个句柄,通过 chnl_write(req)消化,完成后通过 clone 产生

新的 rsp 对象,

d) 将 rsp 对象的句柄返回 generator。

2) channel initiator 与 channel monitor 是一一对应的关系,channel

monitor 从 interface 上拿到数据,monitor 都将监测到的数据送至 mcdf

checker 进行比对,与之进行对比的是 mcdt monitor 监测到的数据,由于

2

�

arbiter 不需要握手需要,因此只外置了 mcdt monitor 而不需要 mcdt

responder

3) 某一时刻,每一个 mailbox 里存放的句柄的数目不会超过一个,即一次只

产生一个有效实例,当实例传送完毕就被销毁。

4) mcdf_root_test::gen_stop_callback()使 generator 停止,

mcdf_root_test::run_stop_callback()使整个仿真停止。

3

�

图 1

图 2

图 3

4

�

图 4

图 5

图 6

5

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc