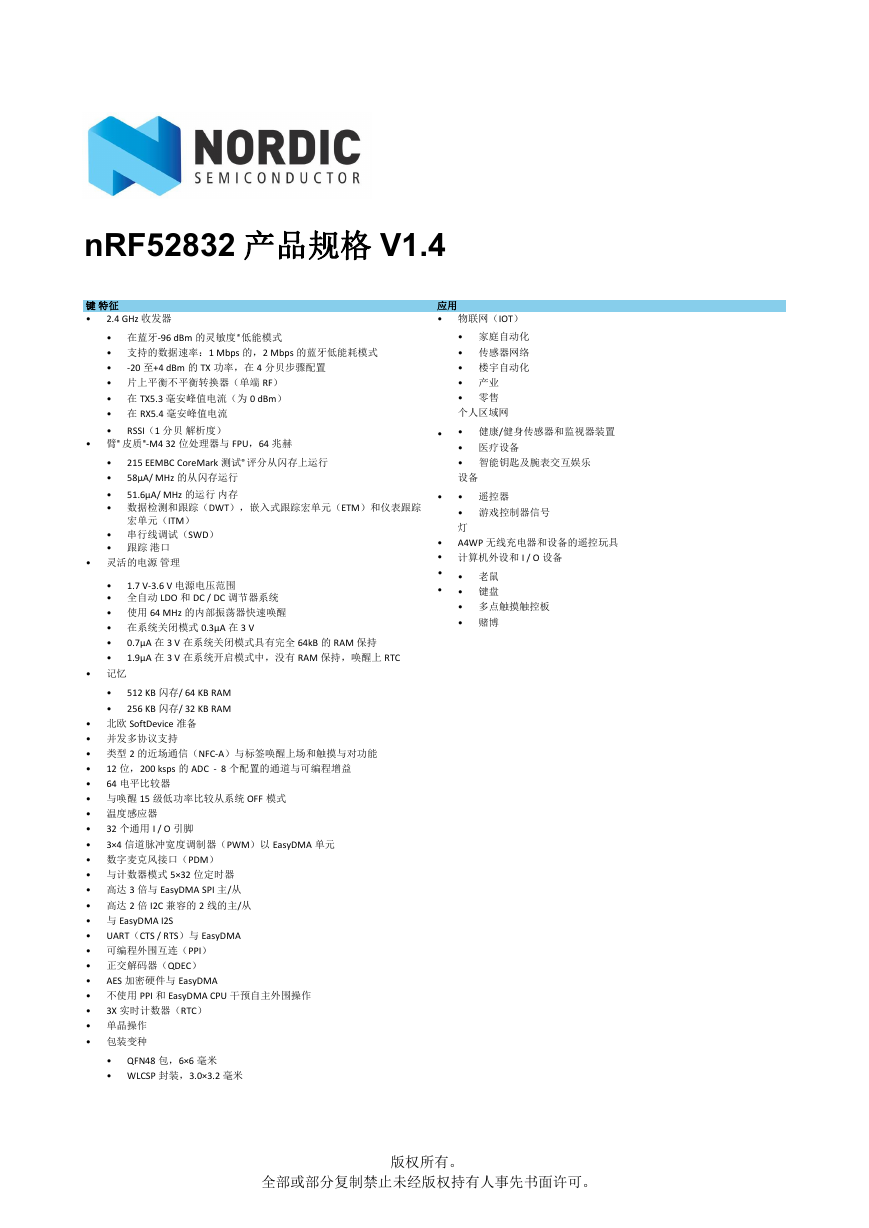

nRF52832_PS_v1.4_部分1.en.zh-CN

1修订记录

2关于本文档

2.1文件命名和状态

表1:定义文件名

2.2外围的命名和缩写

2.3登记表

2.3.1字段和值

2.4寄存器

表2:注册概述

3框图

图1:框图

4引脚分配

4.1QFN48引脚分配

图2:QFN48引脚分配,顶视图表3:QFN48引脚分配

4.2WLCSP球分配

图3:WLCSP球分配,顶视图表4:WLCSP球分配

4.3GPIO使用限制

4.3.1GPIO位于无线电附近

表5:GPIO推荐用量为QFN48包

表6:GPIO推荐用量为WLCSP封装

4.3.2NFC天线引脚

表7:由NFC使用GPIO引脚

5绝对最大额定值

表8:绝对最大额定值

6推荐工作条件

表9:建议的工作条件

6.1WLCSP光灵敏度

7中央处理器

7.1浮点中断

7.2电气规格

7.2.1 CPU性能

7.3 CPU和支持模块配置

8记忆

表10:变体内存

图4:内存布局

8.1RAM - 随机存取存储器

8.2闪存 - 非易失性存储器

8.3存储器映射

图5:存储器映射

8.4实例化

9AHB多层

9.1AHB多层优先

表12:AHB总线主控器

10EasyDMA

图6:示例EasyDMA

图7:EasyDMA存储器布局

10.1EasyDMA数组列表

图8:EasyDMA数组列表

11NVMC - 非挥发性记忆体控制器

11.1写闪存

11.2删除在Flash页面

11.3写入用户信息的配置寄存器(UICR)

11.4擦除用户信息的配置寄存器(UICR)

11.5清除所有

11.6高速缓存

11.7寄存器

表13:实例

11.7.4ERASEPCR1(已取消)

11.7.5清除所有

11.7.6ERASEPCR0(已取消)

11.7.7ERASEUICR

11.7.9我打

11.7.10我想

11.8电气规格

11.8.1Flash编程

12BPROT - 块保护

图9:程序存储器的受保护区域

12.1寄存器

12.1.2CONFIG1

12.1.3DISABLEINDEBUG

12.1.4CONFIG2

12.1.5CONFIG3

13FICR - 工厂信息配置寄存器

13.1寄存器

表17:实例

13.1.14DEVICEADDR [0]

13.1.15DEVICEADDR [1]

13.1.17INFO.VARIANT

13.1.38NFC.TAGHEADER0

13.1.39NFC.TAGHEADER1

13.1.40NFC.TAGHEADER2

13.1.41NFC.TAGHEADER3

14UICR - 用户信息的配置寄存器

14.1寄存器

表19:实例

14.1.3NRFFW [2]

14.1.4NRFFW [3]

14.1.5NRFFW [4]

14.1.6NRFFW [5]

14.1.7NRFFW [6]

14.1.8NRFFW [7]

14.1.9NRFFW [8]

14.1.10NRFFW [9]

14.1.11NRFFW [10]

14.1.12NRFFW [11]

14.1.13NRFFW [12]

14.1.14NRFFW [13]

14.1.15NRFFW [14]

14.1.16NRFHW [0]

14.1.17NRFHW [1]

14.1.18NRFHW [2]

14.1.19NRFHW [3]

14.1.20NRFHW [4]

14.1.21NRFHW [5]

14.1.22NRFHW [6]

14.1.23NRFHW [7]

14.1.24NRFHW [8]

14.1.25NRFHW [9]

14.1.26NRFHW [10]

14.1.27NRFHW [11]

14.1.60PSELRESET [0]

14.1.61PSELRESET [1]

14.1.63NFCPINS

15外围接口

图10:任务,事件,快捷方式和中断

15.1外设ID

15.2与共享ID的外围设备

表21:外围设备共享的ID

15.3外设寄存器

15.4位设置和清除

15.5任务

15.6活动

15.7快捷键

15.8中断

15.8.1中断清除

16调试和跟踪

图11:调试和跟踪概述

16.1DAP - 调试访问端口

重要:

16.2CTRL-AP - 控制访问端口

16.2.1寄存器

表22:注册概述

清除所有

ERASEALLSTATUS

APPROTECTSTATUS

16.3调试接口模式

16.4实时调试

16.5跟踪

16.5.1电气规格

跟踪端口

17电源和时钟管理

图12:电源管理单元

17.1电流消耗场景

表23:电流消耗的情况,常见疾病

电流消耗:收音机

18POWER - 电源

18.1监管机构

图13:LDO调节器设置

18.2系统关闭模式

18.3系统ON模式

18.3.1子电源模式

18.4电源监控器

图15:电源监控器

图16:电源失效比较(BOR =掉电复位)

18.5内存部分

18.6重启

18.6.1上电复位

18.6.2引脚复位

18.6.3从系统关闭模式复位唤醒

18.6.4软复位

18.6.5看门狗复位

18.6.6欠压复位

18.7保留寄存器

18.8复位行为

18.9寄存器

表24:实例

18.9.8GPREGRET2

18.9.9RAMON(已取消)

18.9.10RAMONB(已取消)

18.9.12RAM [0]。电源

18.9.13RAM [0] .POWERSET

18.9.14RAM [0] .POWERCLR

18.9.16RAM [1] .POWERSET

18.9.17RAM [1] .POWERCLR

18.9.19RAM [2] .POWERSET

18.9.20RAM [2] .POWERCLR

18.9.22RAM [3] .POWERSET

18.9.23RAM [3] .POWERCLR

18.9.25RAM [4] .POWERSET

18.9.26RAM [4] .POWERCLR

18.9.28RAM [5] .POWERSET

18.9.29RAM [5] .POWERCLR

18.9.31RAM [6] .POWERSET

18.9.32RAM [6] .POWERCLR

18.9.34RAM [7] .POWERSET

18.9.35RAM [7] .POWERCLR

18.10电气规格

18.10.1电流消耗,睡眠

nRF52832_PS_v1.4_部分2.en.zh-CN

图17:时钟控制

19.1.164兆赫晶体振荡器(HFXO)

图18:64兆赫晶体振荡器的电路图

19.2LFCLK时钟控制器

19.2.132.768 kHz的RC振荡器(LFRC)

19.2.2校准的32.768 kHz RC振荡器

19.2.3校准计时器

图19:校准定时器

19.2.432.768KHz的晶体振荡器(LFXO)

表26:依赖于时钟源LFCLKSRC配置

图20:32.768千赫晶体振荡器的电路图

19.2.532.768KHz的从HFCLK合成(LFSYNT)

19.3寄存器

表27:实例

19.3.5LFCLKRUN

19.3.7 LFCLKSRCCOPY

19.3.10 TRACECONFIG

19.4电气规格

19.4.164 MHz内部振荡器(HFINT)

19.4.532.768KHz的从HFCLK合成(LFSYNT)

20GPIO - 通用输入/输出

20.1引脚配置

图21:GPIO端口和GPIO引脚细节

图22:DETECT信号行为

20.2GPIO位于靠近收音机

20.3寄存器

表29:实例

20.3.4在

20.3.8LATCH

20.3.9DETECTMODE

20.4电气规格

20.4.1 GPIO电气规格

图23:GPIO驱动强度Vs电压,标准驱动,VDD = 3.0V,

图24:GPIO驱动强度Vs电压,高驱动器,VDD = 3.0V,

图25:最大吸收电流Vs电压,标准驱动

图27:上升和下降时间与温度,10%-90%,为25pF的负载电容,VDD = 3.0V,

21GPIOTE - GPIO任务和事件

表31:GPIOTE属性

表32:任务优先级

21.2端口事件

21.3任务和事件引脚配置

21.4寄存器

表33:实例

21.4.4CONFIG [1]

21.4.5CONFIG [2]

21.4.6CONFIG [3]

21.4.7CONFIG [4]

21.4.8CONFIG [5]

21.4.9CONFIG [6]

21.4.10CONFIG [7]

21.5电气规格

21.5.1 GPIOTE电气规格

22PPI - 可编程外围互连

CH [1] .EEP

陈

CHG [0]

...

CHG [米]

CH [0] .TEP

图28:PPI框图

表35:可配置并固定PPI通道

表36:预编程的通道

nRF52832_PS_v1.4_部分3.en.zh-CN

23RADIO - 2.4 GHz无线电

图29:RADIO框图

23.2包配置

图30:在空气包布局

图31:在-RAM无线数据包的表示,S0,长度和S1是可选

23.3最大分组长度

23.4地址配置

表39:逻辑地址的定义

图32:数据增白和去白化

23.6CRC

图33:CRC生成n位CRC的

23.7国家广播电台

表40:RADIO状态图

图34:无线电状态

图35:发射序列

图36:使用快捷键,以避免延误发射序列

图37:多个分组的传输

图38:接收序列

图39:使用快捷键,以避免延误接收序列

图40:多个分组的接收

23.11帧间间隔

23.12器件地址匹配

23.13位计数器

图41:位计数器示例

23.14.12PCNF0

23.14.13PCNF1

23.14.24RSSISAMPLE

23.14.26DATAWHITEIV

23.14.33 DAB [5]

23.14.44DACNF

23.14.45MODECNF0

23.15电气规格

23.15.1通用无线特性

23.15.6RX选择性

23.15.7RX互调

23.15.8无线电时间

24TIMER - 定时器/计数器

图42:示意框图定时器/计数器

24.2相比

24.3任务延迟

24.4任务优先级

24.5寄存器

表43:实例

24.5.7 CC [0]

12年5月24日CC [5]

24.6电气规格

24.6.1定时器电气规格

25RTC - 实时计数器

图43:RTC方框原理

25.2分辨率与溢出和预分频器

表45:RTC分辨率与溢出

25.3计数寄存器

图44:时序图 - COUNTER_PRESCALER_0

图45:时序图 - COUNTER_PRESCALER_1

25.5TICK事件

25.6事件控制功能

图46:任务,事件和中断的RTC

图47:时序图 - COMPARE_CLEAR

图48:时序图 - COMPARE_START

图49:时序图 - 比较

图50:时序图 - COMPARE_N + 2

图51:时序图 - COMPARE_N + 1

图52:时序图 - COMPARE_N-1

表46:在任务RTC抖动幅度

表47:在事件RTC抖动幅度

图53:时序图 - DELAY_CLEAR

图54:时序图 - DELAY_STOP

图55:时序图 - JITTER_START-

图56:时序图 - JITTER_START +

图57:时序图 - COUNTER_READ

25.11电气规格

25.11.1 RTC电气规格

26RNG - 随机数发生器

图58:随机数发生器

26.2速度

26.3寄存器

表50:实例

26.4电气规格

26.4.1 RNG电气规格

27TEMP - 温度传感器

27.1寄存器

表52:实例

27.1.10B0

27.1.11B1

27.1.12B2

27.1.13B3

27.1.14B4

27.1.15B5

17年1月27日T1

27.2电气规格

27.2.1温度传感器电气规格

28ECB - AES电子码本模式加密

28.1共享资源

28.2EasyDMA

28.3欧洲央行的数据结构

表54:ECB数据结构的概述

28.5电气规格

28.5.1 ECB电气规格

29CCM - AES CCM模式加密

图59:密钥流生成接着加密或解密。快捷方式是可选的。

29.2加密

图60:加密

图61:解密

表57:无线配置设置

图62:对即时加密配置

图63:在即时使用PPI连接加密

图64:在即时解密的配置

图65:在即时使用PPI就绪事件之间的电台和KSGEN任务的AES CCM连接解密

表58:CCM数据结构的概述

表59:用于未加密分组数据结构

29.8EasyDMA和ERROR事件

29.9寄存器

表61:实例

10年9月29日SCRATCHPTR

30AAR - 加速地址解析器

30.1共享资源

30.2EasyDMA

30.3解析解析地址

图66:可分解地址

图67:地址解析与包预先加载到RAM

图68:地址解析与数据包由无线电加载到RAM

表63:IRK数据结构的概述

30.7电气规格

30.7.1 AAR电气规格

31SPIM - 与EasyDMA串行外围接口主

图69:SPIM - SPI主机EasyDMA

表66:SPI模式

31.2EasyDMA

31.2.1 EasyDMA名单

EasyDMA数组列表

图70:EasyDMA数组列表

图71:SPI主交易

31.5主控模式引脚配置

表67:GPIO配置

31.6.8频率

31.6.10RXD.MAXCNT

31.6.11RXD.AMOUNT

31.6.14TXD.MAXCNT

31.6.15TXD.AMOUNT

31.6.18ORC

31.7电气规格

31.7.1SPIM主接口电气规格

31.7.2串行外设接口硕士(SPIM)定时规范

图72:SPIM时序图

32SPIS - 与EasyDMA串行外围接口奴

图73:SPI从

表70:SPI模式

32.3SPI从操作

图74:启用END并获得之间的快捷方式,当SPI交易

表71:在启用外围之前GPIO配置

32.5.16MAXRX ( Deprecated )

32.5.17AMOUNTRX ( Deprecated )

32.5.19RXD.MAXCNT

32.5.20RXD.AMOUNT

nRF52832_PS_v1.4_部分4.en.zh-CN

32.5.23AMOUNTTX(已取消)

32.5.25TXD.MAXCNT

32.5.26TXD.AMOUNT

32.5.28DEF

32.6电气规格

32.6.1SPIS从接口的电气规范

32.6.2串行外设接口奴(SPIS)定时规范

图75:SPIS时序图

图76:通用SPIM和SPI时序图

33TWIM - I2C兼容双线接口与主EasyDMA

图77:TWI主与EasyDMA

图78:典型的TWI设置包括一个主站和三个从

33.2EasyDMA

33.2.1 EasyDMA名单

EasyDMA数组列表

图79:EasyDMA数组列表

图80:TWI主数据写入到从属

33.4硕士读序列

图81:来自从该TWI主读取数据

图82:在重复启动序列,其中,所述TWI主从设备读4个字节写入两个字节,随后

图83:使用挂起任务,以确保在低优先级中断运行安全的双重复启动序列

33.7主控模式引脚配置

表74:在启用外围之前GPIO配置

33.8.11RXD.MAXCNT

33.8.12RXD.AMOUNT

33.8.15TXD.MAXCNT

33.8.16TXD.AMOUNT

33.9电气规格

33.9.1TWIM接口电气规范

33.9.2双线接口硕士(TWIM)定时规范

图84:TWIM时序图,1个字节的事务

图85:推荐TWIM上拉值与线电容

34TWIS - 与I2C兼容EasyDMA双线接口从

图86:TWI从与EasyDMA

图87:典型的TWI设置包括一个主站和三个从

图88:TWI从状态机

34.2EasyDMA

34.3TWI从响应于读取命令

图89:该TWI从响应于读取命令

图90:该TWI从响应于写入命令

图91:在重复启动序列,其中,所述TWI主机通过从从机读取四个字节写入两个字节,随后

34.7低电量

34.8从模式引脚配置

表78:在启用外围之前GPIO配置

34.9.12 RXD.AMOUNT

34.9.15 TXD.AMOUNT

34.9.18CONFIG

34.9.19ORC

34.10电气规格

34.10.1TWIS从接口的电气规范

34.10.2TWIS从时序规格

图92:TWIS时序图,1个字节的事务

35UARTE - 通用异步接收器/带EasyDMA发射机

图93:UARTE配置

35.2EasyDMA

35.3传输

图94:UARTE传输

35.4前台

图95:UARTE接收

图96:UARTE接收经由STOPRX强制停止

35.5错误条件

35.6使用UARTE无流量控制

35.7奇偶组态

35.8低电量

35.9引脚配置

表81:在启用外围之前GPIO配置

35.10.13RXD.MAXCNT

35.10.14RXD.AMOUNT

35.10.16TXD.MAXCNT

35.10.17TXD.AMOUNT

35.10.18CONFIG

35.11电气规格

35.11.1 UARTE电气规范

36QDEC - 正交解码器

图97:正交解码器配置

表84:采样值的编码

36.4蓄电池

36.5输出/输入管脚

36.6引脚配置

表85:在启用外围之前GPIO配置

36.7.8REPORTPER

36.7.9ACC

36.7.10ACCREAD

36.7.14DBFEN

36.7.15LEDPRE

36.7.16ACCDBL

36.7.17ACCDBLREAD

36.8电气规格

36.8.1 QDEC电气规格

37SAADC - 逐次逼近模拟 - 数字转换器

37.1共享资源

37.2概观

图98:简化ADC框图

37.3数字输出

V(P)

37.4模拟输入和信道

表88:合法连接CH [N]对模拟输入

37.5.2连续模式

37.5.3过采样

37.5.4扫描模式

图99:RAM放置(甚至RESULT.MAXCNT)的实施例,信道1,2和5启用

图100:RAM放置(奇数RESULT.MAXCNT)的实施例,信道1,2和5启用

图101:ADC

37.7电阻梯

图102:梯形电阻为正输入端(负输入是等价的,采用RESN代替RESP)

37.9采集时间

37.10限制事件监控

图104:的限制的监视信道实施例“n”个

37.11寄存器

表90:实例

表91:注册概述

37.11.9 CH [0] .LIMIT

37.11.12CH [1] .CONFIG

37.11.13CH [1] .LIMIT

37.11.17 CH [2] .LIMIT

37.11.21CH[3].LIMIT

37.11.22CH[4].PSELP

37.11.25 CH[4].LIMIT

37.11.29CH[5].LIMIT

37.11.30CH[6].PSELP

37.11.31CH[6].PSELN

37.11.32CH[6].CONFIG

37.11.33CH[6].LIMIT

37.11.37 CH[7].LIMIT

37.11.39OVERSAMPLE

37.11.40SAMPLERATE

37.11.42RESULT.MAXCNT

37.11.43RESULT.AMOUNT

37.12Electrical specification

37.12.1SAADC Electrical Specification

Figure 105: Model of SAADC input (one channel)

Figure 106: ADC INL vs Output Code

Figure 107: ADC DNL vs Output Code

38 COMP — Comparator

Figure 109: Comparator overview

38 Operation modes

Figure 110: Comparator in differential mode

Figure 111: Hysteresis enabled in differential mod

Figure 112: Comparator in single-ended mode

Figure 113: Hysteresis example where VIN+ s

Figure 114: Hysteresis example where VIN+

38.3.8 REFSEL

nRF52832_PS_v1.4_部分5.en.zh-CN

39LPCOMP - 低功耗比较器

图115:低功率比较

图116:滞后上的噪声的输入信号的影响

39.2引脚配置

39.3寄存器

表94:实例

39.4电气规格

39.4.1 LPCOMP电气规格

40WDT - 看门狗定时器

40.1重载标准

40.2暂时暂停看门狗

40.3看门狗复位

40.4寄存器

表96:实例

40.5电气规格

40.5.1看门狗定时器电气规格

41SWI - 软件中断

41.1寄存器

表98:实例

42nfct成员 - 近场通信标签

42.1概观

图117:NFC框图

图118:NFC状态图

42.3EasyDMA

42.4冲突解决

表99:NFCID1字节分配(第一顶送去空气)

42.5帧定时控制器

图119:帧定时控制器(FRAMEDELAYMODE =窗口)

图120:帧组装

42.7帧分解器

图121:帧拆机插图

42.8天线接口

42.9nfct成员天线建议

图122:nfct成员天线建议

42.10电池保护

42.11参考

42.12寄存器

表100:实例

42.12.6FRAMESTATUS.RX

42.12.7CURRENTLOADCTRL

42.12.8FIELDPRESENT

42.12.11FRAMEDELAYMODE

42.12.12PACKETPTR

42.12.13MAXLEN

42.12.14TXD.FRAMECONFIG

42.12.15TXD.AMOUNT

42.12.16RXD.FRAMECONFIG

42.12.17RXD.AMOUNT

42.12.19 NFCID1_2ND_LAST

42.12.21SENSRES

42.12.22SELRES

42.13电气规格

42.13.1nfct成员电气规格

42.13.2nfct成员时序参数

图123:nfct成员的定时参数(快捷方式FIELDDETECTED和FIEL

43PDM - 脉冲密度调制接口

CLK

DIN

图124:PDM模块

43.3抽取滤波器

43.4EasyDMA

表102:DMA样本存储

43.5硬件示例

图125:单个PDM麦克风的实施例,有线左

图126:单个PDM麦克风的实施例,有线如权利

图127:2个PDM麦克风的实施例

表103:使周之前GPIO配置

43.7.8GAINR

43.7.9PSEL.CLK

43.7.10PSEL.DIN

43.7.11SAMPLE.PTR

43.7.12SAMPLE.MAXCNT

43.8电气规格

43.8.1 PDM电气规格

图128:PDM时序图

44I2S - IC间音频接口

图129:I2S主

图130:发射和接收。CONFIG.FORMAT =对齐,CONFIG.SW

44.4串行时钟(SCK)

44.5主时钟(MCK)

图131:比,MCK和LRCK之间的关系。表106:配置示例

图132:I2S格式。CONFIG.SWIDTH等于半帧大小。

图133:对齐格式。CONFIG.SWIDTH等于半帧大小。

图134:对于8比特立体声内存映射。CONFIG.SWIDTH = 8位,CONFIG.CHANNE

图135:为8位单声道内存映射。CONFIG.SWIDTH = 8位,CONFIG.CHANNELS

图136:16位立体声内存映射。CONFIG.SWIDTH = 16位,CONFIG.CHANNEL

图137:16位单声道内存映射,只有左声道。CONFIG.SWIDTH = 16位,CONFIG.C

图138:24位立体声内存映射。CONFIG.SWIDTH = 24Bit的,CONFIG.CHAN

图139:24位单声道内存映射,只有左声道。CONFIG.SWIDTH = 24Bit的,CONFI

44.9引脚配置

表107:使外围设备(主模式)之前配置GPIO

表108:启用外围设备(从机模式)之前配置GPIO

44.10寄存器

表109:实例

44.10.7CONFIG.TXEN

44.10.9CONFIG.MCKFREQ

44.10.10CONFIG.RATIO

44.10.14 CONFIG.CHANNELS

44.11电气规格

44.11.1 I2S时序规范

图140:I2S时序图

45MWU - 内存手表单元

45.1寄存器

表112:实例

45.1.4NMIEN

45.1.5NMIENSET

45.1.6NMIENCLR

45.1.7PERREGION [0] .SUBSTATWA

45.1.8PERREGION [0] .SUBSTATRA

45.1.9PERREGION [1] .SUBSTATWA

45.1.10PERREGION [1] .SUBSTATRA

45.1.12REGIONENSET

45.1.21 REGION [3] .END

46EGU - 事件发电机组

表114:EGU配置

表115:实例

46.2电气规格

46.2.1 EGU电气规格

47PWM - 脉冲宽度调制

图141:PWM模块

图142:PWM向上计数器例子 - FallingEdge极性

图143:PWM向上和向下计数器示例

图144:解码器存储器的访问模式

表117:当安全地更新寄存器PWM

图145:简单序列示例

nRF52832_PS_v1.4_部分6.en.zh-CN

使用两个序列实施例:图146

图149:复序列(LOOP.CNT> 0)开始SEQ [1]

47.3限制

47.4引脚配置

表118:开始PWM生成之前推荐GPIO配置

47.5.6模式

47.5.7台面板

47.5.11SEQ [0] .PTR

47.5.12SEQ [0] .CNT

47.5.13SEQ [0] .REFRESH

47.5.15SEQ [1] .PTR

47.5.16SEQ [1] .CNT

47.5.17SEQ [1] .REFRESH

47.5.18SEQ [1] .ENDDELAY

47.6电气规格

47.6.1 PWM电气规格

48SPI - 串行外围接口主

图150:SPI主

表121:SPI模式

表122:GPIO配置

48.1.3SPI主交易序列

图151:SPI主交易

图152:SPI主交易

48.2.4PSELSCK(已取消)

48.2.5PSELMOSI(已取消)

48.2.6PSELMISO(已取消)

48.3电气规格

48.3.1SPI主接口

48.3.2串行外设接口(SPI)主定时规范

图153:SPI主时序图

49TWI - I2C兼容的双线接口

图154:TWI大师的主要特点

图155:典型的TWI设置包括一个主站和三个从

表125:GPIO配置

49.4主写序列

图156:TWI主数据写入到从属

49.5硕士读序列

图157:从从该TWI主读取数据

图158:在重复启动序列,其中,所述TWI主而不在其之间执行一个停止写一个字

49.7低电量

49.8寄存器

表126:实例

49.9电气规格

49.9.1TWI接口电气规范

49.9.2两线接口(TWI)定时规范

图159:TWI时序图,1个字节的事务

50UART - 通用异步接收器/发送器

图160:UART配置

50.3共享资源

50.4传输

图161:UART发送

图162:UART接收

50.6暂停UART

50.7错误条件

50.8使用UART无流量控制

50.9奇偶组态

50.10寄存器

表129:实例

50.11电气规格

50.11.1 UART电气规范

51机械参数

51.1QFN48 6×6毫米封装

图163:QFN48 6×6毫米封装

图164:WLCSP封装

52订购信息

52.1IC标记

图165:包装标识

图166:内盒标签

图168:命令码表133:缩写

52.4代码范围和值

表134:封装变量代码

表137:生产配置码

表138:生产版本代码

表139:年代码

表140:周码

表141:地块码

表142:容器码

52.5产品选项

表144:开发工具订货代码

53参考电路

53.1原理QFAA和QFAB QFN48内部LDO设置

图169:QFAA和QFAB QFN48与内部LDO设置

表145:材料QFAA和QFAB QFN48与内部LDO设置的比尔

53.2原理QFAA和QFAB QFN48与DC / DC稳压器设置

图170:QFAA和QFAB QFN48与DC / DC调节器设置

表146:材料QFAA和QFAB QFN48与DC / DC调节器设置的比尔

53.3原理QFAA和QFAB QFN48与DC / DC稳压器和NFC设置

图171:QFAA和QFAB QFN48与DC / DC调节器和NFC设置

表147:材料QFAA和QFAB QFN48与DC / DC转换器和NFC设置的比尔

图172:CIAA WLCSP与内部LDO设置

表148:物料清单为CIAA WLCSP内部LDO设置

图173:CIAA WLCSP与DC / DC调节器设置

表149:为CIAA WLCSP与DC / DC调节器设置物料清单

图174:CIAA WLCSP与DC / DC调节器和NFC设置

表150:为CIAA WLCSP与DC / DC转换器和NFC设置材料的比尔

53.8PCB布局示例

图175:顶丝层

54免责声明

54.1符合RoHS和REACH声明

54.2生命支持应用

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc