"

!!!!!!!"

·产品、研发、测试·

!

!

"!!!!!!!"

一种 FPGA 的远程系统升级方法

吴冬冬 1, 2 杨晓君 1 张佩珩 1

1( 中国科学院计算技术研究所, 北京 100080)

2( 中国科学院研究生院, 北京 100039)

E- mail: wdd@ncic.ac.cn

摘 要 介绍基于 SRAM 工艺的 FPGA 器件的配置方法。结合嵌入式处理器应用, 设计一种使用 CPLD 器件及通用大容

量 Flash 的 FPGA 远程系统升级方法。最后对该方法在系统性能、复杂度和经济性等方面的优越性进行了比较和分析。

关键词 远程系统升级 FPGA 配置

文章编号 1002- 8331- ( 2006) 18- 0086- 03 文献标识码 A 中图分类号 TP302.1

A Method of FPGA Remote System Upgr ade

Wu Dongdong1, 2 Yang Xiaojun1 Zhang Peiheng1

1( Institute of Computing Technology, Chinese Academy of Sciences, Beijing 100080)

2( Graduate School of the Chinese Academy of Sciences, Beijing 100039)

Abstr act:

In this paper, how to configure FPGA devices which use SRAM cells to store configuration data is

introduced firstly.Combined with the use of embedded processor, a method of FPGA remote system upgrade is proposed.

It

this method including the

performance, complexity and economy is surveyed and compared.

is made up of CPLD devices and normal

the advantage of

flash memory.At

last

Keywor ds:

remote system upgrade, FPGA, configuration

1 引言

由于 FPGA 器件所采用的 SRAM 工艺具有挥发性的特点,

掉电后数据会丢失, 因此它的配置数据需要存储在外置的非易

失性存储器中, 每次上电后需重新配置 FPGA 器件[1]。一般厂商

提供专用的非易失性存储器, 可以通过编程器或专用下载电缆

烧写[5]。

随 着 FPGA 规 模 和 性 能 的 不 断 提 高 , FPGA 器 件 应 用 越 来

越广泛。除了厂商提供的配置方法, 研究人员和工程师又设计

了其它方案, 如利用外挂通用 ROM 或 Flash 的 单 片 机 控 制 配

置[2, 3], 通过普通 PC 串口线下载配 置 数 据 [4]等, 避 免 了 使 用 价 格

昂贵的专用器件和电缆。

基 于 FPGA 器 件 设 计 的 产 品 最 大 的 问 题 是 系 统 的 维 护 和

升级, 以上 FPGA 配置方法有个共同的缺点, 就是灵活性较差,

在 FPGA 系 统 升 级 时 都 必 须 重 新 连 接 下 载 电 缆 或 使 用 编 程 器

对存储器件进行烧写。这些硬件上的操作, 不方便软件人员及

用户的使用。为此, 本文提出了一种 FPGA 的远程系统升级方

法, 实现对 FPGA 器件的规格升级和远程系统部署等操作, 达

到缩短开发周期的目的。

本文结合 PowerPC440GX 嵌入式处理器的应用, 用 64Mb

通用 Flash 器件存储配置文件, 用 CPLD 器件作为配置控制器,

设计一种针对 ALTERA 公司 Stratix II 系 列 FPGA 器 件 的 远 程

系统升级方法。本设计的原理对于其它 FPGA 器件同样适合。

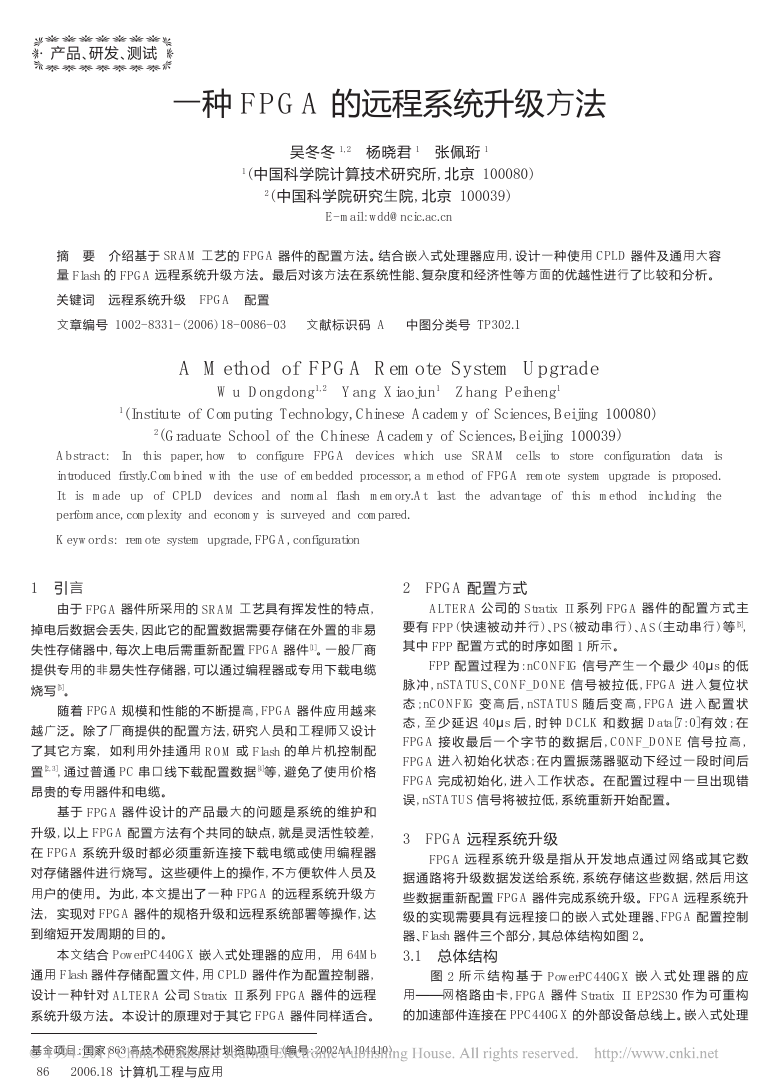

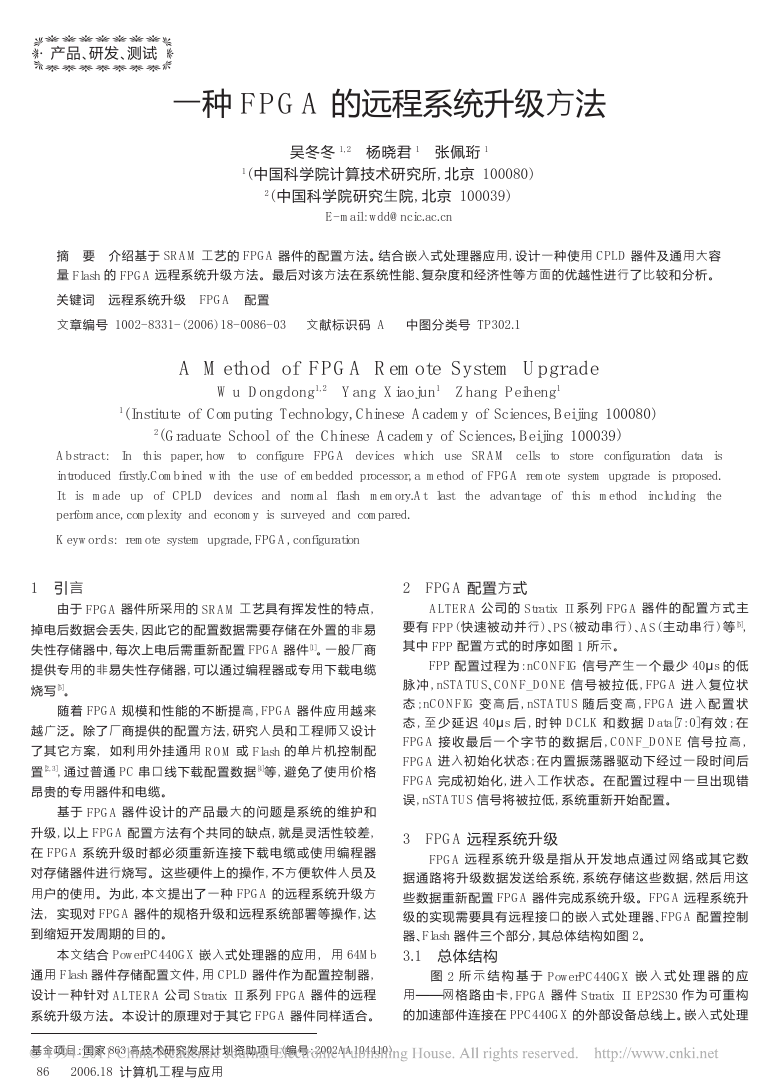

2 FPGA 配置方式

ALTERA 公 司 的 Stratix II 系 列 FPGA 器 件 的 配 置 方 式 主

要有 FPP( 快 速 被 动 并 行) 、PS( 被 动 串 行) 、AS( 主 动 串 行) 等 [5],

其中 FPP 配置方式的时序如图 1 所示。

FPP 配 置 过 程 为: nCONFIG 信 号 产 生 一 个 最 少 40μs 的 低

脉 冲 , nSTATUS、CONF_DONE 信 号 被 拉 低 , FPGA 进 入 复 位 状

态 ; nCONFIG 变 高 后 , nSTATUS 随 后 变 高 , FPGA 进 入 配 置 状

态 , 至 少 延 迟 40μs 后 , 时 钟 DCLK 和 数 据 Data[7: 0]有 效 ; 在

FPGA 接 收 最 后 一 个 字 节 的 数 据 后 , CONF_DONE 信 号 拉 高 ,

FPGA 进入初始化状态; 在 内 置 振 荡 器 驱 动 下 经 过 一 段 时 间 后

FPGA 完成初始化, 进入 工 作 状 态 。 在 配 置 过 程 中 一 旦 出 现 错

误, nSTATUS 信号将被拉低, 系统重新开始配置。

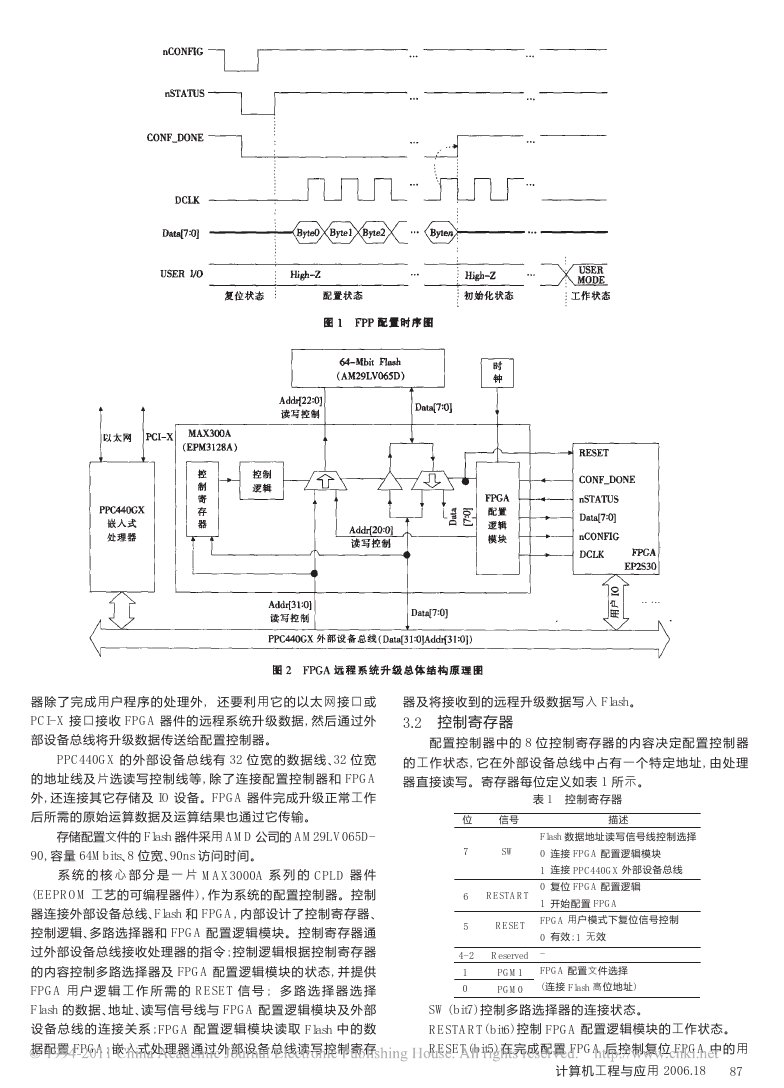

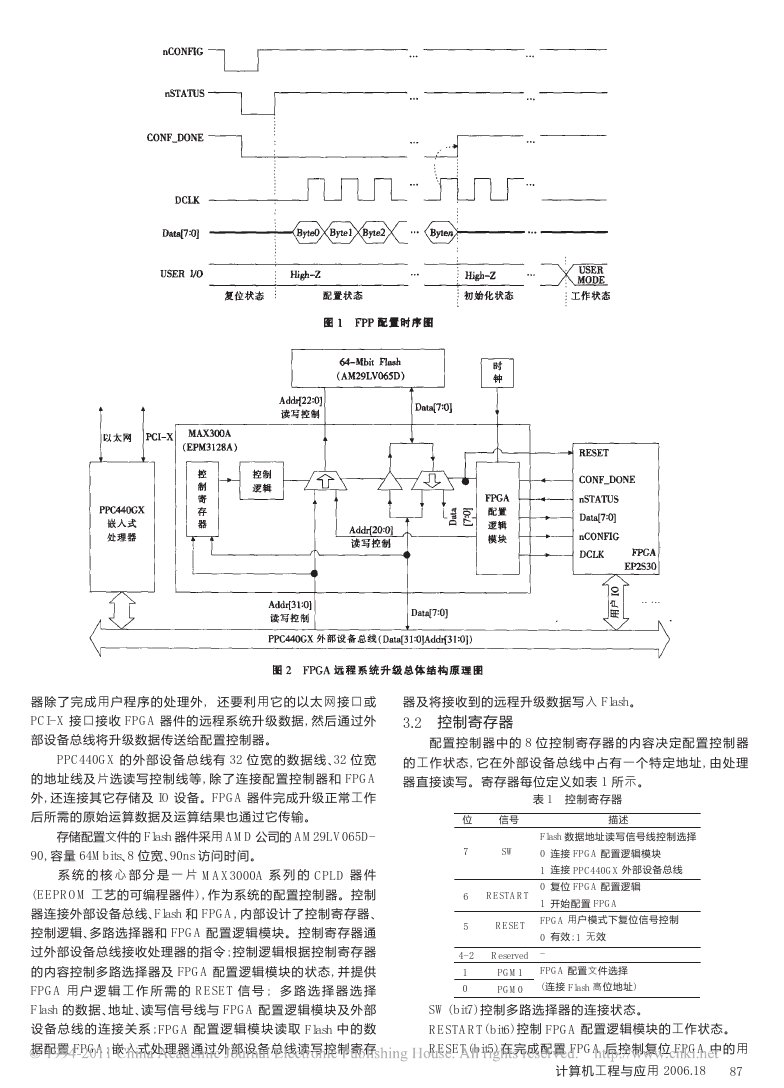

3 FPGA 远程系统升级

FPGA 远 程 系 统 升 级 是 指 从 开 发 地 点 通 过 网 络 或 其 它 数

据 通 路 将 升 级 数 据 发 送 给 系 统 , 系 统 存 储 这 些 数 据, 然 后 用 这

些数据重新配置 FPGA 器件完成系统升级。FPGA 远程系统升

级的实现需要具 有 远 程 接 口 的 嵌 入 式 处 理 器 、FPGA 配 置 控 制

器、Flash 器件三个部分, 其总体结构如图 2。

3.1 总体结构

图 2 所 示 结 构 基 于 PowerPC440GX 嵌 入 式 处 理 器 的 应

用———网 格 路 由 卡 , FPGA 器 件 Stratix II EP2S30 作 为 可 重 构

的加速部件连接在 PPC440GX 的外部设备总线上。嵌入式处理

基金项目: 国家 863 高技术研究发展计划资助项目( 编号: 2002AA104410)

86

2006.18 计算机工程与应用

�

器 除 了 完 成 用 户 程 序 的 处 理 外, 还 要 利 用 它 的 以 太 网 接 口 或

PCI- X 接口接收 FPGA 器件的远程系统升级数据, 然后通过外

部设备总线将升级数据传送给配置控制器。

PPC440GX 的 外 部 设 备 总 线 有 32 位 宽 的 数 据 线 、32 位 宽

的地址线及片选读写控 制 线 等, 除 了 连 接 配 置 控 制 器 和 FPGA

外, 还连接其它存储及 IO 设备。FPGA 器件完成升级正常工作

后所需的原始运算数据及运算结果也通过它传输。

存储配置文件的 Flash 器件采用 AMD 公司的 AM29LV065D-

90, 容量 64Mbits、8 位宽、90ns 访问时间。

系 统 的 核 心 部 分 是 一 片 MAX3000A 系 列 的 CPLD 器 件

( EEPROM 工艺的可编程器件) , 作为系统的配置控制器。控制

器连接外部设备总线、Flash 和 FPGA, 内部设计了控制寄存器、

控制逻辑、多路选择器和 FPGA 配置逻辑模块。控制寄存器通

过外部设备总线接收处理器的指令; 控制逻辑根据控制寄存器

的内容控制多路选择器及 FPGA 配置逻辑模块的状态, 并提供

FPGA 用 户 逻 辑 工 作 所 需 的 RESET 信 号 ; 多 路 选 择 器 选 择

Flash 的数据、地址、读写信号线与 FPGA 配置逻辑模块 及 外 部

设 备 总 线 的 连 接 关 系 ; FPGA 配 置 逻 辑 模 块 读 取 Flash 中 的 数

据配置 FPGA; 嵌入式处 理 器 通 过 外 部 设 备 总 线 读 写 控 制 寄 存

器及将接收到的远程升级数据写入 Flash。

3.2 控制寄存器

配 置 控 制 器 中 的 8 位 控 制 寄 存 器 的 内 容 决 定 配 置 控 制 器

的 工 作 状 态, 它 在 外 部 设 备 总 线 中 占 有 一 个 特 定 地 址, 由 处 理

器直接读写。寄存器每位定义如表 1 所示。

表 1 控制寄存器

位

信号

描述

7

6

5

4- 2

1

0

SW

RESTART

RESET

Reserved

PGM1

PGM0

Flash 数据地址读写信号线控制选择

0 连接 FPGA 配置逻辑模块

1 连接 PPC440GX 外部设备总线

0 复位 FPGA 配置逻辑

1 开始配置 FPGA

FPGA 用户模式下复位信号控制

0 有效; 1 无效

-

FPGA 配置文件选择

( 连接 Flash 高位地址)

SW( bit7) 控制多路选择器的连接状态。

RESTART( bit6) 控制 FPGA 配置逻辑模块的工作状态。

RESET( bit5) 在完成配 置 FPGA 后 控 制 复 位 FPGA 中 的 用

87

计算机工程与应用 2006.18

�

户逻辑, 使其能正常工作。

系 统 使 用 的 FPGA 器 件 EP2S30 的 配 置 文 件 ( .rbf 文 件 )

大小为 10.1Mbits( 1.262 5Mbytes) , 系 统 使 用 的 的 Flash 容 量 为

64Mbits( 8Mbytes) 。将 Flash 的地址空间以 16Mb 大小等分, 总

共可以存储 4 个不同的配置文件。嵌入式处理器和 FPGA 配置

逻 辑 模 块 每 次 能 访 问 的 空 间 也 是 16Mb, 即 需 要 21bits 地 址 。

Flash 总 共 有 23bits 地 址, 它 的 高 位 地 址 Addr[22: 21]由 控 制 寄

存器的 PGM1( bit1) 和 PGM0( bit0) 决 定, 处 理 器 通 过 设 定 PGM

[1: 0]的内容来决定系统能读写的 Flash 地址空间。

寄 存 器 bit[4: 2]保 留 , 如 用 于 在 使 用 更 大 的 Flash 时 增 加

PGM 的位数。

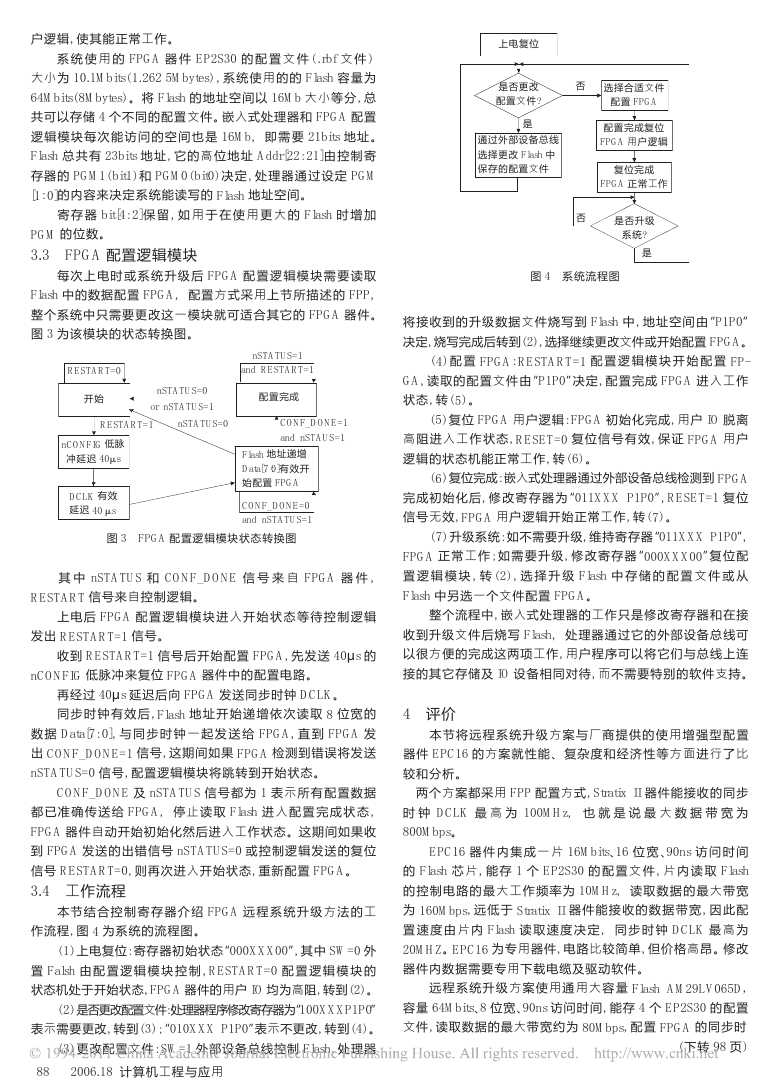

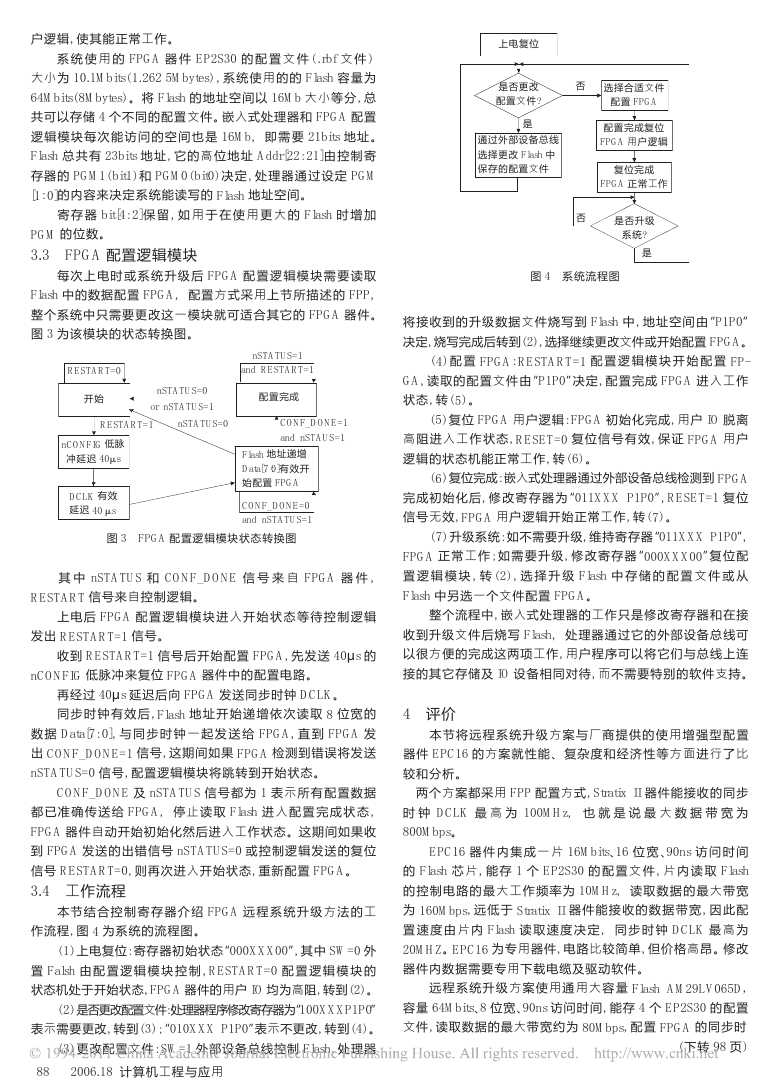

3.3 FPGA 配置逻辑模块

每 次 上 电 时 或 系 统 升 级 后 FPGA 配 置 逻 辑 模 块 需 要 读 取

Flash 中的数据配置 FPGA, 配置方式采用上节所描述的 FPP,

整个系统中只需要更改这一模块就可适合其它的 FPGA 器件。

图 3 为该模块的状态转换图。

RESTART=0

开始

nSTATUS=0

or nSTATUS=1

RESTART=1

nSTATUS=0

nCONFIG 低脉

冲延迟 40!s

DCLK 有效

延迟 40 !s

nSTATUS=1

and RESTART=1

配置完成

CONF_DONE=1

and nSTAUS=1

Flash 地址递增

Data[7∶0]有效开

始配置 FPGA

CONF_DONE=0

and nSTATUS=1

图 3 FPGA 配置逻辑模块状态转换图

其 中 nSTATUS 和 CONF_DONE 信 号 来 自 FPGA 器 件 ,

RESTART 信号来自控制逻辑。

上 电 后 FPGA 配 置 逻 辑 模 块 进 入 开 始 状 态 等 待 控 制 逻 辑

发出 RESTART=1 信号。

收到 RESTART=1 信号后开始配置 FPGA, 先发送 40μs 的

nCONFIG 低脉冲来复位 FPGA 器件中的配置电路。

再经过 40μs 延迟后向 FPGA 发送同步时钟 DCLK。

同 步 时 钟 有 效 后 , Flash 地 址 开 始 递 增 依 次 读 取 8 位 宽 的

数 据 Data[7: 0], 与 同 步 时 钟 一 起 发 送 给 FPGA, 直 到 FPGA 发

出 CONF_DONE=1 信号, 这期间如果 FPGA 检测到错误将发送

nSTATUS=0 信号, 配置逻辑模块将跳转到开始状态。

CONF_DONE 及 nSTATUS 信 号 都 为 1 表 示 所 有 配 置 数 据

都 已 准 确 传 送 给 FPGA, 停 止 读 取 Flash 进 入 配 置 完 成 状 态 ,

FPGA 器件自动开始初始化然后进入工作状态。这期间如果收

到 FPGA 发送的出错信号 nSTATUS=0 或控制逻辑发送的复位

信号 RESTART=0, 则再次进入开始状态, 重新配置 FPGA。

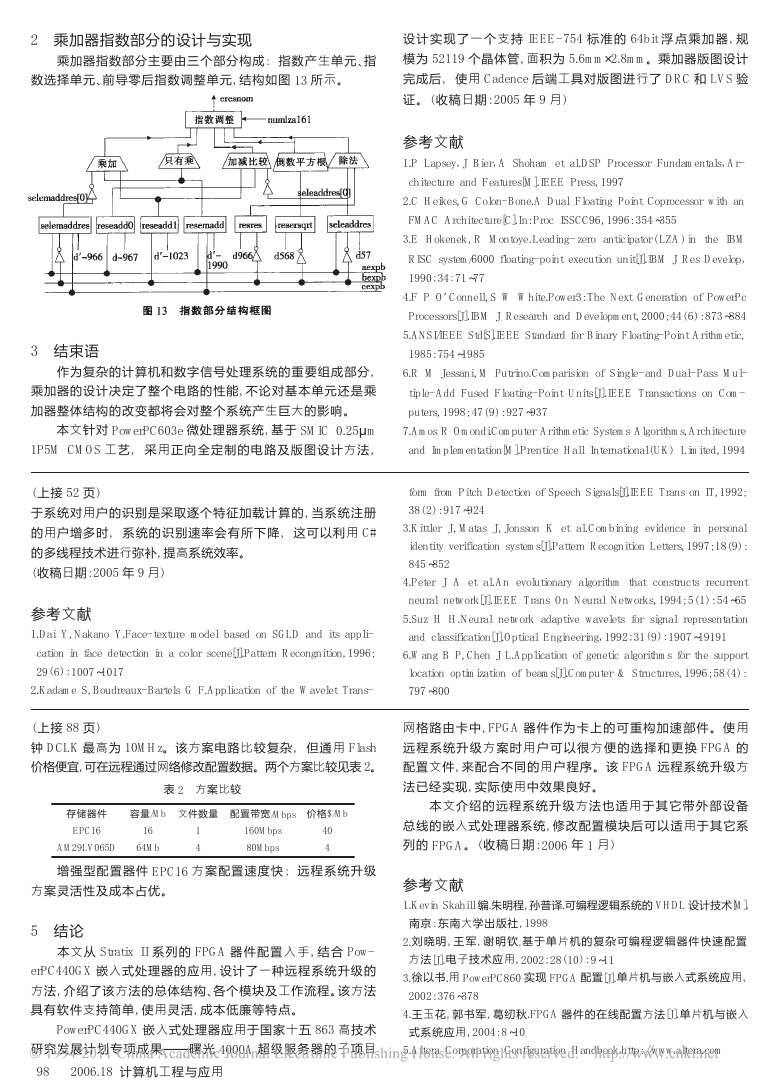

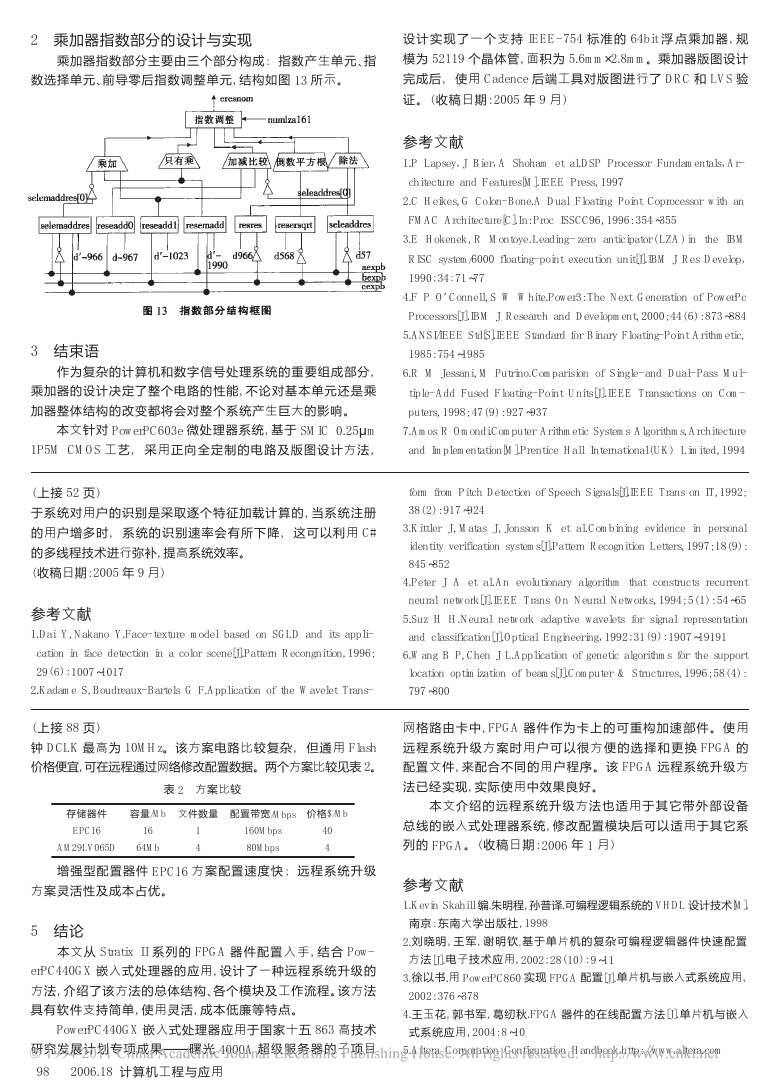

3.4 工作流程

本 节 结 合 控 制 寄 存 器 介 绍 FPGA 远 程 系 统 升 级 方 法 的 工

作流程, 图 4 为系统的流程图。

( 1) 上电复位: 寄存器初始状态“000XXX00”, 其中 SW=0 外

置 Falsh 由 配 置 逻 辑 模 块 控 制 , RESTART=0 配 置 逻 辑 模 块 的

状态机处于开始状态, FPGA 器件的用户 IO 均为高阻, 转到( 2) 。

( 2) 是否更改配置文件: 处理器程序修改寄存器为“100XXXP1P0”

表示需要更改, 转到( 3) ;“010XXX P1P0”表示不更改, 转到( 4) 。

( 3) 更改配置文件: SW=1 外部设备总线控制 Flash, 处理器

88

2006.18 计算机工程与应用

上电复位

是否更改

配置文件?

是

通过外部设备总线

选择更改 Flash 中

保存的配置文件

否

选择合适文件

配置 FPGA

配置完成复位

FPGA 用户逻辑

复位完成

FPGA 正常工作

否

是否升级

系统?

是

图 4 系统流程图

将接收到的升级数据文件 烧 写 到 Flash 中, 地 址 空 间 由“P1P0”

决定, 烧写完成后转到( 2) , 选择继续更改文件或开始配置 FPGA。

( 4) 配 置 FPGA: RESTART=1 配 置 逻 辑 模 块 开 始 配 置 FP-

GA, 读取的配置文件由“P1P0”决定, 配置完成 FPGA 进 入 工 作

状态, 转( 5) 。

( 5) 复位 FPGA 用户逻辑: FPGA 初始化完成, 用户 IO 脱离

高 阻 进 入 工 作 状 态, RESET=0 复 位 信 号 有 效, 保 证 FPGA 用 户

逻辑的状态机能正常工作, 转( 6) 。

( 6) 复位完成: 嵌入式处理器通过外部设备总线检测到 FPGA

完成初始化后, 修 改 寄 存 器 为“011XXX P1P0”, RESET=1 复 位

信号无效, FPGA 用户逻辑开始正常工作, 转( 7) 。

( 7) 升级系统: 如不需要升级, 维持寄存器“011XXX P1P0”,

FPGA 正 常 工 作; 如 需 要 升 级, 修 改 寄 存 器“000XXX00”复 位 配

置 逻 辑 模 块 , 转 ( 2) , 选 择 升 级 Flash 中 存 储 的 配 置 文 件 或 从

Flash 中另选一个文件配置 FPGA。

整个流程中, 嵌入式处理器的工作只是修改寄存器和在接

收到升级文件后烧写 Flash, 处理器通过它的外部设备总线可

以很方便的完成这两项工作, 用户程序可以将它们与总线上连

接的其它存储及 IO 设备相同对待, 而不需要特别的软件支持。

4 评价

本 节 将 远 程 系 统 升 级 方 案 与 厂 商 提 供 的 使 用 增 强 型 配 置

器件 EPC16 的方案就性能、复杂度和经济 性 等 方 面 进 行 了 比

较和分析。

两个方案都采用 FPP 配置方式, Stratix II 器件能接收的同步

时 钟 DCLK 最 高 为 100MHz, 也 就 是 说 最 大 数 据 带 宽 为

800Mbps。

EPC16 器 件 内 集 成 一 片 16Mbits、16 位 宽 、90ns 访 问 时 间

的 Flash 芯 片 , 能 存 1 个 EP2S30 的 配 置 文 件 , 片 内 读 取 Flash

的 控 制 电 路 的 最 大 工 作 频 率 为 10MHz, 读 取 数 据 的 最 大 带 宽

为 160Mbps, 远 低 于 Stratix II 器 件 能 接 收 的 数 据 带 宽 , 因 此 配

置 速 度 由 片 内 Flash 读 取 速 度 决 定 , 同 步 时 钟 DCLK 最 高 为

20MHZ。EPC16 为专用器件, 电路比较简单, 但价格高昂。修改

器件内数据需要专用下载电缆及驱动软件。

远 程 系 统 升 级 方 案 使 用 通 用 大 容 量 Flash AM29LV065D,

容量 64Mbits、8 位宽、90ns 访问时间, 能存 4 个 EP2S30 的配置

文件, 读取数据的最大带宽约为 80Mbps, 配置 FPGA 的同步时

( 下转 98 页)

�

2 乘加器指数部分的设计与实现

乘加器指数部分主要由三个部分构成: 指数产生单元、指

数选择单元、前导零后指数调整单元, 结构如图 13 所示。

设 计 实 现 了 一 个 支 持 IEEE- 754 标 准 的 64bit 浮 点 乘 加 器 , 规

模为 52119 个晶体管, 面积为 5.6mm×2.8mm。乘加器版图设计

完成后, 使用 Cadence 后端工具对版图进行了 DRC 和 LVS 验

证。( 收稿日期: 2005 年 9 月)

参考文献

1.P Lapsey, J Bier, A Shoham et al.DSP Processor Fundamentals, Ar-

chitecture and Features[M].IEEE Press, 1997

2.C Heikes, G Colon- Bone.A Dual Floating Point Coprocessor with an

FMAC Architecture[C].In: Proc ISSCC96, 1996: 354~355

3.E Hokenek , R Montoye.Leading- zero anticipator ( LZA) in the IBM

RISC system/6000 floating- point execution unit[J].IBM J Res Develop,

1990; 34: 71~77

4.F P O’Connell, S W White.Power3: The Next Generation of PowerPc

Processors[J].IBM J Research and Development, 2000; 44( 6) : 873~884

5.ANSI/IEEE Std[S].IEEE Standard for Binary Floating- Point Arithmetic,

1985: 754~1985

6.R M Jessani, M Putrino.Comparision of Single- and Dual- Pass Mul-

tiple- Add Fused Floating- Point Units[J].IEEE Transactions on Com-

puters, 1998; 47( 9) : 927~937

7.Amos R Omondi.Computer Arithmetic Systems Algorithms, Architecture

and Implementation[M].Prentice Hall International( UK) Limited, 1994

form from Pitch Detection of Speech Signals[J].IEEE Trans on IT, 1992;

38( 2) : 917~924

3.Kittler J, Matas J, Jonsson K et al.Combining evidence in personal

identity verification systems[J].Pattern Recognition Letters, 1997; 18( 9) :

845~852

4.Peter J A et al.An evolutionary algorithm that constructs recurrent

neural network[J].IEEE Trans On Neural Networks, 1994; 5( 1) : 54~65

5.Suz H H.Neural network adaptive wavelets for signal representation

and classification[J].Optical Engineering, 1992; 31( 9) : 1907~19191

6.Wang B P, Chen J L.Application of genetic algorithms for the support

location optimization of beams[J].Computer & Structures, 1996; 58( 4) :

797~800

网格路由卡中, FPGA 器 件 作 为 卡 上 的 可 重 构 加 速 部 件 。 使 用

远 程 系 统 升 级 方 案 时 用 户 可 以 很 方 便 的 选 择 和 更 换 FPGA 的

配置文件, 来配合不同的用户程序。该 FPGA 远程系统升级方

法已经实现, 实际使用中效果良好。

本 文 介 绍 的 远 程 系 统 升 级 方 法 也 适 用 于 其 它 带 外 部 设 备

总线的嵌入式处理器系统, 修改配置模块后可以适用于其它系

列的 FPGA。( 收稿日期: 2006 年 1 月)

参考文献

1.Kevin Skahill 编.朱明程, 孙普译.可编程逻辑系统的 VHDL 设计技术[M].

南京: 东南大学出版社, 1998

2.刘 晓 明, 王 军, 谢 明 钦.基 于 单 片 机 的 复 杂 可 编 程 逻 辑 器 件 快 速 配 置

方法[J].电子技术应用, 2002; 28( 10) : 9~11

3.徐以书.用 PowerPC860 实现 FPGA 配置[J].单片机与嵌入式系统应用,

2002: 376~378

4.王玉花, 郭书军, 葛纫秋.FPGA 器件的在线配置方法[J].单片机与嵌入

式系统应用, 2004: 8~10

5.Altera Corporation Configuration Handbook.http: //www.altera.com

3 结束语

作为复杂的计算机和数字信号处理系统的重要组成部分,

乘加器的设计决定了整个电路的性能, 不论对基本单元还是乘

加器整体结构的改变都将会对整个系统产生巨大的影响。

本文针对 PowerPC603e 微处理器系统, 基于 SMIC 0.25μm

1P5M CMOS 工 艺, 采 用 正 向 全 定 制 的 电 路 及 版 图 设 计 方 法,

( 上接 52 页)

于系统对用户的识别是采取逐个特征加载计算的, 当系统注册

的用户增多时, 系统的识别速率会有所下降, 这可以利用 C#

的多线程技术进行弥补, 提高系统效率。

( 收稿日期: 2005 年 9 月)

参考文献

1.Dai Y, Nakano Y.Face- texture model based on SGLD and its appli-

cation in face detection in a color scene[J].Pattern Recongnition, 1996;

29( 6) : 1007~1017

2.Kadame S, Boudreaux- Bartels G F.Application of the Wavelet Trans-

( 上接 88 页)

钟 DCLK 最高为 10MHz。该方案电路比较复杂, 但通用 Flash

价格便宜, 可在远程通过网络修改配置数据。两个方案比较见表 2。

表 2 方案比较

容量/Mb

文件数量

配置带宽/Mbps

价格$/Mb

存储器件

EPC16

16

AM29LV065D

64Mb

1

4

160Mbps

80Mbps

40

4

增强型配置器件 EPC16 方案配置速度 快; 远 程 系 统 升 级

方案灵活性及成本占优。

5 结论

本 文 从 Stratix II 系 列 的 FPGA 器 件 配 置 入 手 , 结 合 Pow-

erPC440GX 嵌入式处理器的应用, 设计了一种远程系统升级的

方法, 介绍了该方法的总体结构、各个模块及工作流程。该方法

具有软件支持简单, 使用灵活, 成本低廉等特点。

PowerPC440GX 嵌入式处理器应用于国家十五 863 高技术

研究发展 计 划 专 项 成 果 ———曙 光 4000A 超 级 服 务 器 的 子 项 目

98

2006.18 计算机工程与应用

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc