DOI:10.16186/j.cnki.1673-9787.2014.06.018

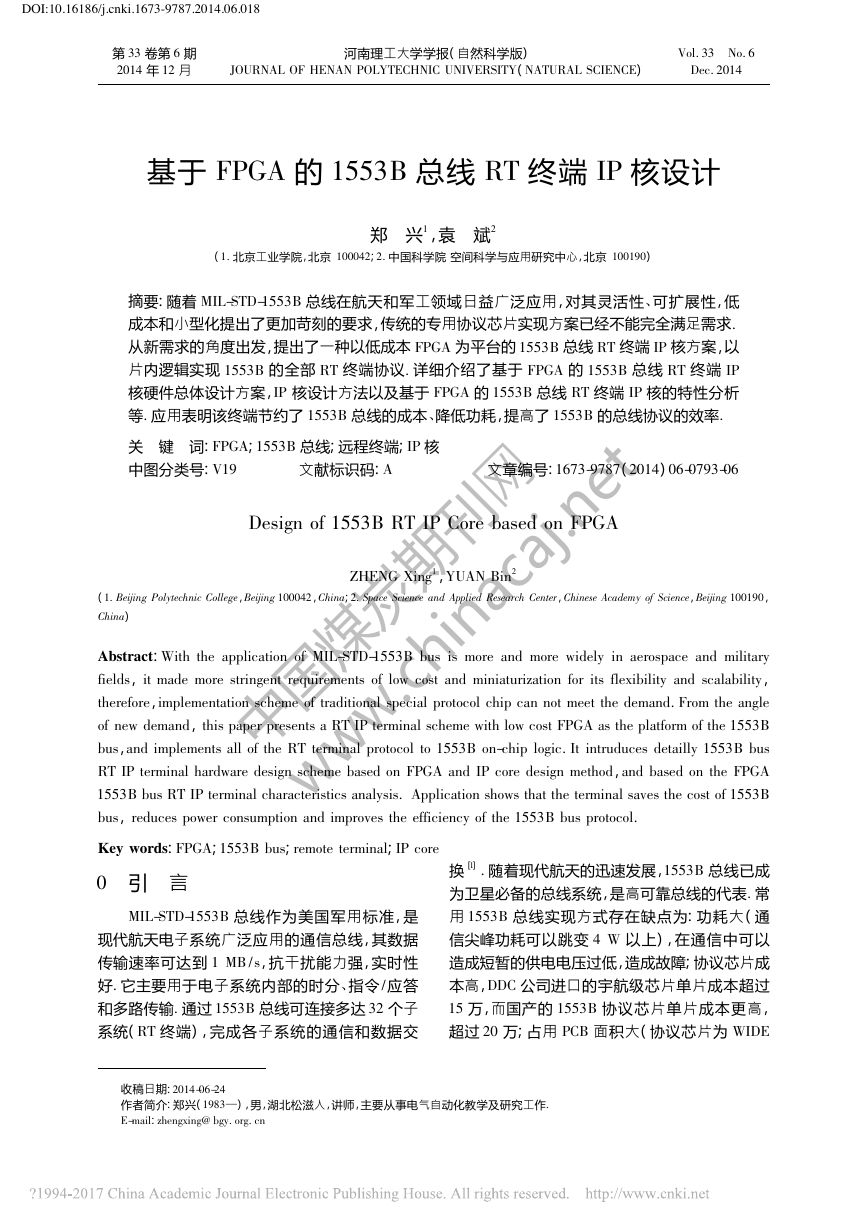

基于FPGA的1553B总线RT终端IP核设计郑兴1,袁斌2(1.北京工业学院,北京100042;2.中国科学院空间科学与应用研究中心,北京100190)*摘要:随着MIL-STD-1553B总线在航天和军工领域日益广泛应用,对其灵活性、可扩展性,低成本和小型化提出了更加苛刻的要求,传统的专用协议芯片实现方案已经不能完全满足需求.从新需求的角度出发,提出了一种以低成本FPGA为平台的1553B总线RT终端IP核方案,以片内逻辑实现1553B的全部RT终端协议.详细介绍了基于FPGA的1553B总线RT终端IP核硬件总体设计方案,IP核设计方法以及基于FPGA的1553B总线RT终端IP核的特性分析等.应用表明该终端节约了1553B总线的成本、降低功耗,提高了1553B的总线协议的效率.关键词:FPGA;1553B总线;远程终端;IP核中图分类号:V19文献标识码:A文章编号:1673-9787(2014)06-0793-06Designof1553BRTIPCorebasedonFPGAZHENGXing1,YUANBin2(1.BeijingPolytechnicCollege,Beijing100042,China;2.SpaceScienceandAppliedResearchCenter,ChineseAcademyofScience,Beijing100190,China)Abstract:WiththeapplicationofMIL-STD-1553Bbusismoreandmorewidelyinaerospaceandmilitaryfields,itmademorestringentrequirementsoflowcostandminiaturizationforitsflexibilityandscalability,therefore,implementationschemeoftraditionalspecialprotocolchipcannotmeetthedemand.Fromtheangleofnewdemand,thispaperpresentsaRTIPterminalschemewithlowcostFPGAastheplatformofthe1553Bbus,andimplementsalloftheRTterminalprotocolto1553Bon-chiplogic.Itintruducesdetailly1553BbusRTIPterminalhardwaredesignschemebasedonFPGAandIPcoredesignmethod,andbasedontheFPGA1553BbusRTIPterminalcharacteristicsanalysis.Applicationshowsthattheterminalsavesthecostof1553Bbus,reducespowerconsumptionandimprovestheefficiencyofthe1553Bbusprotocol.Keywords:FPGA;1553Bbus;remoteterminal;IPcore0引言MIL-STD-1553B总线作为美国军用标准,是现代航天电子系统广泛应用的通信总线,其数据传输速率可达到1MB/s,抗干扰能力强,实时性好.它主要用于电子系统内部的时分、指令/应答和多路传输.通过1553B总线可连接多达32个子系统(RT终端),完成各子系统的通信和数据交换[1].随着现代航天的迅速发展,1553B总线已成为卫星必备的总线系统,是高可靠总线的代表.常用1553B总线实现方式存在缺点为:功耗大(通信尖峰功耗可以跳变4W以上),在通信中可以造成短暂的供电电压过低,造成故障;协议芯片成本高,DDC公司进口的宇航级芯片单片成本超过15万,而国产的1553B协议芯片单片成本更高,超过20万;占用PCB面积大(协议芯片为WIDE第33卷第6期2014年12月河南理工大学学报(自然科学版)JOURNALOFHENANPOLYTECHNICUNIVERSITY(NATURALSCIENCE)Vol.33No.6Dec.2014*收稿日期:2014-06-24作者简介:郑兴(1983—),男,湖北松滋人,讲师,主要从事电气自动化教学及研究工作.E-mail:zhengxing@bgy.org.cn中国煤炭期刊网 www.chinacaj.net�

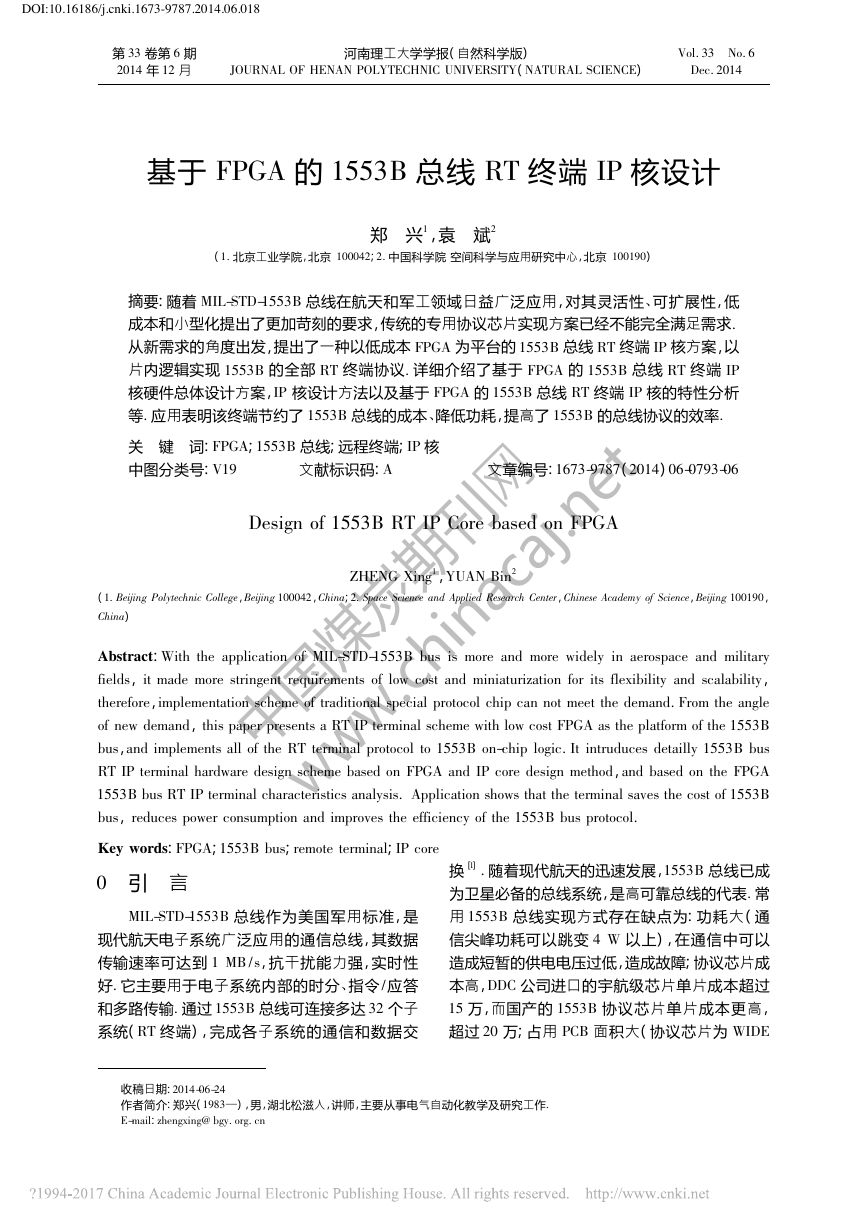

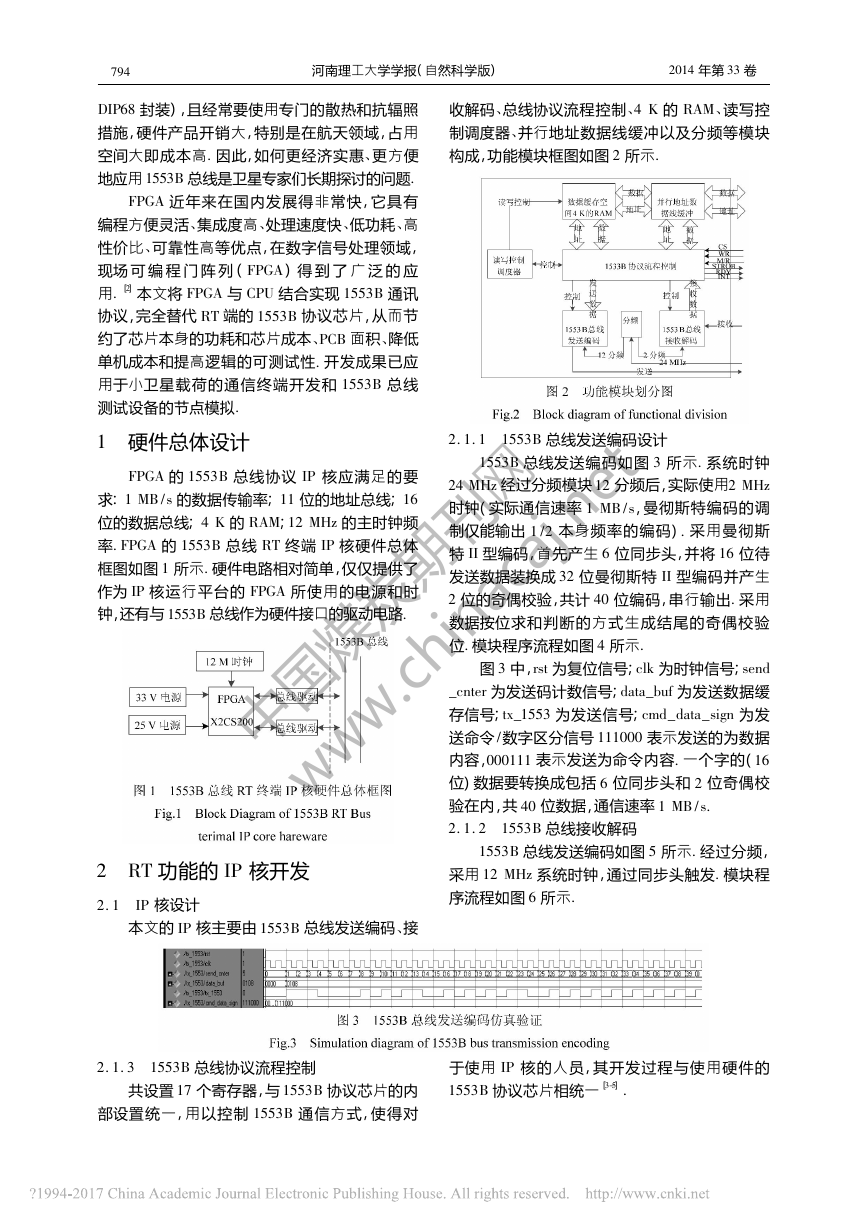

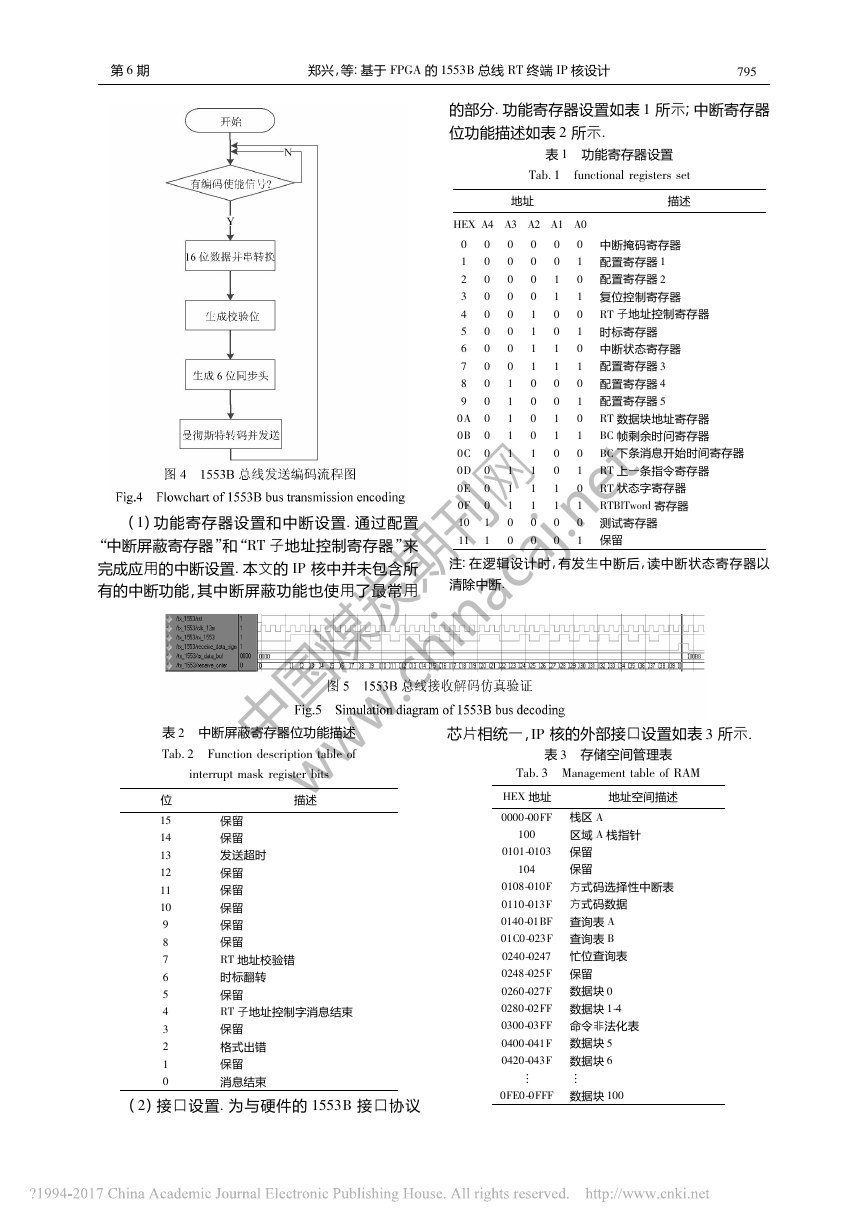

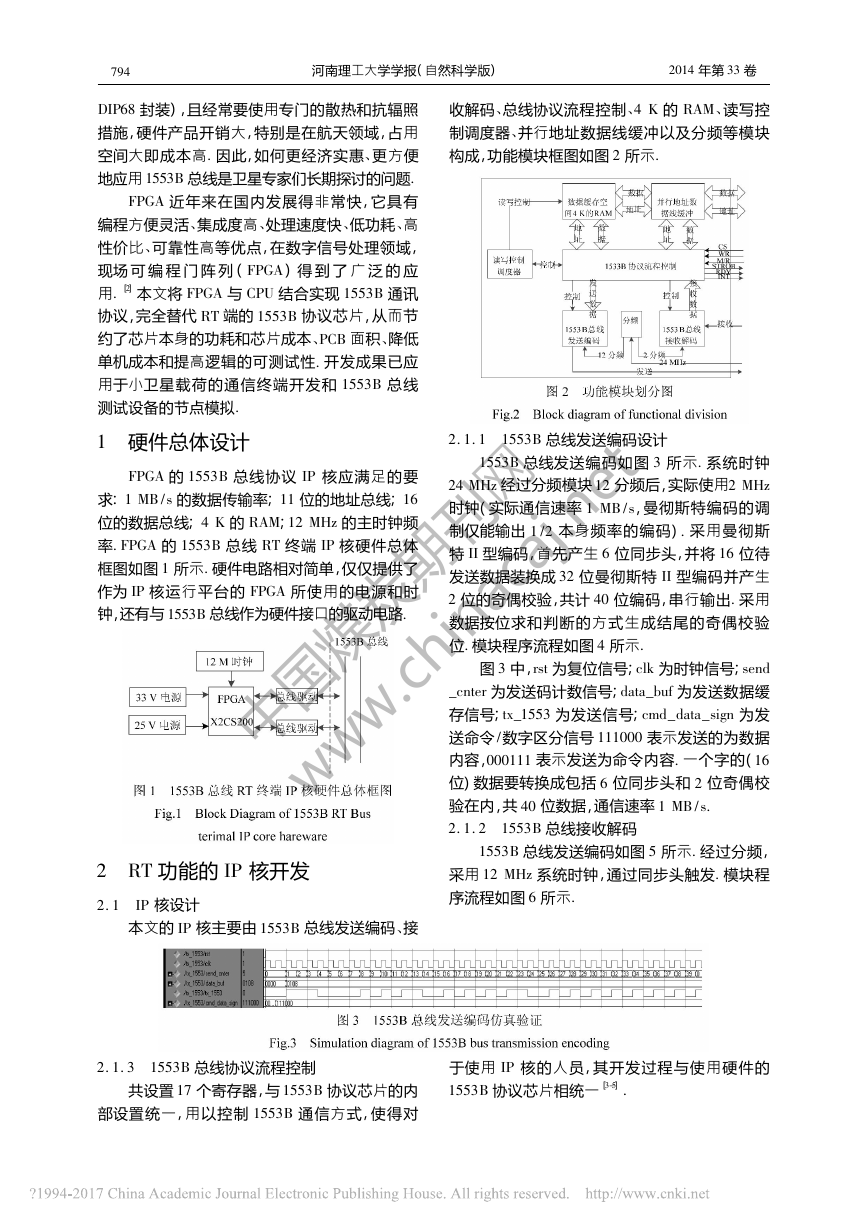

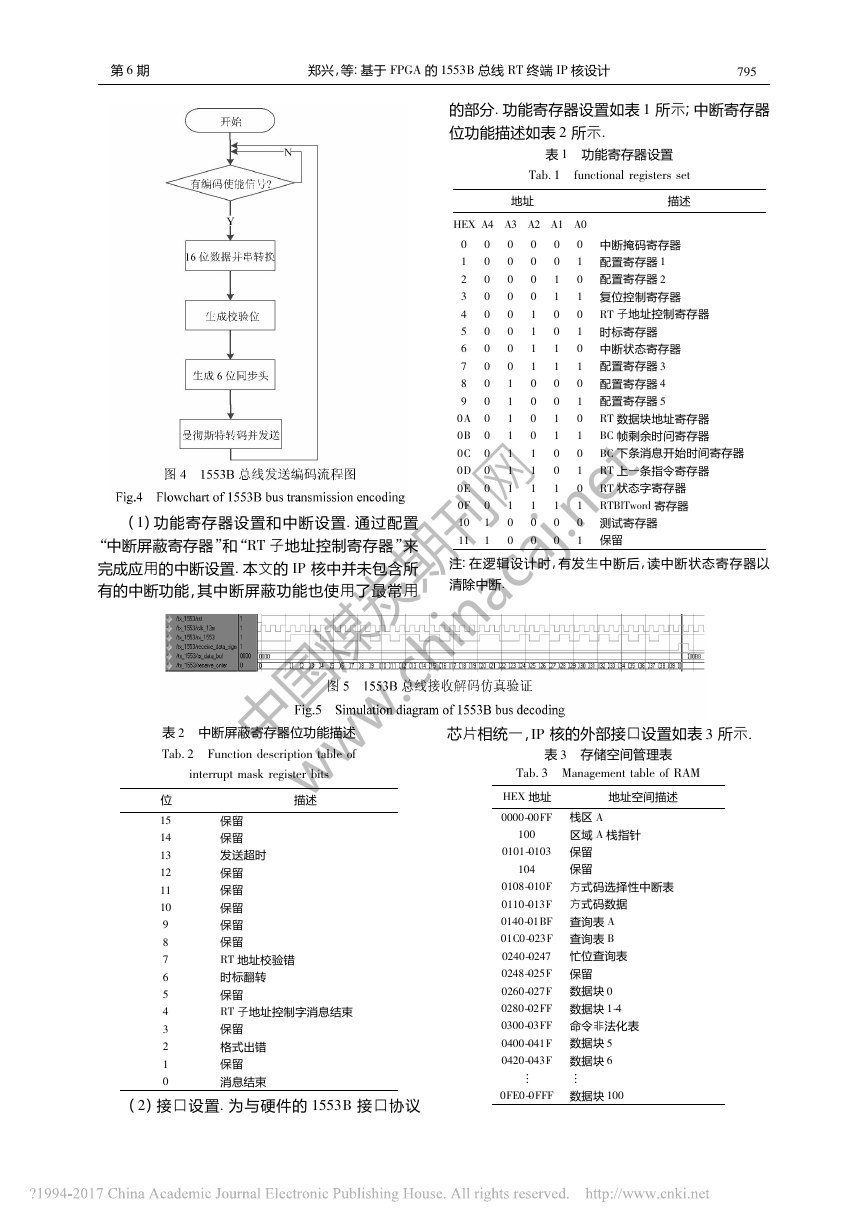

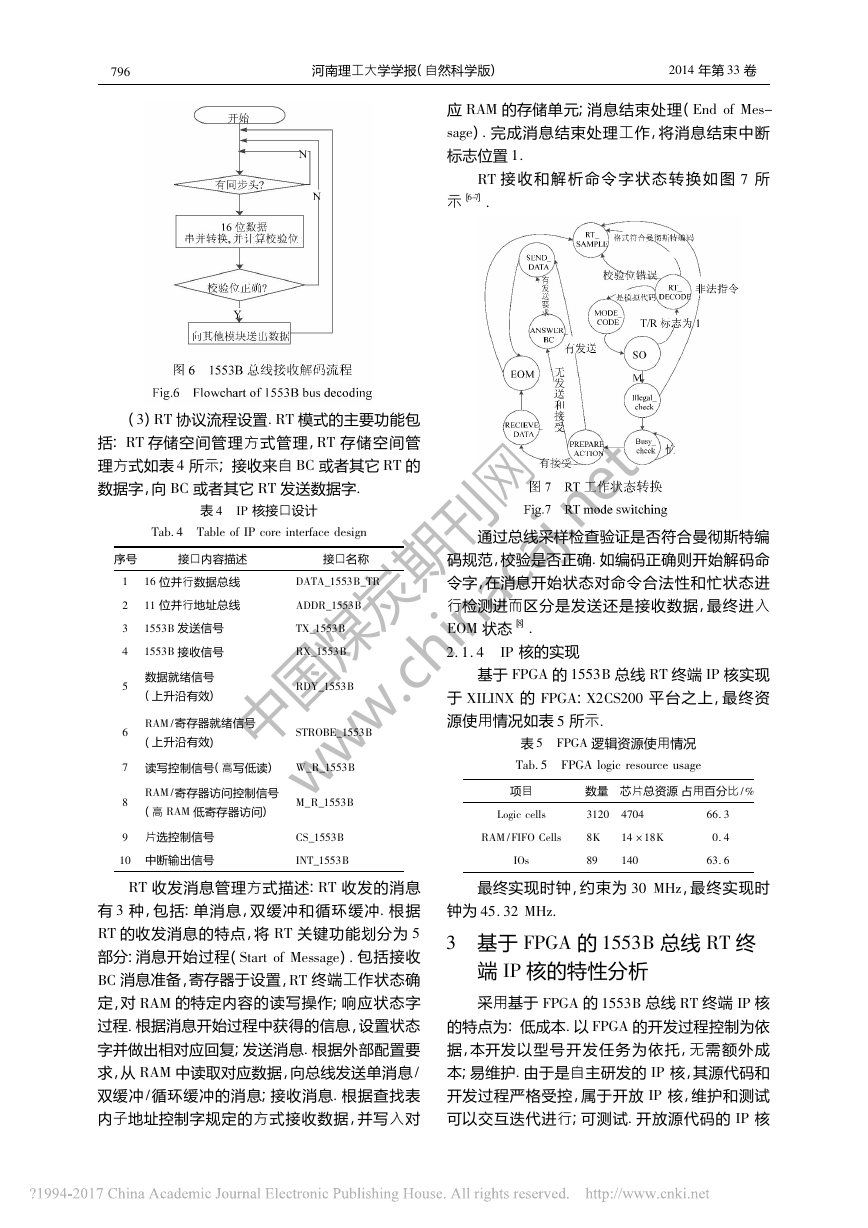

DIP68封装),且经常要使用专门的散热和抗辐照措施,硬件产品开销大,特别是在航天领域,占用空间大即成本高.因此,如何更经济实惠、更方便地应用1553B总线是卫星专家们长期探讨的问题.FPGA近年来在国内发展得非常快,它具有编程方便灵活、集成度高、处理速度快、低功耗、高性价比、可靠性高等优点,在数字信号处理领域,现场可编程门阵列(FPGA)得到了广泛的应用.[2]本文将FPGA与CPU结合实现1553B通讯协议,完全替代RT端的1553B协议芯片,从而节约了芯片本身的功耗和芯片成本、PCB面积、降低单机成本和提高逻辑的可测试性.开发成果已应用于小卫星载荷的通信终端开发和1553B总线测试设备的节点模拟.1硬件总体设计FPGA的1553B总线协议IP核应满足的要求:1MB/s的数据传输率;11位的地址总线;16位的数据总线;4K的RAM;12MHz的主时钟频率.FPGA的1553B总线RT终端IP核硬件总体框图如图1所示.硬件电路相对简单,仅仅提供了作为IP核运行平台的FPGA所使用的电源和时钟,还有与1553B总线作为硬件接口的驱动电路.2RT功能的IP核开发2.1IP核设计本文的IP核主要由1553B总线发送编码、接收解码、总线协议流程控制、4K的RAM、读写控制调度器、并行地址数据线缓冲以及分频等模块构成,功能模块框图如图2所示.2.1.11553B总线发送编码设计1553B总线发送编码如图3所示.系统时钟24MHz经过分频模块12分频后,实际使用2MHz时钟(实际通信速率1MB/s,曼彻斯特编码的调制仅能输出1/2本身频率的编码).采用曼彻斯特II型编码,首先产生6位同步头,并将16位待发送数据装换成32位曼彻斯特II型编码并产生2位的奇偶校验,共计40位编码,串行输出.采用数据按位求和判断的方式生成结尾的奇偶校验位.模块程序流程如图4所示.图3中,rst为复位信号;clk为时钟信号;send_cnter为发送码计数信号;data_buf为发送数据缓存信号;tx_1553为发送信号;cmd_data_sign为发送命令/数字区分信号111000表示发送的为数据内容,000111表示发送为命令内容.一个字的(16位)数据要转换成包括6位同步头和2位奇偶校验在内,共40位数据,通信速率1MB/s.2.1.21553B总线接收解码1553B总线发送编码如图5所示.经过分频,采用12MHz系统时钟,通过同步头触发.模块程序流程如图6所示.2.1.31553B总线协议流程控制共设置17个寄存器,与1553B协议芯片的内部设置统一,用以控制1553B通信方式,使得对于使用IP核的人员,其开发过程与使用硬件的1553B协议芯片相统一[3-5].497河南理工大学学报(自然科学版)2014年第33卷中国煤炭期刊网 www.chinacaj.net�

(1)功能寄存器设置和中断设置.通过配置“中断屏蔽寄存器”和“RT子地址控制寄存器”来完成应用的中断设置.本文的IP核中并未包含所有的中断功能,其中断屏蔽功能也使用了最常用的部分.功能寄存器设置如表1所示;中断寄存器位功能描述如表2所示.表1功能寄存器设置Tab.1functionalregistersset地址描述HEXA4A3A2A1A0000000中断掩码寄存器100001配置寄存器1200010配置寄存器2300011复位控制寄存器400100RT子地址控制寄存器500101时标寄存器600110中断状态寄存器700111配置寄存器3801000配置寄存器4901001配置寄存器50A01010RT数据块地址寄存器0B01011BC帧剩余时问寄存器0C01100BC下条消息开始时间寄存器0D01101RT上一条指令寄存器0E01110RT状态字寄存器0F01111RTBlTword寄存器1010000测试寄存器1110001保留注:在逻辑设计时,有发生中断后,读中断状态寄存器以清除中断.表2中断屏蔽寄存器位功能描述Tab.2Functiondescriptiontableofinterruptmaskregisterbits位描述15保留14保留13发送超时12保留11保留10保留9保留8保留7RT地址校验错6时标翻转5保留4RT子地址控制字消息结束3保留2格式出错1保留0消息结束(2)接口设置.为与硬件的1553B接口协议芯片相统一,IP核的外部接口设置如表3所示.表3存储空间管理表Tab.3ManagementtableofRAMHEX地址地址空间描述0000-00FF栈区A100区域A栈指针0101-0103保留104保留0108-010F方式码选择性中断表0110-013F方式码数据0140-01BF查询表A01C0-023F查询表B0240-0247忙位查询表0248-025F保留0260-027F数据块00280-02FF数据块1-40300-03FF命令非法化表0400-041F数据块50420-043F数据块60FE0-0FFF数据块100597第6期郑兴,等:基于FPGA的1553B总线RT终端IP核设计中国煤炭期刊网 www.chinacaj.net�

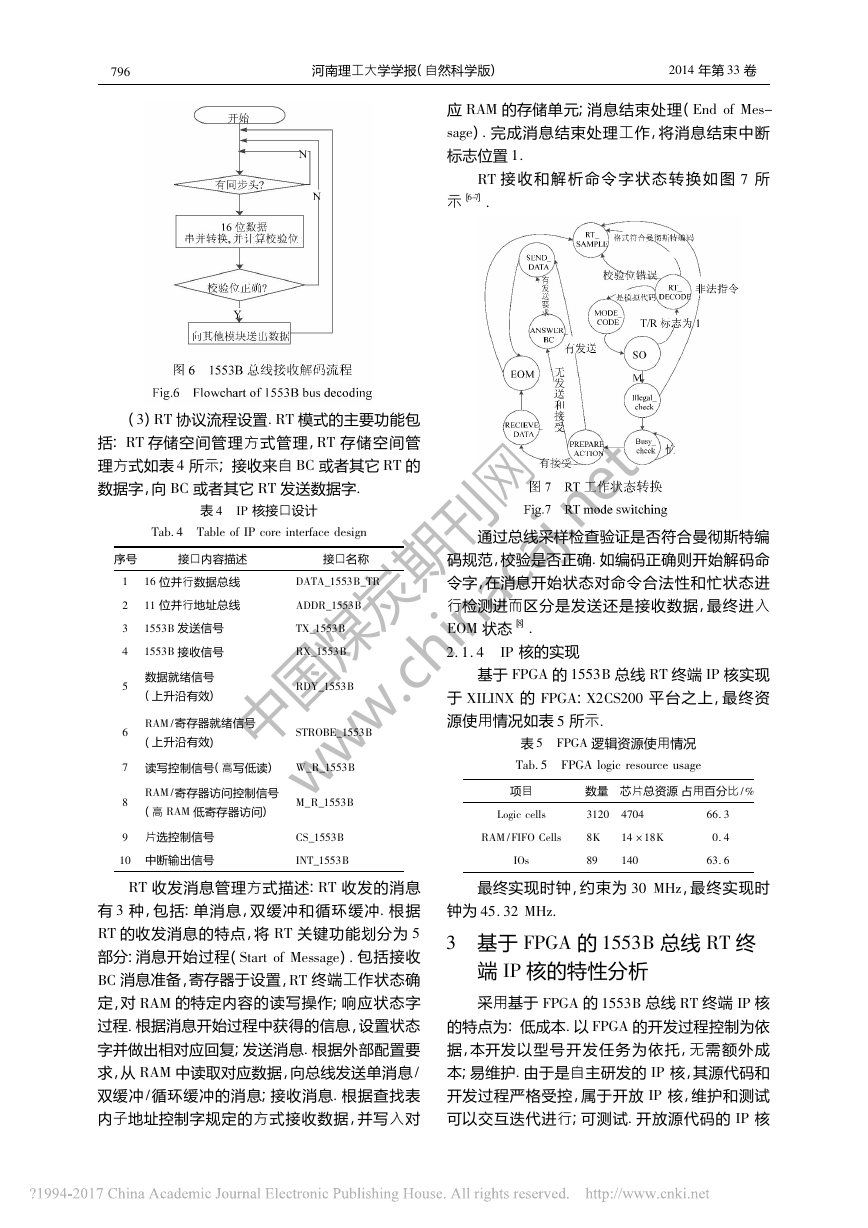

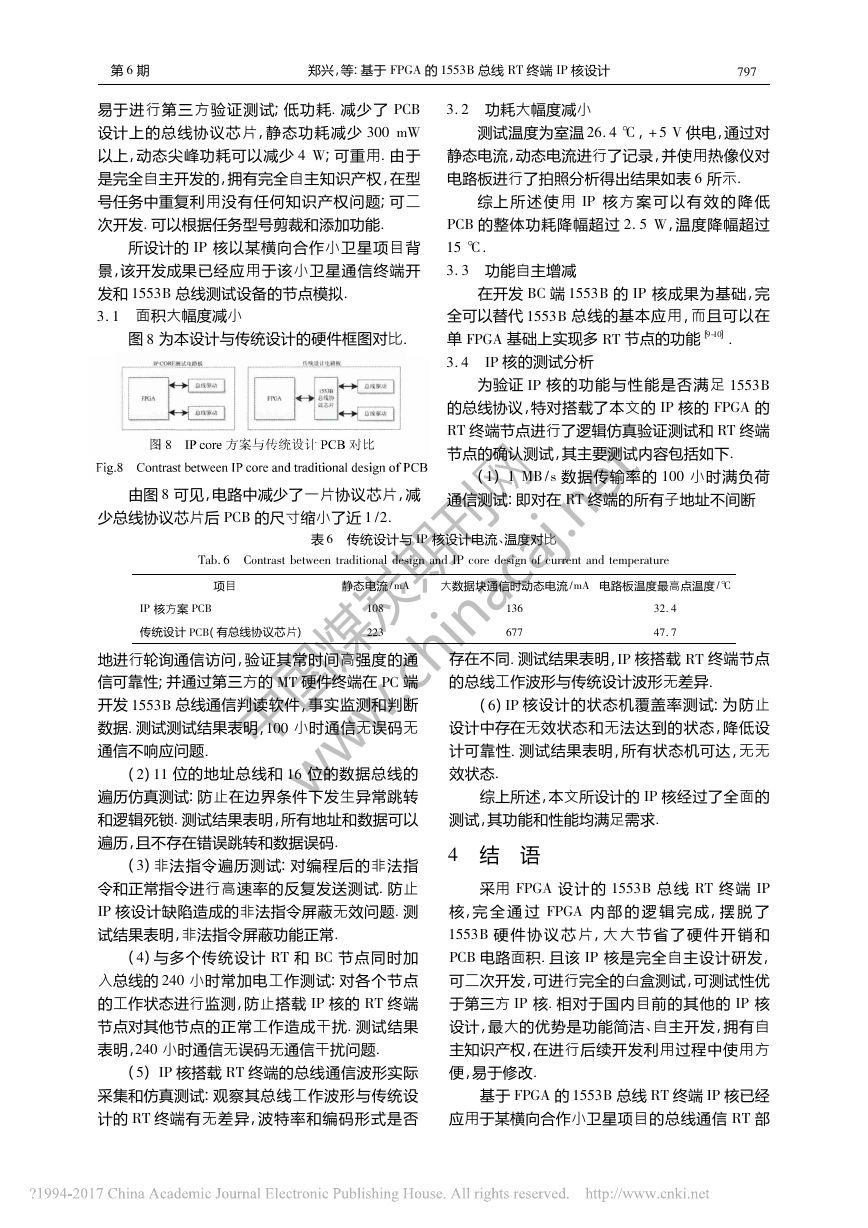

(3)RT协议流程设置.RT模式的主要功能包括:RT存储空间管理方式管理,RT存储空间管理方式如表4所示;接收来自BC或者其它RT的数据字,向BC或者其它RT发送数据字.表4IP核接口设计Tab.4TableofIPcoreinterfacedesign序号接口内容描述接口名称116位并行数据总线DATA_1553B_TR211位并行地址总线ADDR_1553B31553B发送信号TX_1553B41553B接收信号RX_1553B5数据就绪信号(上升沿有效)RDY_1553B6RAM/寄存器就绪信号(上升沿有效)STROBE_1553B7读写控制信号(高写低读)W_R_1553B8RAM/寄存器访问控制信号(高RAM低寄存器访问)M_R_1553B9片选控制信号CS_1553B10中断输出信号INT_1553BRT收发消息管理方式描述:RT收发的消息有3种,包括:单消息,双缓冲和循环缓冲.根据RT的收发消息的特点,将RT关键功能划分为5部分:消息开始过程(StartofMessage).包括接收BC消息准备,寄存器于设置,RT终端工作状态确定,对RAM的特定内容的读写操作;响应状态字过程.根据消息开始过程中获得的信息,设置状态字并做出相对应回复;发送消息.根据外部配置要求,从RAM中读取对应数据,向总线发送单消息/双缓冲/循环缓冲的消息;接收消息.根据查找表内子地址控制字规定的方式接收数据,并写入对应RAM的存储单元;消息结束处理(EndofMes-sage).完成消息结束处理工作,将消息结束中断标志位置1.RT接收和解析命令字状态转换如图7所示[6-7].通过总线采样检查验证是否符合曼彻斯特编码规范,校验是否正确.如编码正确则开始解码命令字,在消息开始状态对命令合法性和忙状态进行检测进而区分是发送还是接收数据,最终进入EOM状态[8].2.1.4IP核的实现基于FPGA的1553B总线RT终端IP核实现于XILINX的FPGA:X2CS200平台之上,最终资源使用情况如表5所示.表5FPGA逻辑资源使用情况Tab.5FPGAlogicresourceusage项目数量芯片总资源占用百分比/%Logiccells3120470466.3RAM/FIFOCells8K14×18K0.4IOs8914063.6最终实现时钟,约束为30MHz,最终实现时钟为45.32MHz.3基于FPGA的1553B总线RT终端IP核的特性分析采用基于FPGA的1553B总线RT终端IP核的特点为:低成本.以FPGA的开发过程控制为依据,本开发以型号开发任务为依托,无需额外成本;易维护.由于是自主研发的IP核,其源代码和开发过程严格受控,属于开放IP核,维护和测试可以交互迭代进行;可测试.开放源代码的IP核697河南理工大学学报(自然科学版)2014年第33卷中国煤炭期刊网 www.chinacaj.net�

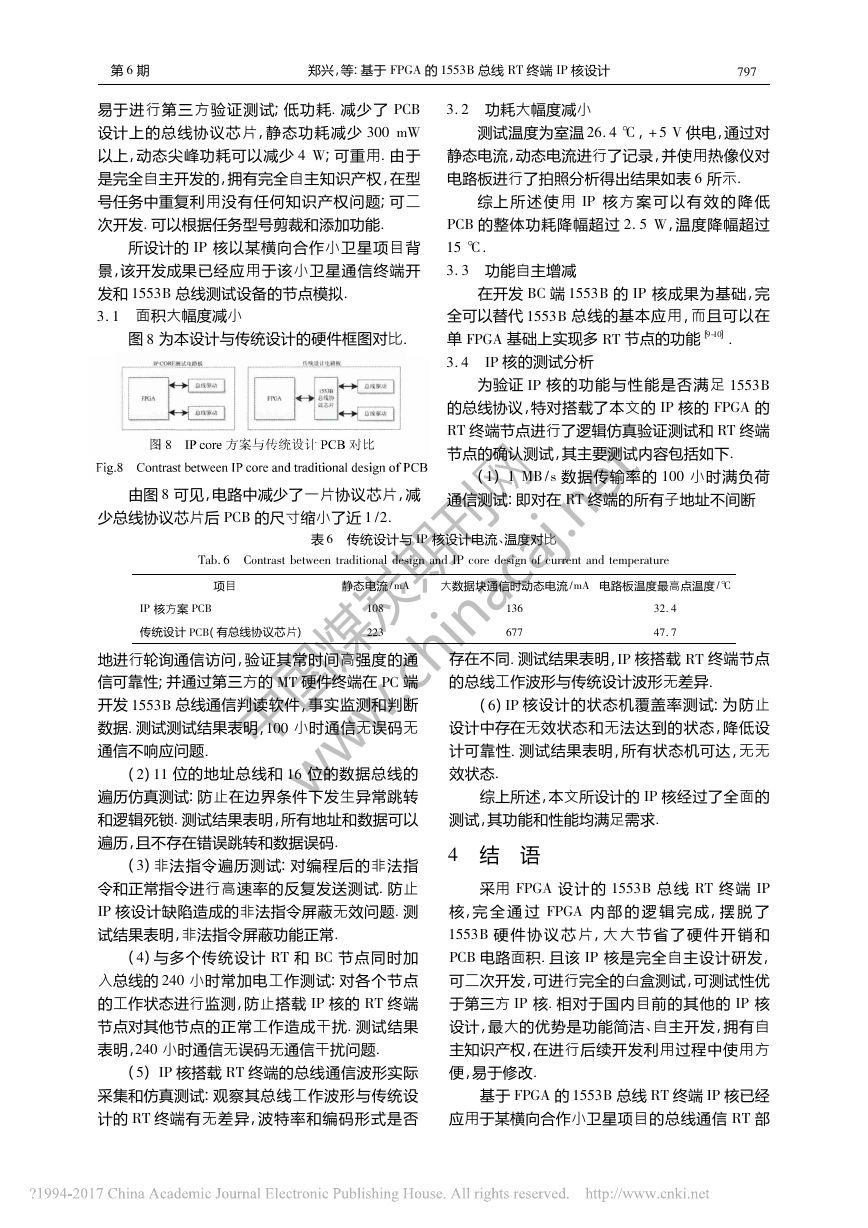

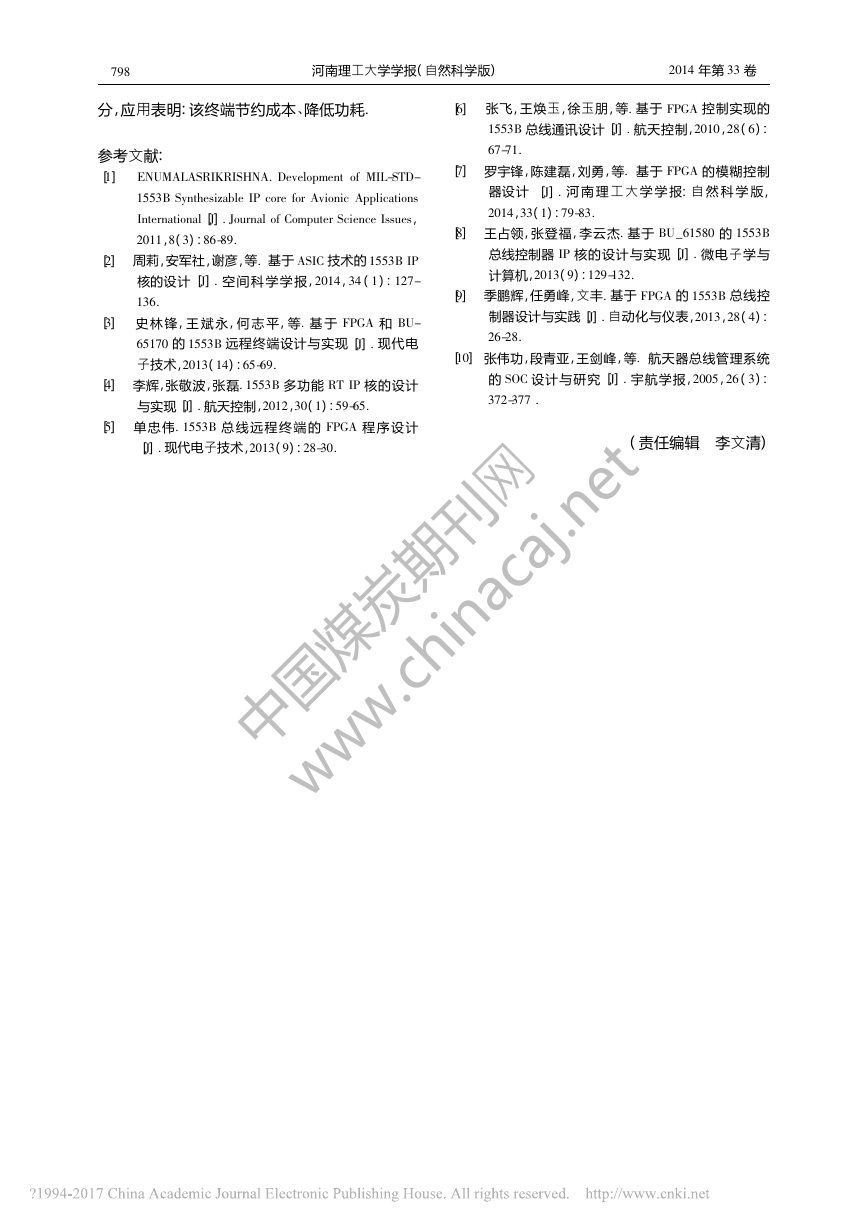

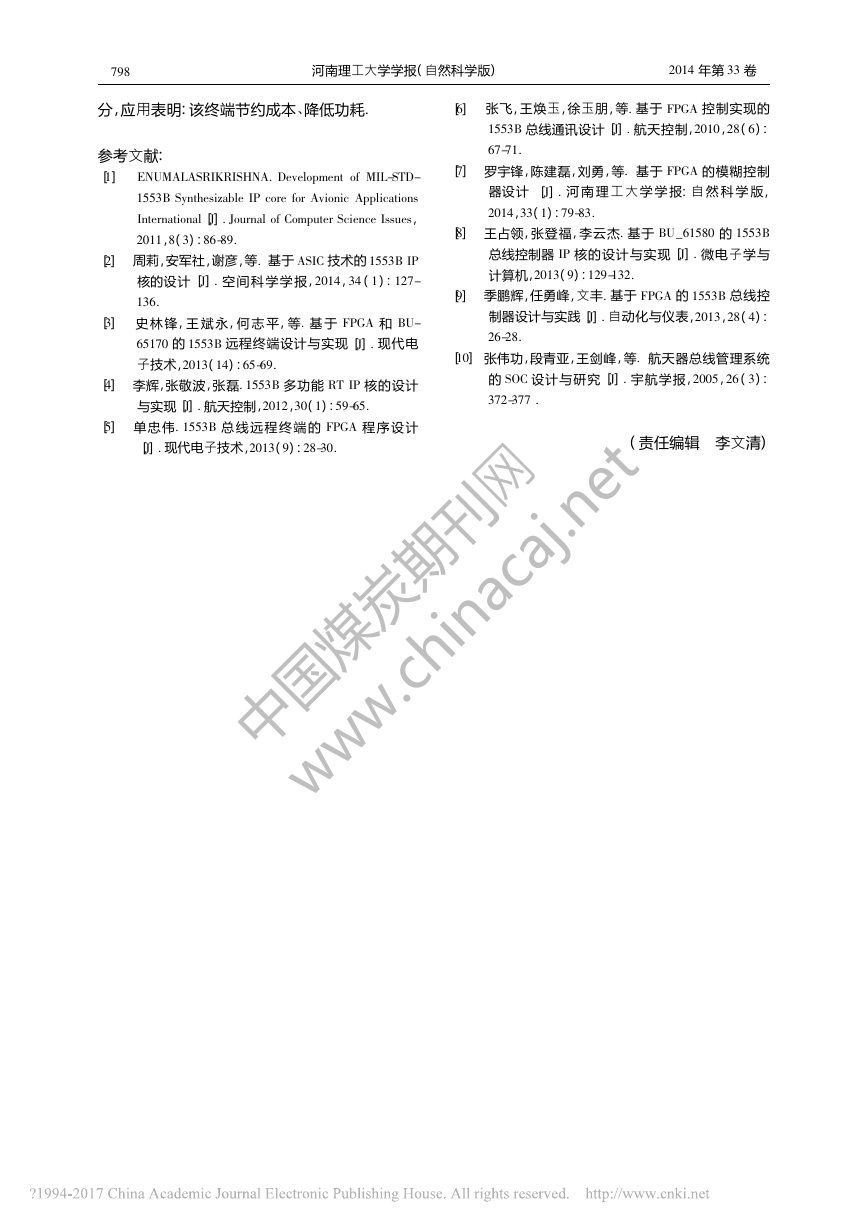

易于进行第三方验证测试;低功耗.减少了PCB设计上的总线协议芯片,静态功耗减少300mW以上,动态尖峰功耗可以减少4W;可重用.由于是完全自主开发的,拥有完全自主知识产权,在型号任务中重复利用没有任何知识产权问题;可二次开发.可以根据任务型号剪裁和添加功能.所设计的IP核以某横向合作小卫星项目背景,该开发成果已经应用于该小卫星通信终端开发和1553B总线测试设备的节点模拟.3.1面积大幅度减小图8为本设计与传统设计的硬件框图对比.由图8可见,电路中减少了一片协议芯片,减少总线协议芯片后PCB的尺寸缩小了近1/2.3.2功耗大幅度减小测试温度为室温26.4℃,+5V供电,通过对静态电流,动态电流进行了记录,并使用热像仪对电路板进行了拍照分析得出结果如表6所示.综上所述使用IP核方案可以有效的降低PCB的整体功耗降幅超过2.5W,温度降幅超过15℃.3.3功能自主增减在开发BC端1553B的IP核成果为基础,完全可以替代1553B总线的基本应用,而且可以在单FPGA基础上实现多RT节点的功能[9-10].3.4IP核的测试分析为验证IP核的功能与性能是否满足1553B的总线协议,特对搭载了本文的IP核的FPGA的RT终端节点进行了逻辑仿真验证测试和RT终端节点的确认测试,其主要测试内容包括如下.(1)1MB/s数据传输率的100小时满负荷通信测试:即对在RT终端的所有子地址不间断表6传统设计与IP核设计电流、温度对比Tab.6ContrastbetweentraditionaldesignandIPcoredesignofcurrentandtemperature项目静态电流/mA大数据块通信时动态电流/mA电路板温度最高点温度/℃IP核方案PCB10813632.4传统设计PCB(有总线协议芯片)22367747.7地进行轮询通信访问,验证其常时间高强度的通信可靠性;并通过第三方的MT硬件终端在PC端开发1553B总线通信判读软件,事实监测和判断数据.测试测试结果表明,100小时通信无误码无通信不响应问题.(2)11位的地址总线和16位的数据总线的遍历仿真测试:防止在边界条件下发生异常跳转和逻辑死锁.测试结果表明,所有地址和数据可以遍历,且不存在错误跳转和数据误码.(3)非法指令遍历测试:对编程后的非法指令和正常指令进行高速率的反复发送测试.防止IP核设计缺陷造成的非法指令屏蔽无效问题.测试结果表明,非法指令屏蔽功能正常.(4)与多个传统设计RT和BC节点同时加入总线的240小时常加电工作测试:对各个节点的工作状态进行监测,防止搭载IP核的RT终端节点对其他节点的正常工作造成干扰.测试结果表明,240小时通信无误码无通信干扰问题.(5)IP核搭载RT终端的总线通信波形实际采集和仿真测试:观察其总线工作波形与传统设计的RT终端有无差异,波特率和编码形式是否存在不同.测试结果表明,IP核搭载RT终端节点的总线工作波形与传统设计波形无差异.(6)IP核设计的状态机覆盖率测试:为防止设计中存在无效状态和无法达到的状态,降低设计可靠性.测试结果表明,所有状态机可达,无无效状态.综上所述,本文所设计的IP核经过了全面的测试,其功能和性能均满足需求.4结语采用FPGA设计的1553B总线RT终端IP核,完全通过FPGA内部的逻辑完成,摆脱了1553B硬件协议芯片,大大节省了硬件开销和PCB电路面积.且该IP核是完全自主设计研发,可二次开发,可进行完全的白盒测试,可测试性优于第三方IP核.相对于国内目前的其他的IP核设计,最大的优势是功能简洁、自主开发,拥有自主知识产权,在进行后续开发利用过程中使用方便,易于修改.基于FPGA的1553B总线RT终端IP核已经应用于某横向合作小卫星项目的总线通信RT部797第6期郑兴,等:基于FPGA的1553B总线RT终端IP核设计中国煤炭期刊网 www.chinacaj.net�

分,应用表明:该终端节约成本、降低功耗.参考文献:[1]ENUMALASRIKRISHNA.DevelopmentofMIL-STD-1553BSynthesizableIPcoreforAvionicApplicationsInternational[J].JournalofComputerScienceIssues,2011,8(3):86-89.[2]周莉,安军社,谢彦,等.基于ASIC技术的1553BIP核的设计[J].空间科学学报,2014,34(1):127-136.[3]史林锋,王斌永,何志平,等.基于FPGA和BU-65170的1553B远程终端设计与实现[J].现代电子技术,2013(14):65-69.[4]李辉,张敬波,张磊.1553B多功能RTIP核的设计与实现[J].航天控制,2012,30(1):59-65.[5]单忠伟.1553B总线远程终端的FPGA程序设计[J].现代电子技术,2013(9):28-30.[6]张飞,王焕玉,徐玉朋,等.基于FPGA控制实现的1553B总线通讯设计[J].航天控制,2010,28(6):67-71.[7]罗宇锋,陈建磊,刘勇,等.基于FPGA的模糊控制器设计[J].河南理工大学学报:自然科学版,2014,33(1):79-83.[8]王占领,张登福,李云杰.基于BU_61580的1553B总线控制器IP核的设计与实现[J].微电子学与计算机,2013(9):129-132.[9]季鹏辉,任勇峰,文丰.基于FPGA的1553B总线控制器设计与实践[J].自动化与仪表,2013,28(4):26-28.[10]张伟功,段青亚,王剑峰,等.航天器总线管理系统的SOC设计与研究[J].宇航学报,2005,26(3):372-377.(责任编辑李文清)897河南理工大学学报(自然科学版)2014年第33卷中国煤炭期刊网 www.chinacaj.net�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc