邮电与信息工程学院

课程设计说明书

课题名称:

电子设计自动化(EDA)课程设计

学生学号:

专业班级:

6402040105

06 自动化 01

学生姓名:

高 军

学生成绩:

指导教师:

邹连英

课题工作时间:

2009.6.8 至 2009.6.19

1

�

目录

一、设计题目和要求-----------------------------------------------------------------2

二、设计思路--------------------------------------------------------------------------2

三、单元模块设计--------------------------------------------------------------------3

--------------------------------------------------------------------------------------------8

3.1、FENPIN 模块设计-----------------------------------------------------(3,4)

3.2、FIRST 模块设计------------------------------------------------------(4,5)

3.3、JIANJISHU 模块设计------------------------------------------------(5,6)

3.4、CHOICE 和 VIEW 模块设计------------------------------------------(7,8)

四、硬件实验---------------------------------------------------------------------------8

五、心得体会---------------------------------------------------------------------------9

附页:程序代码------------------------------------------------------------------------10

---------------------------------------------------------------------------------------------17

2

�

一、设计题目和要求

设计题目为:微波炉定时控制器

要求:1、复位开关:

2、 启动开关:

3、 烹调时间设置:

4、 烹调时间显示:

5、 七段码测试:

6、 启动输出:

7、 按 TEST 键可以测试七段码管,显示为“8888”;

8、 设定时间后,按启动键开始烹调,同时七段码显示剩余时间,时间为 0

时,显示烹调完成信息“CDEF”

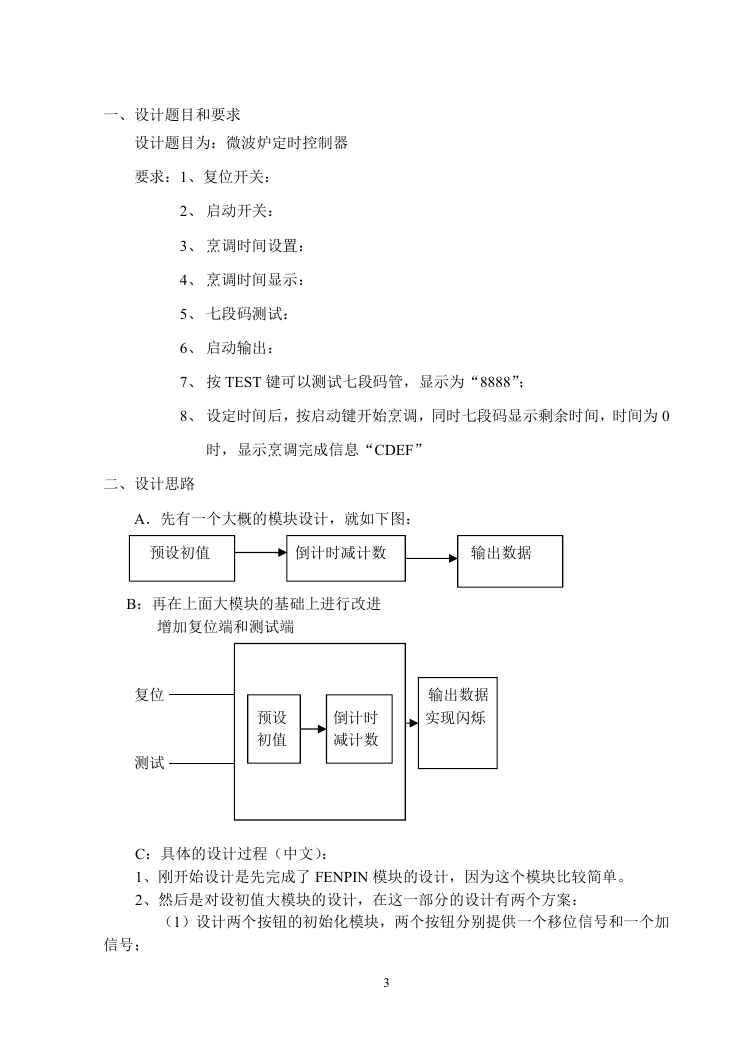

二、设计思路

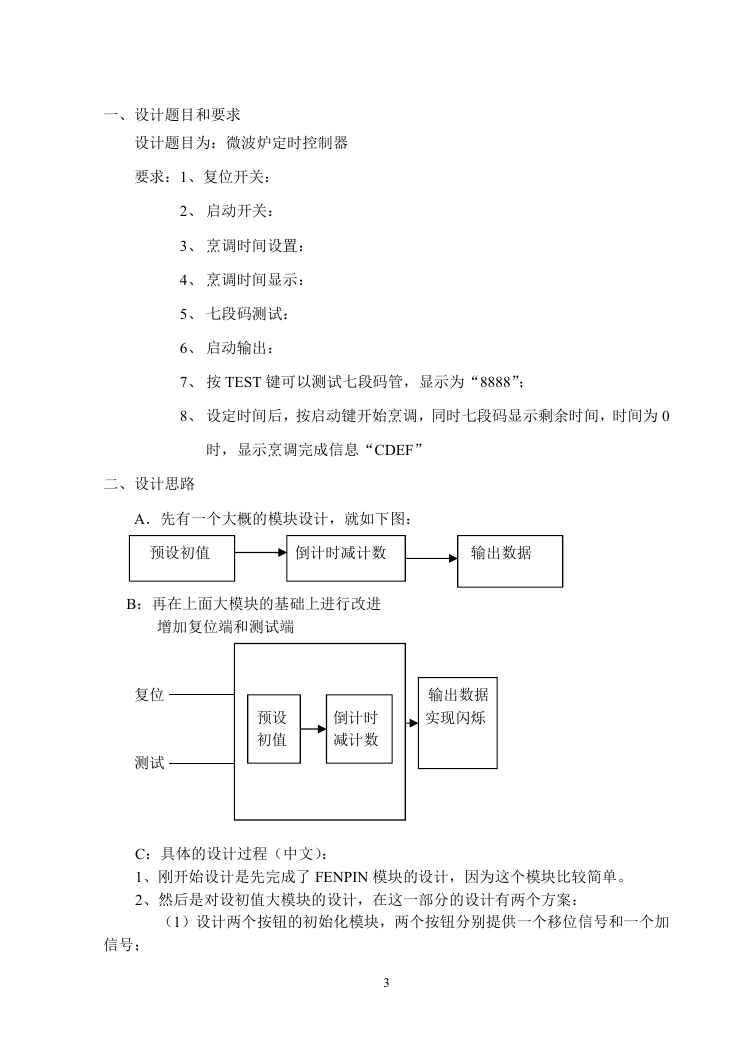

A.先有一个大概的模块设计,就如下图:

预设初值

倒计时减计数

输出数据

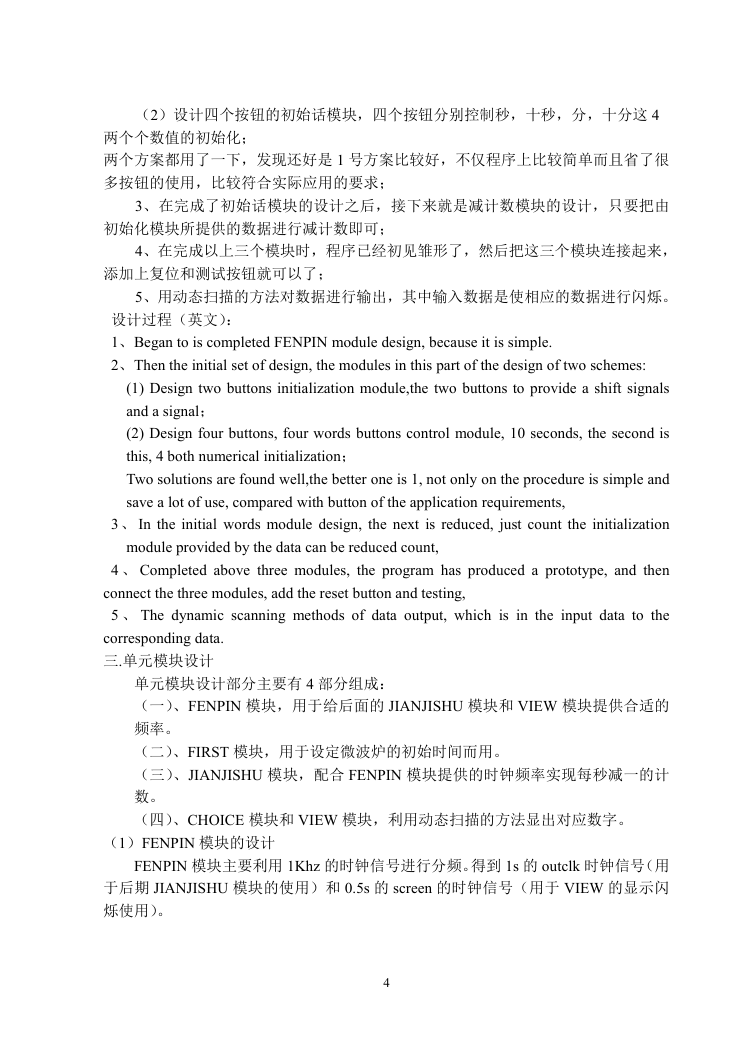

B:再在上面大模块的基础上进行改进

增加复位端和测试端

复位

测试

预设

初值

倒计时

减计数

输出数据

实现闪烁

C:具体的设计过程(中文):

1、刚开始设计是先完成了 FENPIN 模块的设计,因为这个模块比较简单。

2、然后是对设初值大模块的设计,在这一部分的设计有两个方案:

(1)设计两个按钮的初始化模块,两个按钮分别提供一个移位信号和一个加

信号;

3

�

(2)设计四个按钮的初始话模块,四个按钮分别控制秒,十秒,分,十分这 4

两个个数值的初始化;

两个方案都用了一下,发现还好是 1 号方案比较好,不仅程序上比较简单而且省了很

多按钮的使用,比较符合实际应用的要求;

3、在完成了初始话模块的设计之后,接下来就是减计数模块的设计,只要把由

初始化模块所提供的数据进行减计数即可;

4、在完成以上三个模块时,程序已经初见雏形了,然后把这三个模块连接起来,

添加上复位和测试按钮就可以了;

5、用动态扫描的方法对数据进行输出,其中输入数据是使相应的数据进行闪烁。

设计过程(英文):

1、Began to is completed FENPIN module design, because it is simple.

2、Then the initial set of design, the modules in this part of the design of two schemes:

(1) Design two buttons initialization module,the two buttons to provide a shift signals

and a signal;

(2) Design four buttons, four words buttons control module, 10 seconds, the second is

this, 4 both numerical initialization;

Two solutions are found well,the better one is 1, not only on the procedure is simple and

save a lot of use, compared with button of the application requirements,

3 、 In the initial words module design, the next is reduced, just count the initialization

module provided by the data can be reduced count,

4 、 Completed above three modules, the program has produced a prototype, and then

connect the three modules, add the reset button and testing,

5 、 The dynamic scanning methods of data output, which is in the input data to the

corresponding data.

三.单元模块设计

单元模块设计部分主要有 4 部分组成:

(一)、FENPIN 模块,用于给后面的 JIANJISHU 模块和 VIEW 模块提供合适的

频率。

(二)、FIRST 模块,用于设定微波炉的初始时间而用。

(三)、JIANJISHU 模块,配合 FENPIN 模块提供的时钟频率实现每秒减一的计

数。

(四)、CHOICE 模块和 VIEW 模块,利用动态扫描的方法显出对应数字。

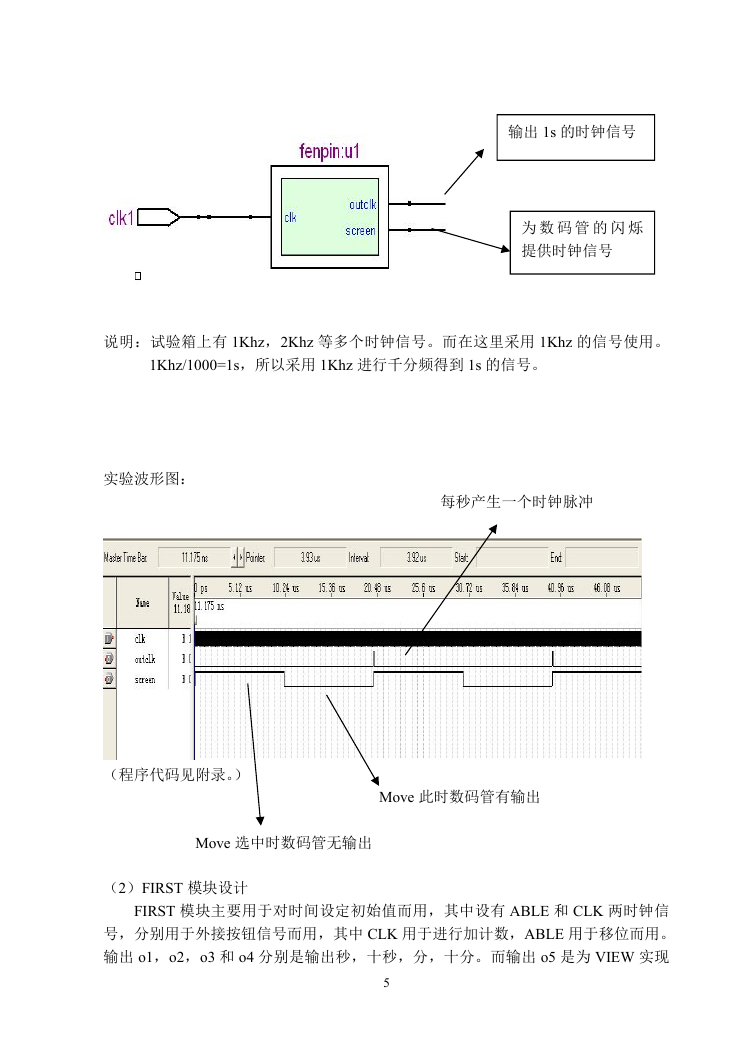

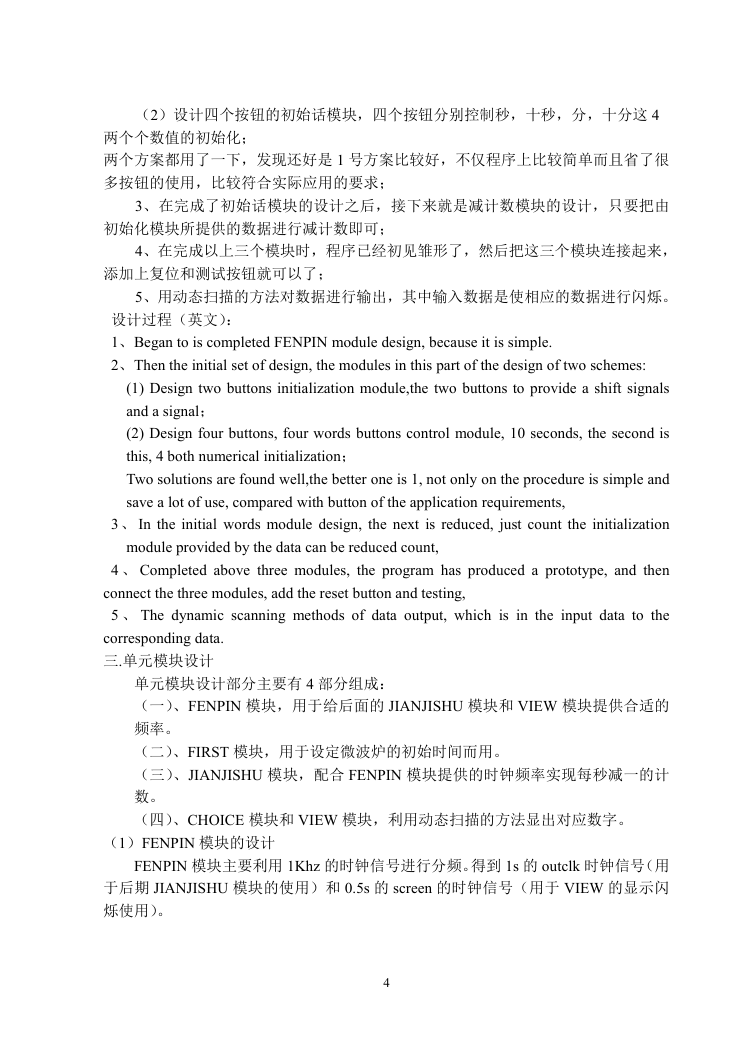

(1)FENPIN 模块的设计

FENPIN 模块主要利用 1Khz 的时钟信号进行分频。得到 1s 的 outclk 时钟信号(用

于后期 JIANJISHU 模块的使用)和 0.5s 的 screen 的时钟信号(用于 VIEW 的显示闪

烁使用)。

4

�

输出 1s 的时钟信号

为 数 码 管 的 闪 烁

提供时钟信号

说明:试验箱上有 1Khz,2Khz 等多个时钟信号。而在这里采用 1Khz 的信号使用。

1Khz/1000=1s,所以采用 1Khz 进行千分频得到 1s 的信号。

实验波形图:

每秒产生一个时钟脉冲

(程序代码见附录。)

Move 此时数码管有输出

Move 选中时数码管无输出

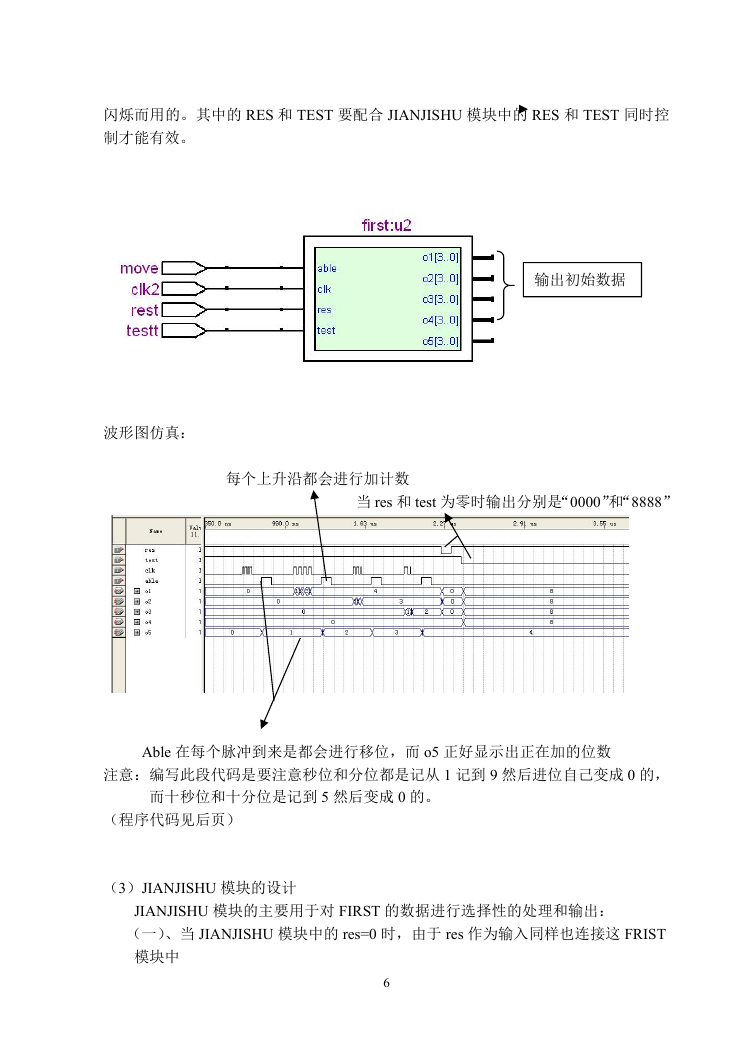

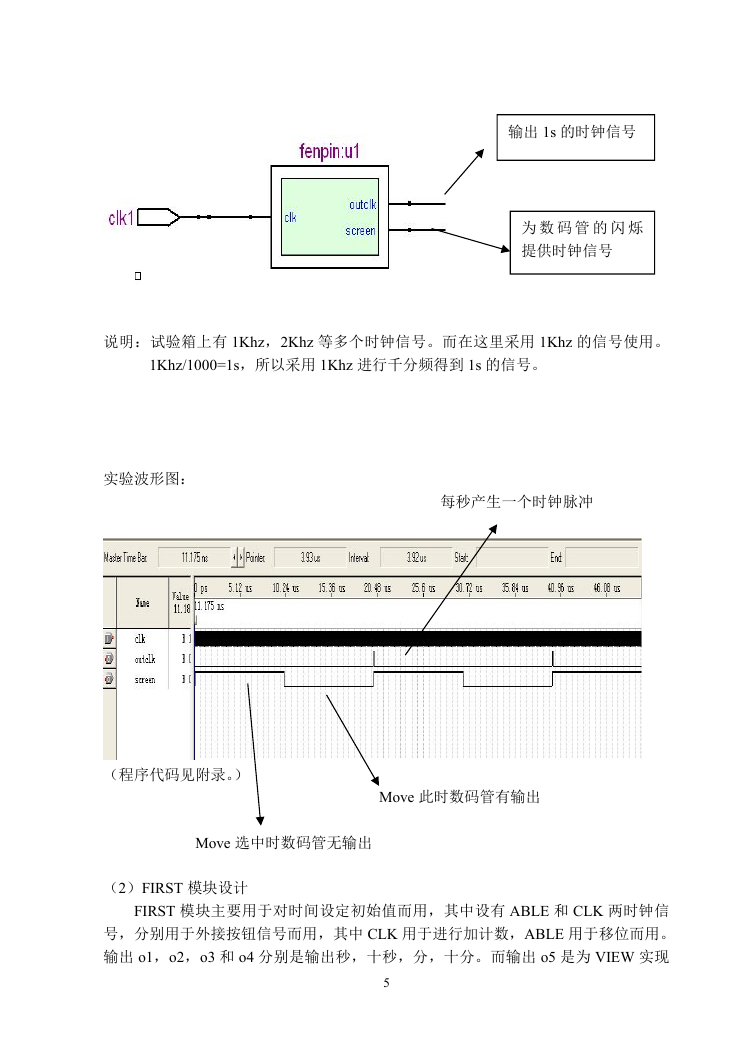

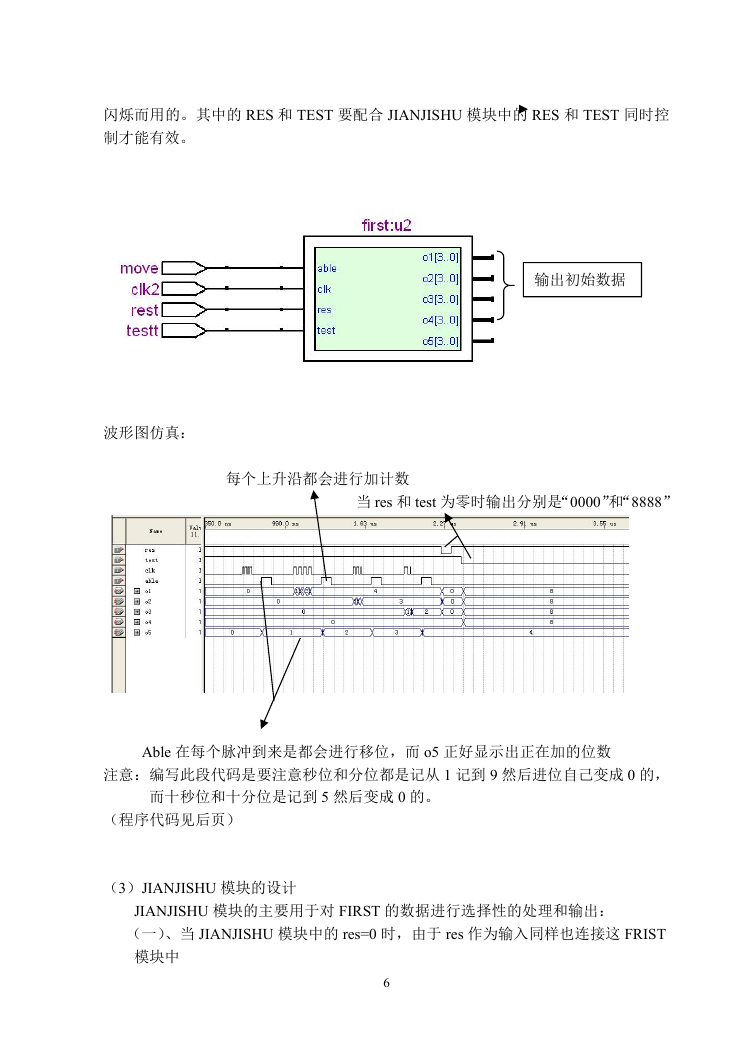

(2)FIRST 模块设计

FIRST 模块主要用于对时间设定初始值而用,其中设有 ABLE 和 CLK 两时钟信

号,分别用于外接按钮信号而用,其中 CLK 用于进行加计数,ABLE 用于移位而用。

输出 o1,o2,o3 和 o4 分别是输出秒,十秒,分,十分。而输出 o5 是为 VIEW 实现

5

�

闪烁而用的。其中的 RES 和 TEST 要配合 JIANJISHU 模块中的 RES 和 TEST 同时控

制才能有效。

输出初始数据

波形图仿真:

每个上升沿都会进行加计数

当 res 和 test 为零时输出分别是“0000”和“8888”

Able 在每个脉冲到来是都会进行移位,而 o5 正好显示出正在加的位数

注意:编写此段代码是要注意秒位和分位都是记从 1 记到 9 然后进位自己变成 0 的,

而十秒位和十分位是记到 5 然后变成 0 的。

(程序代码见后页)

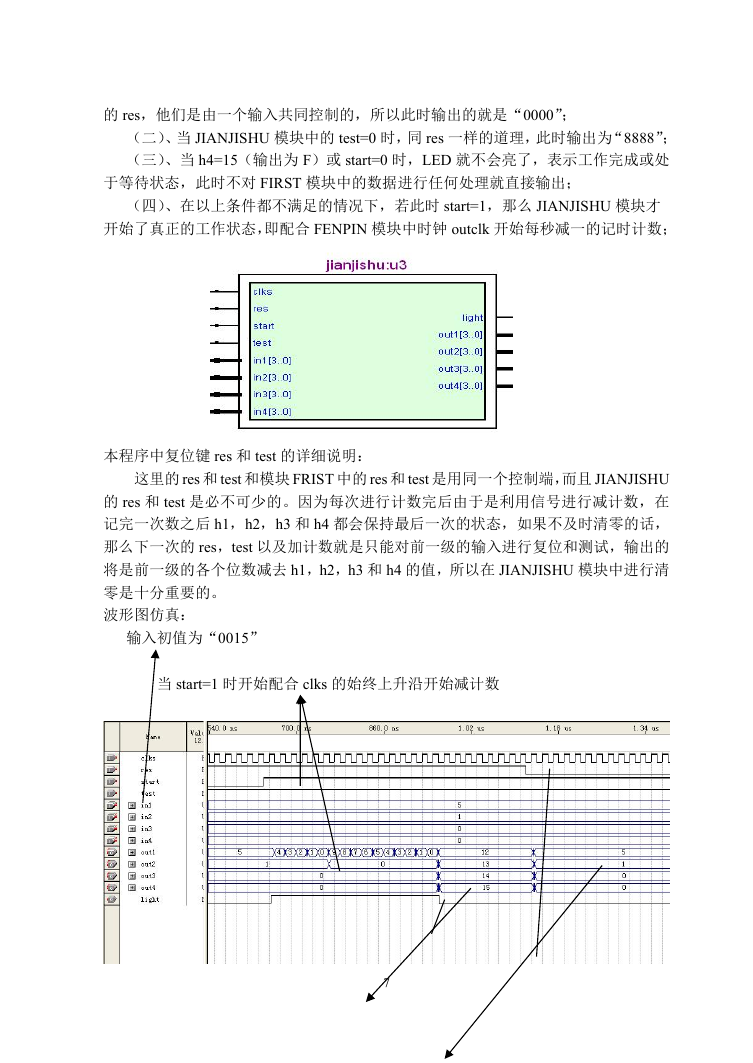

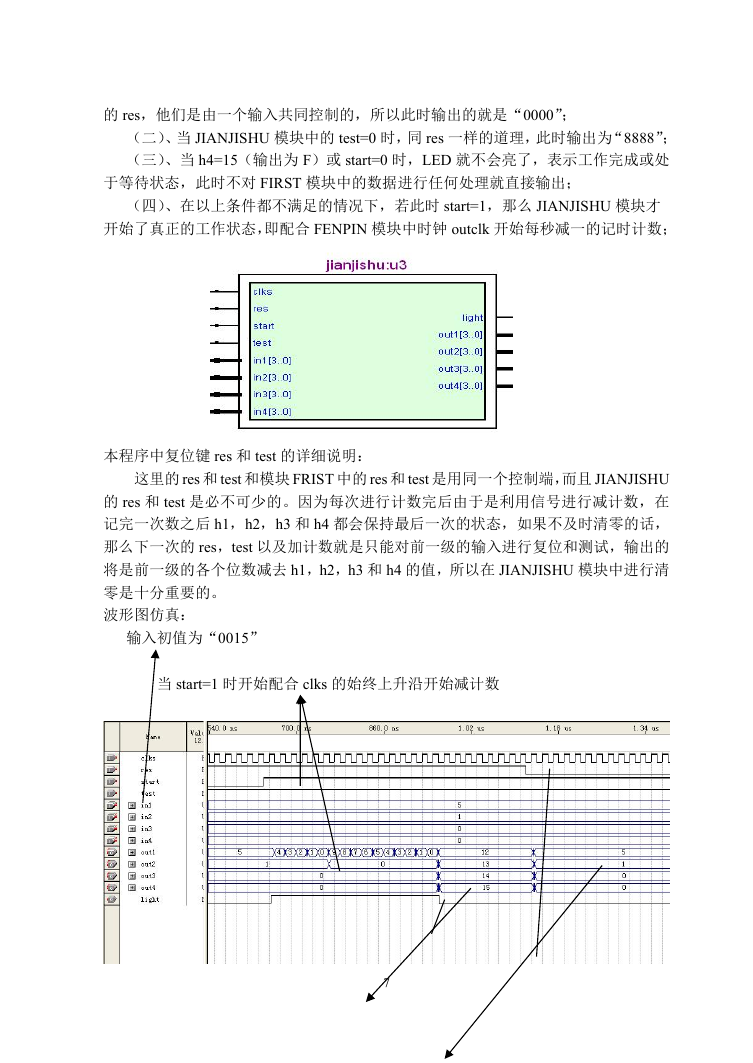

(3)JIANJISHU 模块的设计

JIANJISHU 模块的主要用于对 FIRST 的数据进行选择性的处理和输出:

(一)、当 JIANJISHU 模块中的 res=0 时,由于 res 作为输入同样也连接这 FRIST

模块中

6

�

的 res,他们是由一个输入共同控制的,所以此时输出的就是“0000”;

(二)、当 JIANJISHU 模块中的 test=0 时,同 res 一样的道理,此时输出为“8888”;

(三)、当 h4=15(输出为 F)或 start=0 时,LED 就不会亮了,表示工作完成或处

于等待状态,此时不对 FIRST 模块中的数据进行任何处理就直接输出;

(四)、在以上条件都不满足的情况下,若此时 start=1,那么 JIANJISHU 模块才

开始了真正的工作状态,即配合 FENPIN 模块中时钟 outclk 开始每秒减一的记时计数;

本程序中复位键 res 和 test 的详细说明:

这里的 res 和 test 和模块 FRIST 中的 res 和 test 是用同一个控制端,而且 JIANJISHU

的 res 和 test 是必不可少的。因为每次进行计数完后由于是利用信号进行减计数,在

记完一次数之后 h1,h2,h3 和 h4 都会保持最后一次的状态,如果不及时清零的话,

那么下一次的 res,test 以及加计数就是只能对前一级的输入进行复位和测试,输出的

将是前一级的各个位数减去 h1,h2,h3 和 h4 的值,所以在 JIANJISHU 模块中进行清

零是十分重要的。

波形图仿真:

输入初值为“0015”

当 start=1 时开始配合 clks 的始终上升沿开始减计数

7

�

在各位都记到 0 时,就数码管就会显示 “FEDC”同时 LED 熄灭

这就是上次提到的复位是清零了所有的中间信号,这样输出为 FIRST 中提供原始数据

(程序代码见后页)

(4)CHOICE 模块和 VIEW 模块

CHOICE 模块和 VIEW 模块必须放在一起进行使用,CHOICE 模块是进行数据选

则而使用的,VIEW 模块是用于在相应的位进行输出对应的数,两者和起来就是一个

动态扫描的过程。

说明:这里的 clk 时钟信号是使用和 FENPIN 模块中一样的时钟信号(1Khz),因为人

的眼睛对时间的分辨为 20 个微秒,用 1Khz 的信号完全能满足这样的要求;要

注意 CHOICE 有两个输出,o2 显然输出的是对应的数据信号,而 o1 要输出的是

一个位选信号,是为下一个模块 VIEW 显示而用。

A:CHOICE 模块;

B:VIEW 模块;

说明:f1 是接受位信号用的,f2 是接受数据而用的。

详细说明一下 screen 和 able 的作用:

Screen 是有 FENPIN 模块通过对时钟信号分频得到的,当在模块 FRIST 选中某一

进行加数初始化是,VIEW 就可以在时钟 screen 在为 1 是正常输出 able 所指的那位,

当 screen 为 0 时,able 所指的那位不能对应输出,这样就能达到让相应的数码管闪烁

8

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc