8

7

6

5

4

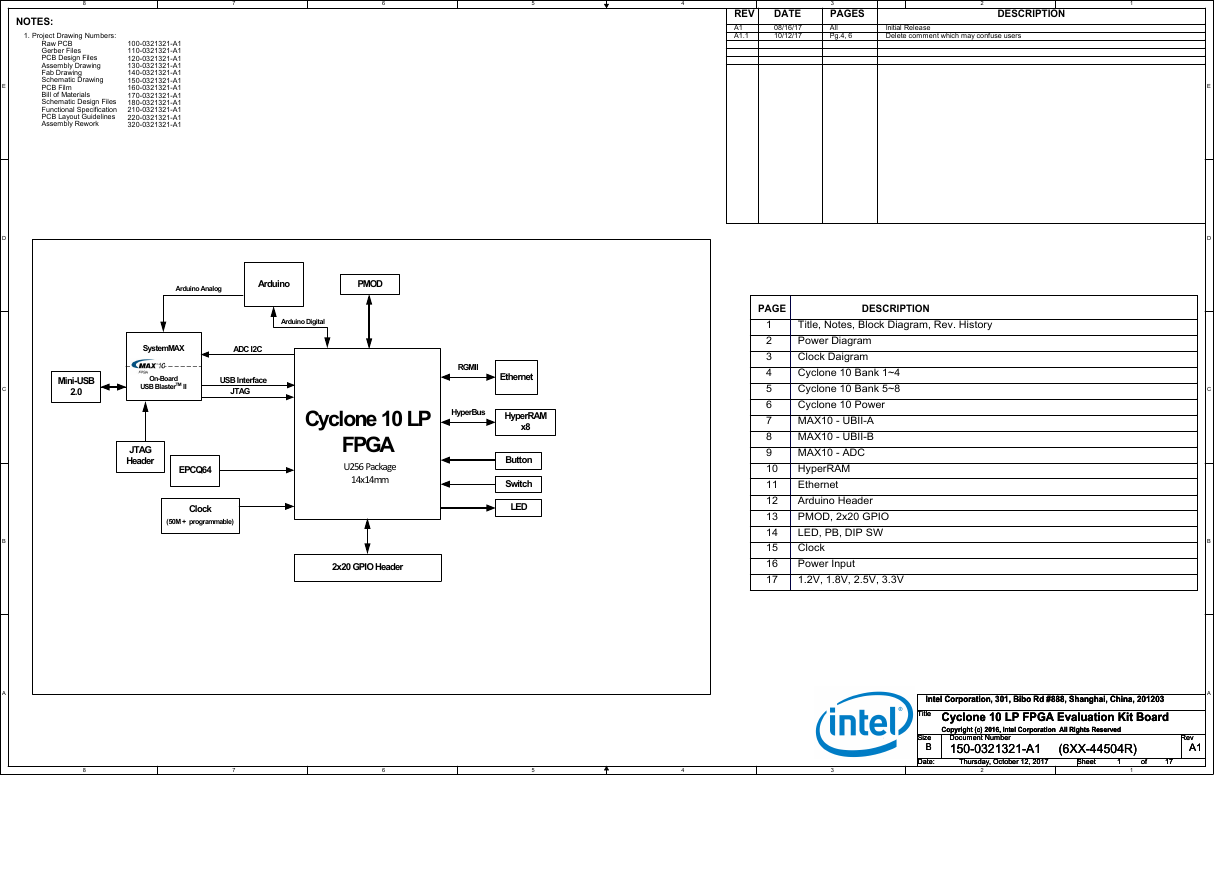

NOTES:

1. Project Drawing Numbers:

Raw PCB

Gerber Files

PCB Design Files

Assembly Drawing

Fab Drawing

Schematic Drawing

PCB Film

Bill of Materials

Schematic Design Files

Functional Specification

PCB Layout Guidelines

Assembly Rework

100-0321321-A1

110-0321321-A1

120-0321321-A1

130-0321321-A1

140-0321321-A1

150-0321321-A1

160-0321321-A1

170-0321321-A1

180-0321321-A1

210-0321321-A1

220-0321321-A1

320-0321321-A1

REV

A1

A1.1

DATE

08/16/17

10/12/17

3

PAGES

All

Pg.4, 6

2

DESCRIPTION

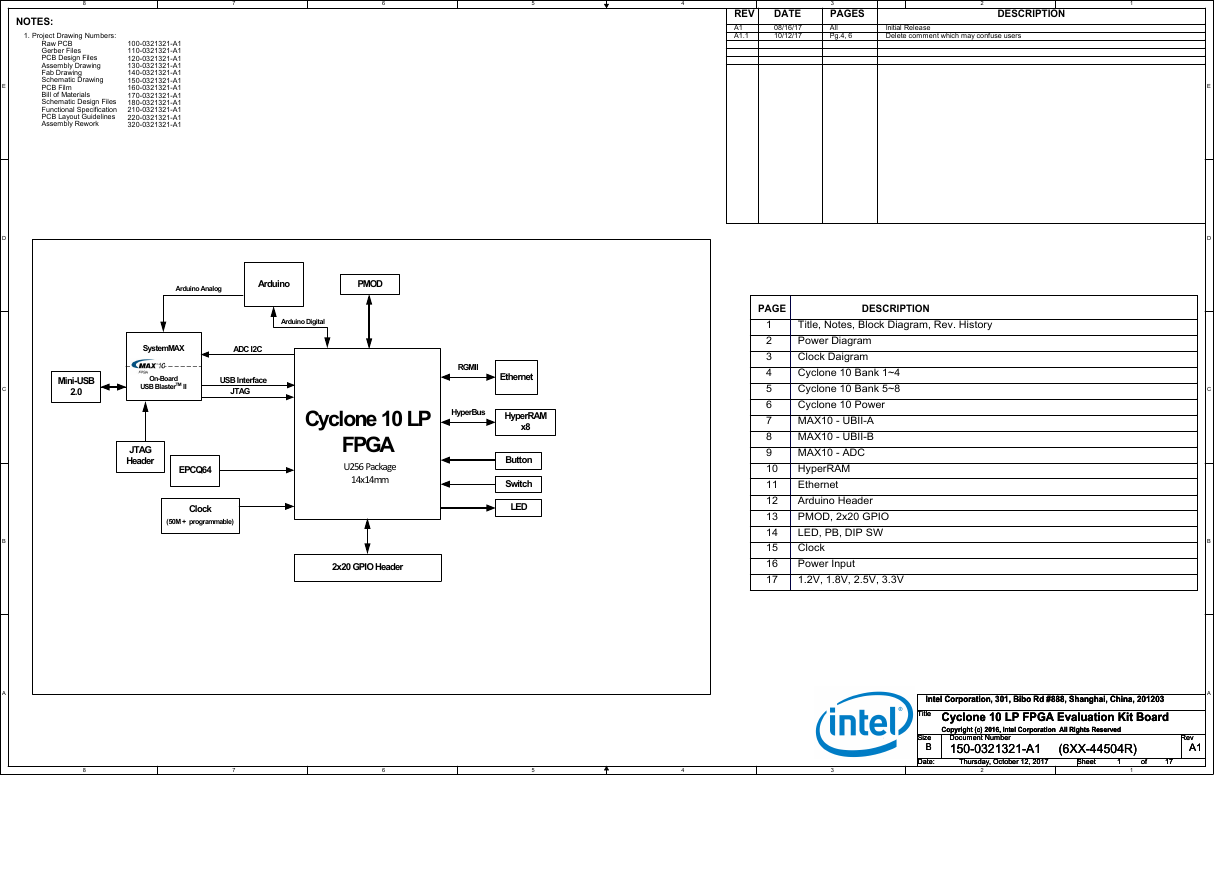

1

Initial Release

Delete comment which may confuse users

Arduino Analog

Arduino

PMOD

Arduino Digital

SystemMAX

ADC I2C

Mini-USB

2.0

On-Board

USB BlasterTM II

USB Interface

JTAG

JTAG

Header

EPCQ64

Clock

(50M + programmable)

RGMII

Ethernet

HyperBus

HyperRAM

x8

Button

Switch

LED

Cyclone 10 LP

FPGA

U256 Package

14x14mm

2x20 GPIO Header

PAGE

DESCRIPTION

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

Title, Notes, Block Diagram, Rev. History

Power Diagram

Clock Daigram

Cyclone 10 Bank 1~4

Cyclone 10 Bank 5~8

Cyclone 10 Power

MAX10 - UBII-A

MAX10 - UBII-B

MAX10 - ADC

HyperRAM

Ethernet

Arduino Header

PMOD, 2x20 GPIO

LED, PB, DIP SW

Clock

Power Input

1.2V, 1.8V, 2.5V, 3.3V

8

7

6

5

4

3

Intel Corporation, 301, Bibo Rd #888, Shanghai, China, 201203

Intel Corporation, 301, Bibo Rd #888, Shanghai, China, 201203

Intel Corporation, 301, Bibo Rd #888, Shanghai, China, 201203

Cyclone 10 LP FPGA Evaluation Kit Board

Cyclone 10 LP FPGA Evaluation Kit Board

Cyclone 10 LP FPGA Evaluation Kit Board

Copyright (c) 2016, Intel Corporation All Rights Reserved

Copyright (c) 2016, Intel Corporation All Rights Reserved

Copyright (c) 2016, Intel Corporation All Rights Reserved

Document Number

Document Number

Document Number

150-0321321-A1 (6XX-44504R)

150-0321321-A1 (6XX-44504R)

150-0321321-A1 (6XX-44504R)

Thursday, October 12, 2017

Thursday, October 12, 2017

Thursday, October 12, 2017

2

Sheet

Sheet

Sheet

1

1

1

of

of

of

17

17

17

1

Title

Title

Title

Size

Size

Size

B

B

B

Date:

Date:

Date:

E

D

C

B

A

E

D

C

B

A

Rev

Rev

Rev

A1

A1

A1

�

5

4

3

2

1

D

C

B

A

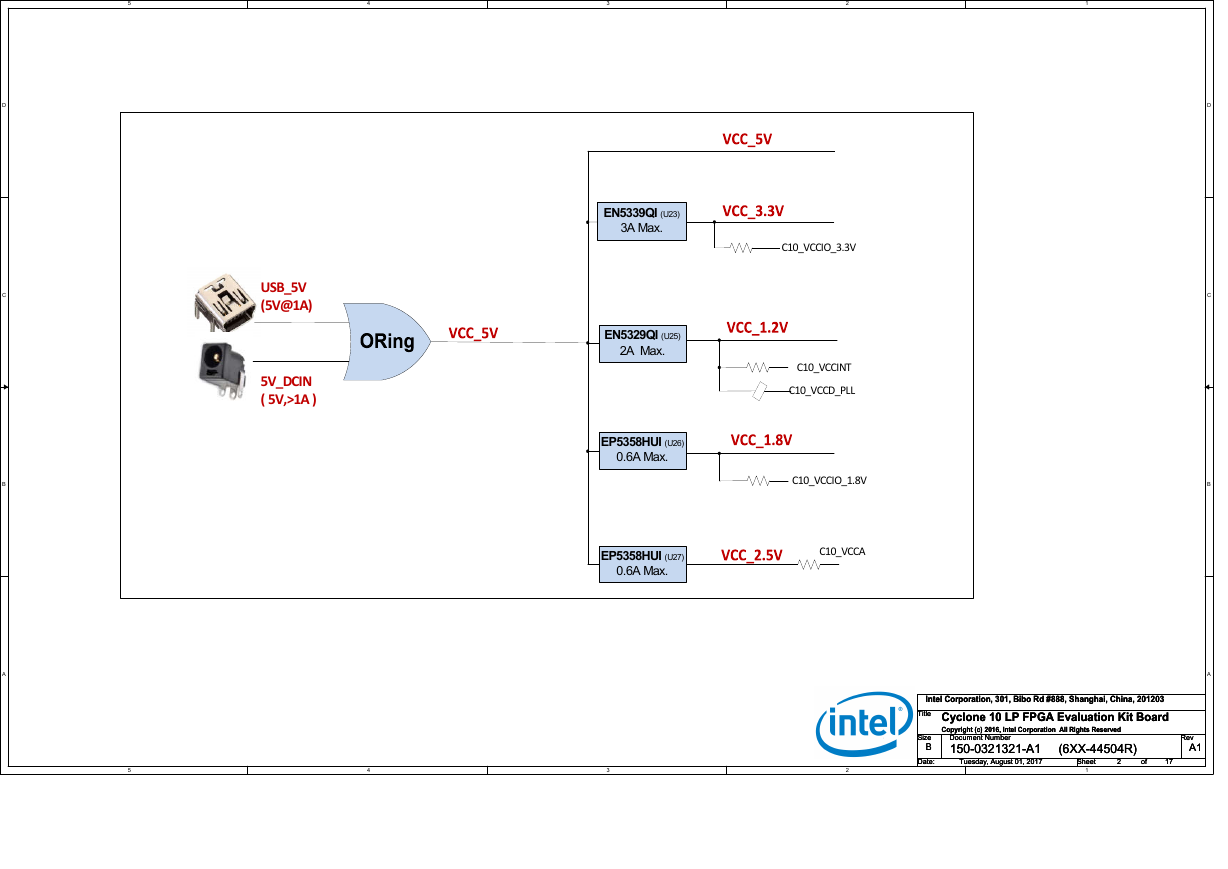

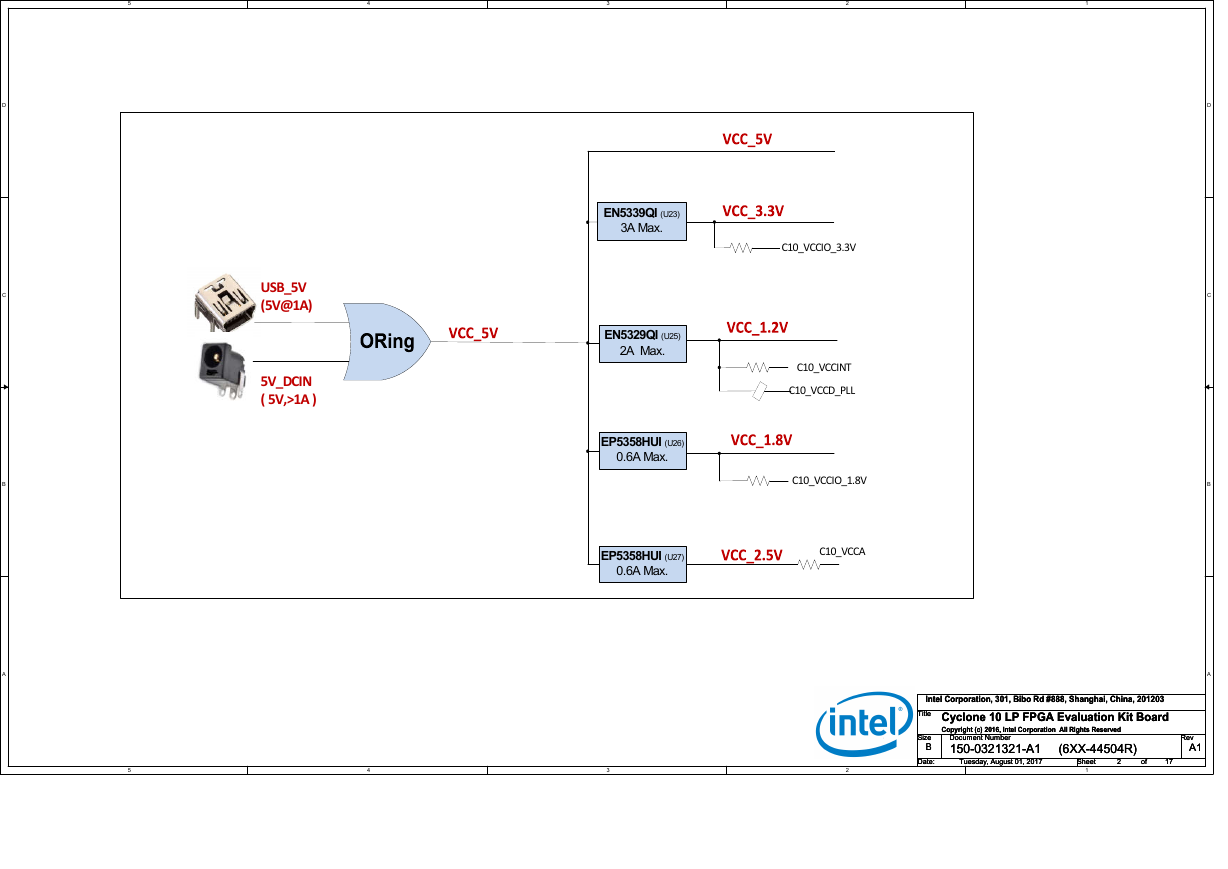

USB_5V

(5V@1A)

5V_DCIN

( 5V,>1A )

EN5339QI (U23)

3A Max.

EN5329QI (U25)

2A Max.

EP5358HUI (U26)

0.6A Max.

EP5358HUI (U27)

0.6A Max.

C10_VCCIO_3.3V

C10_VCCINT

C10_VCCD_PLL

C10_VCCIO_1.8V

C10_VCCA

5

4

3

2

D

C

B

A

Rev

Rev

Rev

A1

A1

A1

Intel Corporation, 301, Bibo Rd #888, Shanghai, China, 201203

Intel Corporation, 301, Bibo Rd #888, Shanghai, China, 201203

Intel Corporation, 301, Bibo Rd #888, Shanghai, China, 201203

Cyclone 10 LP FPGA Evaluation Kit Board

Cyclone 10 LP FPGA Evaluation Kit Board

Cyclone 10 LP FPGA Evaluation Kit Board

Copyright (c) 2016, Intel Corporation All Rights Reserved

Copyright (c) 2016, Intel Corporation All Rights Reserved

Copyright (c) 2016, Intel Corporation All Rights Reserved

Document Number

Document Number

Document Number

150-0321321-A1 (6XX-44504R)

150-0321321-A1 (6XX-44504R)

150-0321321-A1 (6XX-44504R)

Tuesday, August 01, 2017

Tuesday, August 01, 2017

Tuesday, August 01, 2017

Sheet

Sheet

Sheet

1

2

2

2

of

of

of

17

17

17

Title

Title

Title

Size

Size

Size

B

B

B

Date:

Date:

Date:

�

5

4

3

2

1

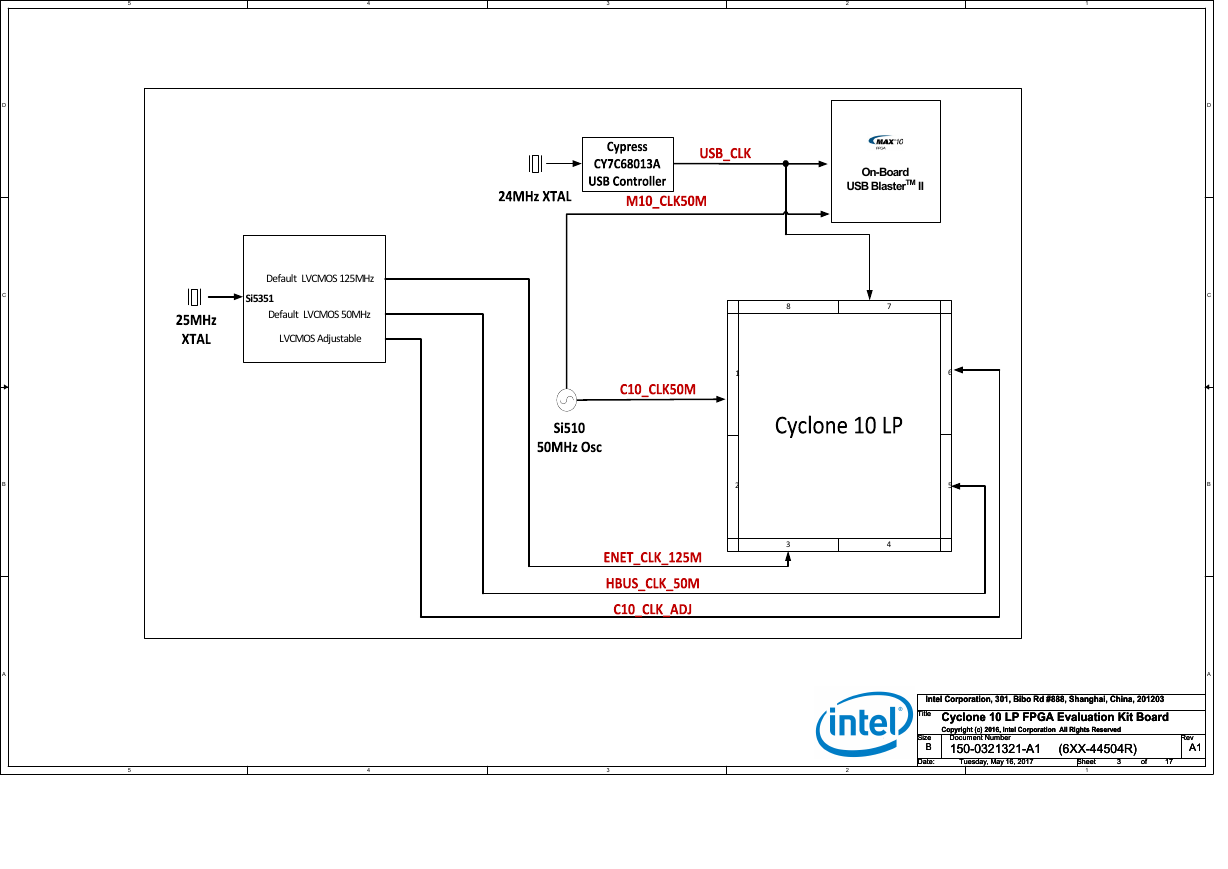

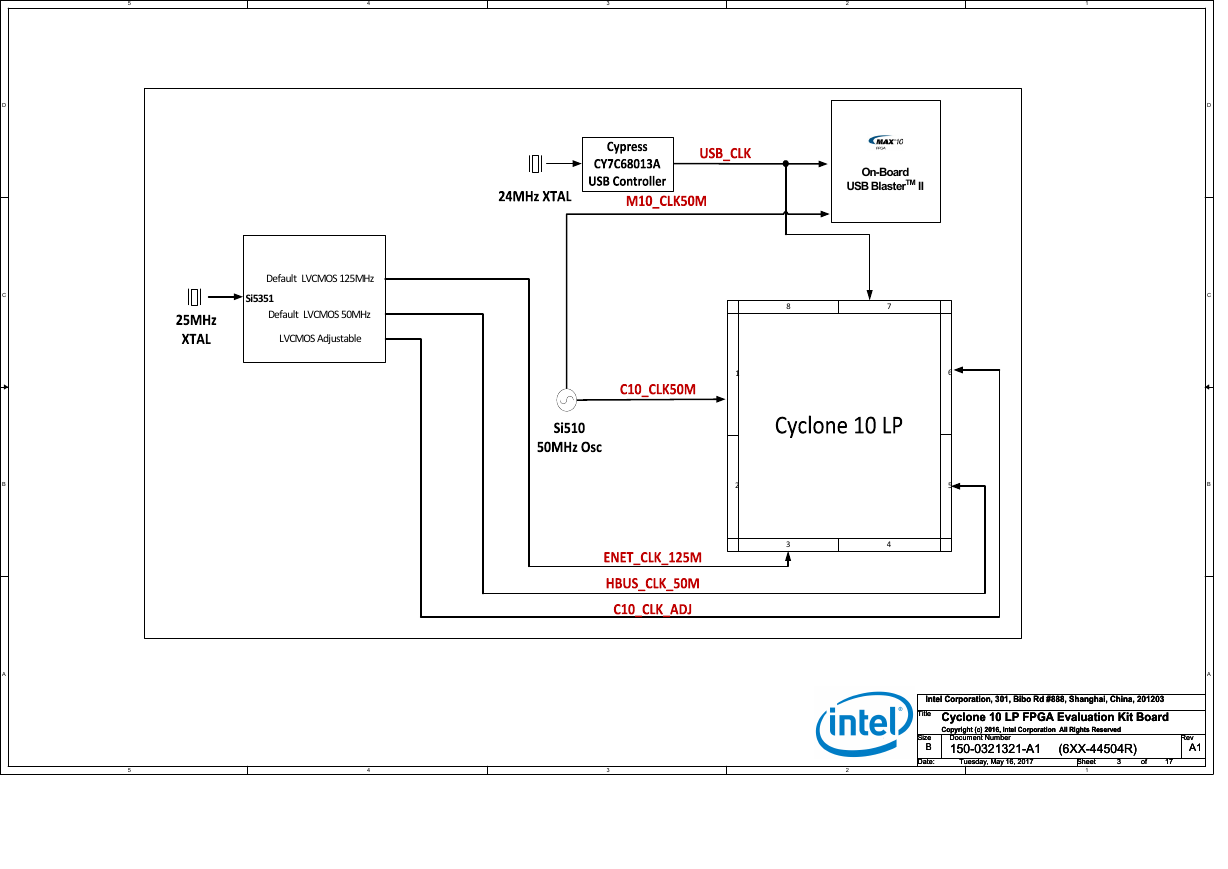

Default LVCMOS 125MHz

Si5351

Default LVCMOS 50MHz

LVCMOS Adjustable

Cypress

CY7C68013A

USB Controller

On-Board

USB BlasterTM II

1

2

8

3

7

4

6

5

D

C

B

A

5

4

3

2

Intel Corporation, 301, Bibo Rd #888, Shanghai, China, 201203

Intel Corporation, 301, Bibo Rd #888, Shanghai, China, 201203

Intel Corporation, 301, Bibo Rd #888, Shanghai, China, 201203

Cyclone 10 LP FPGA Evaluation Kit Board

Cyclone 10 LP FPGA Evaluation Kit Board

Cyclone 10 LP FPGA Evaluation Kit Board

Copyright (c) 2016, Intel Corporation All Rights Reserved

Copyright (c) 2016, Intel Corporation All Rights Reserved

Copyright (c) 2016, Intel Corporation All Rights Reserved

Document Number

Document Number

Document Number

150-0321321-A1 (6XX-44504R)

150-0321321-A1 (6XX-44504R)

150-0321321-A1 (6XX-44504R)

Tuesday, May 16, 2017

Tuesday, May 16, 2017

Tuesday, May 16, 2017

Sheet

Sheet

Sheet

1

3

3

3

of

of

of

17

17

17

Title

Title

Title

Size

Size

Size

B

B

B

Date:

Date:

Date:

D

C

B

A

Rev

Rev

Rev

A1

A1

A1

�

5

4

3

2

1

D

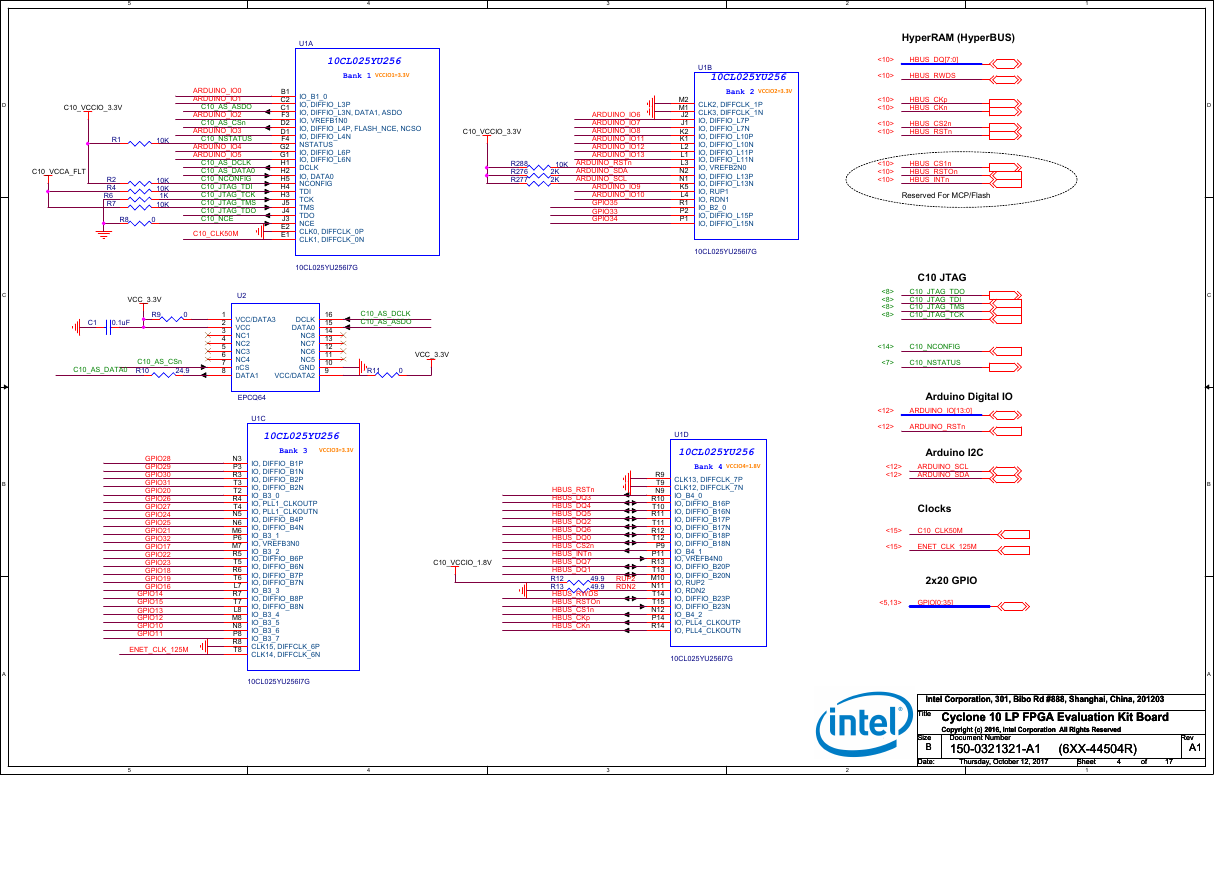

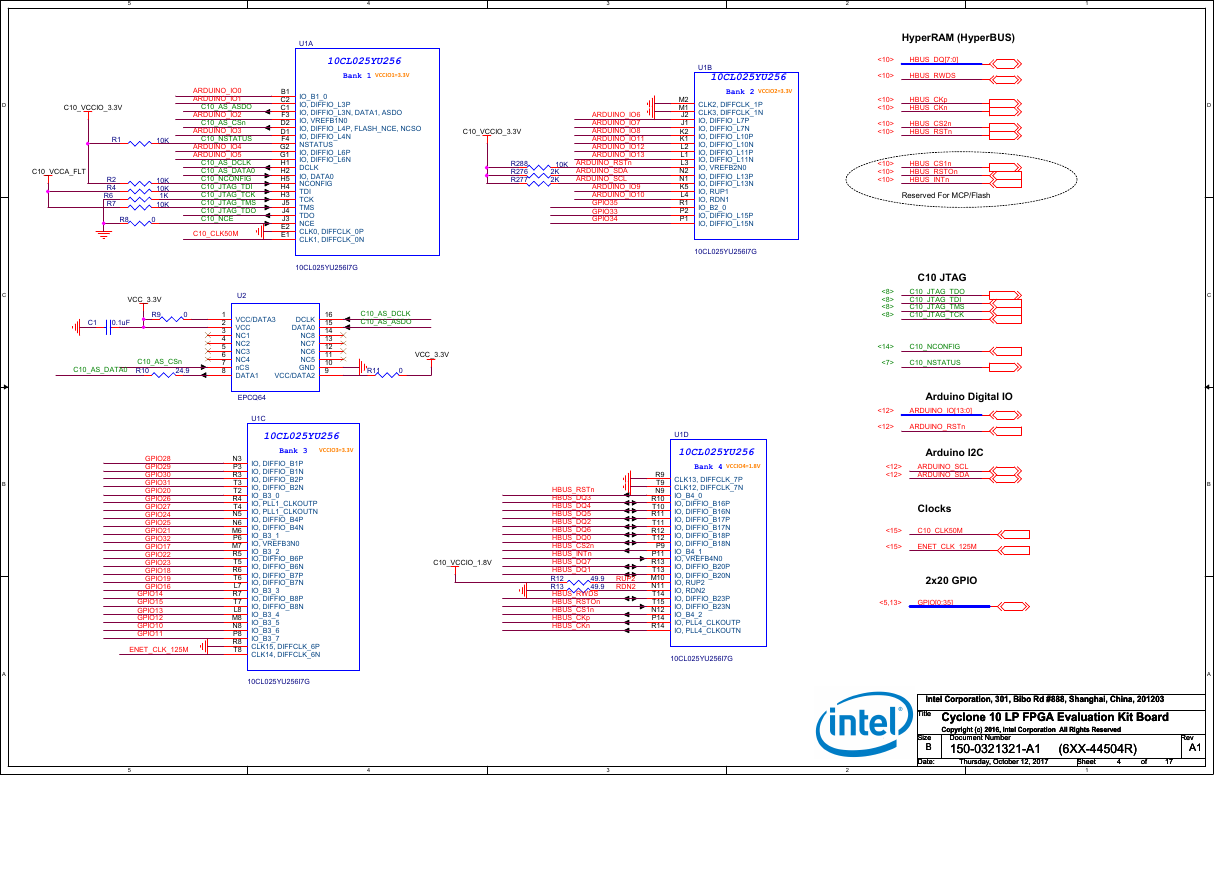

C10_VCCIO_3.3V

C10_VCCA_FLT

R1

R2

R4

R6

R7

10K

10K

10K

1K

10K

R8

0

ARDUINO_IO0

ARDUINO_IO1

C10_AS_ASDO

ARDUINO_IO2

C10_AS_CSn

ARDUINO_IO3

C10_NSTATUS

ARDUINO_IO4

ARDUINO_IO5

C10_AS_DCLK

C10_AS_DATA0

C10_NCONFIG

C10_JTAG_TDI

C10_JTAG_TCK

C10_JTAG_TMS

C10_JTAG_TDO

C10_NCE

C10_CLK50M

U1A

10CL025YU256

Bank 1

VCCIO1=3.3V

B1

C2

C1

F3

D2

D1

F4

G2

G1

H1

H2

H5

H4

H3

J5

J4

J3

E2

E1

IO_B1_0

IO, DIFFIO_L3P

IO, DIFFIO_L3N, DATA1, ASDO

IO, VREFB1N0

IO, DIFFIO_L4P, FLASH_NCE, NCSO

IO, DIFFIO_L4N

NSTATUS

IO, DIFFIO_L6P

IO, DIFFIO_L6N

DCLK

IO, DATA0

NCONFIG

TDI

TCK

TMS

TDO

NCE

CLK0, DIFFCLK_0P

CLK1, DIFFCLK_0N

10CL025YU256I7G

C10_VCCIO_3.3V

R288

R276

R277

10K

2K

2K

ARDUINO_IO6

ARDUINO_IO7

ARDUINO_IO8

ARDUINO_IO11

ARDUINO_IO12

ARDUINO_IO13

ARDUINO_RSTn

ARDUINO_SDA

ARDUINO_SCL

ARDUINO_IO9

ARDUINO_IO10

GPIO35

GPIO33

GPIO34

M2

M1

J2

J1

K2

K1

L2

L1

L3

N2

N1

K5

L4

R1

P2

P1

U1B

10CL025YU256

VCCIO2=3.3V

Bank 2

CLK2, DIFFCLK_1P

CLK3, DIFFCLK_1N

IO, DIFFIO_L7P

IO, DIFFIO_L7N

IO, DIFFIO_L10P

IO, DIFFIO_L10N

IO, DIFFIO_L11P

IO, DIFFIO_L11N

IO, VREFB2N0

IO, DIFFIO_L13P

IO, DIFFIO_L13N

IO, RUP1

IO, RDN1

IO_B2_0

IO, DIFFIO_L15P

IO, DIFFIO_L15N

10CL025YU256I7G

C

B

A

VCC_3.3V

U2

C1

0.1uF

R9

0

C10_AS_DATA0

C10_AS_CSn

R10

24.9

1

2

3

4

5

6

7

8

VCC/DATA3

VCC

NC1

NC2

NC3

NC4

nCS

DATA1

DCLK

DATA0

NC8

NC7

NC6

NC5

GND

VCC/DATA2

16

15

14

13

12

11

10

9

C10_AS_DCLK

C10_AS_ASDO

VCC_3.3V

R11

0

EPCQ64

U1C

GPIO28

GPIO29

GPIO30

GPIO31

GPIO20

GPIO26

GPIO27

GPIO24

GPIO25

GPIO21

GPIO32

GPIO17

GPIO22

GPIO23

GPIO18

GPIO19

GPIO16

GPIO14

GPIO15

GPIO13

GPIO12

GPIO10

GPIO11

ENET_CLK_125M

N3

P3

R3

T3

T2

R4

T4

N5

N6

M6

P6

M7

R5

T5

R6

T6

L7

R7

T7

L8

M8

N8

P8

R8

T8

10CL025YU256

VCCIO3=3.3V

Bank 3

IO, DIFFIO_B1P

IO, DIFFIO_B1N

IO, DIFFIO_B2P

IO, DIFFIO_B2N

IO_B3_0

IO, PLL1_CLKOUTP

IO, PLL1_CLKOUTN

IO, DIFFIO_B4P

IO, DIFFIO_B4N

IO_B3_1

IO, VREFB3N0

IO_B3_2

IO, DIFFIO_B6P

IO, DIFFIO_B6N

IO, DIFFIO_B7P

IO, DIFFIO_B7N

IO_B3_3

IO, DIFFIO_B8P

IO, DIFFIO_B8N

IO_B3_4

IO_B3_5

IO_B3_6

IO_B3_7

CLK15, DIFFCLK_6P

CLK14, DIFFCLK_6N

C10_VCCIO_1.8V

HBUS_RSTn

HBUS_DQ3

HBUS_DQ4

HBUS_DQ5

HBUS_DQ2

HBUS_DQ6

HBUS_DQ0

HBUS_CS2n

HBUS_INTn

HBUS_DQ7

HBUS_DQ1

R12

R13

HBUS_RWDS

HBUS_RSTOn

HBUS_CS1n

HBUS_CKp

HBUS_CKn

49.9

49.9

RUP2

RDN2

U1D

10CL025YU256

VCCIO4=1.8V

Bank 4

CLK13, DIFFCLK_7P

CLK12, DIFFCLK_7N

IO_B4_0

IO, DIFFIO_B16P

IO, DIFFIO_B16N

IO, DIFFIO_B17P

IO, DIFFIO_B17N

IO, DIFFIO_B18P

IO, DIFFIO_B18N

IO_B4_1

IO, VREFB4N0

IO, DIFFIO_B20P

IO, DIFFIO_B20N

IO, RUP2

IO, RDN2

IO, DIFFIO_B23P

IO, DIFFIO_B23N

IO_B4_2

IO, PLL4_CLKOUTP

IO, PLL4_CLKOUTN

10CL025YU256I7G

R9

T9

N9

R10

T10

R11

T11

R12

T12

P9

P11

R13

T13

M10

N11

T14

T15

N12

P14

R14

HyperRAM (HyperBUS)

<10>

<10>

<10>

<10>

<10>

<10>

<10>

<10>

<10>

HBUS_DQ[7:0]

HBUS_RWDS

HBUS_CKp

HBUS_CKn

HBUS_CS2n

HBUS_RSTn

HBUS_CS1n

HBUS_RSTOn

HBUS_INTn

Reserved For MCP/Flash

C10 JTAG

C10_JTAG_TDO

C10_JTAG_TDI

C10_JTAG_TMS

C10_JTAG_TCK

<8>

<8>

<8>

<8>

<14>

<7>

C10_NCONFIG

C10_NSTATUS

Arduino Digital IO

<12>

<12>

ARDUINO_IO[13:0]

ARDUINO_RSTn

Arduino I2C

<12>

<12>

ARDUINO_SCL

ARDUINO_SDA

Clocks

<15>

<15>

C10_CLK50M

ENET_CLK_125M

2x20 GPIO

<5,13>

GPIO[0:35]

D

C

B

A

Rev

Rev

Rev

A1

A1

A1

10CL025YU256I7G

5

4

3

2

Intel Corporation, 301, Bibo Rd #888, Shanghai, China, 201203

Intel Corporation, 301, Bibo Rd #888, Shanghai, China, 201203

Intel Corporation, 301, Bibo Rd #888, Shanghai, China, 201203

Cyclone 10 LP FPGA Evaluation Kit Board

Cyclone 10 LP FPGA Evaluation Kit Board

Cyclone 10 LP FPGA Evaluation Kit Board

Copyright (c) 2016, Intel Corporation All Rights Reserved

Copyright (c) 2016, Intel Corporation All Rights Reserved

Copyright (c) 2016, Intel Corporation All Rights Reserved

Document Number

Document Number

Document Number

150-0321321-A1 (6XX-44504R)

150-0321321-A1 (6XX-44504R)

150-0321321-A1 (6XX-44504R)

Thursday, October 12, 2017

Thursday, October 12, 2017

Thursday, October 12, 2017

Sheet

Sheet

Sheet

1

4

4

4

of

of

of

17

17

17

Title

Title

Title

Size

Size

Size

B

B

B

Date:

Date:

Date:

�

5

4

C10_VCCIO_3.3V

R16

R21

R246

10K

10K

10K

U1E

10CL025YU256

VCCIO5=3.3V

Bank 5

IO, RUP3

IO, RDN3

IO, DIFFIO_R15N

IO, DIFFIO_R15P

IO, DIFFIO_R13N

IO, DIFFIO_R13P

IO, VREFB5N0

IO_B5_0

IO, DIFFIO_R11N

IO, DIFFIO_R11P

IO, DIFFIO_R10N

IO, DIFFIO_R10P

IO, DIFFIO_R9N, DEV_OE

IO, DIFFIO_R9P, DEV_CLRN

IO_B5_1

IO_B5_2

CLK7, DIFFCLK_3N

CLK6, DIFFCLK_3P

10CL025YU256I7G

C10_CLK_ADJ

USER_PB0

C10_CONF_DONE

C10_MSEL0

C10_MSEL1

C10_MSEL2

C10_INIT_DONE

C10_CRC_ERROR

USER_PB1

PMOD_D1

PMOD_D3

PMOD_D5

PMOD_D7

PMOD_D0

PMOD_D2

PMOD_D4

PMOD_D6

3

U1F

10CL025YU256

VCCIO6=3.3V

Bank 6

CLK5, DIFFCLK_2N

CLK4, DIFFCLK_2P

CONF_DONE

MSEL0

MSEL1

MSEL2

IO, DIFFIO_R5N, INIT_DONE

IO, DIFFIO_R5P, CRC_ERROR

IO_B6_0

IO, DIFFIO_R4N, NCEO

IO, DIFFIO_R4P, CLKUSR

IO_B6_1

IO, VREFB6N0

IO_B6_2

IO_B6_3

IO, DIFFIO_R1N

IO, DIFFIO_R1P

E16

E15

H14

H13

H12

G12

G16

G15

F13

F16

F15

B16

F14

D16

D15

C16

C15

10CL025YU256I7G

2

R17

R18

R19

R20

R22

R23

C10_MSEL2

C10_MSEL1

C10_MSEL0

MSEL[2:0]=101: ASx1, Fast POR, 3.3V IO

1

C10_VCCA_FLT

2.5V

0

DNI

DNI

0

0

DNI

C10 M10 Interconnetion

<7>

C10_M10_IO[3:0]

C10 Misc. Signals

<14>

<7>

<7>

<7>

C10_RESETn

C10_CONF_DONE

C10_CRC_ERROR

C10_INIT_DONE

Arduino ADC I2C

<8>

<8>

ARDUINO_ADC_SCL

ARDUINO_ADC_SDA

<11>

<11>

<11>

<11>

<11>

<11>

<11>

<11>

<11>

<11>

<11>

<11>

<11>

<11>

<11>

<11>

<8>

<8>

<8>

<8>

<8>

<8>

<8>

<8>

<8>

<8>

Ethernet

ENET_RG_RXCLK

ENET_RG_RXCTL

ENET_RG_RXD0

ENET_RG_RXD1

ENET_RG_RXD2

ENET_RG_RXD3

ENET_RG_TXCLK

ENET_RG_TXCTL

ENET_RG_TXD0

ENET_RG_TXD1

ENET_RG_TXD2

ENET_RG_TXD3

ENET_MDC

ENET_MDIO

ENET_INT

ENET_RSTn

MAX10 USB Interface

USB_DATA[7:0]

USB_ADDR[1:0]

USB_FULL

USB_EMPTY

USB_SCL

USB_SDA

USB_RESETn

USB_OEn

USB_RDn

USB_WRn

User PBs, LEDs, SWs

<14>

<14>

<14>

USER_LED[0:3]

USER_PB[0:3]

USER_DIP[0:2]

2x20 GPIO

GPIO[0:35]

PMOD

PMOD_D[0:7]

<4,13>

<13>

Clock

C10_CLK_ADJ

HBUS_CLK_50M

<15>

<15>

<7>

USB_CLK

D

C

B

A

Rev

Rev

Rev

A1

A1

A1

C10_VCCIO_3.3V

R207

R136

10K

10K

GPIO8

GPIO9

GPIO4

GPIO5

GPIO6

GPIO7

USER_LED0

GPIO0

GPIO1

GPIO2

GPIO3

USER_LED1

C10_DEV_OE

C10_RESETn

USER_LED2

USER_LED3

USER_DIP0

HBUS_CLK_50M

USB_SCL

USB_EMPTY

USB_RDn

USB_FULL

USB_DATA4

USB_DATA3

USB_DATA2

USB_DATA1

USB_DATA6

USB_DATA5

USB_ADDR1

USB_WRn

USB_DATA0

USB_OEn

USB_ADDR0

USB_DATA7

USB_RESETn

USER_PB2

USER_PB3

USB_SDA

USER_DIP2

USB_CLK

R248

0

C10_USB_CLK

N14

P15

P16

R16

N16

N15

L14

L13

L16

L15

K16

K15

J16

J15

J14

J13

M16

M15

C14

D14

D11

D12

A13

B13

A14

B14

E11

E10

A12

B12

A11

B11

C11

A15

F9

A10

B10

C9

D9

E9

A9

B9

D

C

B

A

U1G

10CL025YU256

VCCIO7=3.3V

Bank 7

IO, DIFFIO_T24N

IO, DIFFIO_T24P

IO, DIFFIO_T23N

IO, DIFFIO_T23P

IO, DIFFIO_T22N

IO, DIFFIO_T22P

IO, PLL2_CLKOUTN

IO, PLL2_CLKOUTP

IO, RUP4

IO, RDN4

IO, DIFFIO_T21N

IO, DIFFIO_T21P

IO, DIFFIO_T20N

IO, DIFFIO_T20P

IO, VREFB7N0

IO_B7_0

IO_B7_1

IO, DIFFIO_T16N

IO, DIFFIO_T16P

IO, DIFFIO_T15N

IO, DIFFIO_T15P

IO_B7_2

CLK8, DIFFCLK_5N

CLK9, DIFFCLK_5P

C10_VCCIO_3.3V

R278

R279

2K

2K

ENET_RG_TXD0

ENET_RG_TXCTL

ENET_RG_TXD3

ENET_RG_TXD1

ENET_RG_TXD2

ENET_RG_TXCLK

R306

R301

R302

R303

R304

R305

USER_DIP1

ENET_RG_RXCLK

ARDUINO_ADC_SDA

ARDUINO_ADC_SCL

C10_M10_IO0

C10_M10_IO2

ENET_RG_RXD0

ENET_RG_RXD1

ENET_RSTn

ENET_RG_RXD2

ENET_RG_RXD3

C10_RG_TXCTL

C10_M10_IO1

C10_RG_TXD0

33

ENET_RG_RXCTL

ENET_INT

33

ENET_MDIO

ENET_MDC

33

33

33

C10_RG_TXD3

C10_RG_TXD1

C10_RG_TXD2

C10_M10_IO3

C10_RG_TXCLK

33

A8

B8

C8

D8

E8

F8

A7

B7

C6

A6

B6

E7

E6

A5

B5

D6

A4

B4

A2

A3

B3

C3

D3

U1H

10CL025YU256

VCCIO8=3.3V

Bank 8

CLK10, DIFFCLK_4N

CLK11, DIFFCLK_4P

IO_B8_0

IO_B8_1

IO, DIFFIO_T10N, DATA2

IO, DIFFIO_T10P, DATA3

IO, DIFFIO_T9N

IO, DIFFIO_T9P, DATA4

IO, VREFB8N0

IO, DIFFIO_T7N

IO, DIFFIO_T7P

IO, DATA5

IO, DATA6

IO, DIFFIO_T5N, DATA7

IO, DIFFIO_T5P

IO_B8_2

IO, DIFFIO_T3N

IO, DIFFIO_T3P

IO, DIFFIO_T2N

IO, DIFFIO_T2P

IO_B8_3

IO, PLL3_CLKOUTN

IO, PLL3_CLKOUTP

10CL025YU256I7G

10CL025YU256I7G

5

4

3

2

Intel Corporation, 301, Bibo Rd #888, Shanghai, China, 201203

Intel Corporation, 301, Bibo Rd #888, Shanghai, China, 201203

Intel Corporation, 301, Bibo Rd #888, Shanghai, China, 201203

Cyclone 10 LP FPGA Evaluation Kit Board

Cyclone 10 LP FPGA Evaluation Kit Board

Cyclone 10 LP FPGA Evaluation Kit Board

Copyright (c) 2016, Intel Corporation All Rights Reserved

Copyright (c) 2016, Intel Corporation All Rights Reserved

Copyright (c) 2016, Intel Corporation All Rights Reserved

Document Number

Document Number

Document Number

150-0321321-A1 (6XX-44504R)

150-0321321-A1 (6XX-44504R)

150-0321321-A1 (6XX-44504R)

Tuesday, May 16, 2017

Tuesday, May 16, 2017

Tuesday, May 16, 2017

Sheet

Sheet

Sheet

1

5

5

5

of

of

of

17

17

17

Title

Title

Title

Size

Size

Size

B

B

B

Date:

Date:

Date:

�

5

4

3

2

1

1.2V

C10_VCCINT

F7

F11

G6

G7

G8

G9

G10

H6

H11

J6

K7

K11

L6

K9

K10

M9

M11

J12

U1I

10CL025YU256

VCCINT

C10_VCCIO_3.3V

C10_VCCIO_1.8V

E3

G3

K3

M3

P4

P7

T1

P10

P13

T16

VCCINT

VCCINT

VCCINT

VCCINT

VCCINT

VCCINT

VCCINT

VCCINT

VCCINT

VCCINT

VCCINT

VCCINT

VCCINT

VCCINT

VCCINT

VCCINT

VCCINT

VCCINT

10CL025YU256I7G

U1J

10CL025YU256

VCCIO

VCCIO1

VCCIO1

VCCIO2

VCCIO2

VCCIO3

VCCIO3

VCCIO3

VCCIO4

VCCIO4

VCCIO4

VCCIO5

VCCIO5

VCCIO6

VCCIO6

VCCIO7

VCCIO7

VCCIO7

VCCIO8

VCCIO8

VCCIO8

K14

M14

E14

G14

A16

C10

C13

A1

C4

C7

10CL025YU256I7G

C10_VCCIO_3.3V

C10_VCCA

C10_VCCA_FLT

2.5V

L17

1.5A, 180 Ohm FB

C10_VCCD_PLL

1.2V

L5

F12

F5

L12

N4

D13

D4

N13

U1L

10CL025YU256

Misc. Power

VCCA1

VCCA2

VCCA3

VCCA4

VCCD_PLL1

VCCD_PLL2

VCCD_PLL3

VCCD_PLL4

10CL025YU256I7G

GNDA1

GNDA2

GNDA3

GNDA4

M5

E12

E5

M12

C10_VCCINT

C10_VCCIO_3.3V

C10_VCCA_FLT

C134

C136

C138

C139

C124

C129

4700pF

4700pF

0.01uF

0.01uF

0.022uF

0.022uF

C195

4.7uF

C196

C120

0.47uF

0.01uF

C117

0.1uF

C141

C143

C142

0.047uF

0.1uF

0.22uF

C130

1uF

C194

4.7uF

C193

47uF

VCC_1.8V

C10_VCCIO_1.8V

VCC_1.2V

TP27

R236

0.2

TP25

C197

C122

1uF

0.01uF

L15

R237

1.5A, 180 Ohm FB

C10_VCCD_PLL

TP26

0.2

C115

1uF

U1K

10CL025YU256

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

10CL025YU256I7G

H7

H8

H9

H10

J7

J8

J9

J10

F6

F10

J11

K8

K6

L9

L10

L11

K12

G11

B2

B15

C5

C12

D7

D10

E4

E13

G4

G13

K4

K13

M4

M13

N7

N10

P5

P12

R2

R15

H16

H15

D5

F1

F2

G5

D

C

B

A

5

4

3

2

Intel Corporation, 301, Bibo Rd #888, Shanghai, China, 201203

Intel Corporation, 301, Bibo Rd #888, Shanghai, China, 201203

Intel Corporation, 301, Bibo Rd #888, Shanghai, China, 201203

Cyclone 10 LP FPGA Evaluation Kit Board

Cyclone 10 LP FPGA Evaluation Kit Board

Cyclone 10 LP FPGA Evaluation Kit Board

Copyright (c) 2016, Intel Corporation All Rights Reserved

Copyright (c) 2016, Intel Corporation All Rights Reserved

Copyright (c) 2016, Intel Corporation All Rights Reserved

Document Number

Document Number

Document Number

150-0321321-A1 (6XX-44504R)

150-0321321-A1 (6XX-44504R)

150-0321321-A1 (6XX-44504R)

Thursday, October 12, 2017

Thursday, October 12, 2017

Thursday, October 12, 2017

Sheet

Sheet

Sheet

1

6

6

6

of

of

of

17

17

17

Title

Title

Title

Size

Size

Size

B

B

B

Date:

Date:

Date:

D

C

B

A

Rev

Rev

Rev

A1

A1

A1

�

5

4

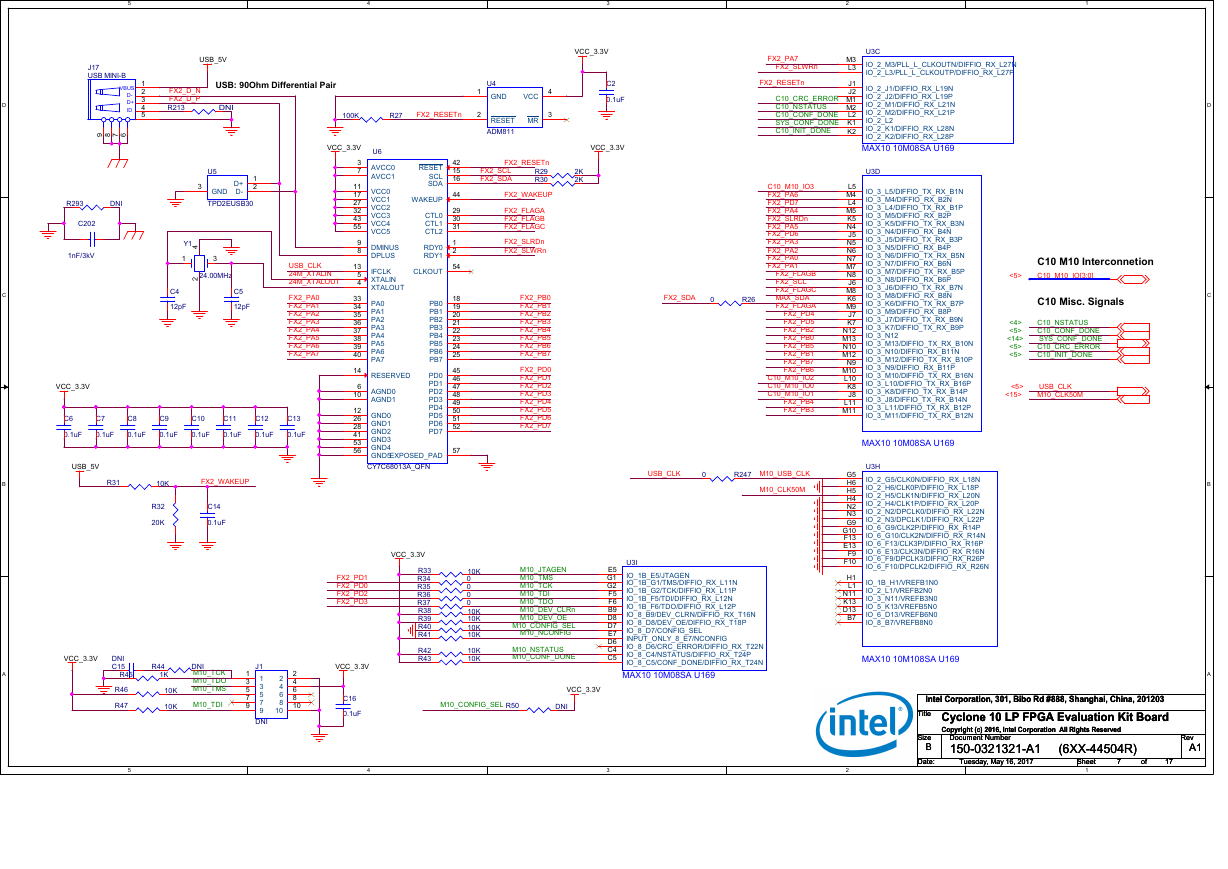

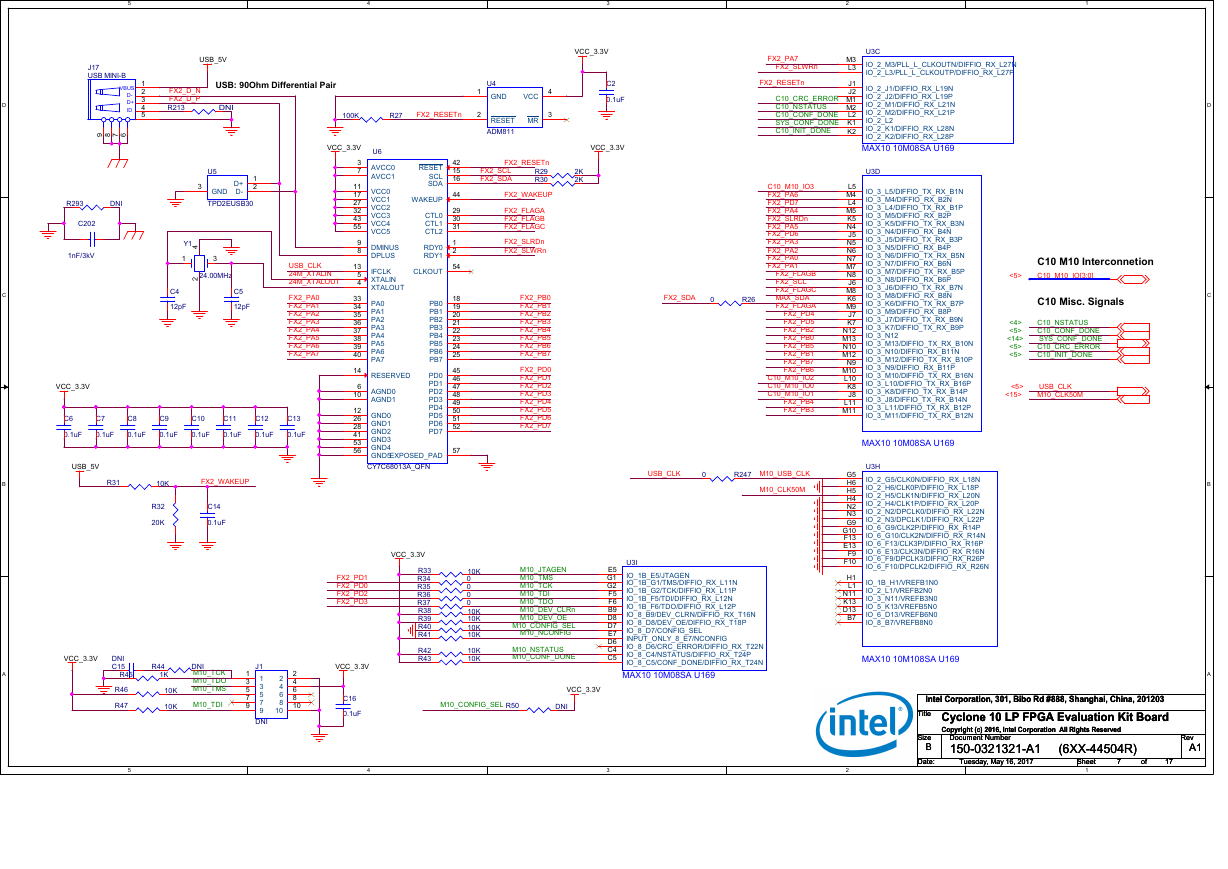

USB: 90Ohm Differential Pair

100K

R27

FX2_RESETn

1

2

U4

GND

RESET

ADM811

4

3

VCC

MR

VCC_3.3V

3

VCC_3.3V

C2

0.1uF

VCC_3.3V

D

C

B

A

USB_5V

FX2_D_N

FX2_D_P

R213

3

DNI

U5

1

2

D+

D-

GND

TPD2EUSB30

J17

USB MINI-B

VBUS

D-

D+

ID

1

2

3

4

5

6789

R293

DNI

C202

1nF/3kV

Y1

4

1

3

24.00MHz

2

C4

12pF

C5

12pF

USB_CLK

24M_XTALIN

24M_XTALOUT

FX2_PA0

FX2_PA1

FX2_PA2

FX2_PA3

FX2_PA4

FX2_PA5

FX2_PA6

FX2_PA7

VCC_3.3V

C6

C7

C8

C9

C10

C11

C12

C13

0.1uF

0.1uF

0.1uF

0.1uF

0.1uF

0.1uF

0.1uF

0.1uF

USB_5V

R31

10K

R32

20K

FX2_WAKEUP

C14

0.1uF

R44

1K

10K

10K

DNI

M10_TCK

M10_TDO

M10_TMS

M10_TDI

1

3

5

7

9

J1

1

3

5

7

9

DNI

2

4

6

8

10

2

4

6

8

10

VCC_3.3V

DNI

C15

R45

R46

R47

5

2

M3

L3

J1

J2

M1

M2

L2

K1

K2

L5

M4

L4

M5

K5

N4

J5

N5

N6

N7

M7

N8

J6

M8

K6

M9

J7

K7

N12

M13

N10

M12

N9

M10

L10

K8

J8

L11

M11

G5

H6

H5

H4

N2

N3

G9

G10

F13

E13

F9

F10

H1

L1

N11

K13

D13

B7

1

U3C

IO_2_M3/PLL_L_CLKOUTN/DIFFIO_RX_L27N

IO_2_L3/PLL_L_CLKOUTP/DIFFIO_RX_L27P

C10 M10 Interconnetion

C10_M10_IO[3:0]

<5>

C10 Misc. Signals

<4>

<5>

<14>

<5>

<5>

C10_NSTATUS

C10_CONF_DONE

SYS_CONF_DONE

C10_CRC_ERROR

C10_INIT_DONE

<5>

<15>

USB_CLK

M10_CLK50M

IO_2_J1/DIFFIO_RX_L19N

IO_2_J2/DIFFIO_RX_L19P

IO_2_M1/DIFFIO_RX_L21N

IO_2_M2/DIFFIO_RX_L21P

IO_2_L2

IO_2_K1/DIFFIO_RX_L28N

IO_2_K2/DIFFIO_RX_L28P

MAX10 10M08SA U169

U3D

IO_3_L5/DIFFIO_TX_RX_B1N

IO_3_M4/DIFFIO_RX_B2N

IO_3_L4/DIFFIO_TX_RX_B1P

IO_3_M5/DIFFIO_RX_B2P

IO_3_K5/DIFFIO_TX_RX_B3N

IO_3_N4/DIFFIO_RX_B4N

IO_3_J5/DIFFIO_TX_RX_B3P

IO_3_N5/DIFFIO_RX_B4P

IO_3_N6/DIFFIO_TX_RX_B5N

IO_3_N7/DIFFIO_RX_B6N

IO_3_M7/DIFFIO_TX_RX_B5P

IO_3_N8/DIFFIO_RX_B6P

IO_3_J6/DIFFIO_TX_RX_B7N

IO_3_M8/DIFFIO_RX_B8N

IO_3_K6/DIFFIO_TX_RX_B7P

IO_3_M9/DIFFIO_RX_B8P

IO_3_J7/DIFFIO_TX_RX_B9N

IO_3_K7/DIFFIO_TX_RX_B9P

IO_3_N12

IO_3_M13/DIFFIO_TX_RX_B10N

IO_3_N10/DIFFIO_RX_B11N

IO_3_M12/DIFFIO_TX_RX_B10P

IO_3_N9/DIFFIO_RX_B11P

IO_3_M10/DIFFIO_TX_RX_B16N

IO_3_L10/DIFFIO_TX_RX_B16P

IO_3_K8/DIFFIO_TX_RX_B14P

IO_3_J8/DIFFIO_TX_RX_B14N

IO_3_L11/DIFFIO_TX_RX_B12P

IO_3_M11/DIFFIO_TX_RX_B12N

MAX10 10M08SA U169

U3H

IO_2_G5/CLK0N/DIFFIO_RX_L18N

IO_2_H6/CLK0P/DIFFIO_RX_L18P

IO_2_H5/CLK1N/DIFFIO_RX_L20N

IO_2_H4/CLK1P/DIFFIO_RX_L20P

IO_2_N2/DPCLK0/DIFFIO_RX_L22N

IO_2_N3/DPCLK1/DIFFIO_RX_L22P

IO_6_G9/CLK2P/DIFFIO_RX_R14P

IO_6_G10/CLK2N/DIFFIO_RX_R14N

IO_6_F13/CLK3P/DIFFIO_RX_R16P

IO_6_E13/CLK3N/DIFFIO_RX_R16N

IO_6_F9/DPCLK3/DIFFIO_RX_R26P

IO_6_F10/DPCLK2/DIFFIO_RX_R26N

IO_1B_H1/VREFB1N0

IO_2_L1/VREFB2N0

IO_3_N11/VREFB3N0

IO_5_K13/VREFB5N0

IO_6_D13/VREFB6N0

IO_8_B7/VREFB8N0

MAX10 10M108SA U169

Intel Corporation, 301, Bibo Rd #888, Shanghai, China, 201203

Intel Corporation, 301, Bibo Rd #888, Shanghai, China, 201203

Intel Corporation, 301, Bibo Rd #888, Shanghai, China, 201203

Cyclone 10 LP FPGA Evaluation Kit Board

Cyclone 10 LP FPGA Evaluation Kit Board

Cyclone 10 LP FPGA Evaluation Kit Board

Copyright (c) 2016, Intel Corporation All Rights Reserved

Copyright (c) 2016, Intel Corporation All Rights Reserved

Copyright (c) 2016, Intel Corporation All Rights Reserved

Document Number

Document Number

Document Number

150-0321321-A1 (6XX-44504R)

150-0321321-A1 (6XX-44504R)

150-0321321-A1 (6XX-44504R)

Tuesday, May 16, 2017

Tuesday, May 16, 2017

Tuesday, May 16, 2017

Sheet

Sheet

Sheet

1

7

7

7

of

of

of

17

17

17

Title

Title

Title

Size

Size

Size

B

B

B

Date:

Date:

Date:

D

C

B

A

Rev

Rev

Rev

A1

A1

A1

3

7

11

17

27

32

43

55

9

8

13

5

4

33

34

35

36

37

38

39

40

14

6

10

12

26

28

41

53

56

U6

AVCC0

AVCC1

VCC0

VCC1

VCC2

VCC3

VCC4

VCC5

DMINUS

DPLUS

IFCLK

XTALIN

XTALOUT

PA0

PA1

PA2

PA3

PA4

PA5

PA6

PA7

RESERVED

AGND0

AGND1

RESET

SCL

SDA

WAKEUP

CTL0

CTL1

CTL2

RDY0

RDY1

CLKOUT

PB0

PB1

PB2

PB3

PB4

PB5

PB6

PB7

PD0

PD1

PD2

PD3

PD4

PD5

PD6

PD7

GND0

GND1

GND2

GND3

GND4

GND5

CY7C68013A_QFN

EXPOSED_PAD

FX2_SCL

FX2_SDA

FX2_RESETn

R29

R30

2K

2K

FX2_WAKEUP

FX2_FLAGA

FX2_FLAGB

FX2_FLAGC

FX2_SLRDn

FX2_SLWRn

FX2_PB0

FX2_PB1

FX2_PB2

FX2_PB3

FX2_PB4

FX2_PB5

FX2_PB6

FX2_PB7

FX2_PD0

FX2_PD1

FX2_PD2

FX2_PD3

FX2_PD4

FX2_PD5

FX2_PD6

FX2_PD7

42

15

16

44

29

30

31

1

2

54

18

19

20

21

22

23

24

25

45

46

47

48

49

50

51

52

57

FX2_PA7

FX2_SLWRn

FX2_RESETn

C10_CRC_ERROR

C10_NSTATUS

C10_CONF_DONE

SYS_CONF_DONE

C10_INIT_DONE

C10_M10_IO3

FX2_PA6

FX2_PD7

FX2_PA4

FX2_SLRDn

FX2_PA5

FX2_PD6

FX2_PA3

FX2_PA2

FX2_PA0

FX2_PA1

FX2_FLAGB

FX2_SCL

FX2_FLAGC

MAX_SDA

FX2_FLAGA

FX2_PD4

FX2_PD5

FX2_PB2

FX2_PB0

FX2_PB5

FX2_PB1

FX2_PB7

FX2_PB6

C10_M10_IO2

C10_M10_IO0

C10_M10_IO1

FX2_PB4

FX2_PB3

FX2_SDA

0

R26

USB_CLK

0

R247

M10_USB_CLK

M10_CLK50M

VCC_3.3V

R33

R34

R35

R36

R37

R38

R39

R40

R41

R42

R43

10K

0

0

0

0

10K

10K

10K

10K

10K

10K

M10_JTAGEN

M10_TMS

M10_TCK

M10_TDI

M10_TDO

M10_DEV_CLRn

M10_DEV_OE

M10_CONFIG_SEL

M10_NCONFIG

M10_NSTATUS

M10_CONF_DONE

E5

G1

G2

F5

F6

B9

D8

D7

E7

D6

C4

C5

U3I

IO_1B_E5/JTAGEN

IO_1B_G1/TMS/DIFFIO_RX_L11N

IO_1B_G2/TCK/DIFFIO_RX_L11P

IO_1B_F5/TDI/DIFFIO_RX_L12N

IO_1B_F6/TDO/DIFFIO_RX_L12P

IO_8_B9/DEV_CLRN/DIFFIO_RX_T16N

IO_8_D8/DEV_OE/DIFFIO_RX_T18P

IO_8_D7/CONFIG_SEL

INPUT_ONLY_8_E7/NCONFIG

IO_8_D6/CRC_ERROR/DIFFIO_RX_T22N

IO_8_C4/NSTATUS/DIFFIO_RX_T24P

IO_8_C5/CONF_DONE/DIFFIO_RX_T24N

MAX10 10M08SA U169

M10_CONFIG_SEL

R50

DNI

VCC_3.3V

FX2_PD1

FX2_PD0

FX2_PD2

FX2_PD3

VCC_3.3V

C16

0.1uF

4

3

2

�

5

4

3

2

1

VCC_3.3V

R53

R51

1K

1K

R54

1K

R52

1K

USB_SDA

USB_FULL

USB_RESETn

USB_OEn

USB_RDn

USB_ADDR1

USB_WRn

USB_SCL

USB_ADDR0

USB_DATA6

USB_DATA7

USB_DATA2

USB_DATA5

USB_DATA0

USB_EMPTY

USB_DATA1

USB_DATA3

USB_DATA4

C10

C9

A8

A9

B10

A10

A11

E8

A7

A6

B6

A4

B5

A3

E6

B3

B4

A5

A2

B2

U3G

IO_8_C10/DIFFIO_RX_T14P

IO_8_C9/DIFFIO_RX_T14N

IO_8_A8/DIFFIO_RX_T15P

IO_8_A9/DIFFIO_RX_T15N

IO_8_B10/DIFFIO_RX_T16P

IO_8_A10/DIFFIO_RX_T17P

IO_8_A11/DIFFIO_RX_T17N

IO_8_E8/DIFFIO_RX_T18N

IO_8_A7/DIFFIO_RX_T19P

IO_8_A6/DIFFIO_RX_T19N

IO_8_B6/DIFFIO_RX_T20P

IO_8_A4/DIFFIO_RX_T21P

IO_8_B5/DIFFIO_RX_T20N

IO_8_A3/DIFFIO_RX_T21N

IO_8_E6/DIFFIO_RX_T22P

IO_8_B3/DIFFIO_RX_T23P

IO_8_B4/DIFFIO_RX_T23N

IO_8_A5

IO_8_A2/DIFFIO_RX_T26P

IO_8_B2/DIFFIO_RX_T26N

MAX10 10M08SA U169

VCCIO=2.5V

C10_JTAG_TDI

C10_JTAG_TCK

C10_JTAG_TMS

C10_JTAG_TDO

F12

E12

C13

F8

B12

E9

B11

C12

B13

C11

A12

E10

D9

D12

D11

U3F

IO_6_F12/DIFFIO_RX_R18P

IO_6_E12/DIFFIO_RX_R18N

IO_6_C13

IO_6_F8/DIFFIO_RX_R27P

IO_6_B12/DIFFIO_RX_R28P

IO_6_E9/DIFFIO_RX_R27N

IO_6_B11/DIFFIO_RX_R28N

IO_6_C12/DIFFIO_RX_R29P

IO_6_B13/DIFFIO_RX_R30P

IO_6_C11/DIFFIO_RX_R29N

IO_6_A12/DIFFIO_RX_R30N

IO_6_E10/DIFFIO_RX_R31P

IO_6_D9/DIFFIO_RX_R31N

IO_6_D12/DIFFIO_RX_R33P

IO_6_D11/DIFFIO_RX_R33N

MAX10 10M08SA U169

USB Blaster Programming Header

(uses JTAG mode only)

VCC_3.3V

C17

0.1uF

R57

DNI

R58

R60

R61

1K

10K

10K

EXT_JTAG_TCK

EXT_JTAG_TDO

EXT_JTAG_TMS

EXT_JTAG_TDI

1

3

5

7

9

J2

2

4

6

8

10

2X5_100mil

1

3

5

7

9

2

4

6

8

10

USB_DISABLEn

1K

R59

VCC_3.3V

C18

0.1uF

VCC_3.3V

M10_VCCIO1A

L2

1.5A, 180 Ohm FB

VCC_2.5V

C182

1uF

C189

0.22uF

VCC_3.3V

C176

C156

10uF

0.22uF

C190

4.7uF

C155

C157

0.01uF

0.01uF

VCC_3.3V

M10_VCCA_3.3V

L3

1.5A, 180 Ohm FB

C177

C178

C179

C180

C181

VCC_3.3V

10uF

0.1uF

0.1uF

0.1uF

0.1uF

C153

C151

0.01uF

0.047uF

C146

4.7uF

F2

G3

K3

J3

L8

L7

L6

J11

H11

G11

F11

C8

C7

C6

K4

D10

D4

K9

H7

G8

G6

F7

U3A

VCCIO1A__F2

VCCIO1B__G3

VCCIO2__K3

VCCIO2__J3

VCCIO3__L8

VCCIO3__L7

VCCIO3__L6

VCCIO5__J11

VCCIO5__H11

VCCIO6__G11

VCCIO6__F11

VCCIO8__C8

VCCIO8__C7

VCCIO8__C6

VCCA1__K4

VCCA2__D10

VCCA3__D4

VCCA4__K9

VCC_ONE__H7

VCC_ONE__G8

VCC_ONE__G6

VCC_ONE__F7

MAX10 10M08SA U169

A1

A13

B8

C3

D5

E11

F3

G7

H12

J4

L9

M6

N1

N13

U3K

GND__A1

GND__A13

GND__B8

GND__C3

GND__D5

GND__E11

GND__F3

GND__G7

GND__H12

GND__J4

GND__L9

GND__M6

GND__N1

GND__N13

MAX10 10M08SA U169

VCC_3.3V

R214

R215

2K

2K

VCC_3.3V

R55

R56

2K

2K

VTAP_BYPASSn

ARDUINO_ADC_SDA

ARDUINO_ADC_SCL

EXT_JTAG_TDO

EXT_JTAG_TMS

EXT_JTAG_TCK

EXT_JTAG_TDI

USB_DISABLEn

VCC_1.2V_PG

VCC_3.3V_PG

PWR_GD_LED

SYS_I2C_SCL

SYS_I2C_SDA

MAX10 USB Interface

<5>

<5>

<5>

<5>

<5>

<5>

<5>

<5>

<5>

<5>

USB_DATA[7:0]

USB_ADDR[1:0]

USB_FULL

USB_EMPTY

USB_SCL

USB_SDA

USB_RESETn

USB_OEn

USB_RDn

USB_WRn

System I2C

<15>

<15>

SYS_I2C_SCL

SYS_I2C_SDA

C10 JTAG

C10_JTAG_TDO

C10_JTAG_TDI

C10_JTAG_TMS

C10_JTAG_TCK

<4>

<4>

<4>

<4>

<14>

VTAP_BYPASSn

Arduino ADC I2C

<5>

<5>

ARDUINO_ADC_SCL

ARDUINO_ADC_SDA

Power Good

VCC_1.2V_PG

VCC_3.3V_PG

<17>

<17>

<14>

PWR_GD_LED

K10

J10

K11

L12

K12

L13

J12

J9

J13

H10

H13

H9

G13

H8

G12

U3E

IO_5_K10/DIFFIO_RX_R1P

IO_5_J10/DIFFIO_RX_R1N

IO_5_K11/DIFFIO_RX_R2P

IO_5_L12/DIFFIO_RX_R2N

IO_5_K12/DIFFIO_RX_R7P

IO_5_L13

IO_5_J12/DIFFIO_RX_R7N

IO_5_J9/DIFFIO_RX_R8P

IO_5_J13/DIFFIO_RX_R9P

IO_5_H10/DIFFIO_RX_R8N

IO_5_H13/DIFFIO_RX_R9N

IO_5_H9/DIFFIO_RX_R10P

IO_5_G13/DIFFIO_RX_R11P

IO_5_H8/DIFFIO_RX_R10N

IO_5_G12/DIFFIO_RX_R11N

MAX10 10M08SA U169

D

C

B

A

5

4

3

2

Intel Corporation, 301, Bibo Rd #888, Shanghai, China, 201203

Intel Corporation, 301, Bibo Rd #888, Shanghai, China, 201203

Intel Corporation, 301, Bibo Rd #888, Shanghai, China, 201203

Cyclone 10 LP FPGA Evaluation Kit Board

Cyclone 10 LP FPGA Evaluation Kit Board

Cyclone 10 LP FPGA Evaluation Kit Board

Copyright (c) 2016, Intel Corporation All Rights Reserved

Copyright (c) 2016, Intel Corporation All Rights Reserved

Copyright (c) 2016, Intel Corporation All Rights Reserved

Document Number

Document Number

Document Number

150-0321321-A1 (6XX-44504R)

150-0321321-A1 (6XX-44504R)

150-0321321-A1 (6XX-44504R)

Monday, June 26, 2017

Monday, June 26, 2017

Monday, June 26, 2017

Sheet

Sheet

Sheet

1

8

8

8

of

of

of

17

17

17

Title

Title

Title

Size

Size

Size

B

B

B

Date:

Date:

Date:

D

C

B

A

Rev

Rev

Rev

A1

A1

A1

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc