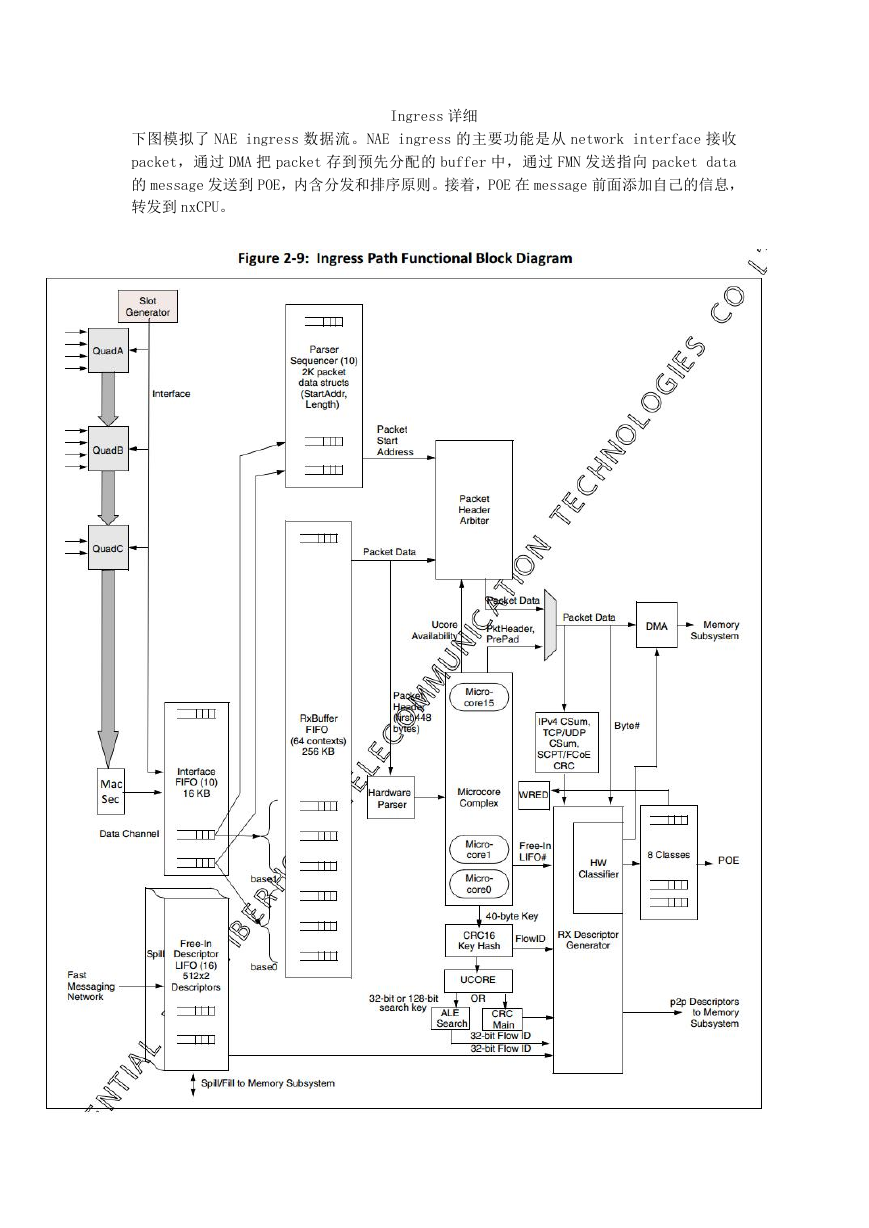

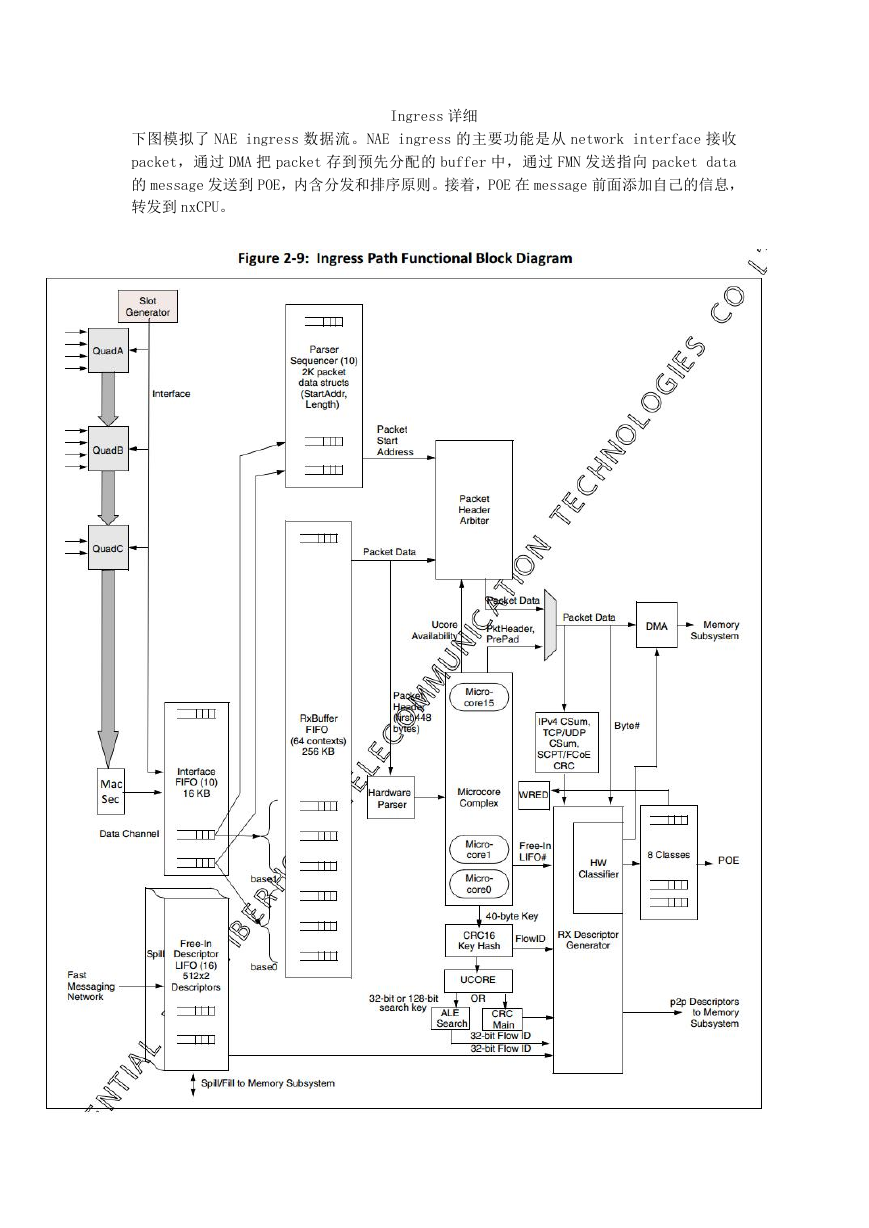

Ingress 详细

下图模拟了 NAE ingress 数据流。NAE ingress 的主要功能是从 network interface 接收

packet,通过 DMA 把 packet 存到预先分配的 buffer 中,通过 FMN 发送指向 packet data

的 message 发送到 POE,内含分发和排序原则。接着,POE 在 message 前面添加自己的信息,

转发到 nxCPU。

�

下图显示了 ingress data flow path

NAE ingress 从按照 slot 划分的 bus 上接收 packet data。

NAE ingress 不断扫描从 calendar slots 0~CalLen ,从 calendar slots 的 IfNum fileld

指定的接口读取 packet data。

NetRXMacSec:该模块 take in the data coming from the NetIor,解密并鉴定。它还会

检查各种 MacSec 错误,然后把所有信息传给 NetInterfaceFIFO。

interface FIFO:数据被存储到每个 interface FIFO(共有10个),这个 FIFO 被划分成256

个 entry,每个64byte。这个 IF interface 被 NAE 用来存储和调度 packet data 到 RX context

buffer。

RX buffer:接收到的 data 被移动到 RX buffer,该 buffer 被分成64个 context。每个 context

代表一个 sub-interface 或者系统意义上的 interface。该 buffer 中有 forwarding mode MTU

size 的限制。当 FIFO's empty space 少于某个可设置值时,新来的 packet 都会被丢弃。

parser seq FIFO:

一个循环调度器会不断从 RX buffer 中读出 data 并填充到 parser 和 DMA block 的 data

buffer 中。共有10个 parser seq FIFO,分为2048个 entry。

在进行调度前,需要确认 context 中接收的总字节数目应该比 一个可设置门限值 要大或者

在 RX buffer 中出现了一个该 section 的 EOP。

parser seq FIFO 的 data struct 包含诸如 startAddr、packet length 的信息。

hardware parser:该 parser 对每个来包生成 40字节大小的 classfication(分类) key,

这个 key 可以发给16个可编程 micro-cores 中的一个做进一步的分类处理。

micro-cores 是可编程 MIPS 处理器,对包的解析和分类提供了极大的灵活性。

�

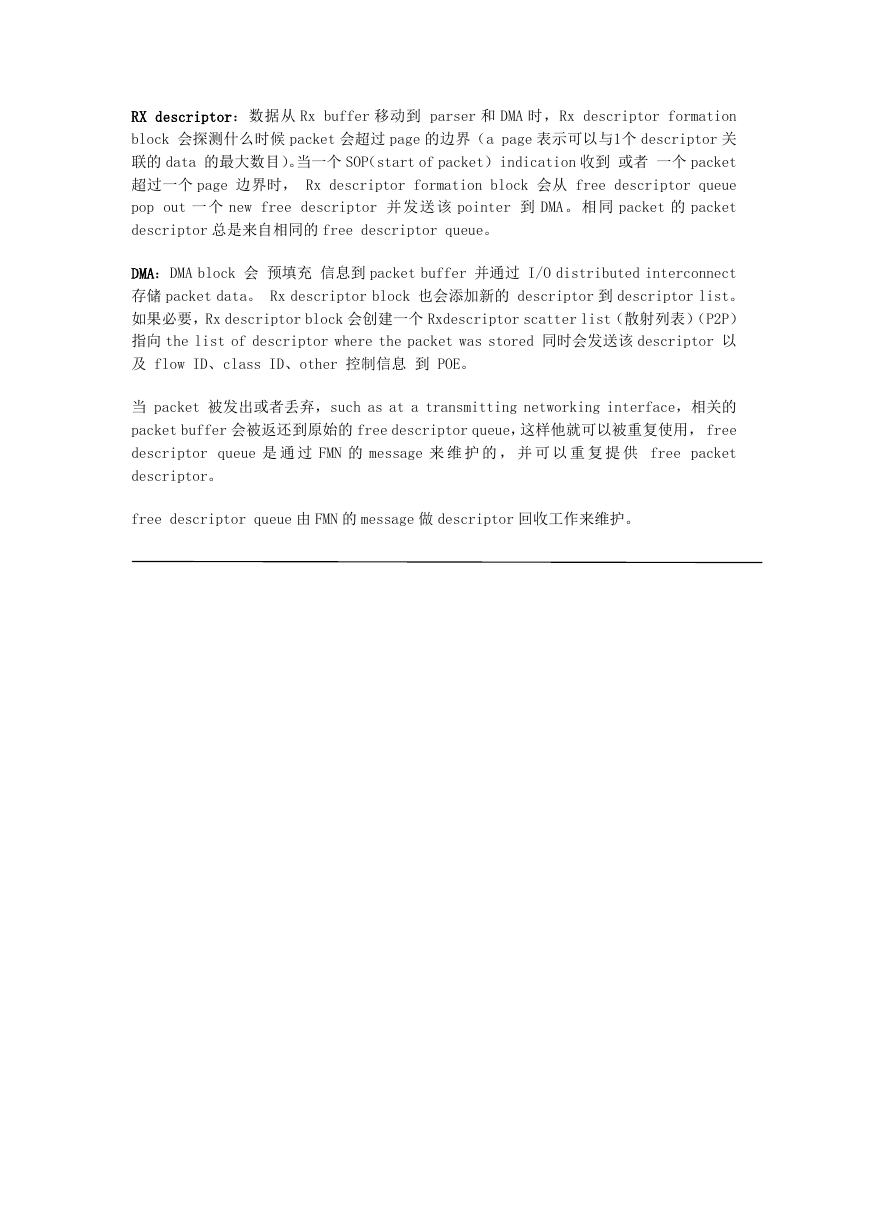

RX descriptor:数据从 Rx buffer 移动到 parser 和 DMA 时,Rx descriptor formation

block 会探测什么时候 packet 会超过 page 的边界(a page 表示可以与1个 descriptor 关

联的 data 的最大数目)。当一个 SOP(start of packet)indication 收到 或者 一个 packet

超过一个 page 边界时, Rx descriptor formation block 会从 free descriptor queue

pop out 一 个 new free descriptor 并 发 送该 pointer 到 DMA。 相 同 packet 的 packet

descriptor 总是来自相同的 free descriptor queue。

DMA:DMA block 会 预填充 信息到 packet buffer 并通过 I/O distributed interconnect

存储 packet data。 Rx descriptor block 也会添加新的 descriptor 到 descriptor list。

如果必要,Rx descriptor block 会创建一个 Rxdescriptor scatter list(散射列表)(P2P)

指向 the list of descriptor where the packet was stored 同时会发送该 descriptor 以

及 flow ID、class ID、other 控制信息 到 POE。

当 packet 被发出或者丢弃,such as at a transmitting networking interface,相关的

packet buffer 会被返还到原始的 free descriptor queue,这样他就可以被重复使用, free

descriptor queue 是 通 过 FMN 的 message 来 维 护 的 , 并 可 以 重 复 提 供 free packet

descriptor。

free descriptor queue 由 FMN 的 message 做 descriptor 回收工作来维护。

�

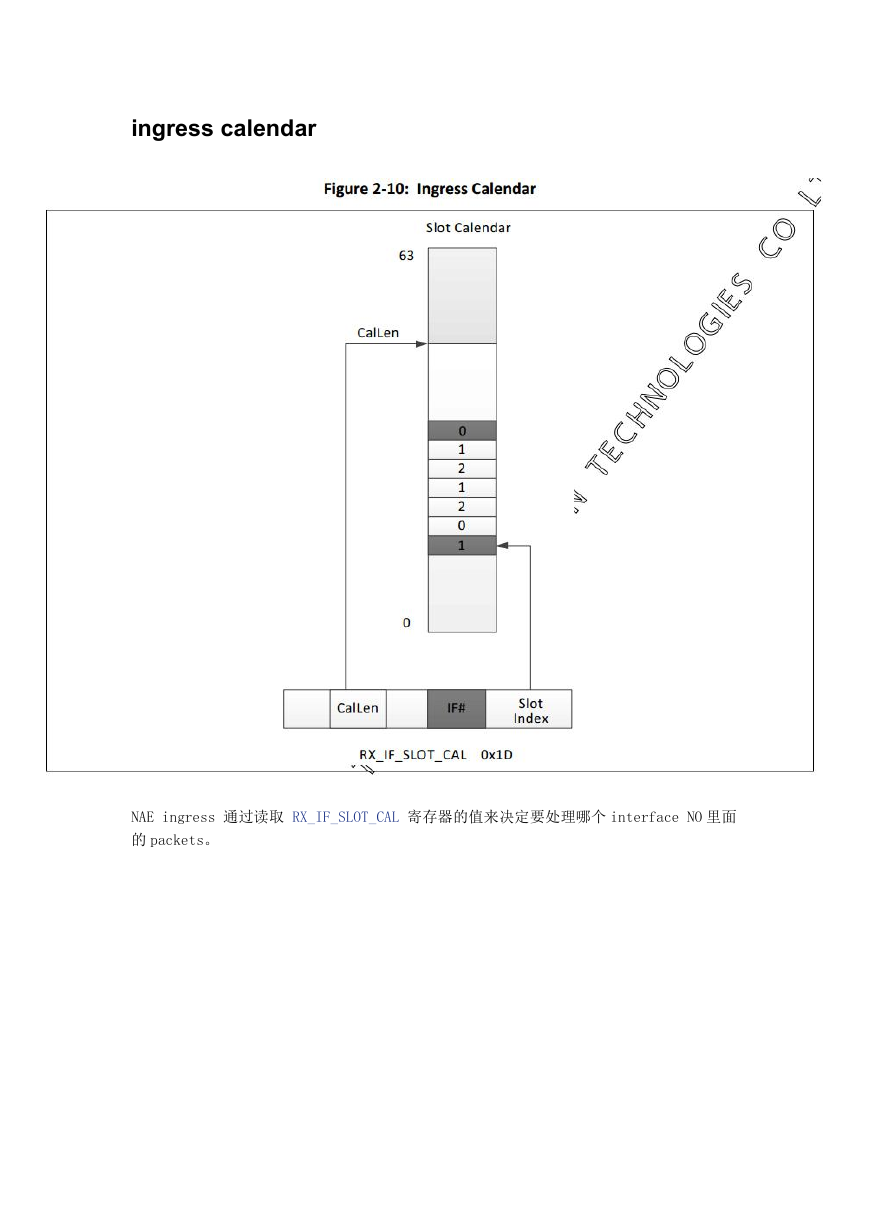

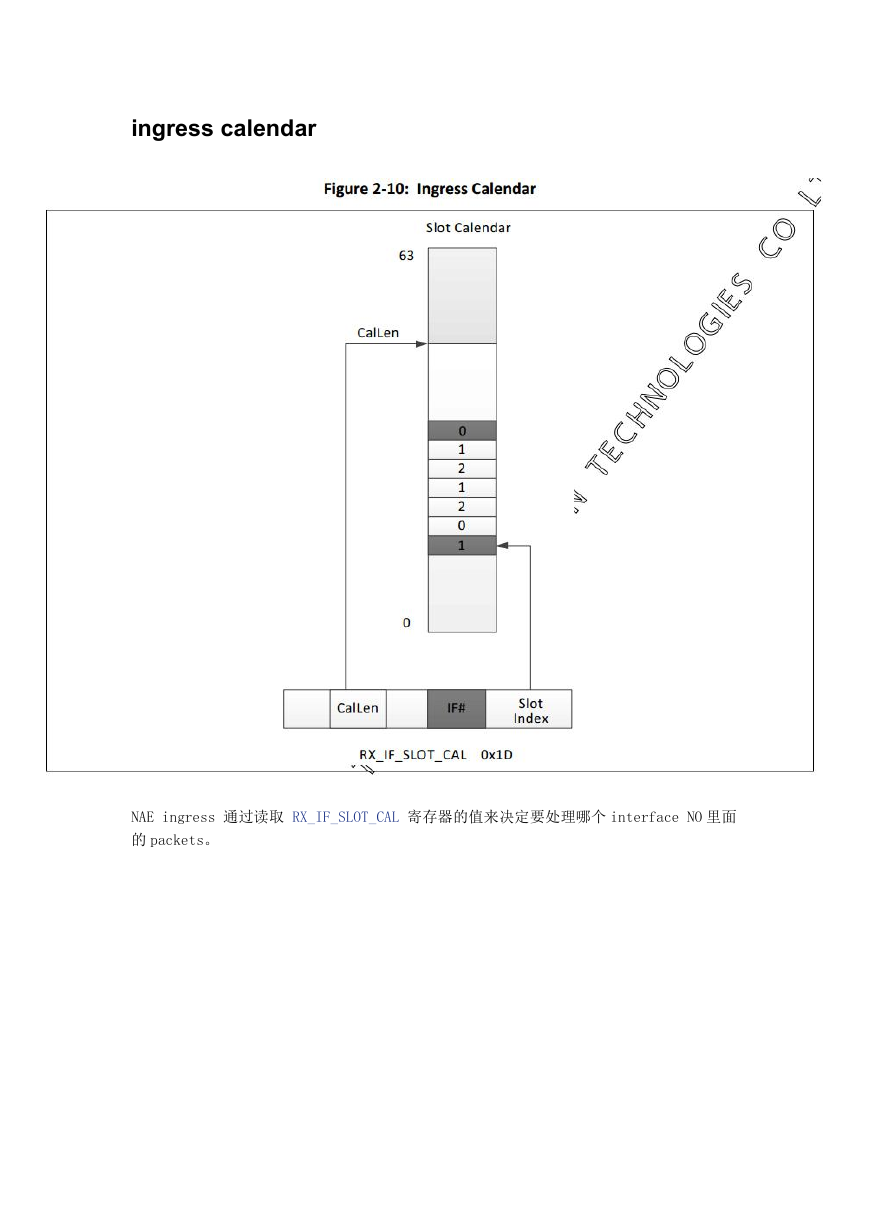

ingress calendar

NAE ingress 通过读取 RX_IF_SLOT_CAL 寄存器的值来决定要处理哪个 interface NO 里面

的 packets。

�

[5:0] calslot 要映射给一个 interface 的 calendar slot NO:0~calLen

[11:8] IfNum 被分配给 calslot field 设置的 calendar slot 的 interface NO:0~9

[21:16] callen

应是1~64的 length

calendar 是一个 ring,这是表示该 ring 的最大长度,有效值为0~63,对

ingress 先读 calslot0对应的 interface 的 MacFIFO,如果其中有 data,切 interface FIFO

还有 credit,它就会传16byte packet data 到 interface FIFO,然后移到下一个 calslot

(每过一个 cpu cycle 切换一次),直到到达 calslot callen 后又重新从 calslot 0开始。

credit 由硬件来控制,他会在 data 写入 interface FIFO 完成后增加 credit,每个 interface

的 credit 必须比 IFACE_FIFO_CFG 中指定的每个 interface 的 FIFO carving(FifoSize)

要少4,以确保 interface FIFO 不会 overrun。

这 个 calendar 的 加 入 是 为 了 让 不 同 interface 尽 可 能 都 被 处 理 到 , 推 荐 设 置 是 相 邻

calendar slot 对应的 interface 尽可能均匀地散布,以避免其他 interface 的 MacFIFO 溢

出。所以一般临近的 calendar slot 会有不同的 IfNum,这样 NAE 不会在连续的 cycle 只处

理相同的 interface。

其实 calendar slot 代表一个 interface 的16byte 数据传输窗口 across ingress Net-IO

�

Ring(NETIO)

interface FIFO 上的 credit,每个 credit 也代表一个 interface 的16byte 的数据传输,

credit 在 NETIOR_MISC_CTRL2/3中指定。

这个不断循环的东西叫 NAE's token-based ring。

interface FIFO

interface FIFO 被分成256个 entry,每个64byte-->16KB,该 FIFO 不支持 spill(???)。

IFACE_FIFO_CFG 寄存器来控制把这256个 entry 分配给10个 interface。

�

[3:0] index

interface NO,有效值:0~9

[15:8] fifostart 起始 entry,有效值:0~255

[24:16] fifosize 要分配给该 interface 的 entry 个数

[35:25] fifoXoffTh 当 interface FIFO word count 超过该 field 规定的门限时,基于

RXbuffer threshold 的 Xon/Xoff behavior 被 overriden

�

interface 与 context 的对应关系

对 XAUI 接口(需要4个 lane 组成),只有 base interface number(我也理解为 lane number)

用于配置,所以 PHY quads 与 base interface number 之间的对应关系为:

PHY Quad 0A:base interface number=0

PHY Quad 0B:base interface number=4

PHY Quad 1A:base interface number=0

PHY Quad 1B:base interface number=4

对 interlaken 接口(需要8个 lane 组成):

PHY Quad 0A+0B:base interface number=0

PHY Quad 1A+1B:base interface number=0

context 把 interface 分成了 sub-interface。

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc