simultaneous users

applications.

• Quad-stream spatial multiplexing to 4.8 Gbps

data rate.

IEEE 802.11a/b/g/n/ax, 4×4 160 MHz channels.

FEATURES

•

• Dual-Band OFDMA allows for a higher density of

IEEE 802.11ax compliant.

•

• 1024-QAM modulation rates.

• 4×4 MU-MIMO on 80 MHz channels.

• Expanded 5 GHz frequency coverage including

spectrum up to 5925 MHz expected to become

available under new regulatory rules.

Advance Data Sheet

BCM43684

IEEE 802.11ax 4x4 2.4/5 GHz Single-Chip MAC/PHY/Radio

GENERAL DESCRIPTION

The Broadcom® BCM43684 is a dual-band (2.4 GHz

and 5 GHz) 4×4 IEEE 802.11ax MAC/PHY/Radio

System-on-a-Chip (SoC). The device enables the

development of advanced high-efficiency wireless

(HE) 802.11ax Access points, repeaters, and WLAN

client solutions.

IEEE 802.11ax introduces Orthogonal Frequency-

Division Multiple Access (OFDMA) to enhance the

multi-user experience. It is an evolutionary step

forward from IEEE 802.11ac in that it allows multi-

client transmissions in both the uplink and downlink

directions. OFDMA multiplexes clients across

frequency instead of spatial streams to allow for more

concurrent users than MU-MIMO. BSS Coloring

allows for better spatial reuse by differentiating

Inter-BSS traffic from Intra-BSS traffic, and deferring

to Inter-BSS traffic at a higher threshold level. Target

Wake Time saves battery life in associated clients, by

scheduling Wake Up and Service Periods for STA to

be active.

The BCM43684 supports 160 MHz channels and

IEEE standardized 1024-QAM modulation. These,

combined with a 4x longer OFDM symbol length,

allow for a maximum PHY rate of 4.8 Gbps.

IEEE 802.11ax is backward compatible to previous

generations and supports MU-MIMO from IEEE

802.11ac.

State-of-the-art security is provided by industry

standardized system support for WPA, WPA2 (IEEE

802.11i), and hardware accelerated AES encryption/

decryption, coupled with TKIP and IEEE 802.1X

support.

Embedded hardware acceleration enables increased

system performance and significant reduction in host-

CPU utilization in both client and access point (AP)

configurations. The BCM43684 also supports the

widely accepted and deployed Broadcom Wi-Fi

Protected Setup (WPS) for ease-of-use wireless

secured networks.

• CQI and CSI can be captured and passed to the

Host along with the MAC address associated with

the captured data.

• Complies with PCI Express base specification

revision 2.0 for ×2 lane and power management

base specification.

• Comprehensive wireless network security

support that includes WPA, WPA2, and AES

encryption/decryption.

• Supports full-host CPU IEEE 802.11 packet offload.

• Available in a 13 mm × 13 mm, 284-pin 0.65 mm

• Supports Digital Pre-Distortion (DPD) which

reduces power consumption and improves Band

Edge performance.

• Full IEEE 802.11a/b/g/n/ac legacy compatibility

• Supports Linux for access point and router

with enhanced performance.

• Supports RangeBoost technology.

• Support for LDPC in both TX and RX for

increased wireless coverage.

• 3+1 DSP-based Spectrum Capture and Zero Wait

DFS.

pitch (FCBGA) package.

APPLICATIONS

• High-performance IEEE 802.11ax access points,

routers, and home residential gateways.

• High-performance IEEE 802.11ax enterprise and

carrier class access points and business class

Integrated Service Routers.

Corporate Headquarters: San Jose, CA

3/27/2017 X8UKE

43684-DS100-R

March 10, 2017

�

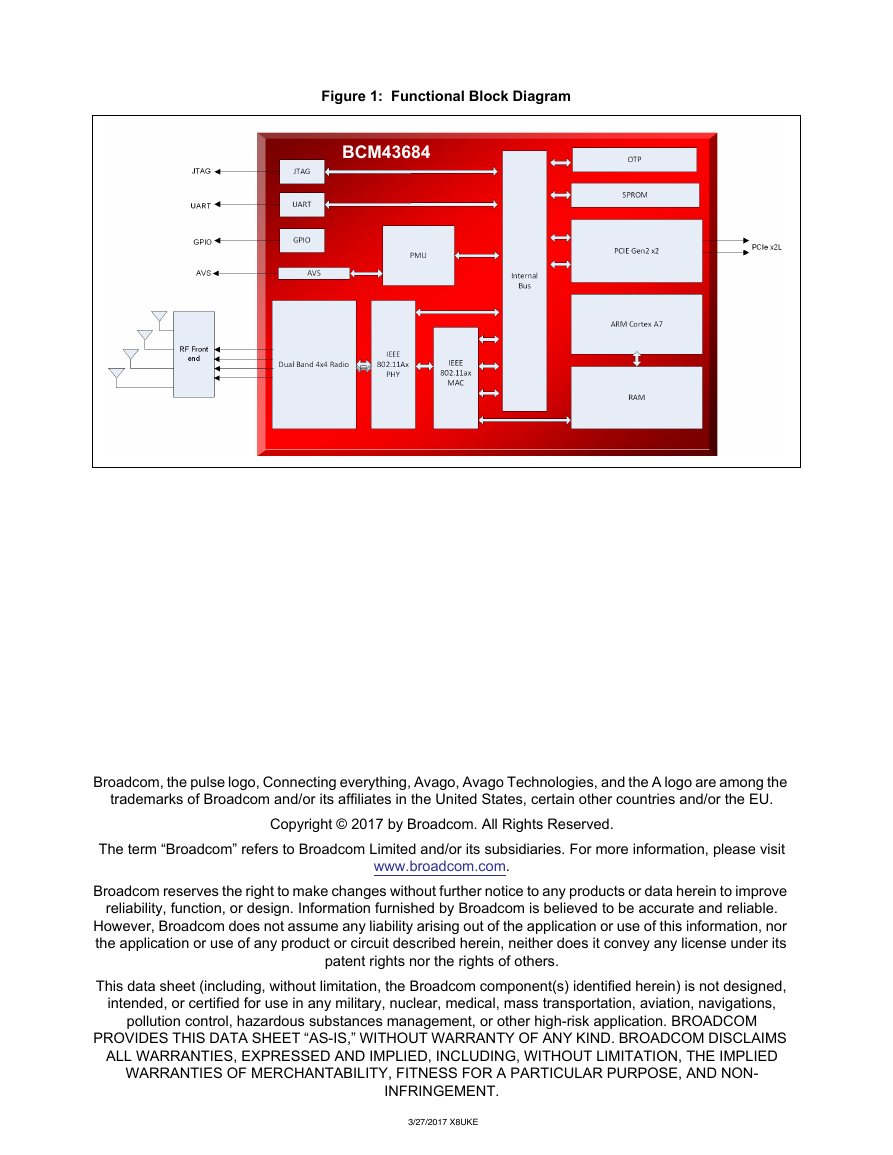

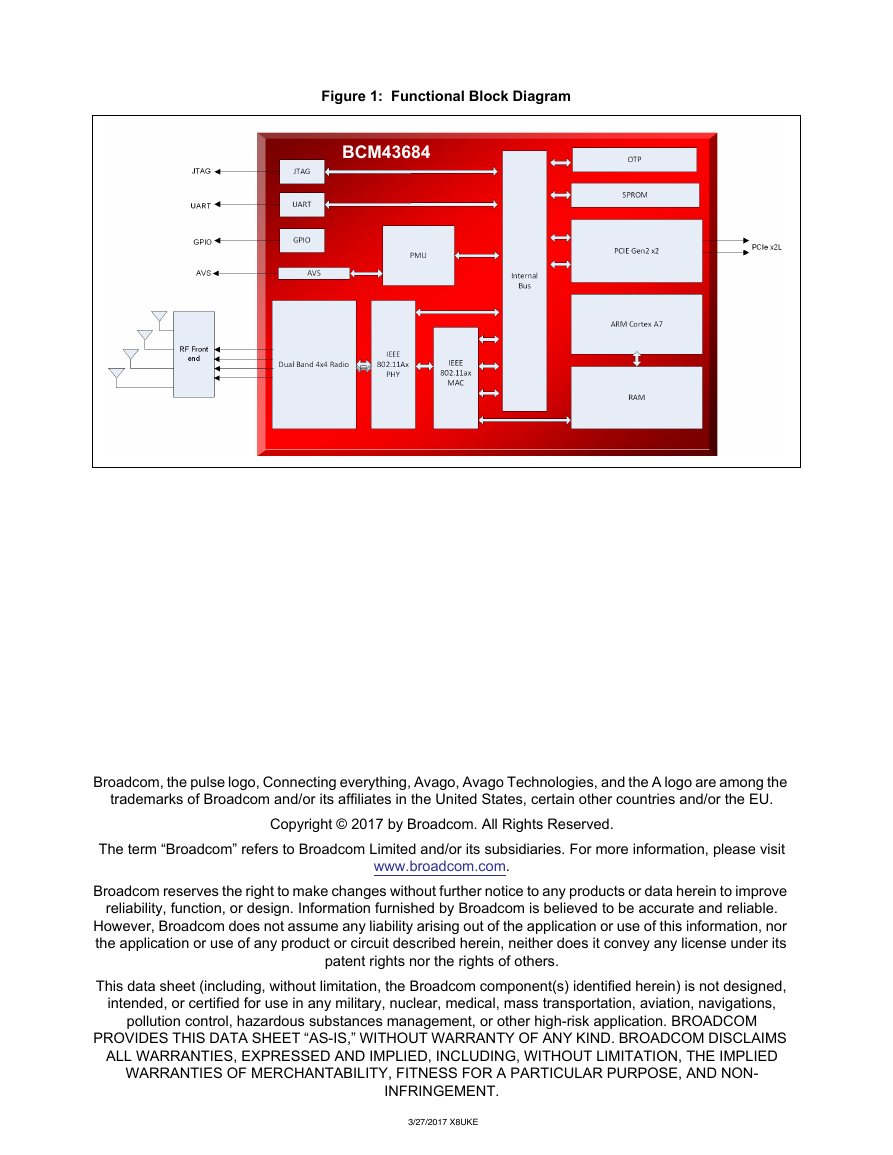

Figure 1: Functional Block Diagram

BCM43684

Broadcom, the pulse logo, Connecting everything, Avago, Avago Technologies, and the A logo are among the

trademarks of Broadcom and/or its affiliates in the United States, certain other countries and/or the EU.

Copyright © 2017 by Broadcom. All Rights Reserved.

The term “Broadcom” refers to Broadcom Limited and/or its subsidiaries. For more information, please visit

www.broadcom.com.

Broadcom reserves the right to make changes without further notice to any products or data herein to improve

reliability, function, or design. Information furnished by Broadcom is believed to be accurate and reliable.

However, Broadcom does not assume any liability arising out of the application or use of this information, nor

the application or use of any product or circuit described herein, neither does it convey any license under its

patent rights nor the rights of others.

This data sheet (including, without limitation, the Broadcom component(s) identified herein) is not designed,

intended, or certified for use in any military, nuclear, medical, mass transportation, aviation, navigations,

pollution control, hazardous substances management, or other high-risk application. BROADCOM

PROVIDES THIS DATA SHEET “AS-IS,” WITHOUT WARRANTY OF ANY KIND. BROADCOM DISCLAIMS

ALL WARRANTIES, EXPRESSED AND IMPLIED, INCLUDING, WITHOUT LIMITATION, THE IMPLIED

WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, AND NON-

INFRINGEMENT.

3/27/2017 X8UKE

�

BCM43684 Advance Data Sheet

Revision History

For a comprehensive list of changes to this document, see the Revision History.

Broadcom®

March 10, 2017 • 43684-DS100-R

IEEE 802.11ax 4x4 2.4/5 GHz Single-Chip MAC/PHY/Radio

Page 3

BROADCOM CONFIDENTIAL

3/27/2017 X8UKE

�

BCM43684 Advance Data Sheet

Table of Contents

Table of Contents

Section 1: Introduction ....................................................................................................... 6

General Description ..................................................................................................................................... 6

Features .................................................................................................................................................. 7

Applications............................................................................................................................................. 7

Functional Block Diagram ....................................................................................................................... 8

OFDMA (HE) Technology ....................................................................................................................... 9

Section 2: Functional Description ................................................................................... 10

Global Functions ........................................................................................................................................ 10

Power Management .............................................................................................................................. 10

Voltage Regulators................................................................................................................................ 10

AVS Section .......................................................................................................................................... 10

Reset..................................................................................................................................................... 10

GPIO Interface ...................................................................................................................................... 11

Smart Antenna Subsystem Interface..................................................................................................... 11

UART Interface...................................................................................................................................... 11

OTP....................................................................................................................................................... 11

SPROM Interface .................................................................................................................................. 11

JTAG Interface ...................................................................................................................................... 12

SWD Interface....................................................................................................................................... 12

Crystal Oscillator ................................................................................................................................... 12

Fundamental Crystal Oscillator Mode ................................................................................................... 13

Fundamental Crystal Example .............................................................................................................. 14

Host CPU Offload Support .................................................................................................................... 14

Power Topology .................................................................................................................................... 15

PCI Express Interface................................................................................................................................. 17

Transaction Layer Interface................................................................................................................... 18

Data Link Layer ..................................................................................................................................... 18

Physical Layer....................................................................................................................................... 18

Logical Subblock ................................................................................................................................... 18

Scrambler/Descrambler......................................................................................................................... 18

8B/10B Encoder/Decoder...................................................................................................................... 19

Elastic FIFO........................................................................................................................................... 19

Electrical Subblock................................................................................................................................ 19

Configuration Space.............................................................................................................................. 19

IEEE 802.11ax MAC Description ............................................................................................................... 20

IEEE 802.11 PHY Description .................................................................................................................... 22

Broadcom®

March 10, 2017 • 43684-DS100-R

IEEE 802.11ax 4x4 2.4/5 GHz Single-Chip MAC/PHY/Radio

Page 4

BROADCOM CONFIDENTIAL

3/27/2017 X8UKE

�

BCM43684 Advance Data Sheet

Table of Contents

Dual-Band Radio Transceiver ............................................................................................................... 23

Receiver Path................................................................................................................................. 23

Transmitter Path............................................................................................................................. 23

Calibration...................................................................................................................................... 23

Section 3: BGA Ball Assignments ................................................................................... 24

Ballout Diagram.......................................................................................................................................... 24

Ball and Signal Definitions ........................................................................................................................ 25

Signals by Signal Name ........................................................................................................................ 29

Section 4: Signal and Pin Descriptions........................................................................... 33

Package Signal Descriptions .................................................................................................................... 33

Strapping Options ...................................................................................................................................... 40

Section 5: RF Specifications ............................................................................................ 41

Introduction................................................................................................................................................. 41

WLAN.................................................................................................................................................... 41

2.4 GHz Band General RF Specifications............................................................................................. 42

WLAN 2.4 GHz Receiver Performance Specifications.......................................................................... 42

WLAN 2.4 GHz Transmitter Performance Specifications ....................................................................... 46

WLAN 5 GHz Receiver Performance Specifications ............................................................................... 47

WLAN 5 GHz Transmitter Performance Specifications .......................................................................... 50

General Spurious Emissions Specifications ........................................................................................... 51

Section 6: Electrical Characteristics ............................................................................... 52

Absolute Maximum Ratings ...................................................................................................................... 52

Recommended Operating Conditions and DC Characteristics ............................................................. 53

Section 7: Timing Characteristics.................................................................................... 54

Power Sequence Timing............................................................................................................................ 54

SPROM Timing Diagram ............................................................................................................................ 56

PCI Express Parameters............................................................................................................................ 57

Section 8: Thermal information........................................................................................ 59

Junction Temperature Estimation and PSIJT Versus ThetaJC................................................................ 59

Section 9: Package Information ....................................................................................... 60

Section 10: Ordering Information .................................................................................... 61

Revision History ......................................................................................................................................... 62

Broadcom®

March 10, 2017 • 43684-DS100-R

IEEE 802.11ax 4x4 2.4/5 GHz Single-Chip MAC/PHY/Radio

Page 5

BROADCOM CONFIDENTIAL

3/27/2017 X8UKE

�

BCM43684 Advance Data Sheet

Introduction

Section 1: Introduction

General Description

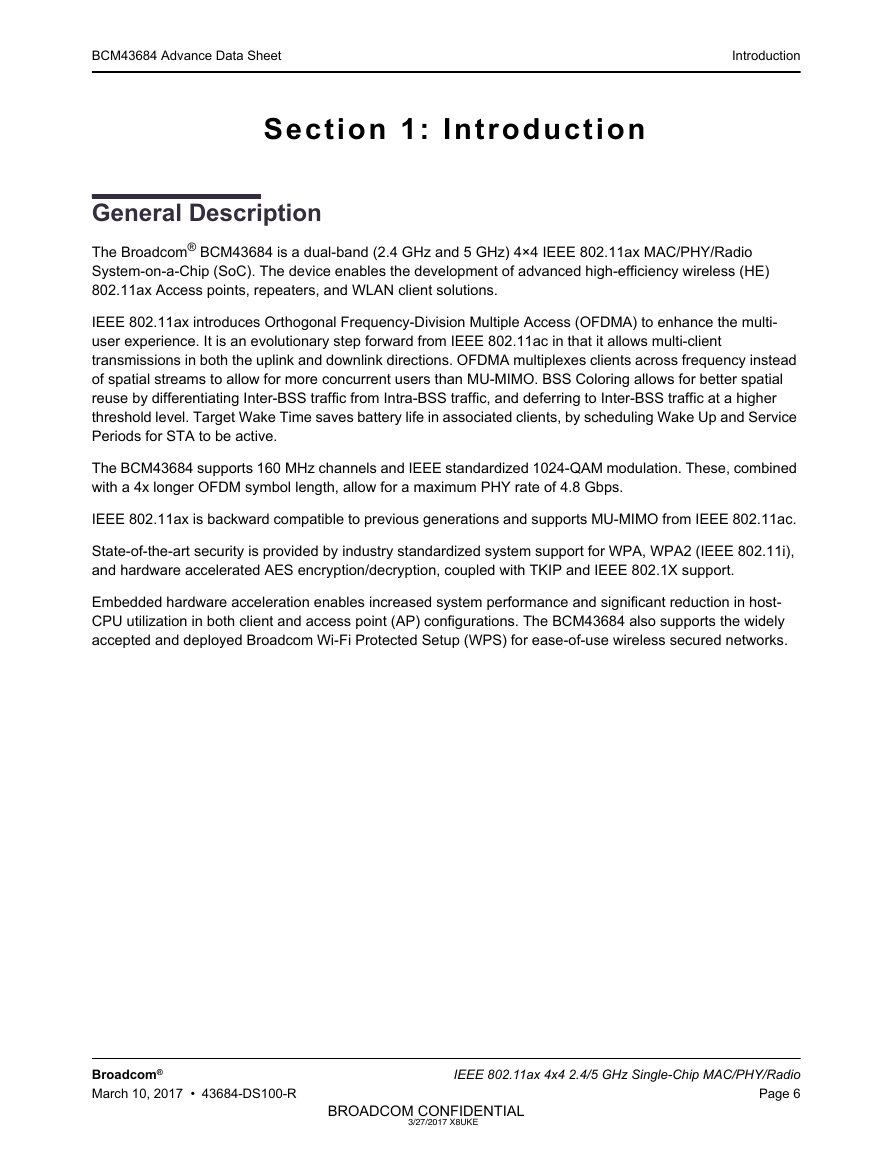

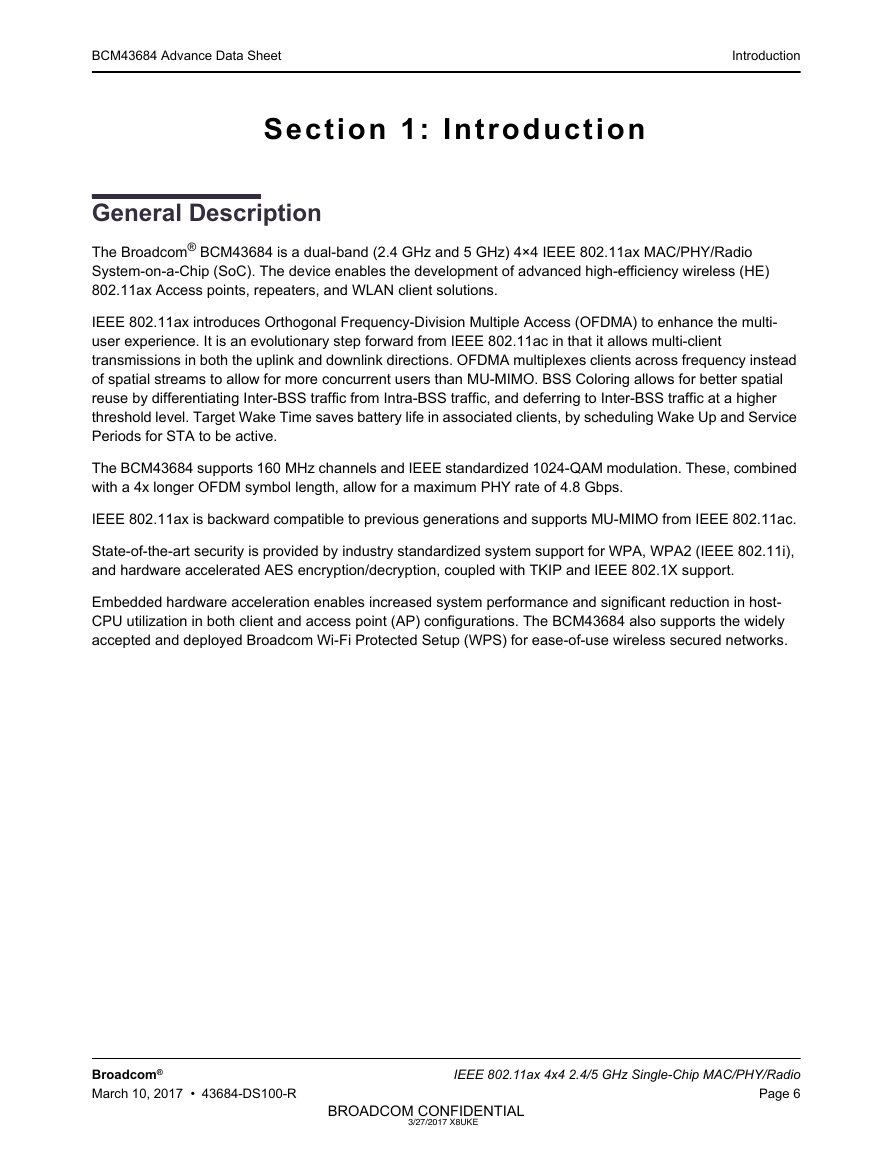

The Broadcom® BCM43684 is a dual-band (2.4 GHz and 5 GHz) 4×4 IEEE 802.11ax MAC/PHY/Radio

System-on-a-Chip (SoC). The device enables the development of advanced high-efficiency wireless (HE)

802.11ax Access points, repeaters, and WLAN client solutions.

IEEE 802.11ax introduces Orthogonal Frequency-Division Multiple Access (OFDMA) to enhance the multi-

user experience. It is an evolutionary step forward from IEEE 802.11ac in that it allows multi-client

transmissions in both the uplink and downlink directions. OFDMA multiplexes clients across frequency instead

of spatial streams to allow for more concurrent users than MU-MIMO. BSS Coloring allows for better spatial

reuse by differentiating Inter-BSS traffic from Intra-BSS traffic, and deferring to Inter-BSS traffic at a higher

threshold level. Target Wake Time saves battery life in associated clients, by scheduling Wake Up and Service

Periods for STA to be active.

The BCM43684 supports 160 MHz channels and IEEE standardized 1024-QAM modulation. These, combined

with a 4x longer OFDM symbol length, allow for a maximum PHY rate of 4.8 Gbps.

IEEE 802.11ax is backward compatible to previous generations and supports MU-MIMO from IEEE 802.11ac.

State-of-the-art security is provided by industry standardized system support for WPA, WPA2 (IEEE 802.11i),

and hardware accelerated AES encryption/decryption, coupled with TKIP and IEEE 802.1X support.

Embedded hardware acceleration enables increased system performance and significant reduction in host-

CPU utilization in both client and access point (AP) configurations. The BCM43684 also supports the widely

accepted and deployed Broadcom Wi-Fi Protected Setup (WPS) for ease-of-use wireless secured networks.

Broadcom®

March 10, 2017 • 43684-DS100-R

IEEE 802.11ax 4x4 2.4/5 GHz Single-Chip MAC/PHY/Radio

Page 6

BROADCOM CONFIDENTIAL

3/27/2017 X8UKE

�

BCM43684 Advance Data Sheet

General Description

IEEE 802.11ax compliant.

Features

•

• Dual-Band OFDMA allows for a higher density of simultaneous users.

• Quad-stream spatial multiplexing to 4.8 Gbps data rate.

•

• 1024-QAM modulation rates.

• 4×4 MU-MIMO on 80 MHz channels.

• Expanded 5 GHz frequency coverage including spectrum up to 5925 MHz expected to become available

IEEE 802.11a/b/g/n/ax, 4×4 160 MHz channels.

under new regulatory rules.

• Supports RangeBoost technology.

• Support for LDPC in both TX and RX for increased wireless coverage.

• 3+1 DSP-based Spectrum Capture and Zero Wait DFS.

• CQI and CSI can be captured and passed to the Host along with the MAC address associated with the

captured data.

• Supports Digital Pre-Distortion (DPD) which reduces power consumption and improves Band Edge

performance.

• Full IEEE 802.11a/b/g/n/ac legacy compatibility with enhanced performance.

• Complies with PCI Express base specification revision 2.0 for ×2 lane and power management base

specification.

• Supports Linux for access point and router applications.

• Comprehensive wireless network security support that includes WPA, WPA2, and AES encryption/

decryption.

• Supports full-host CPU IEEE 802.11 packet offload.

• Available in a 13 mm × 13 mm, 284-pin 0.65 mm pitch (FCBGA) package.

Applications

• High-performance IEEE 802.11ax access points, routers, and home residential gateways.

• High-performance IEEE 802.11ax enterprise and carrier class access points and business class Integrated

Service Routers.

Broadcom®

March 10, 2017 • 43684-DS100-R

IEEE 802.11ax 4x4 2.4/5 GHz Single-Chip MAC/PHY/Radio

Page 7

BROADCOM CONFIDENTIAL

3/27/2017 X8UKE

�

BCM43684 Advance Data Sheet

General Description

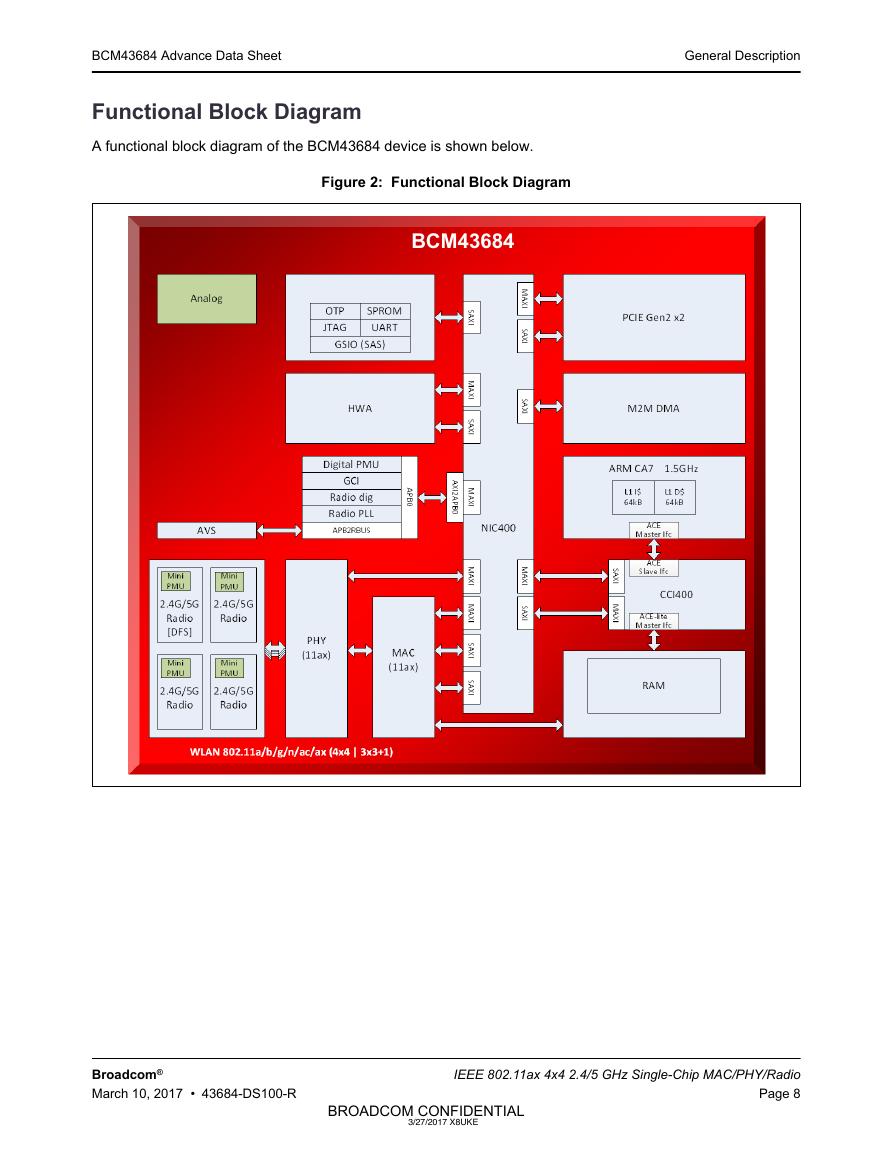

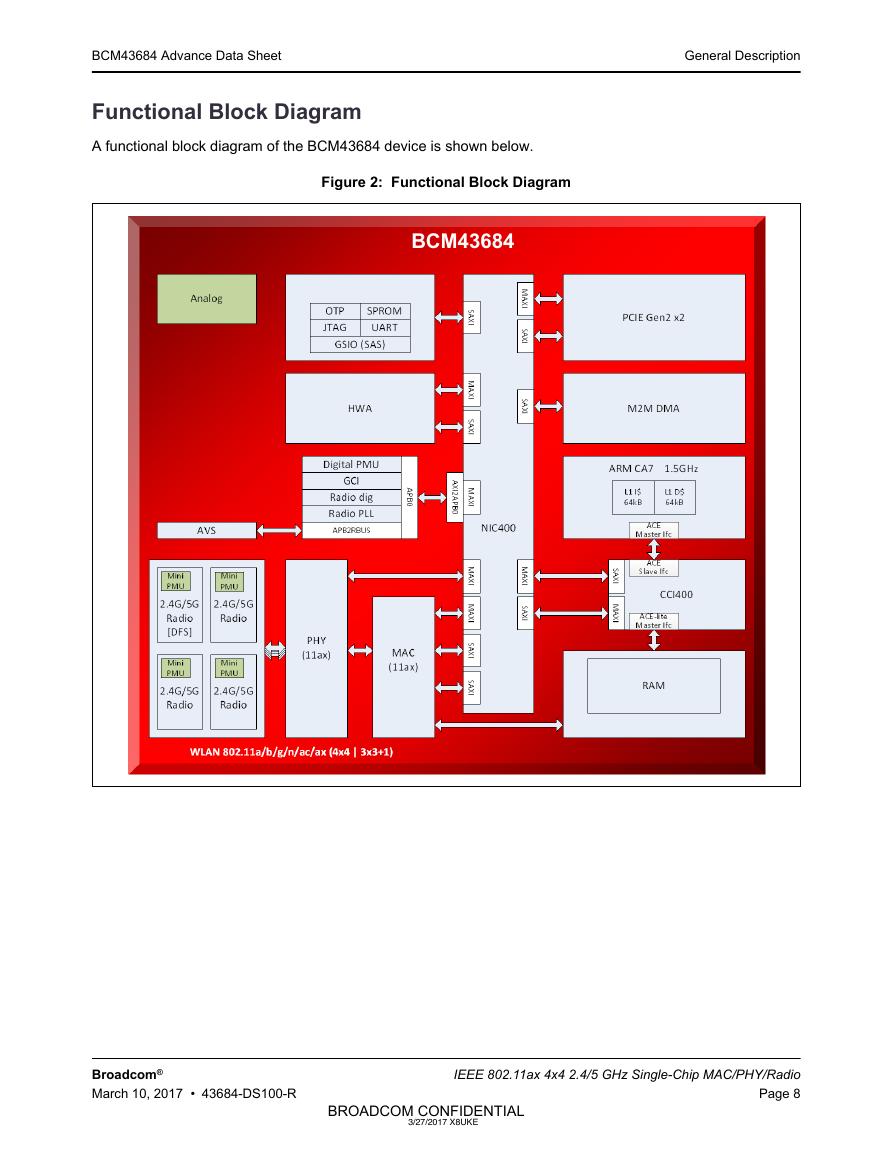

Functional Block Diagram

A functional block diagram of the BCM43684 device is shown below.

Figure 2: Functional Block Diagram

BCM43684

Broadcom®

March 10, 2017 • 43684-DS100-R

IEEE 802.11ax 4x4 2.4/5 GHz Single-Chip MAC/PHY/Radio

Page 8

BROADCOM CONFIDENTIAL

3/27/2017 X8UKE

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc