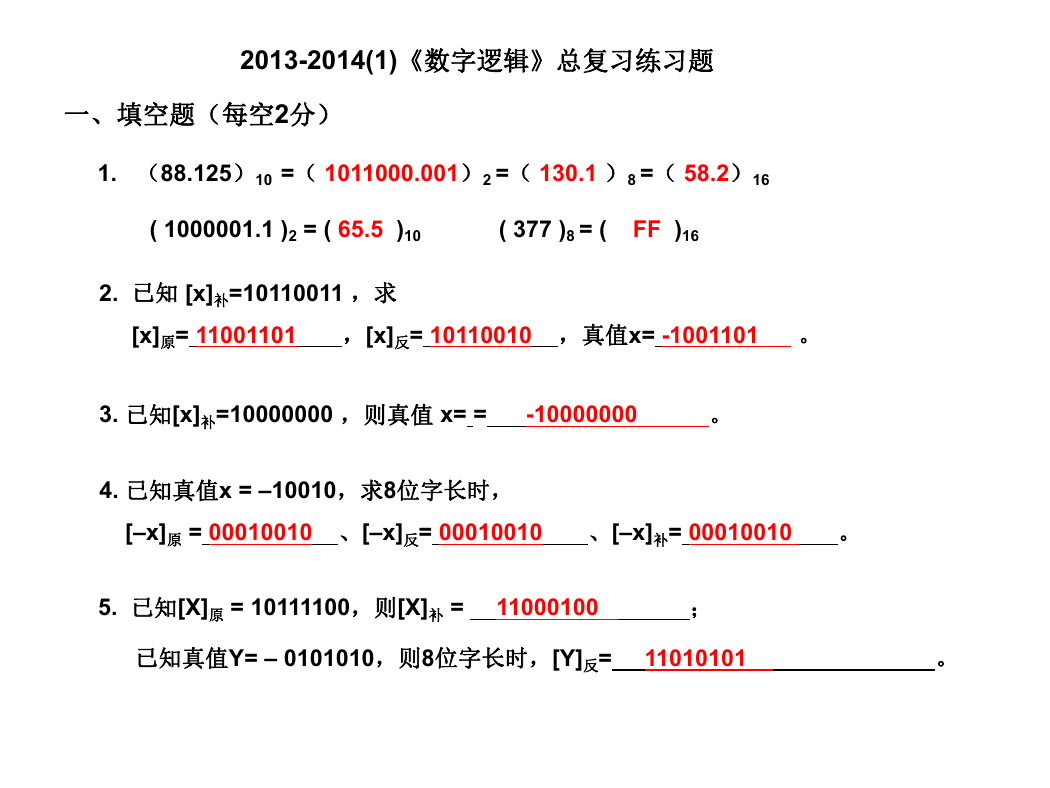

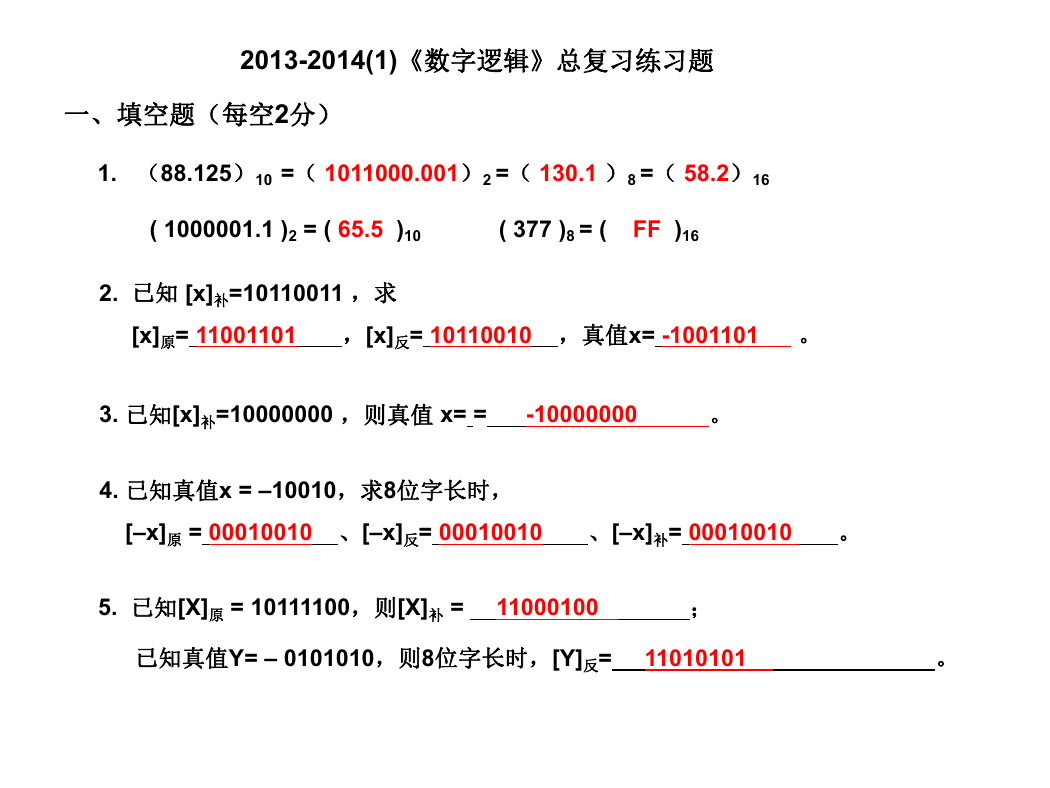

2013-2014(1)《数字逻辑》总复习练习题

一、填空题(每空2分)

1. (88.125)10 =( 1011000.001)2 =( 130.1 )8 =( 58.2)16

( 1000001.1 )2 = ( 65.5 )10 ( 377 )8 = ( FF )16

2. 已知 [x]补=10110011 ,求

[x]原= 11001101 ,[x]反= 10110010 ,真值x= -1001101 。

3. 已知[x]补=10000000 ,则真值 x= = -10000000 。

4. 已知真值x = –10010,求8位字长时,

[–x]原 = 00010010 、[–x]反= 00010010 、[–x]补= 00010010 。

5. 已知[X]原 = 10111100,则[X]补 = 11000100 ;

已知真值Y= – 0101010,则8位字长时,[Y]反= 11010101 。

�

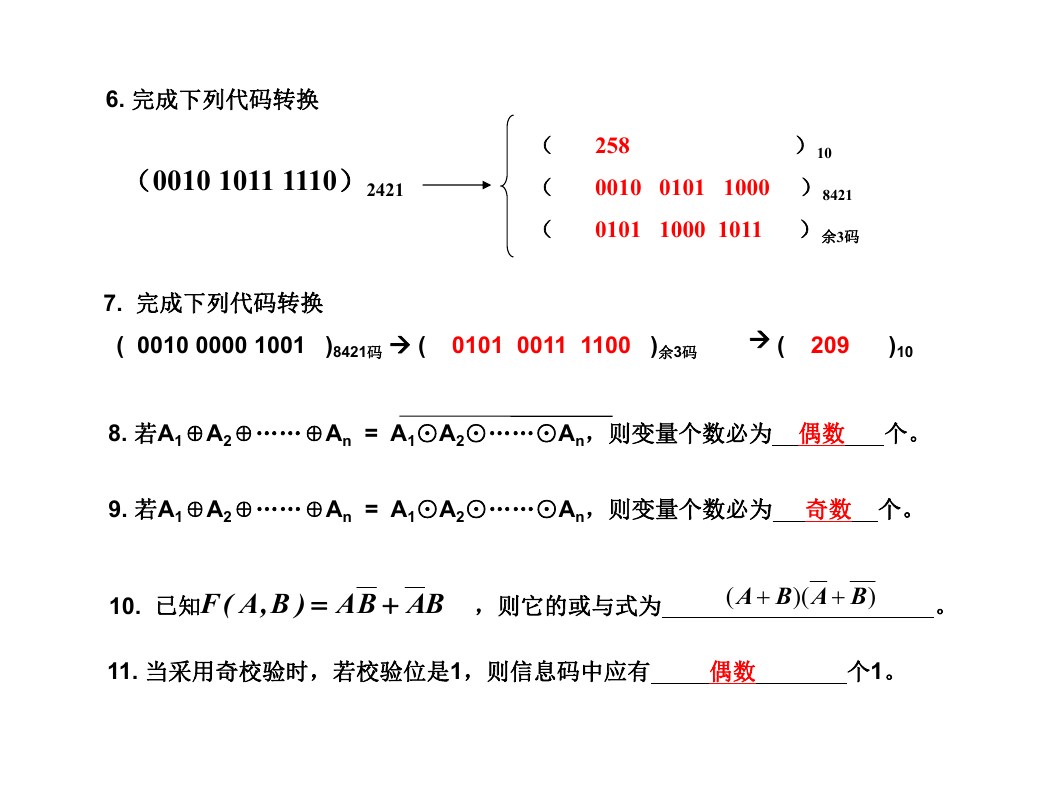

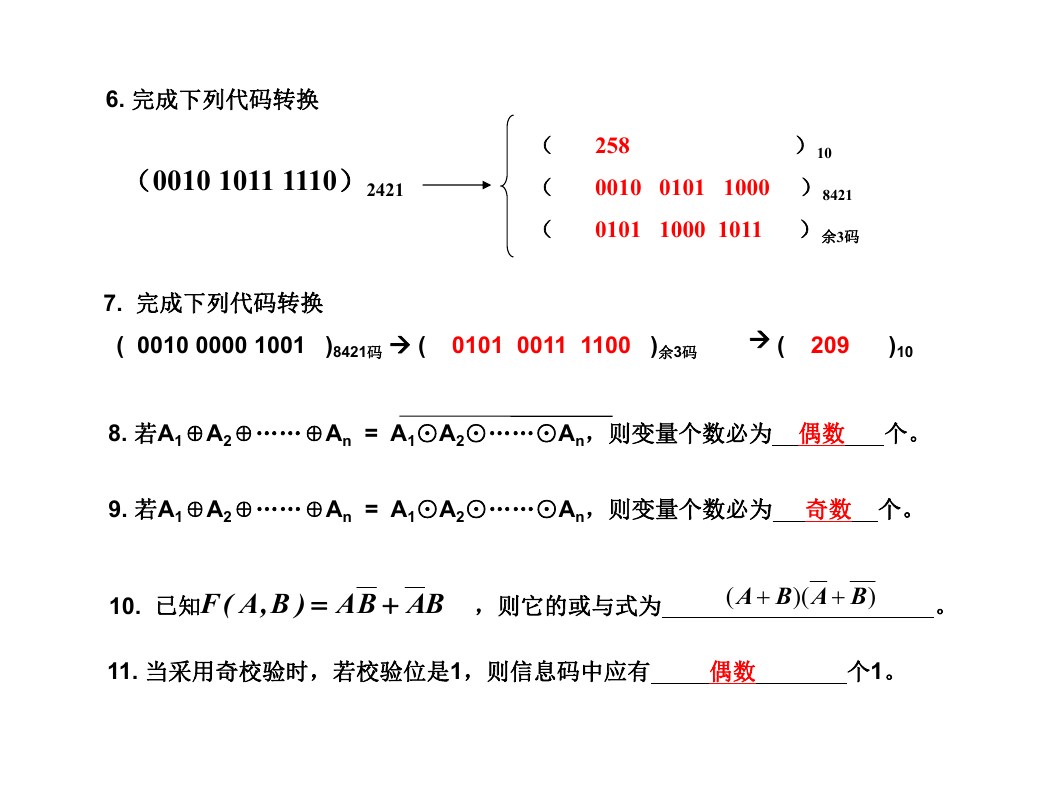

6. 完成下列代码转换

(0010 1011 1110)2421

( 258 )10

( 0010 0101 1000 )8421

( 0101 1000 1011 )余3码

7. 完成下列代码转换

( 0010 0000 1001 )8421码 ( 0101 0011 1100 )余3码 ( 209 )10

8. 若A1⊕A2⊕……⊕An = A1⊙A2⊙……⊙An,则变量个数必为 偶数 个。

9. 若A1⊕A2⊕……⊕An = A1⊙A2⊙……⊙An,则变量个数必为 奇数 个。

10. 已知 ,则它的或与式为 。

BABA)B,A(F

(

BABA

)(

)

11. 当采用奇校验时,若校验位是1,则信息码中应有 偶数 个1。

�

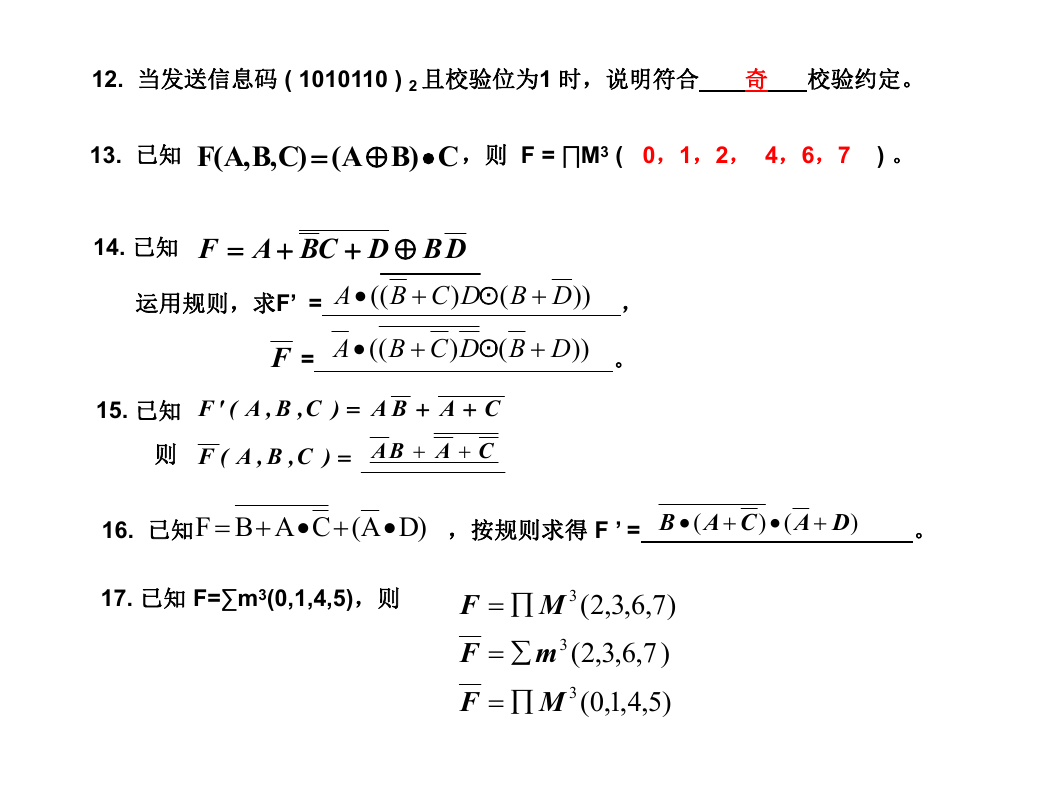

12. 当发送信息码 ( 1010110 ) 2 且校验位为1 时,说明符合 奇 校验约定。

13. 已知 ,则 F = ∏M3 ( 0,1,2, 4,6,7 ) 。

C)BA(

)C,B,A(F

14. 已知

运用规则,求F’ = ,

DBDCBAF

)

)

A

A

((

((

))

DBDCB

))

DBDCB

(

○·

(

○·

= 。

F

15. 已知

则

)C,B,A('F

)C,B,A(F

BA

BA

CA

CA

16. 已知 ,按规则求得 F ’ = 。

)DA(CABF

CAB

DA

)

(

)

(

17. 已知 F=∑m3(0,1,4,5),则

F

F

F

M

3

m

M

3

)7,6,3,2(

)7,6,3,2(

3

)5,4,1,0(

�

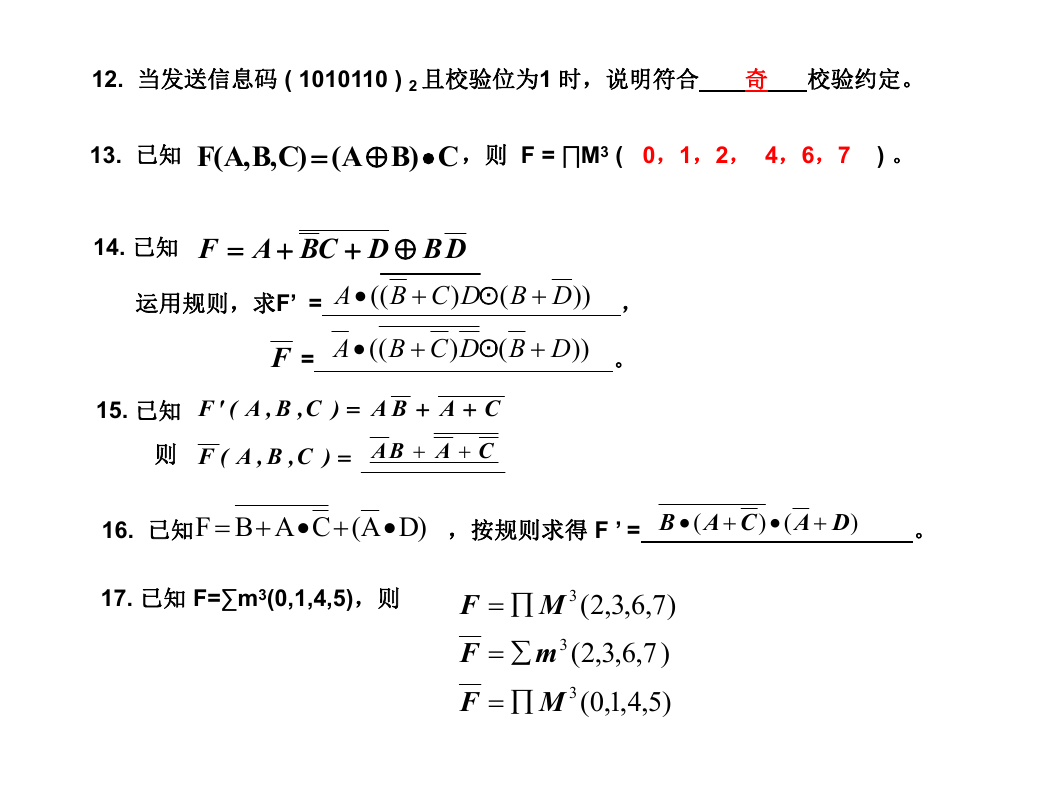

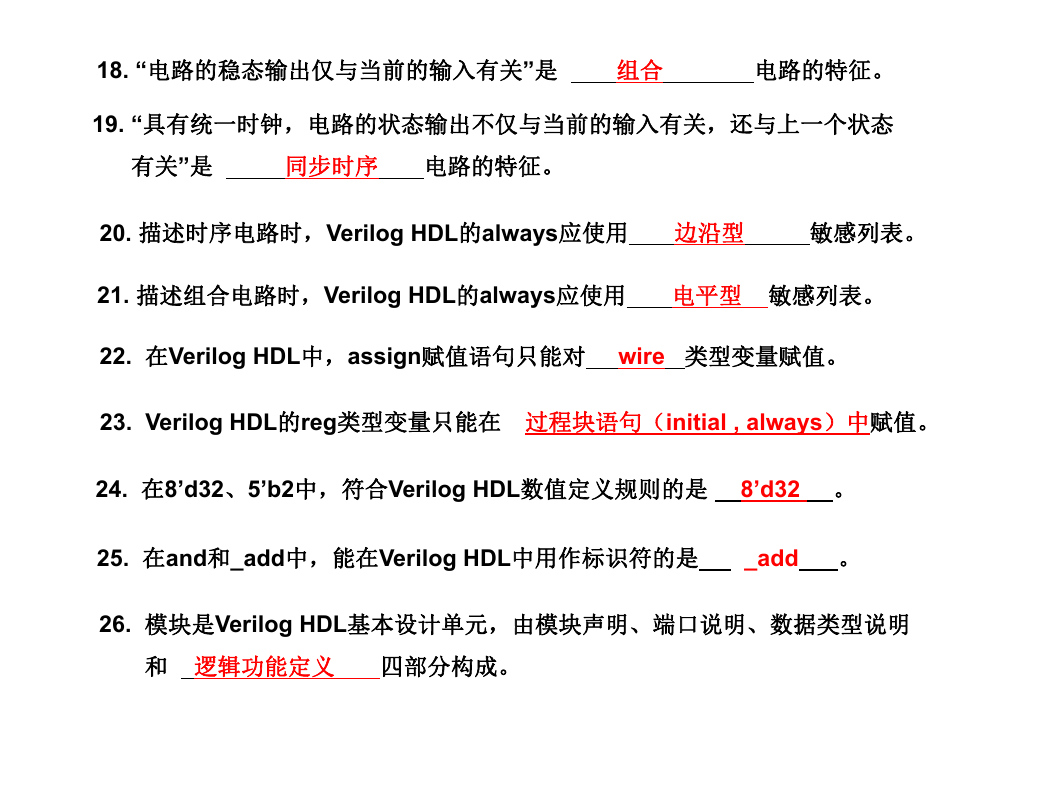

18. “电路的稳态输出仅与当前的输入有关”是 组合 电路的特征。

19. “具有统一时钟,电路的状态输出不仅与当前的输入有关,还与上一个状态

有关”是 同步时序 电路的特征。

20. 描述时序电路时,Verilog HDL的always应使用 边沿型 敏感列表。

21. 描述组合电路时,Verilog HDL的always应使用 电平型 敏感列表。

22. 在Verilog HDL中,assign赋值语句只能对 wire 类型变量赋值。

23. Verilog HDL的reg类型变量只能在在过程块语句(initial , always)中赋值。

24. 在8’d32、5’b2中,符合Verilog HDL数值定义规则的是 8’d32 。

25. 在and和_add中,能在Verilog HDL中用作标识符的是 _add 。

26. 模块是Verilog HDL基本设计单元,由模块声明、端口说明、数据类型说明

和 逻辑功能定义 四部分构成。

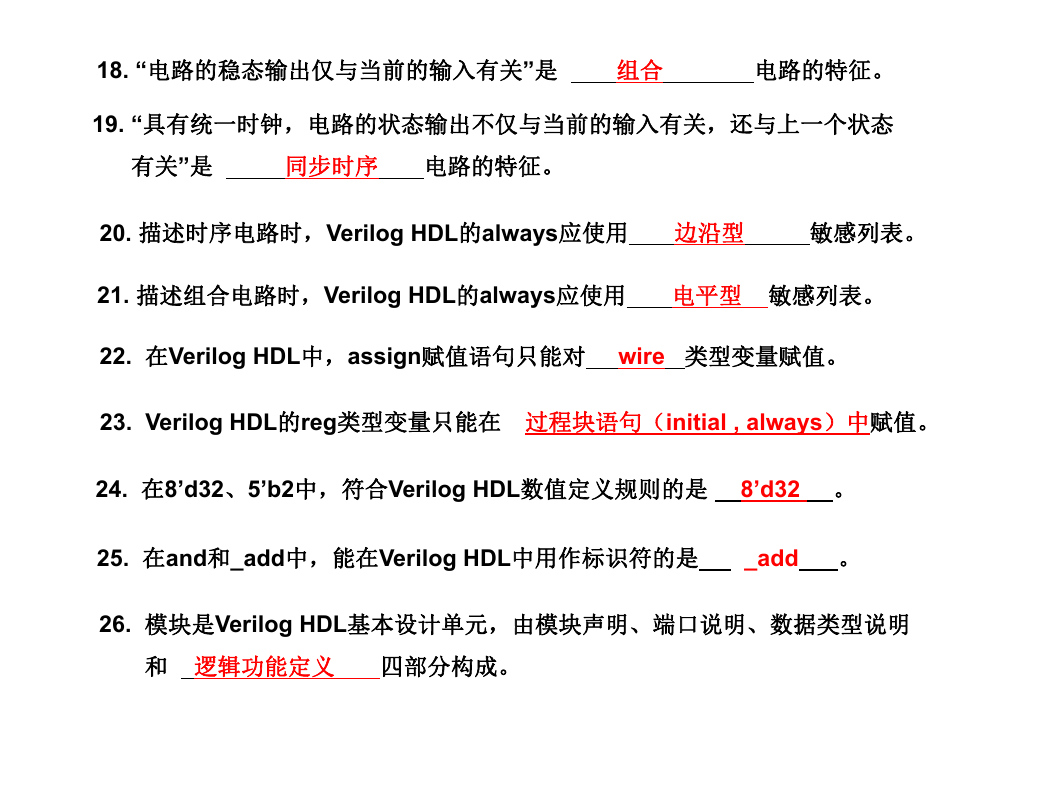

�

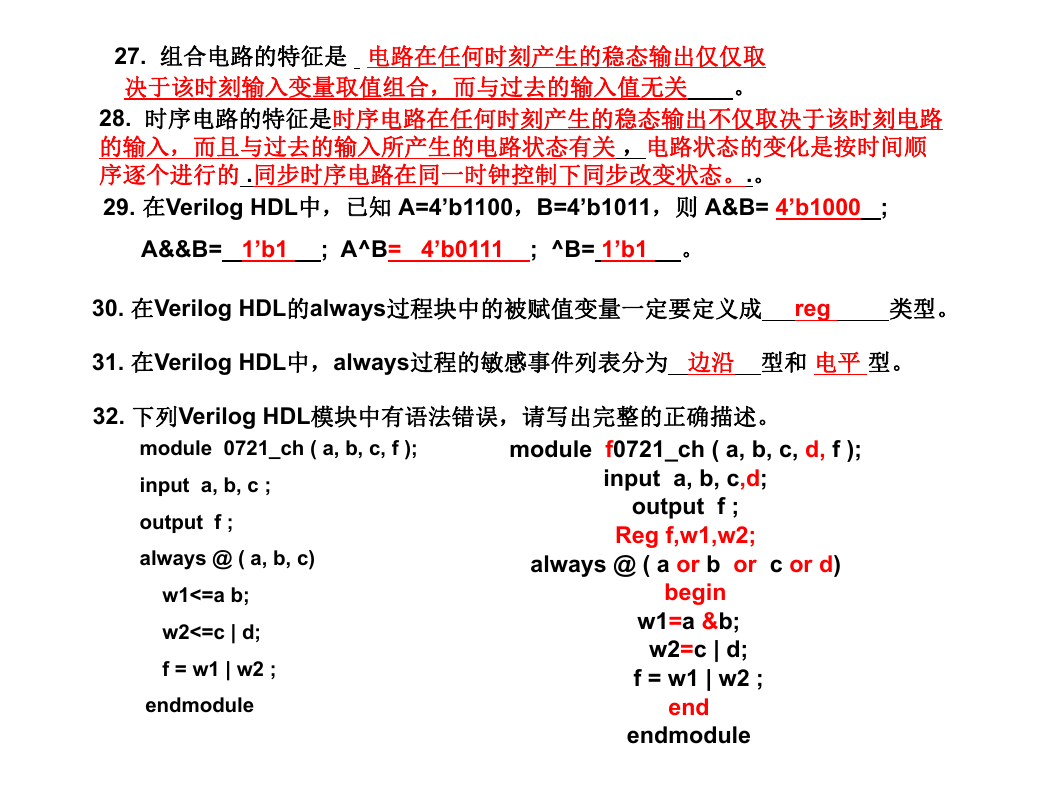

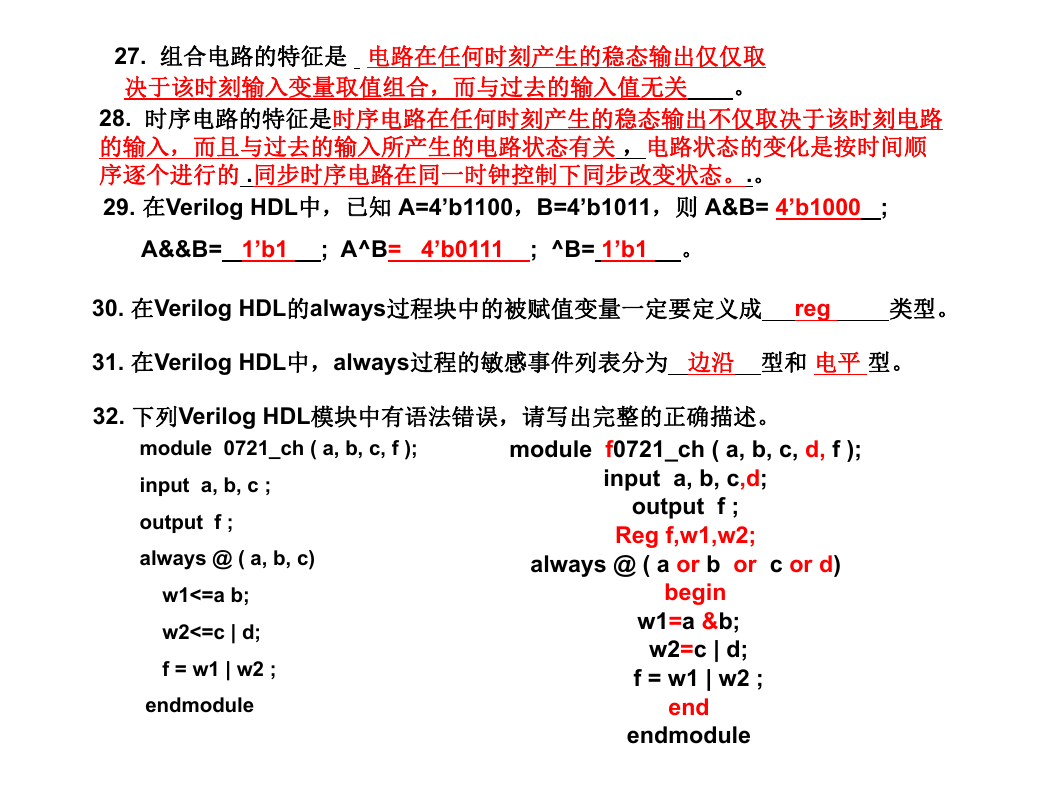

27. 组合电路的特征是 电路在任何时刻产生的稳态输出仅仅取

决于该时刻输入变量取值组合,而与过去的输入值无关 。

28. 时序电路的特征是时序电路在任何时刻产生的稳态输出不仅取决于该时刻电路

的输入,而且与过去的输入所产生的电路状态有关 ,电路状态的变化是按时间顺

序逐个进行的 .同步时序电路在同一时钟控制下同步改变状态。.。

29. 在Verilog HDL中,已知 A=4’b1100,B=4’b1011,则 A&B= 4’b1000 ;

A&&B= 1’b1 ; A^B= 4’b0111 ; ^B= 1’b1 。

30. 在Verilog HDL的always过程块中的被赋值变量一定要定义成 reg 类型。

31. 在Verilog HDL中,always过程的敏感事件列表分为 边沿 型和 电平 型。

32. 下列Verilog HDL模块中有语法错误,请写出完整的正确描述。

module f0721_ch ( a, b, c, d, f );

module 0721_ch ( a, b, c, f );

input a, b, c ;

output f ;

always @ ( a, b, c)

w1<=a b;

w2<=c | d;

f = w1 | w2 ;

endmodule

input a, b, c,d;

output f ;

Reg f,w1,w2;

always @ ( a or b or c or d)

begin

w1=a &b;

w2=c | d;

f = w1 | w2 ;

end

endmodule

�

二. 简答题(每题5分)

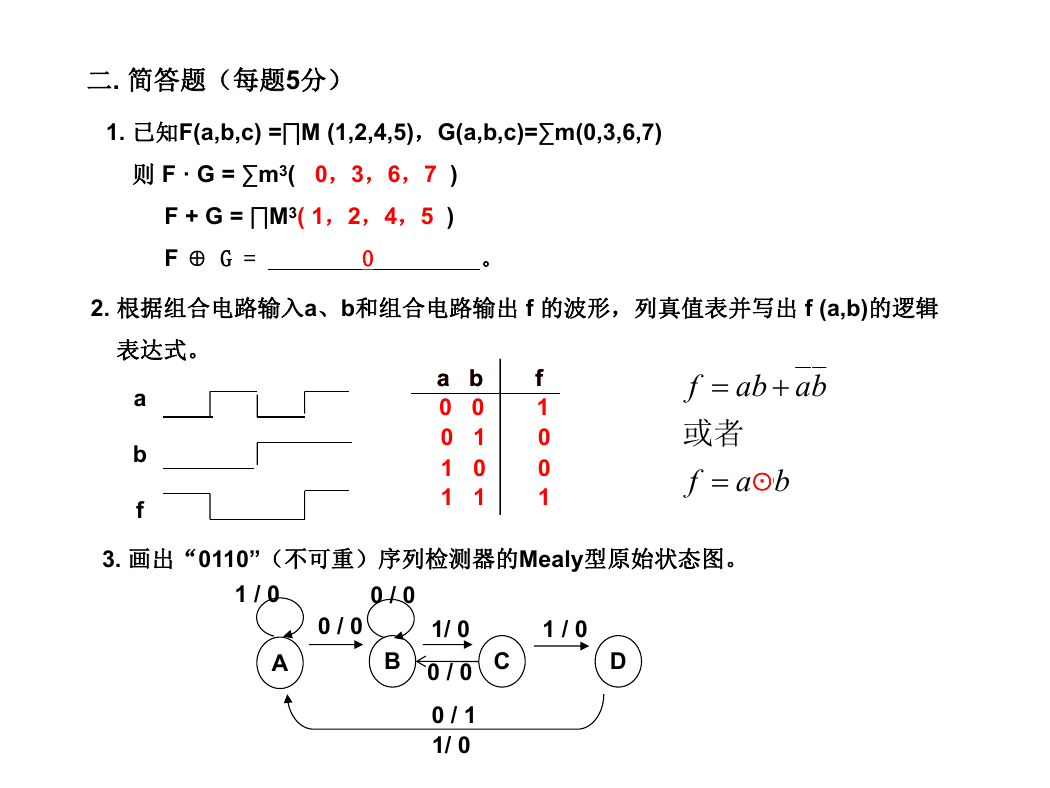

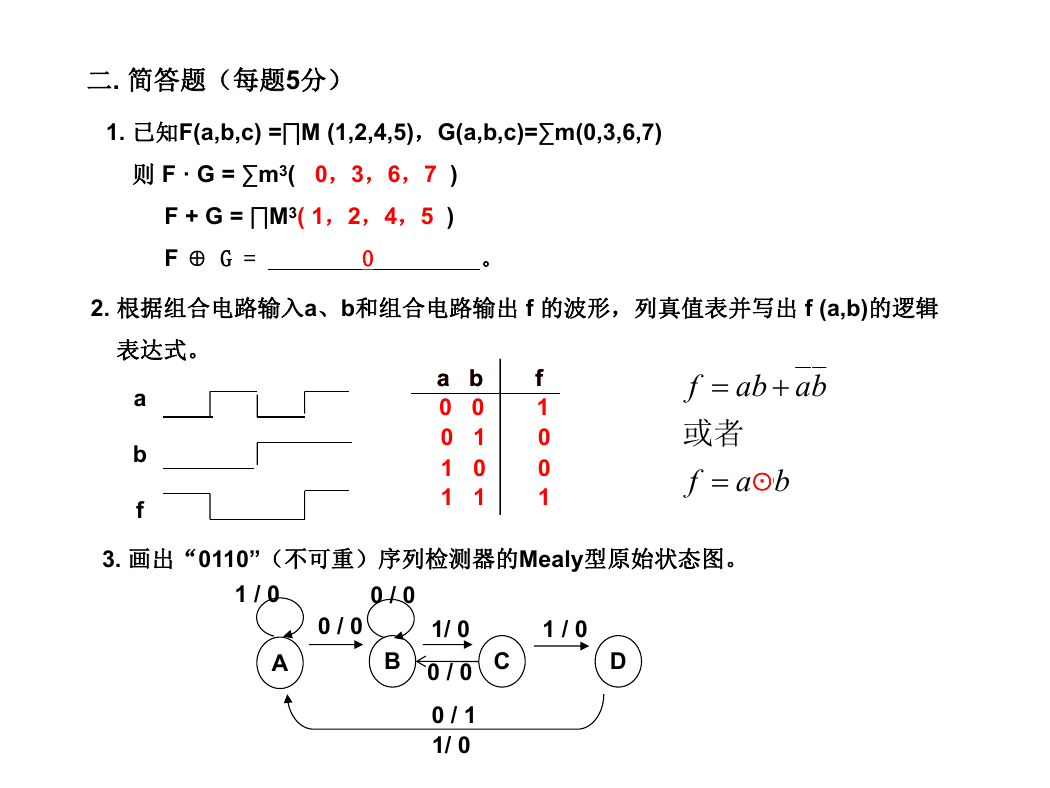

1. 已知F(a,b,c) =∏M (1,2,4,5),G(a,b,c)=∑m(0,3,6,7)

则 F · G = ∑m3( 0,3,6,7 )

F + G = ∏M3( 1,2,4,5 )

F ⊕ G = 0 。

2. 根据组合电路输入a、b和组合电路输出 f 的波形,列真值表并写出 f (a,b)的逻辑

表达式。

ab

ba

a

b

f

a b f

a b f

0 0 1

0 1 0

1 0 0

1 1 1

f

或者

f

ba

○·

3. 画出“0110”(不可重)序列检测器的Mealy型原始状态图。

1 / 0

A

0 / 0

0 / 0

B

1 / 0

D

C

1/ 0

0 / 0

0 / 1

1/ 0

�

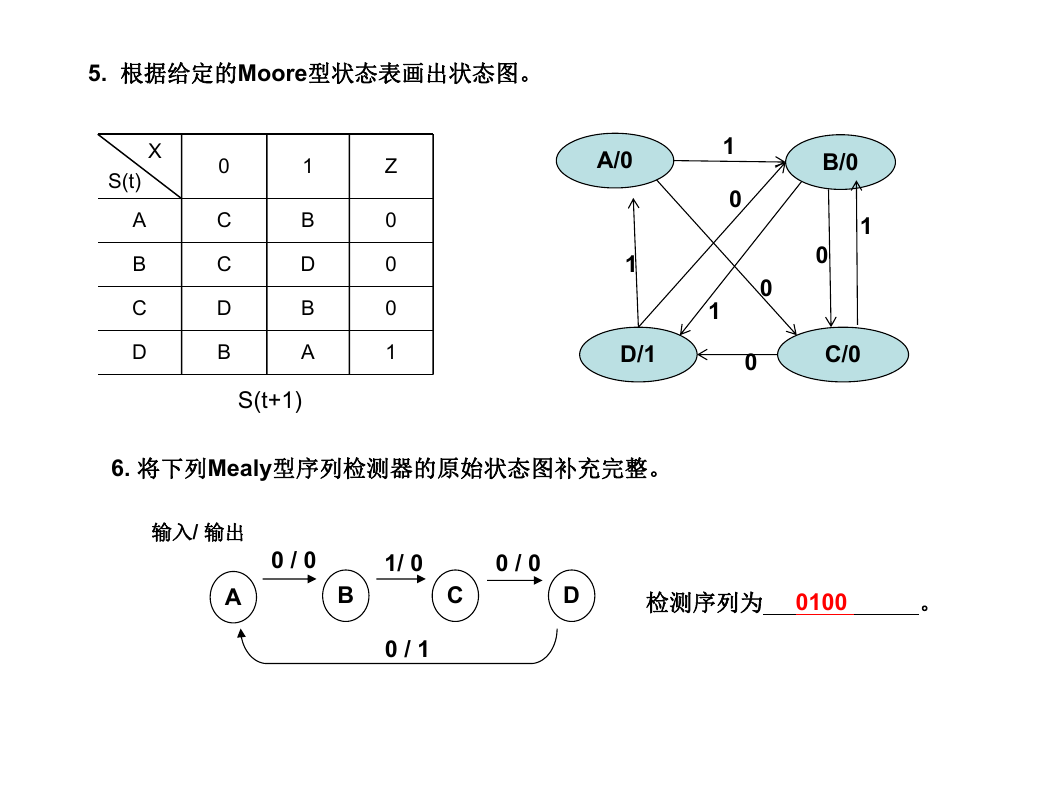

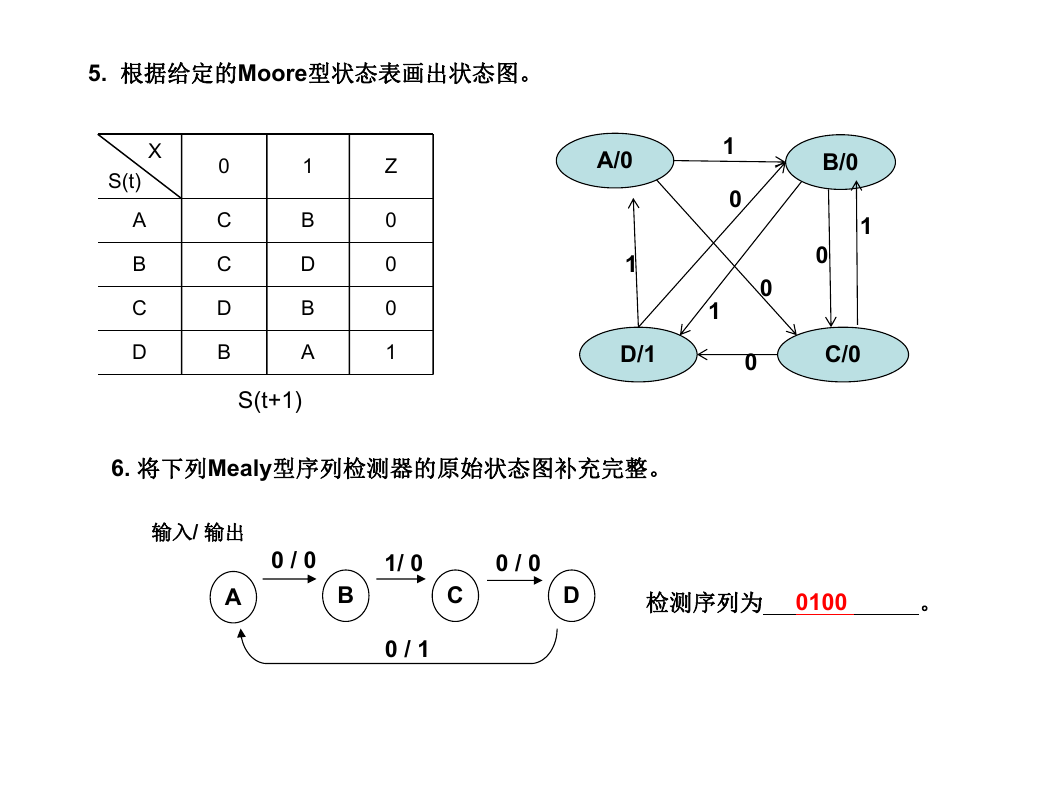

5. 根据给定的Moore型状态表画出状态图。

X

S(t)

A

B

C

D

0

C

C

D

B

1

B

D

B

A

Z

0

0

0

1

S(t+1)

A/0

1

D/1

1

0

1

0

0

B/0

1

0

C/0

6. 将下列Mealy型序列检测器的原始状态图补充完整。

输入/ 输出

0 / 0

A

B

0 / 0

D

C

1/ 0

0 / 1

检测序列为 0100 。

�

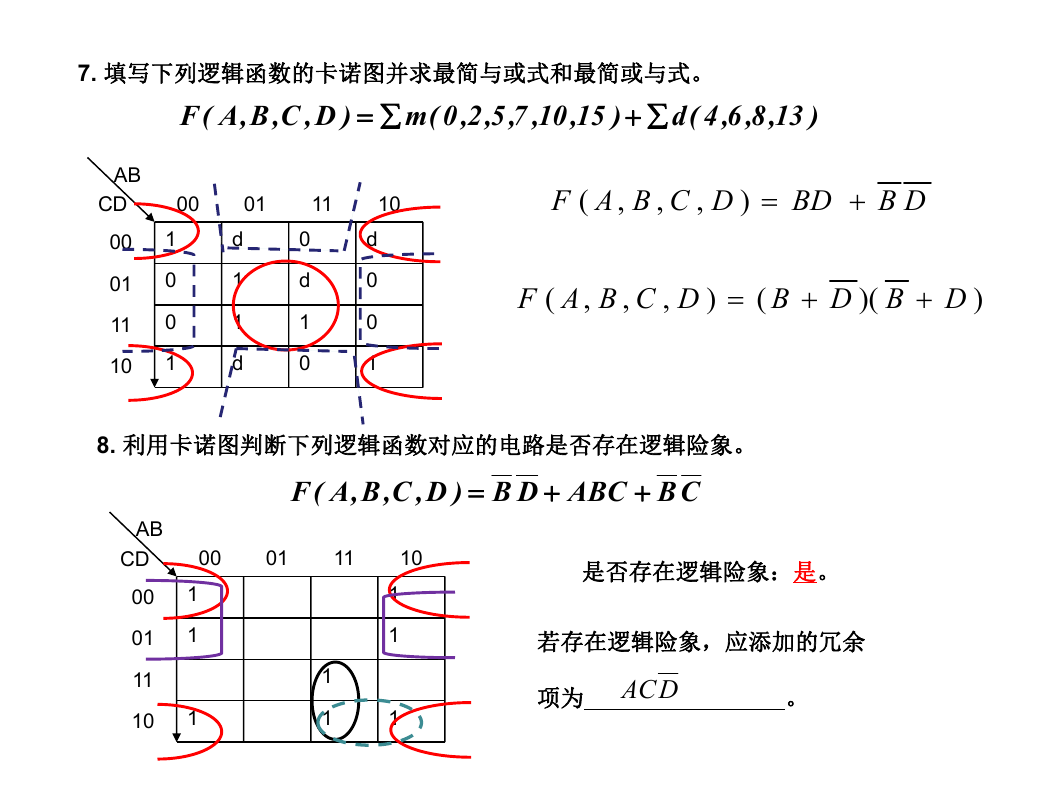

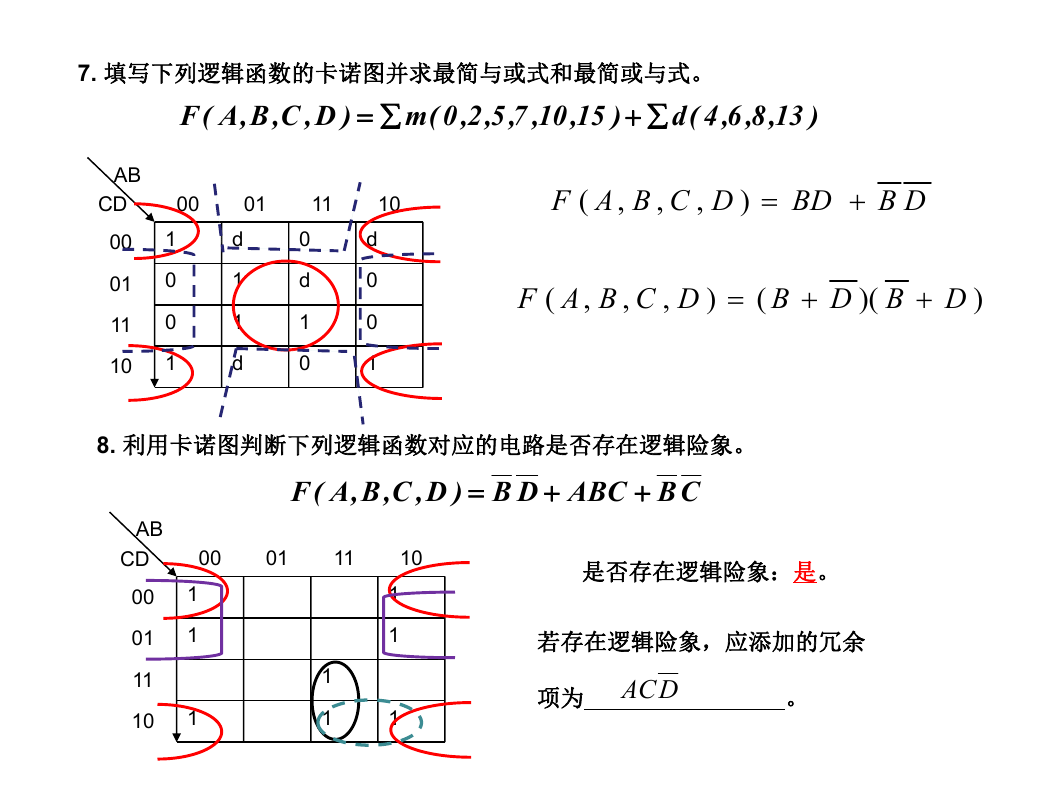

7. 填写下列逻辑函数的卡诺图并求最简与或式和最简或与式。

)D,C,B,A(F

)15,10,7,5,2,0(m

)13,8,6,4(d

AB

CD

00

01

11

10

1

0

0

1

00

01

11

10

d

1

1

d

0

d

1

0

d

0

0

1

DCBAF

(

,

,

,

)

BD

DB

DCBAF

(

,

,

,

)

(

DBDB

)(

)

8. 利用卡诺图判断下列逻辑函数对应的电路是否存在逻辑险象。

DB)D,C,B,A(F

ABC

CB

AB

CD

00

01

11

10

1

1

1

00

01

11

10

1

1

1

1

1

是否存在逻辑险象:是。

若存在逻辑险象,应添加的冗余

项为 。

DAC

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc