***

四位二进制加法器和乘法器

第 1页 共 17 页

1 引言

EDA(ElectronicDesign Automatic)技术的应用引起电子产品及系统开发的革命性

变革。VHDL语言作为可编程逻辑器件的标准语言描述能力强,覆盖面广,抽象能力强,

在实际应用中越来越广泛。

1.1 设计的目的

本次设计的目的就是在掌握EDA实验开发系统的初步使用基础上,了解EDA技术,

了解并掌握VHDL硬件描述语言的设计方法和思想,通过学习的VHDL语言结合电子电

路的设计知识理论联系实际,掌握所学的课程知识,学习VHDL基本单元电路的综合设

计应用。通过对四位二进制加法器和四位二进制乘法器的设计,巩固和综合运用所学课

程,加深对数字电路和VHDL基本单元的理解,理论联系实际,提高设计能力,提高分

析、解决计算机技术实际问题的独立工作能力。通过课程设计深入理解VHDL语言的精

髓,达到课程设计的目标,加法器的设计可以加深对门电路的理解,乘法器的设计可以

使对计算机怎样工作有了更深了解。

1.2 设计的基本内容

本文是设计的一个四位二进制加法器和四位二进制乘法器。四位二进制加法器使用

门电路构成,用 VHDL 语言对其实现。乘法器使用 VHDL 语言里的乘法运算符实现,使用

数码管动态显示一个三位数结果。然后用 VHDL 语言编写相应的程序,在计算机上实现,

最后进行了加法器和乘法器的仿真分析。

1

�

***

四位二进制加法器和乘法器

第 2页 共 17 页

2 EDA、VHDL 简介

2.1 EDA 简介

EDA 是电子设计自动化(Electronic Design Automation)缩写,是 90 年代初从 CAD

(计算机辅助设计)、CAM(计算机辅助制造)、CAT(计算机辅助测试)和 CAE(计

算机辅助工程)的概念发展而来的。EDA 技术是以计算机为工具,根据硬件描述语言

HDL( Hardware Description language)完成的设计文件,自动地完成逻辑编译、化简、

分割、综合及优化、布局布线、仿真以及对于特定目标芯片的适配编译和编程下载等工

作。典型的 EDA 工具中必须包含两个特殊的软件包,即综合器和适配器。综合器的功

能就是将设计者在 EDA 平台上完成的针对某个系统项目的 HDL、原理图或状态图形描

述,针对给定的硬件系统组件,进行编译、优化、转换和综合,最终获得我们欲实现功

能的描述文件。综合器在工作前,必须给定所要实现的硬件结构参数,它的功能就是将

软件描述与给定的硬件结构用一定的方式联系起来。也就是说,综合器是软件描述与硬

件实现的一座桥梁。综合过程就是将电路的高级语言描述转换低级的、可与目标器件

FPGA/CPLD 相映射的网表文件。

适配器的功能是将由综合器产生的王表文件配置与指定的目标器件中,产生最终的

下载文件,如 JED 文件。适配所选定的目标器件(FPGA/CPLD 芯片)必须属于在综合

器中已指定的目标器件系列。

硬件描述语言 HDL 是相对于一般的计算机软件语言,如:C、PASCAL 而言的。

HDL 语言使用与设计硬件电子系统的计算机语言,它能描述电子系统的逻辑功能、电

路结构和连接方式。设计者可利用 HDL 程序来描述所希望的电路系统,规定器件结构

特征和电路的行为方式;然后利用综合器和适配器将此程序编程能控制 FPGA 和 CPLD

内部结构,并实现相应逻辑功能的的门级或更底层的结构网表文件或下载文件。目前,

就 FPGA/CPLD 开发来说,比较常用和流行的 HDL 主要有 ABEL-HDL、AHDL 和 VHDL。

2.2 硬件描述语言——VHDL

2.2.1 VHDL 简介

VHDL 语言是一种用于电路设计的高级语言。它在 80 年代的后期出现。最初

是由美国国防部开发出来供美军用来提高设计的可靠性和缩减开发周期的一种使用范

围较小的设计语言 。但是,由于它在一定程度上满足了当时的设计需求,于是他在 1987

2

�

***

四位二进制加法器和乘法器

第 3页 共 17 页

年成为 A I/IEEE 的标准(IEEE STD 1076-1987)。1993 年更进一步修订,变得更加完备,

成为 A I/IEEE 的 A I/IEEE STD 1076-1993 标准。目前,大多数的 CAD 厂商出品的 EDA

软件都兼容了这种标准。VHDL 的英文全写是:VHSIC(Very High eed Integrated Circuit)

Hardware Descriptiong Language.翻译成中文就是超高速集成电路硬件描述语言。因此它

的 应 用 主 要 是 应 用 在 数 字 电 路 的 设 计 中 。 目 前 , 它 在 中 国 的 应 用 多 数 是 用 在

FPGA/CPLD/EPLD 的设计中。当然在一些实力较为雄厚的单位,它也被用来设计

ASIC。 VHDL 主要用于描述数字系统的结构,行为,功能和接口。除了含有许多具

有硬件特征的语句外,VHDL 的语言形式和描述风格与句法是十分类似于一般的计算机

高级语言。VHDL 的程序结构特点是将一项工程设计,或称设计实体(可以是一个元件,

一个电路模块或一个系统)分成外部(或称可是部分,及端口)和内部(或称不可视部分),

既涉及实体的内部功能和算法完成部分。在对一个设计实体定义了外部界面后,一旦其

内部开发完成后,其他的设计就可以直接调用这个实体。这种将设计实体分成内外部分

的概念是 VHDL 系统设计的基本点。VHDL 比其它硬件描述语言相比有以下优点:

(1)与其他的硬件描述语言相比,VHDL 具有更强的行为描述能力,从而决定了

他成为系统设计领域最佳的硬件描述语言。强大的行为描述能力是避开具体的器件结

构,从逻辑行为上描述和设计大规模电子系统的重要保证。

(2)VHDL 丰富的仿真语句和库函数,使得在任何大系统的设计早期就能查验设

计系统的功能可行性,随时可对设计进行仿真模拟。

(3)VHDL 语句的行为描述能力和程序结构决定了他具有支持大规模设计的分解

和已有设计的再利用功能。符合市场需求的大规模系统高效,

高速的完成必须有多人甚至多个代发组共同并行工作才能实现。(4)对于用 VHDL

完成的一个确定的设计,可以利用 EDA 工具进行逻辑综合和优化,并自动的把 VHDL

描述设计转变成门级网表。

(5)VHDL 对设计的描述具有相对独立性,设计者可以不懂硬件的结构,也不必管理

最终设计实现的目标器件是什么,而进行独立的设计。

2.2.2 VHDL 语言特点

应用 VHDL 进行系统设计,有以下几方面的特点。

(一)功能强大

VHDL 具有功能强大的语言结构。它可以用明确的代码描述复杂的控制逻辑设计。

3

�

***

四位二进制加法器和乘法器

第 4页 共 17 页

并且具有多层次的设计描述功能,支持设计库和可重复使用的元件生成。VHDL 是一种

设计、仿真和综合的标准硬件描述语言。

(二)可移植性

VHDL 语言是一个标准语言,其设计描述可以为不同的 EDA 工具支持。它可以从

一个仿真工具移植到另一个仿真工具,从一个综合工具移植到另一个综合工具,从一个

工作平台移植到另一个工作平台。此外,通过更换库再重新综合很容易移植为 ASIC 设

计。

(三)独立性

VHDL 的硬件描述与具体的工艺技术和硬件结构无关。设计者可以不懂硬件的结

构,也不必管最终设计实现的目标器件是什么,而进行独立的设计。程序设计的硬件目

标器件有广阔的选择范围,可以是各系列的 CPLD、FPGA 及各种门阵列器件。

(四)可操作性

由于 VHDL 具有类属描述语句和子程序调用等功能,对于已完成的设计,在不改变

源程序的条件下,只需改变端口类属参量或函数,就能轻易地改变设计的规模和结构。

(五)灵活性

VHDL 最初是作为一种仿真标准格式出现的,有着丰富的仿真语句和库函数。使其

在任何大系统的设计中,随时可对设计进行仿真模拟。所以,即使在远离门级的高层次

(即使设计尚未完成时),设计者就能够对整个工程设计的结构和功能的可行性进行查

验,并做出决策。

4

�

***

四位二进制加法器和乘法器

第 5页 共 17 页

3 设计规划过程

3.1 加法器与乘法器的原理

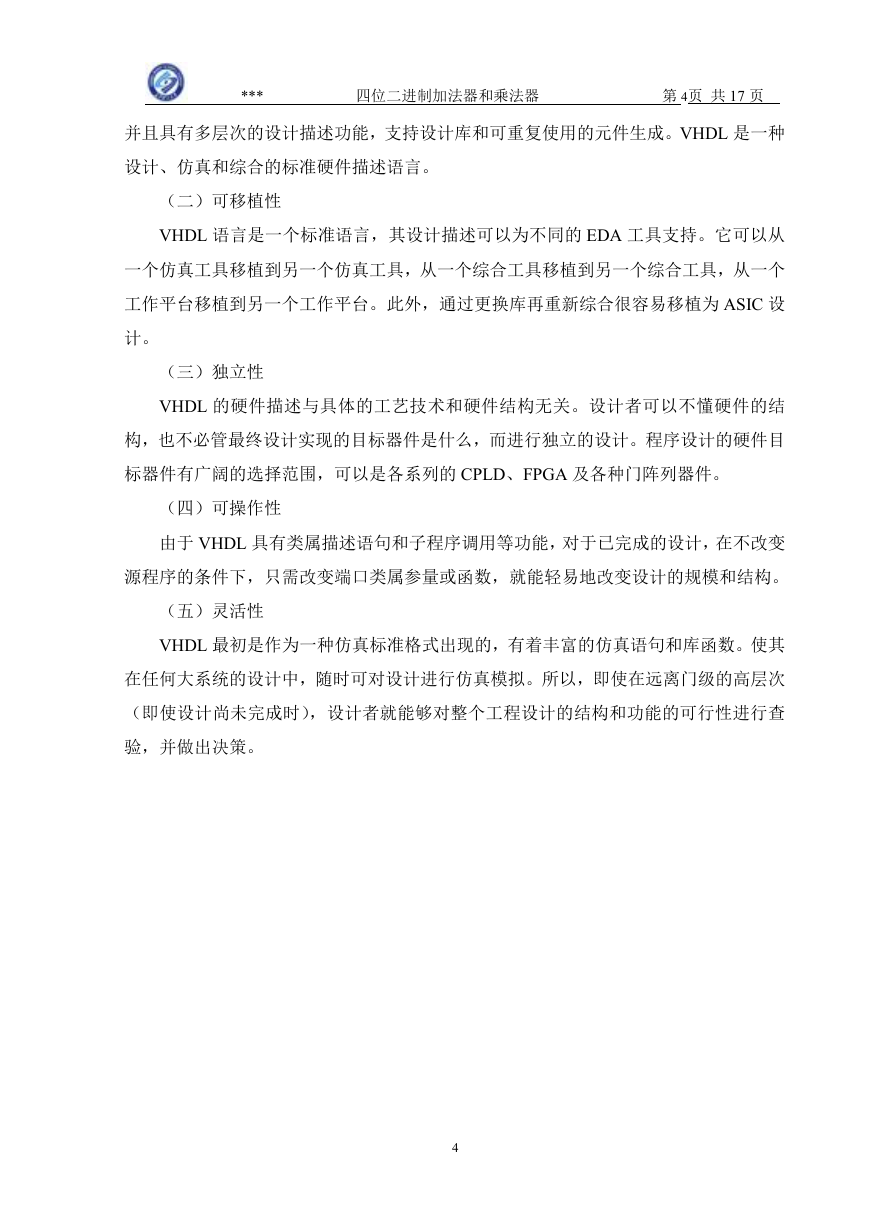

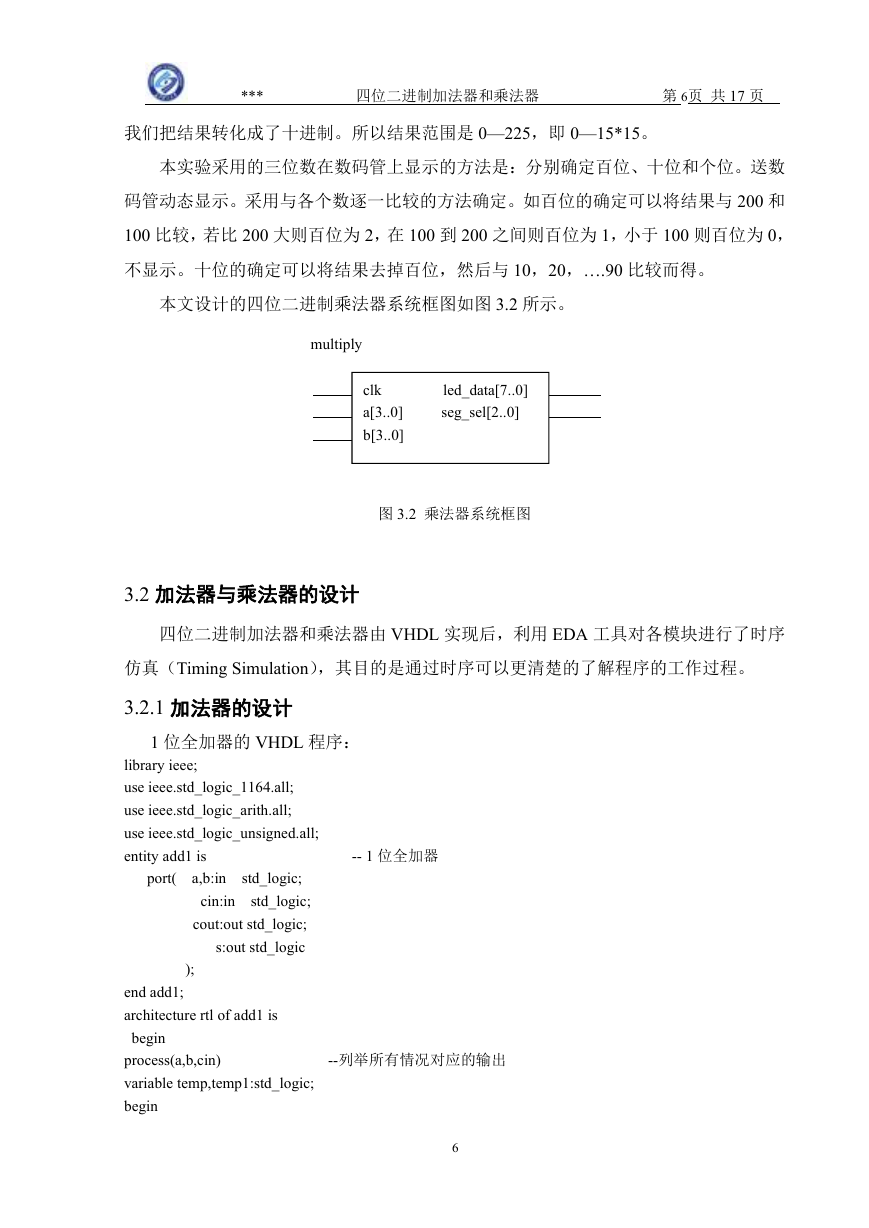

3.1.1 四位二进制加法器的组成原理

加法器是运算电路的核心。计算机中实现减法、乘法和除法都要最终转化成加法

来运算。

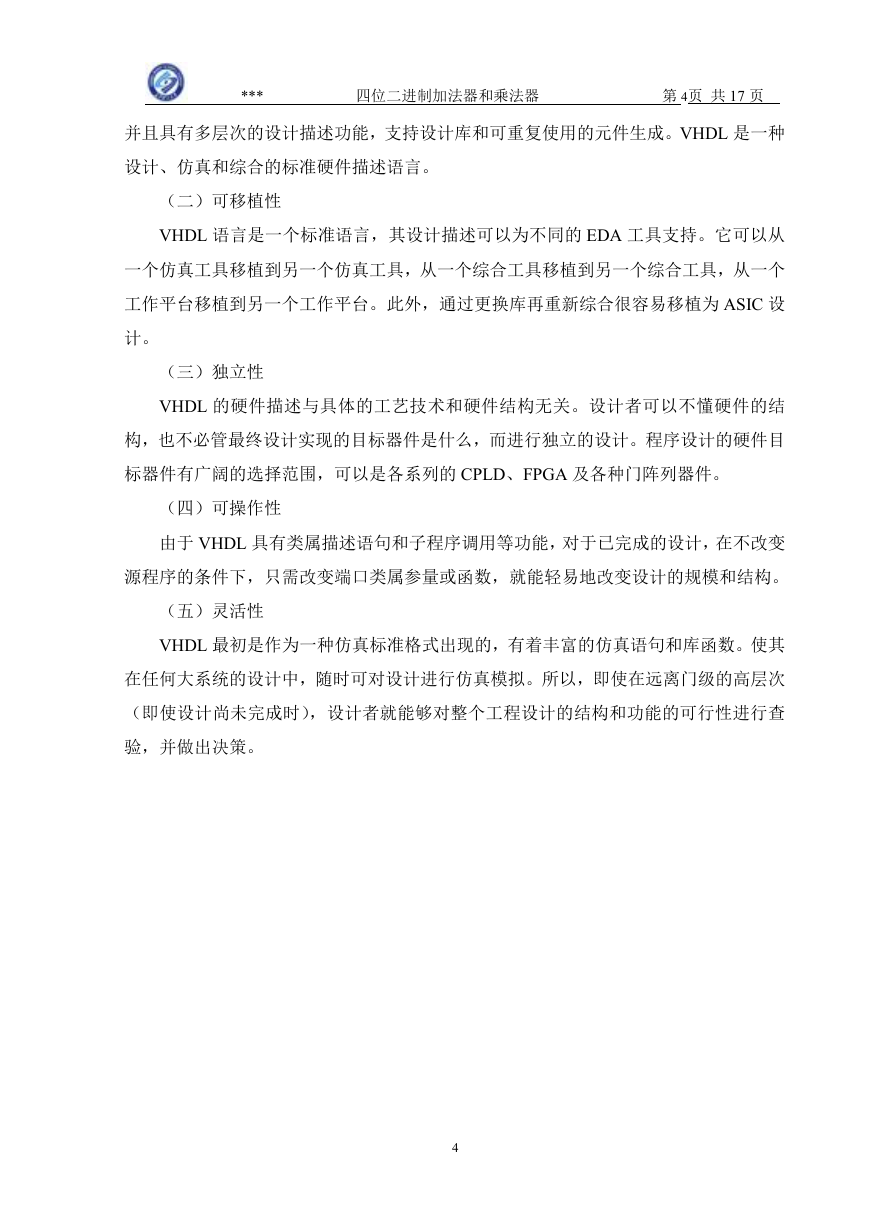

本实验才没有用 VHDL 语言中的加法运算符。而是用基本门电路来实现的。一方

面可以提高运算速度,另一方面可以使我们加深对数字电路的认识。图 3.1 所示是四位

二进制加法器的原理框图。

INPUT

a0

b0

a1

b1

a2

b2

a3

b3

OUTPUT

INPUT

s0

s1

s2

cout

s3

cout

s

cout

s

cout

s

cout

s

a

b

cin

a

b

cin

a

b

cin

a

b

cin

图 3.1 加法器系统框图

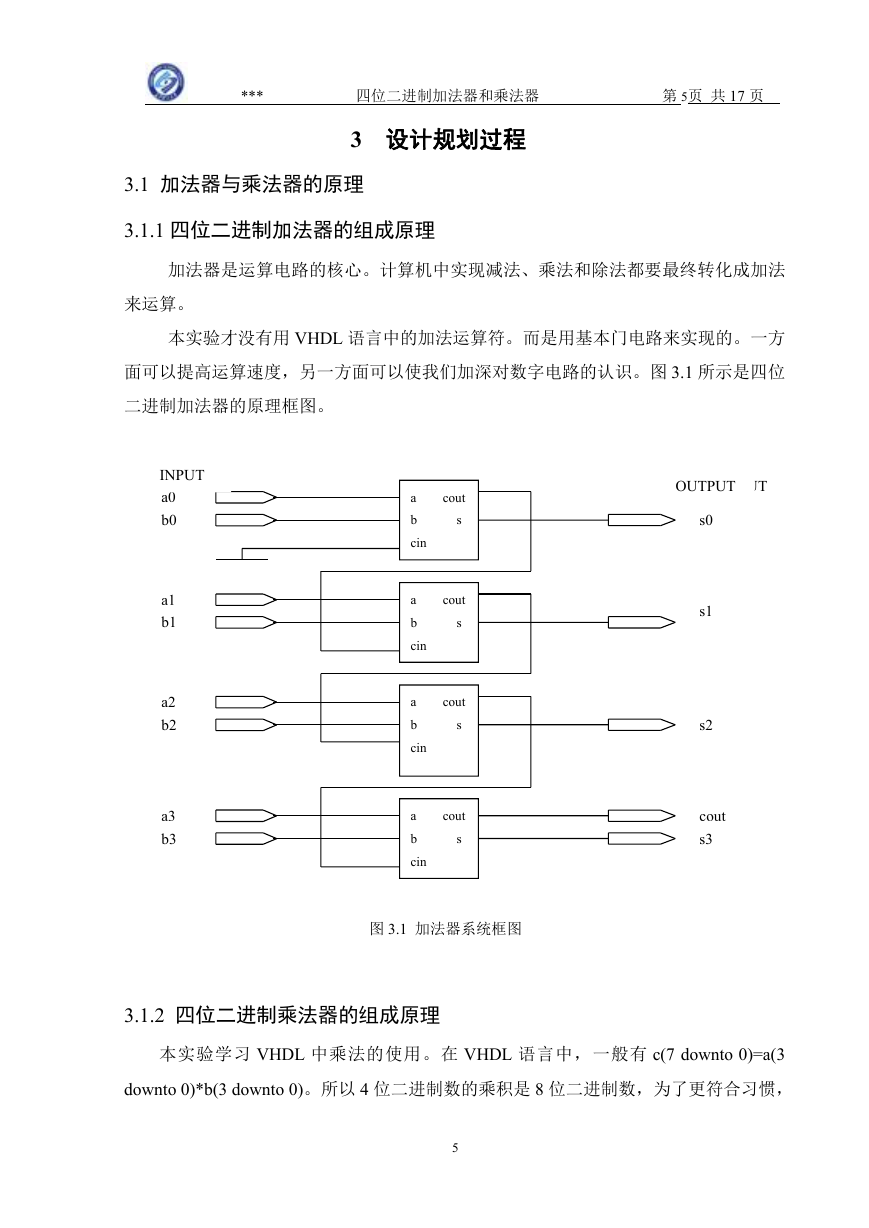

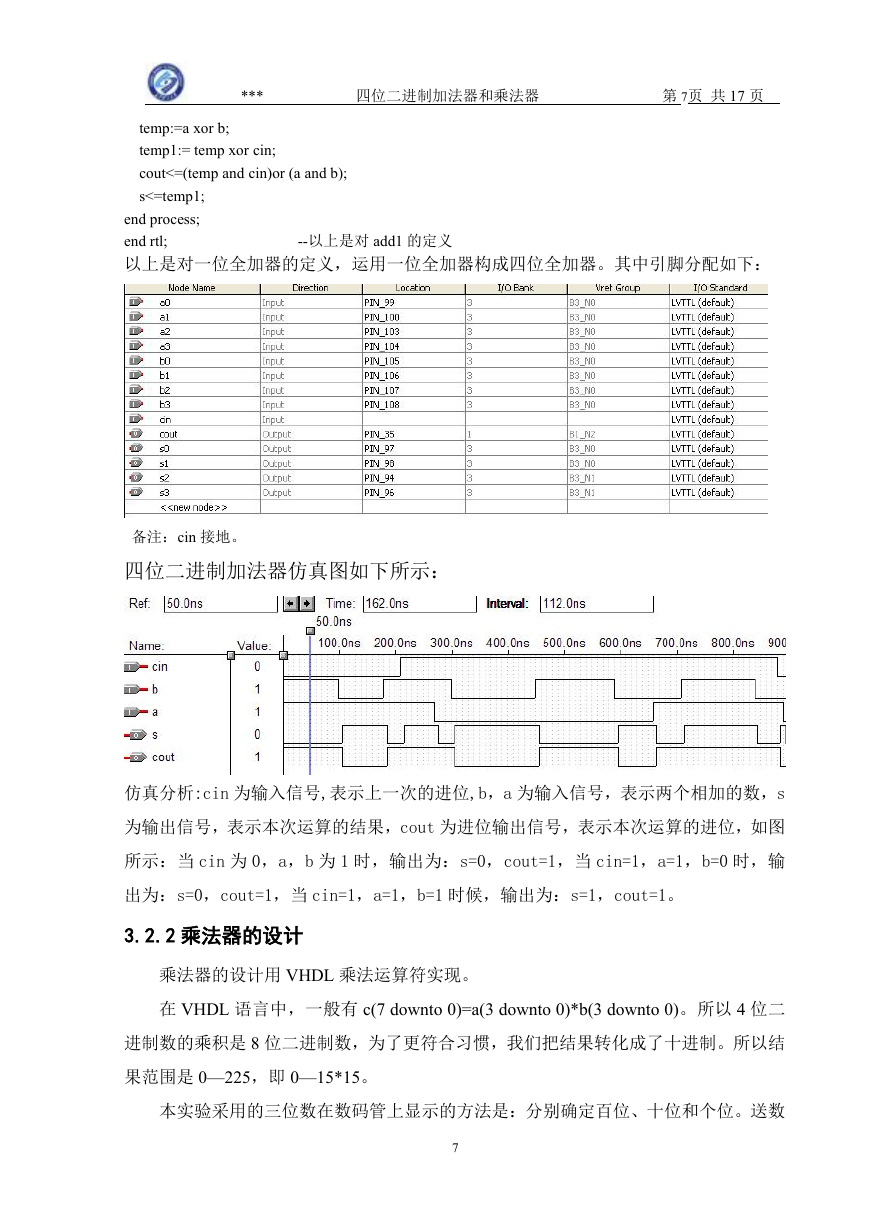

3.1.2 四位二进制乘法器的组成原理

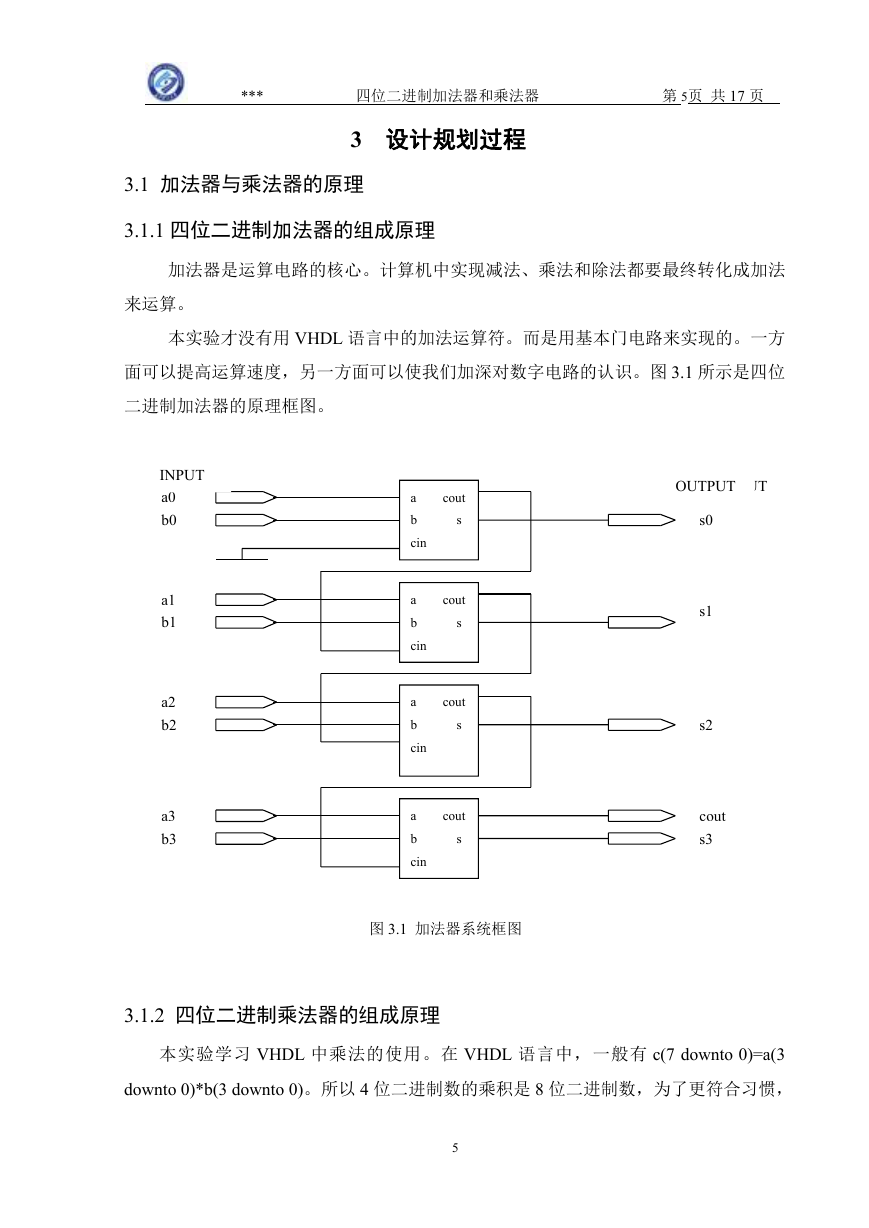

本实验学习 VHDL 中乘法的使用。在 VHDL 语言中,一般有 c(7 downto 0)=a(3

downto 0)*b(3 downto 0)。所以 4 位二进制数的乘积是 8 位二进制数,为了更符合习惯,

5

�

***

四位二进制加法器和乘法器

第 6页 共 17 页

我们把结果转化成了十进制。所以结果范围是 0—225,即 0—15*15。

本实验采用的三位数在数码管上显示的方法是:分别确定百位、十位和个位。送数

码管动态显示。采用与各个数逐一比较的方法确定。如百位的确定可以将结果与 200 和

100 比较,若比 200 大则百位为 2,在 100 到 200 之间则百位为 1,小于 100 则百位为 0,

不显示。十位的确定可以将结果去掉百位,然后与 10,20,….90 比较而得。

本文设计的四位二进制乘法器系统框图如图 3.2 所示。

multiply

clk

a[3..0]

b[3..0]

led_data[7..0]

seg_sel[2..0]

图 3.2 乘法器系统框图

3.2 加法器与乘法器的设计

四位二进制加法器和乘法器由 VHDL 实现后,利用 EDA 工具对各模块进行了时序

仿真(Timing Simulation),其目的是通过时序可以更清楚的了解程序的工作过程。

3.2.1 加法器的设计

1 位全加器的 VHDL 程序:

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_arith.all;

use ieee.std_logic_unsigned.all;

entity add1 is

port(

std_logic;

a,b:in

cin:in

std_logic;

cout:out std_logic;

s:out std_logic

);

end add1;

architecture rtl of add1 is

begin

process(a,b,cin)

variable temp,temp1:std_logic;

begin

-- 1 位全加器

--列举所有情况对应的输出

6

�

***

四位二进制加法器和乘法器

第 7页 共 17 页

temp:=a xor b;

temp1:= temp xor cin;

cout<=(temp and cin)or (a and b);

s<=temp1;

end process;

end rtl;

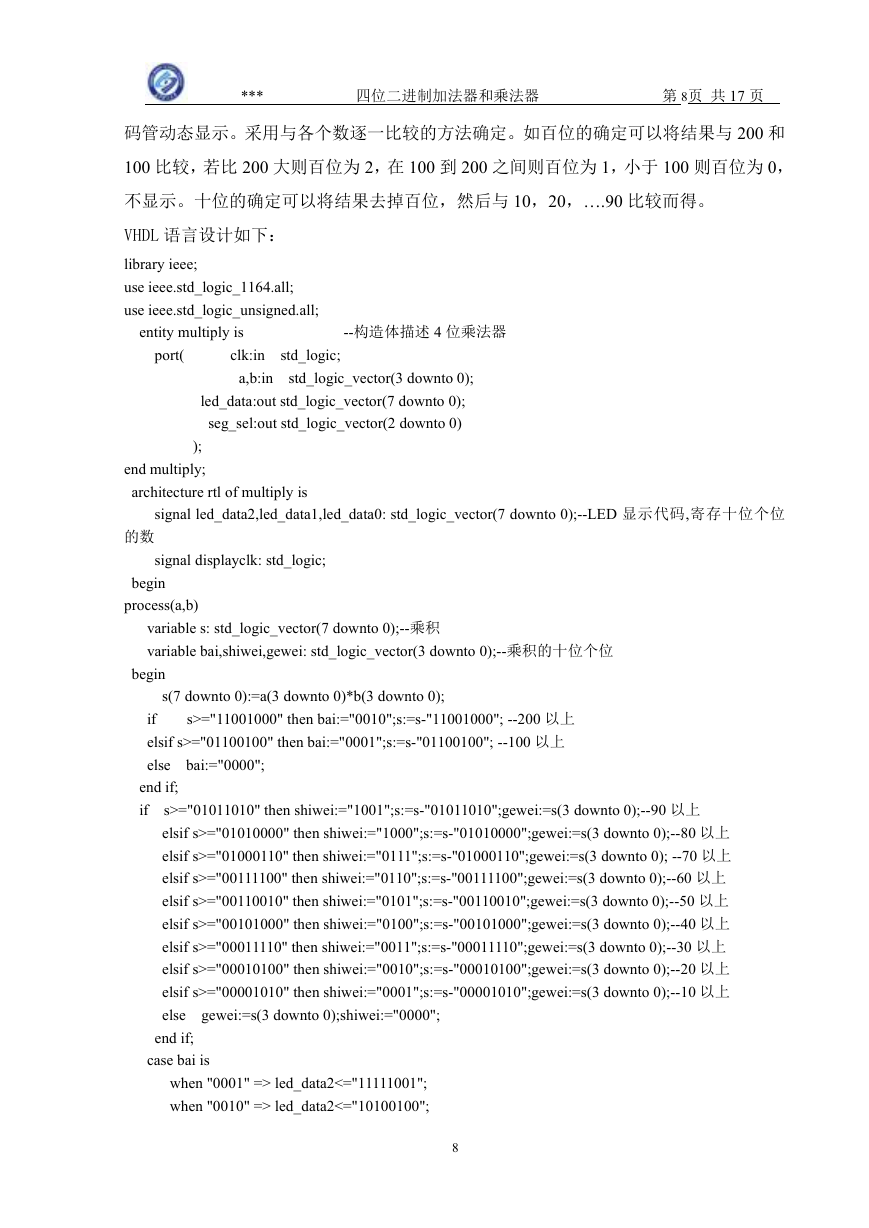

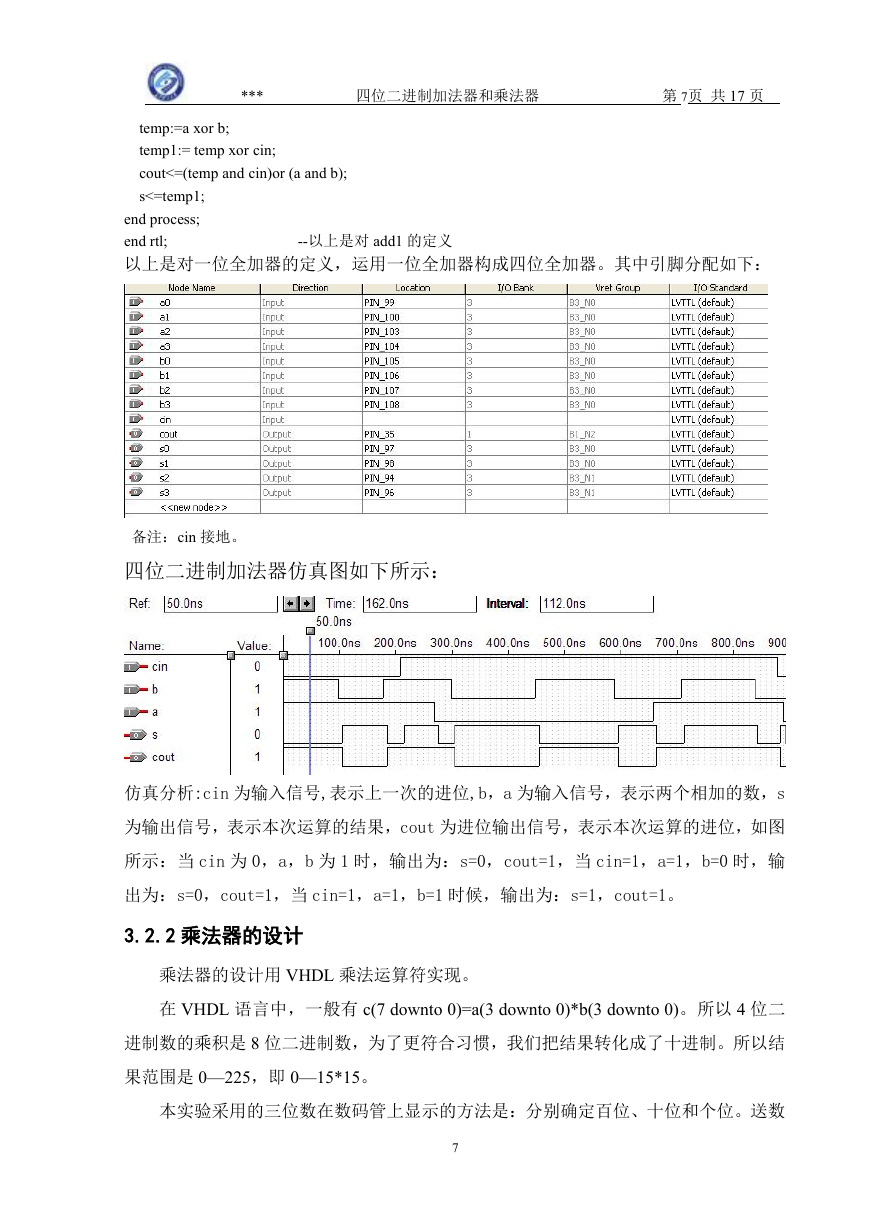

以上是对一位全加器的定义,运用一位全加器构成四位全加器。其中引脚分配如下:

--以上是对 add1 的定义

备注:cin 接地。

四位二进制加法器仿真图如下所示:

仿真分析:cin 为输入信号,表示上一次的进位,b,a 为输入信号,表示两个相加的数,s

为输出信号,表示本次运算的结果,cout 为进位输出信号,表示本次运算的进位,如图

所示:当 cin 为 0,a,b 为 1 时,输出为:s=0,cout=1,当 cin=1,a=1,b=0 时,输

出为:s=0,cout=1,当 cin=1,a=1,b=1 时候,输出为:s=1,cout=1。

3.2.2 乘法器的设计

乘法器的设计用 VHDL 乘法运算符实现。

在 VHDL 语言中,一般有 c(7 downto 0)=a(3 downto 0)*b(3 downto 0)。所以 4 位二

进制数的乘积是 8 位二进制数,为了更符合习惯,我们把结果转化成了十进制。所以结

果范围是 0—225,即 0—15*15。

本实验采用的三位数在数码管上显示的方法是:分别确定百位、十位和个位。送数

7

�

***

四位二进制加法器和乘法器

第 8页 共 17 页

码管动态显示。采用与各个数逐一比较的方法确定。如百位的确定可以将结果与 200 和

100 比较,若比 200 大则百位为 2,在 100 到 200 之间则百位为 1,小于 100 则百位为 0,

不显示。十位的确定可以将结果去掉百位,然后与 10,20,….90 比较而得。

VHDL 语言设计如下:

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity multiply is

--构造体描述 4 位乘法器

port(

clk:in

a,b:in

std_logic;

std_logic_vector(3 downto 0);

led_data:out std_logic_vector(7 downto 0);

seg_sel:out std_logic_vector(2 downto 0)

);

end multiply;

architecture rtl of multiply is

signal led_data2,led_data1,led_data0: std_logic_vector(7 downto 0);--LED 显示代码,寄存十位个位

的数

signal displayclk: std_logic;

begin

process(a,b)

variable s: std_logic_vector(7 downto 0);--乘积

variable bai,shiwei,gewei: std_logic_vector(3 downto 0);--乘积的十位个位

begin

s(7 downto 0):=a(3 downto 0)*b(3 downto 0);

if

s>="11001000" then bai:="0010";s:=s-"11001000"; --200 以上

elsif s>="01100100" then bai:="0001";s:=s-"01100100"; --100 以上

else

end if;

if

bai:="0000";

s>="01011010" then shiwei:="1001";s:=s-"01011010";gewei:=s(3 downto 0);--90 以上

elsif s>="01010000" then shiwei:="1000";s:=s-"01010000";gewei:=s(3 downto 0);--80 以上

elsif s>="01000110" then shiwei:="0111";s:=s-"01000110";gewei:=s(3 downto 0); --70 以上

elsif s>="00111100" then shiwei:="0110";s:=s-"00111100";gewei:=s(3 downto 0);--60 以上

elsif s>="00110010" then shiwei:="0101";s:=s-"00110010";gewei:=s(3 downto 0);--50 以上

elsif s>="00101000" then shiwei:="0100";s:=s-"00101000";gewei:=s(3 downto 0);--40 以上

elsif s>="00011110" then shiwei:="0011";s:=s-"00011110";gewei:=s(3 downto 0);--30 以上

elsif s>="00010100" then shiwei:="0010";s:=s-"00010100";gewei:=s(3 downto 0);--20 以上

elsif s>="00001010" then shiwei:="0001";s:=s-"00001010";gewei:=s(3 downto 0);--10 以上

else

end if;

case bai is

gewei:=s(3 downto 0);shiwei:="0000";

when "0001" => led_data2<="11111001";

when "0010" => led_data2<="10100100";

8

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc