Vivado 设计套件的 UltraFast 设计方法指南

修订历史

目录

1: 引言

关于 UltraFast 设计方法

利用本指南

使用 UltraFAST 设计方法检查表

使用 UltraFAST 设计方法 DRC

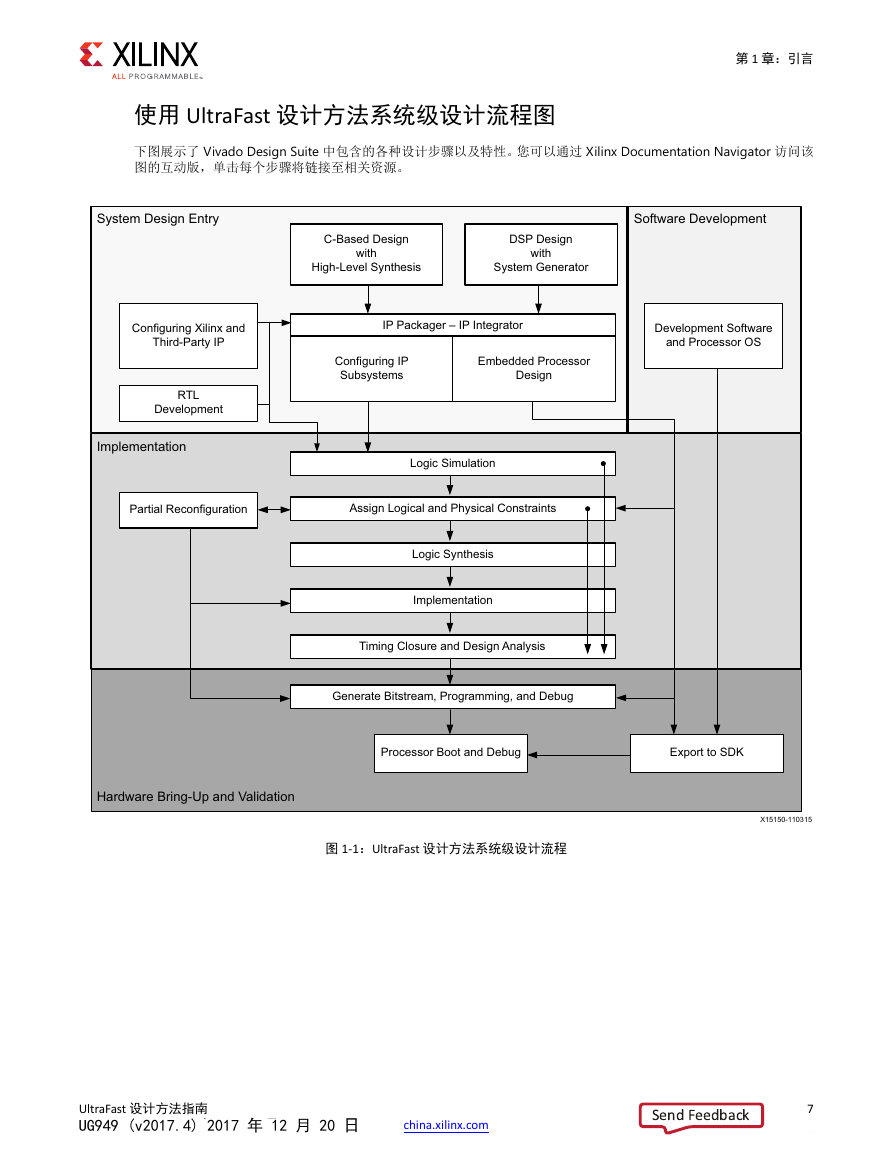

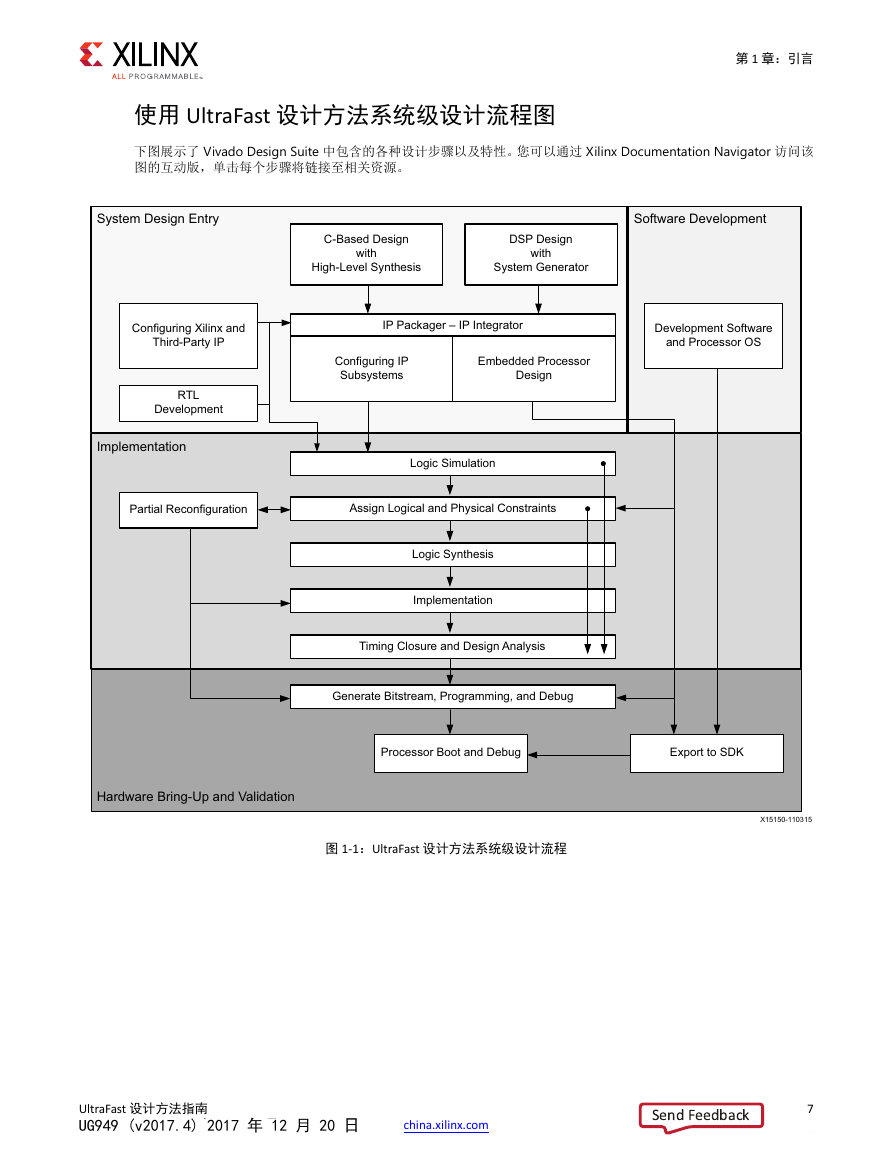

使用 UltraFast 设计方法系统级设计流程图

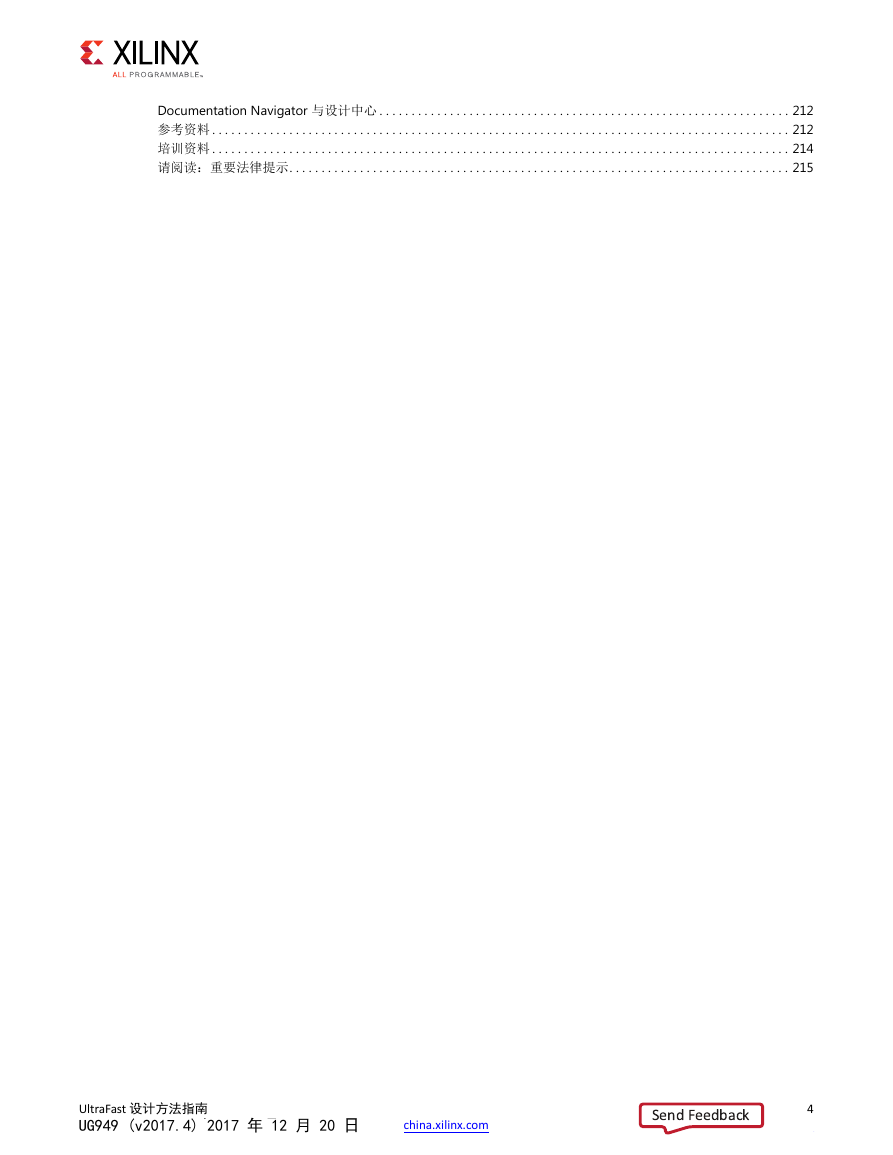

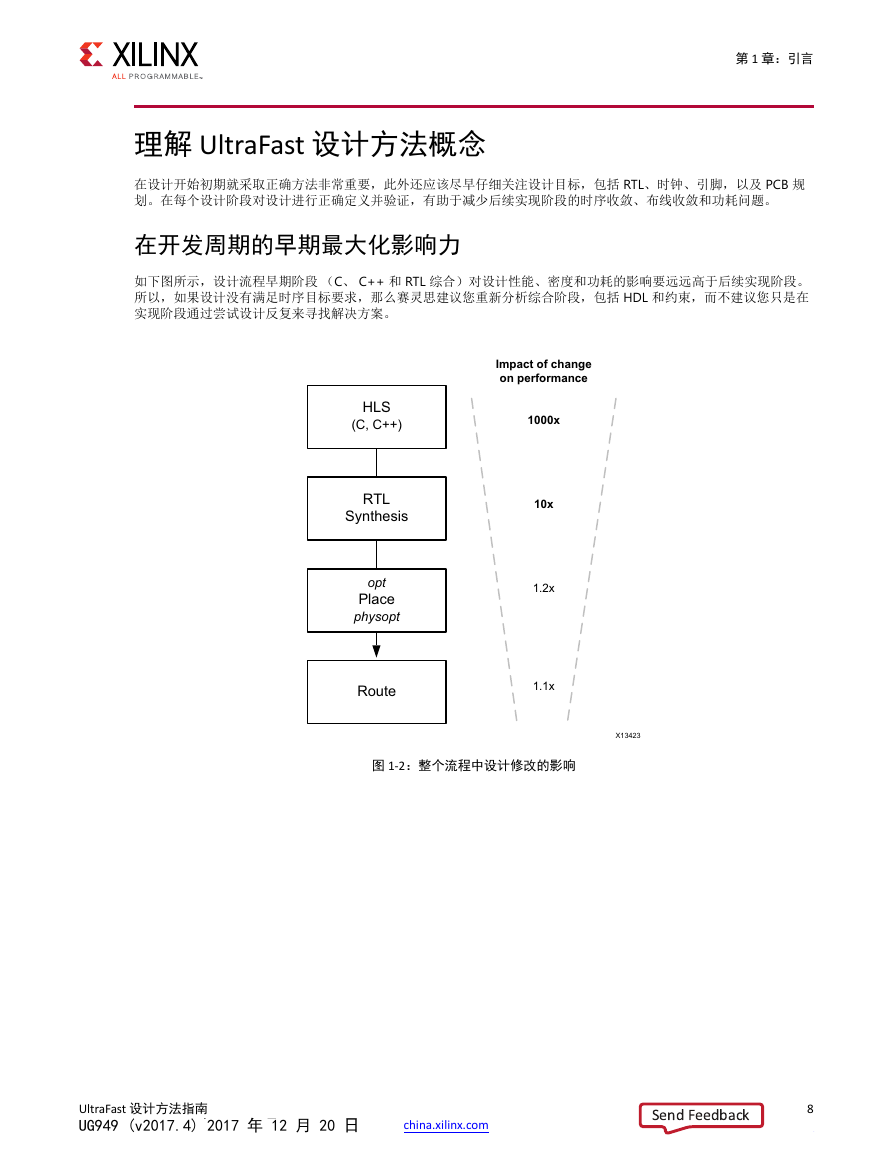

理解 UltraFast 设计方法概念

在开发周期的早期最大化影响力

在每一个设计阶段进行验证

利用快速验证的优势

使用 Vivado Design Suite

采用版本控制系统管理 Vivado Design Suite 源

升级到新发布的 Vivado Design Suite 版本

访问其他技术文档和培训资料

2: 单板和器件规划

单板和器件规划简介

PCB 布局建议

与 PCB 上的物理组件保持一致

配电系统

PCB 设计的具体考虑因素

时钟资源规划与分配

I/O 管脚分配设计流程

I/O 管脚分配的相关 Vivado Design Suite 项目种类

Pre-RTL I/O 管脚分配

基于网表的 I/O 管脚分配

定义替代器件

引脚分配

使用赛灵思工具选择管脚

所需的信息

管脚选择

接口数据、地址和控制引脚

接口控制信号

极高的扇出、涉及范围大的控制信号

配置引脚

存储器接口

千兆位收发器 (GT)

高速 I/O

内部参考电压和 DCI 级联约束

接口带宽验证

采用 SSI 器件进行设计

SSI 管脚的考虑因素

超级逻辑区域 (SLR)

SLR 术语

主超级逻辑区域

硅中介层

超长线路 (SLL) 布线

传输限制

SLR 利用率考虑因素

大宽度总线的 SLR 交汇

器件电源因素与系统关联性

器件的供电源路径

功耗模式

上电

启动功耗

待机功耗

有功功耗

影响功耗的环境因素

电源供电线合并影响功耗

功耗模型精度

器件功耗及整体系统设计进程

利用 Xilinx Power Estimator(XPE) 进行最差情况功耗分析

配置

单板设计技巧

3: 设计创建

设计创建简介

定义理想的设计层级

靠近顶层添加 I/O 组件

在顶层附近插入时钟元件

在逻辑边界上寄存数据路径

妥善考虑布局规划事项

针对功能和时序调试优化层级

在模块级应用属性

针对高级设计技术优化层级

高速 DSP 设计的预先层级规划实例

RTL 编码指南

使用 Vivado Design Suite HDL 模板

控制信号与控制集

复位

使用复位的时间和位置

同步复位与异步复位

复位编码实例 1:乘法器与异步复位

复位编码实例 2:同步复位乘法器

尝试消除 HDL 代码重置时出现问题

时钟使能

创建时钟使能

复位和时钟使能的先后

使用综合属性控制使能/重置提取

使用 DIRECT_ENABLE 和 DIRECT_RESET

将逻辑从控制引脚推到数据引脚

信号控制技巧

掌握调用的结果

调用 RAM 和 ROM

实现 RAM 时应该考虑的性能因素

场景防止块 RAM 输出寄存器调用

检查读取数据寄存器输出的多扇出

检查地址/读数据寄存器上的复位信号

检查寄存器中的反馈结构

将存储器映射到 UltraRAM 块

为适用 DSP 和算术调用进行

移位寄存器和延迟线

初始化全部调用的寄存器、SRL 和存储器

判断实例化或调用的时机

综合工具优化

判断实例化的时机

提升性能的编码方式

关键路径上的高扇出

在不需要高扇出网络的设计部分精简负载

使用寄存器复制

流水线考虑因素

考虑 SSI 器件的流水线

预先考虑流水线

检查调用的逻辑

确定是否需要管道

平衡延迟

平衡管线深度和 SRL 使用

避免不必要的流水线

考虑流水线宏原语

提升功耗的编码方式

门控时钟或数据路径

使门控元件数量最大化

使用专用时钟缓冲器的时钟使能引脚

当不需要优先编码器时使用 Case 块

性能/功耗块 RAM 利弊取舍

分解更深的存储器配置,实现功耗与性能平衡

运行 RTL DRC

时钟指南

UltraScale 器件时钟

时钟原语

全局时钟缓冲器连接和布局跟踪

时钟布线、根和分布

时钟树缓存布局布线

时钟功能

高扇出时钟

低扇出时钟

平衡利用高和低扇出时钟

时钟约束

使用 LOC 约束 IO/MMCM/PLL/GT

在时钟缓冲器上使用 CLOCK_REGION 属性

使用 Pblock 限制时钟缓冲器布局

在时钟网络上使用 USER_CLOCK_ROOT 属性

在多个时钟网络上使用 CLOCK_DELAY_GROUP 约束

使用 CLOCK_DEDICATED_ROUTE 约束

使用 CLOCK_LOW_FANOUT 约束

时钟拓扑结构建议

并行时钟缓冲器

级联时钟缓冲器

时钟多路复用

PLL/MMCM 反馈路径和补偿模式

BUFG_GT 除法器

SelectIO 时钟

ISERDESE3 和 IDDRE1 时钟

OSERDESE3 时钟

使用 MMCM 的 I/O 时序 ZHOLD/BUF_IN 补偿

同步 CDC

GT 接口时钟

BUFG_GT 与动态除法器

单四通道和多四通道接口

[RT]XUSRCLK/[RT]XUSRCLK2 偏差匹配

面向 PCI Express 的集成块 CORECLK/PIPECLK/USERCLK 偏差匹配

7 系列器件时钟

使用水平时钟区域缓存实现时钟门控

关于SSI 器件的更多时钟考虑

SSI 技术器件中的全局时钟资源的时钟偏差

时钟结构设计

调用

综合约束和属性

IP 的使用

实例化

控制时钟的相位、频率、占空比和抖动

使用时钟修改块(MMCM 和 PLL)

在时钟上使用 IDELAY 控制相位

使用门控时钟

将时钟门控转换为时钟使能

门控时钟缓冲器

控制和同步器件启动

避免本地时钟

创建输出时钟

时钟域交汇

单比特 CDC

多位 CDC

优化 MTBF

为 D EST_SYNC_FF 参数选择正确的值

正确地约束设计

充分利用 IP 核

规划 IP 要求

AMBA AXI

Vivado Design Suite IP 目录

定制 IP

从 IP 目录选择 IP

自定义 IP

使用定制 GUI

使用 Tcl 脚本

IP 版本和版本控制

利用约束

编制设计约束

建议的约束文件

简单设计

复杂设计

验证读取顺序

建议的约束顺序

创建综合约束

创建实现约束

将块级约束读入顶层设计

分四个步骤定义时序约束

定义时钟约束

识别时钟源

时钟网络报告

检查时序报告

创建主时钟

输入端口

7 系列器件中千兆位收发器输出引脚

某些硬件原语输出引脚

创建生成时钟

自动衍生时钟

用户定义的生成时钟

主时钟与生成时钟间的路径

核实时钟定义与覆盖范围

调整时钟特性

抖动

更多不确定性

时钟源位置的时钟延迟

MMCM 或 PLL 外部反馈回路延迟

约束输入和输出端口

系统级视角

定义输入延迟

定义输出延迟

选择参考时钟

识别与每个端口有关的时钟

浏览单板原理图

浏览设计原理图

报告进出端口的时序

使用自动识别的采样时钟

使用主时钟

使用虚拟时钟

使用生成时钟

参考时钟上升沿和下降沿

核实延迟约束

I/O 路径报告命令行实例

输入至输出馈通路径

实例 1

实例 2

使用 XDC 模板——源同步接口

定义时钟组和 CDC 约束

检查时钟交互

同步

异步

专属

时钟对分类

时钟交互报告

检查时序报告

约束专属时钟组

在相同时钟源上定义的重叠时钟

由时钟多路复用器驱动的重叠时钟

约束异步时钟组和时钟域交汇

Report CDC

双向时钟间的全局约束

单独路径上的约束

时钟例外优先于 set_max_delay

指定时序例外

时序例外使用指南

时序例外优先级规则

添加伪路径约束

用例

对综合的影响

对实现的影响

添加最小和最大延迟约束

用例

对综合的影响

对实现的影响

避免路径分段

添加多周期路径约束

降低“建立”要求,同时让“保持”不变

对综合与设计实现的影响

常见错误

其它高级时序约束

Case 分析

不分析时序

数据检查

最长时间借用

定义物理约束

4: 实现

综合和设计实现简介

运行综合

综合属性

KEEP 和 DONT_TOUCH

MAX_FANOUT

块级综合策略

使用块级综合策略

综合后的步骤

检查和清理 DRC

运行报告方法

检查综合日志

检查时序约束

满足综合后的时序要求

遵循处理剩余违规行为的指南

处理高逻辑级数

检查利用率

检查时钟树

时钟缓存的使用

时钟树拓扑结构

实现设计

使用工程模式与非工程模式选项

策略

指令

反复循环的流程

使用检查点分析不同阶段的设计

使用交互式报告文件

使用增量编译流程

增量编译流程模式

运行时间考虑因素

并行流程

打开综合设计。

逻辑优化 (opt_design)

优化分析

实现过程中的功耗注意事项

布局 (place_design)

布局分析

物理优化 (phys_opt_design)

物理综合需求

布线 (route_design)

布线分析

5: 设计收敛

设计收敛简介

时序收敛

理解时序收敛指标

检查有效约束

检查正时序裕量

理解时序报告

检查设计是否正确约束

修复由 check_timing 标记的问题

无时钟和未约束的内部端点

生成时钟

环路和锁存器环

无输入/输出延迟和部分输入/输出延迟

多个时钟

修复被 report_methodology 标记的问题

方法 DRC 对时序收敛的影响

方法 DRC 对验收质量的影响

其他时序方法 DRC

设计基准 (baseline)

定义基准约束

确定必须创建哪些时钟

确认没有时钟遗漏

时钟域交汇约束

检查时钟关系

识别没有主时钟的时钟对

明确严格的时序要求

同时约束主时钟和生成时钟

限制 I/O 约束和时序例外

在每个步骤前后评估设计 WNS

综合后与逻辑优化后

布局前后

物理优化前后

预布线和后布线

基线(baselining)与时序约束验证流程

分析并解决时序违规

确定时序违规的根源

检查时序裕量

使用设计分析报告

分析路径特性

查看逻辑层次分布

数据路径延迟和逻辑层次

时钟偏差与不确定性

减少逻辑延迟

优化常规结构路径

使用专用块和宏原语优化路径

降低信号网络延迟

检查物理约束

识别拥塞

拥塞区和水平定义

拥塞级别范围

“Device”窗口窗口中每个 CLB 的布线拥塞

在 Placer 日志中的拥塞

布线器日志中的拥塞

报告设计分析拥塞报告

报告设计分析复杂性报告

减少时钟偏差

使用内部时钟时序路径

限制同步时钟域交汇路径

在异步时钟之间添加时序例外

应用可减少时钟偏差的常见技术

应用技巧提升 7 系列器件的偏差

提升 UltraScale 和 UltraScale+ 器件的偏差

减少时钟不确定性

使用 MMCM 设置来减少时钟不确定性

使用 BUFGCE_DIV 减少时钟不确定性

应用通用时序收敛技术

用块级综合策略提升网表

减少 MUXF 映射以降低拥塞

提升逻辑层次

减少控制集

优化高扇出网

使用寄存器复制

将高扇出网络推广到全局布线

物理优化

利用 group_path 选项确定关键逻辑的优先级

在布线之前修复较大的保持违规问题

解决拥塞

降低器件利用率

平衡 SSI 器件的 SLR 利用率

使用替代布局和布线指令

关闭跨边界优化

禁用 LUT 组合和 MUXF 调用

使用块级综合策略

在拥塞区域中限制高扇出网络

调节编译流程

策略与指令

优化反复循环

设计过约束

使用增量编译

选择高质量的参考检查点

限制高重用模式下的差异

为高重用模式选择增量编译指令

提升高重用模式的时序 QoR

降低低重用模式的 QoR 可变性

布局规划考虑因素

群关键逻辑

SSI 技术考虑因素

重复使用布局

功耗分析与优化

估计整个流程的功耗

使用电源约束顾问

精确功耗分析的最佳做法

在运行 Vivado Design Suite 功耗分析后检查设计的配电

在运行 Vivado Design Suite 功耗分析后进一步优化控制信号活动

功耗优化

分析功耗估计和优化结果

运行功耗优化

使用功耗优化报告

使用时序报告确定功耗优化的影响

配置与调试

配置

调试

设计探测

选择调试网络

使用 MARK_DEBUG 保留调试探针探测网络名称

使用 ILA 核

ILA 核和时序考虑因素

使用 Vivado IP 集成器进行调试设计

在 Vivado 硬件管理器中调试 AXI 接口

使用系统内 IBERT

运行有关调试的 DRC

生成 AXI 事务

修改已实现的网表以替换现有的调试探针

在已实现的网表上插入、删除或编辑 ILA 核

使用远程调试

附录 A: 附加资源与法律提示

赛灵思资源

解决方案中心

Documentation Navigator 与设计中心

参考资料

Vivado Design Suite 用户指南及参考资料指南

Vivado Design Suite 教程

其它赛灵思技术文档

培训资料

请阅读:重要法律提示

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc