EDA 课程设计报告

系别: 电子通信工程系

专业: 电子信息工程

姓名:

学号:

指导教师:

1

�

数字秒表的设计

目录

一、课程设计任务书...........................................................................3

二、设计方案......................................................................................4

三、实验仪器.......................................................................................5

四、测试步骤.......................................................................................5

五、测试结果.......................................................................................7

六、遇到的问题及解决方案............................................................. 8

七、总结..............................................................................................8

八、参考文献......................................................................................8

附注 1 原理图及 PCB 图.....................................................................9

附注 2 元件清单...............................................................................12

附注 3 程序清单...............................................................................13

2

�

一、课程设计任务书

课程名称:EDA 课程设计

设计题目:数字秒表

专业班级:

学生姓名:

学号:

指导教师:

任务书下达日期:2010 年 12 月 6 日

设计完成日期: 2010 年 12 月 17 日

二、设计方案

3

�

1、设计内容

(1)4 位数码管显示,精度 0.1 秒,实现 100—0 倒计时,带开始键、暂停键

和复位键。

(2)电源 5V,系统时钟 12MHz,带 JTAG 下载电路。

(3)核心芯片 Altera,EMP7064,PLC44 封装。

2、设计要求

设计思路清晰,给出设计整体方框图;

设计个单元电路,给出具体设计思路、电路图、元器件清单;

总电路设计;

安装调试电路;

写出主要设计程序。

3、主要设计条件

提供 EDA 试验箱,直流稳压电源,万用表;

提供实验所需的核心芯片 Altera,EPM7064;

系统时钟 12MHZ,带 JTAG 下载电路。

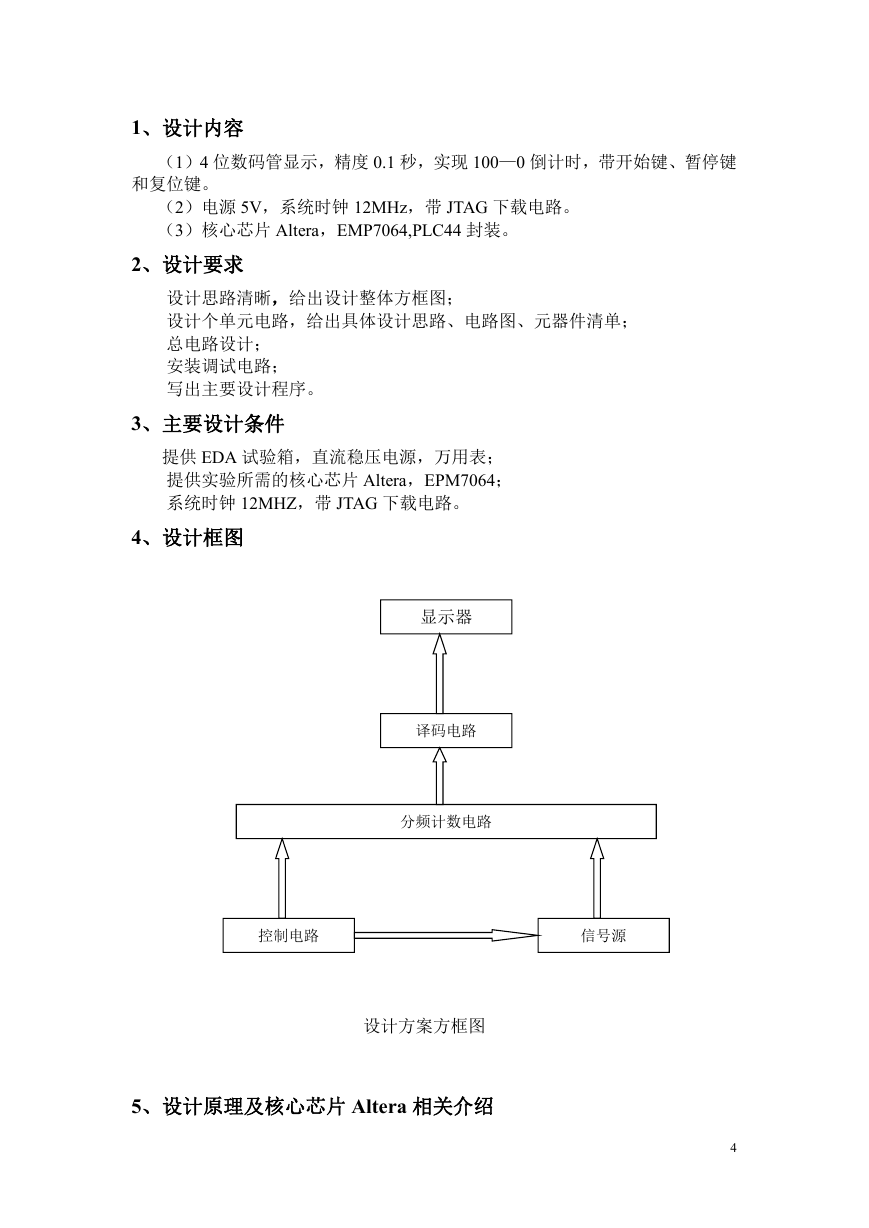

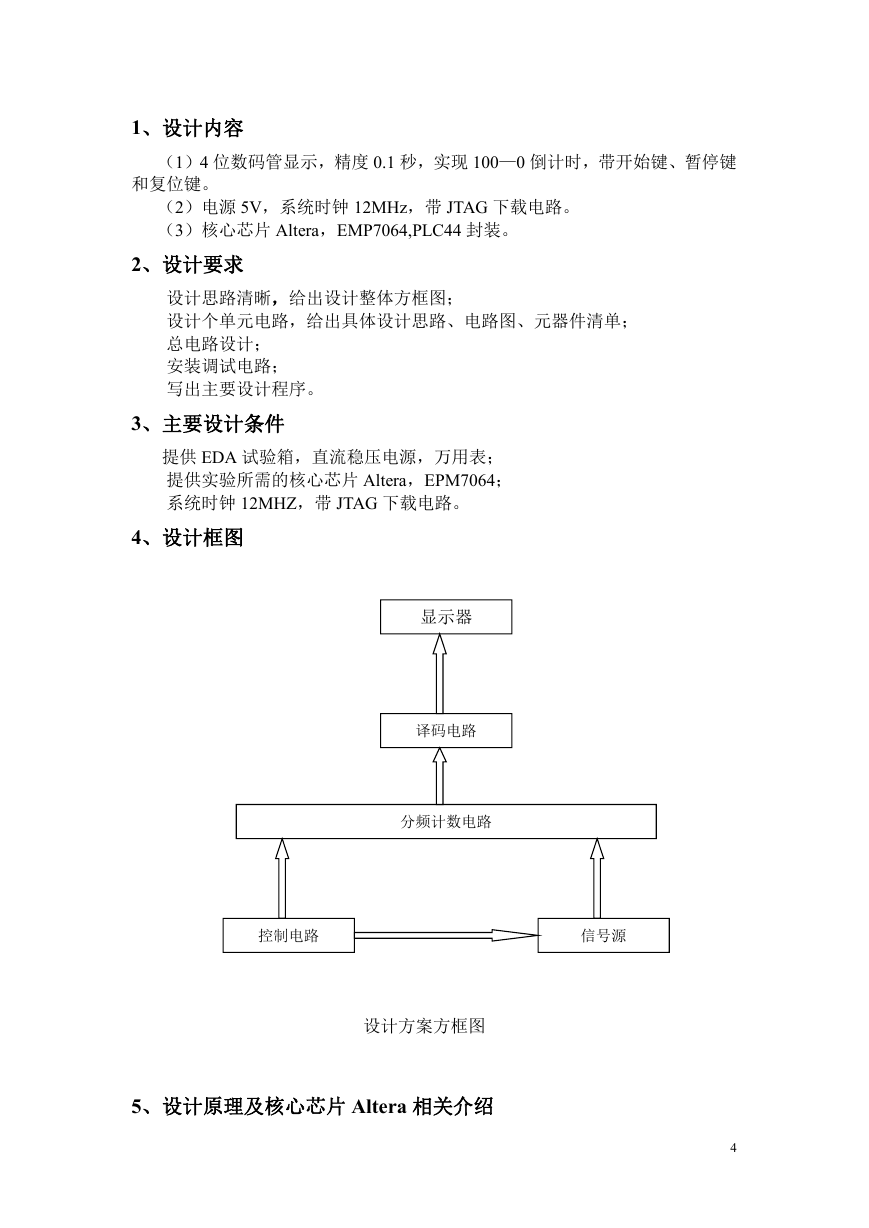

4、设计框图

显示器

译码电路

分频计数电路

控制电路

信号源

设计方案方框图

5、设计原理及核心芯片 Altera 相关介绍

4

�

由 Altera,EPM7064 作为核心芯片,采用 10HZ 分频电路。现在以 Quartus

II 5.0 为设计平台 ,设计了一个具体数字系统即带计时器功能的秒表系统,使用

Quartus II 5.0 的综合器和仿真器对系统进行了编译和仿真已经获得了成功。

Quartus II 是一款功能强大的 EDA 软件。在这个集成开发环境中,PLD 使用者可

以完成编辑、编译、仿真、综合、布局布线、时序分析、生成编程文件、编程等

全套 PLD 开发流程。

Altera 的主流 FPGA 分为两大类,一种侧重低成本应用,容量中等,性能

可以满足一般的逻辑设计要求,如 Cyclone,CycloneII;还有一种侧重于高性能

应用,容量大,性能能满足各类高端应用,如 Startix,StratixII 等,用户可以根

据自己实际应用要求进行选择。在性能可以满足的情况下,优先选择低成本器件。

Cyclone(飓风):Altera 中等规模 FPGA,2003 年推出,0.13um 工艺,1.5v

内核供电,与 Stratix 结构类似,是一种低成本 FPGA 系列 ,是目前主流产品,

其配置芯片也改用全新的产品。Altera 最成功的器件之一,性价比不错,是一种

适合中低端应用的通用 FPGA,推荐使用。

CycloneII:Cyclone 的下一代产品,2005 年开始推出,90nm 工艺,1.2v 内

核供电,属于低成本 FPGA,性能和 Cyclone 相当,提供了硬件乘法器单元。

三、实验仪器

EDA 试验箱,5V 直流稳压电源,数字万用表,电烙铁,所需的核心芯片 Altera

EPM7064

四、测试步骤

下面使用 Quartus II6.0 对本设计进行编译和仿真。首先创建工程,使用文

本编辑器输入本设计的所有模块的源程序,把 miaobiao.vhd 设为顶层文件。把本

设计中的所有设计文件添加进工程后,先对每个模块进行编译纠错,然后把各个

模块连接在一起保存然后在全程编译,通过之后就可以进行仿真。先进行软件仿

真每一部分的仿真从略,下面只说明系统的整体仿真波形。系统工作时的仿真波

形如图所示。

5

�

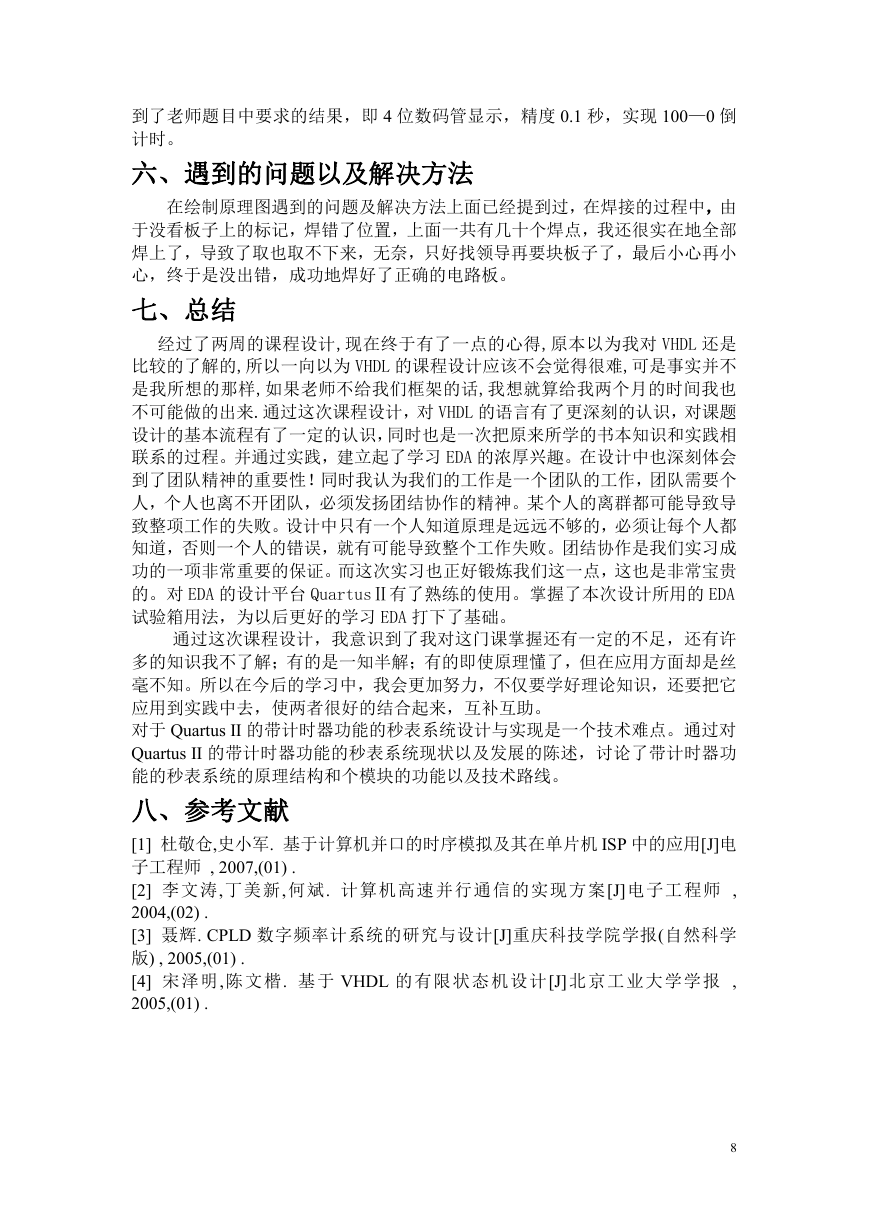

确定准确无误后然后开始锁定管脚,执行菜单命令 assignments→pins 出现如

下:

锁定后的管脚结果如下:

Node

Name

a13

b12

Direction

Output

Output

Location

PIN_2

PIN_3

6

�

c9

clk

clkdsp

d10

e11

f8

g

lamp[2]

lamp[1]

lamp[0]

reset

sel[2]

sel[1]

sel[0]

setmsec

setsec

Output

Input

Input

Output

Output

Output

Output

Output

Output

Output

Input

Output

Output

Output

Input

Input

Pin_4

PIN_28

PIN_6

PIN_7

PIN_8

PIN_11

PIN_12

PIN_37

PIN_39

PIN_38

PIN_16

PIN_19

PIN_18

PIN_17

PIN_20

PIN_21

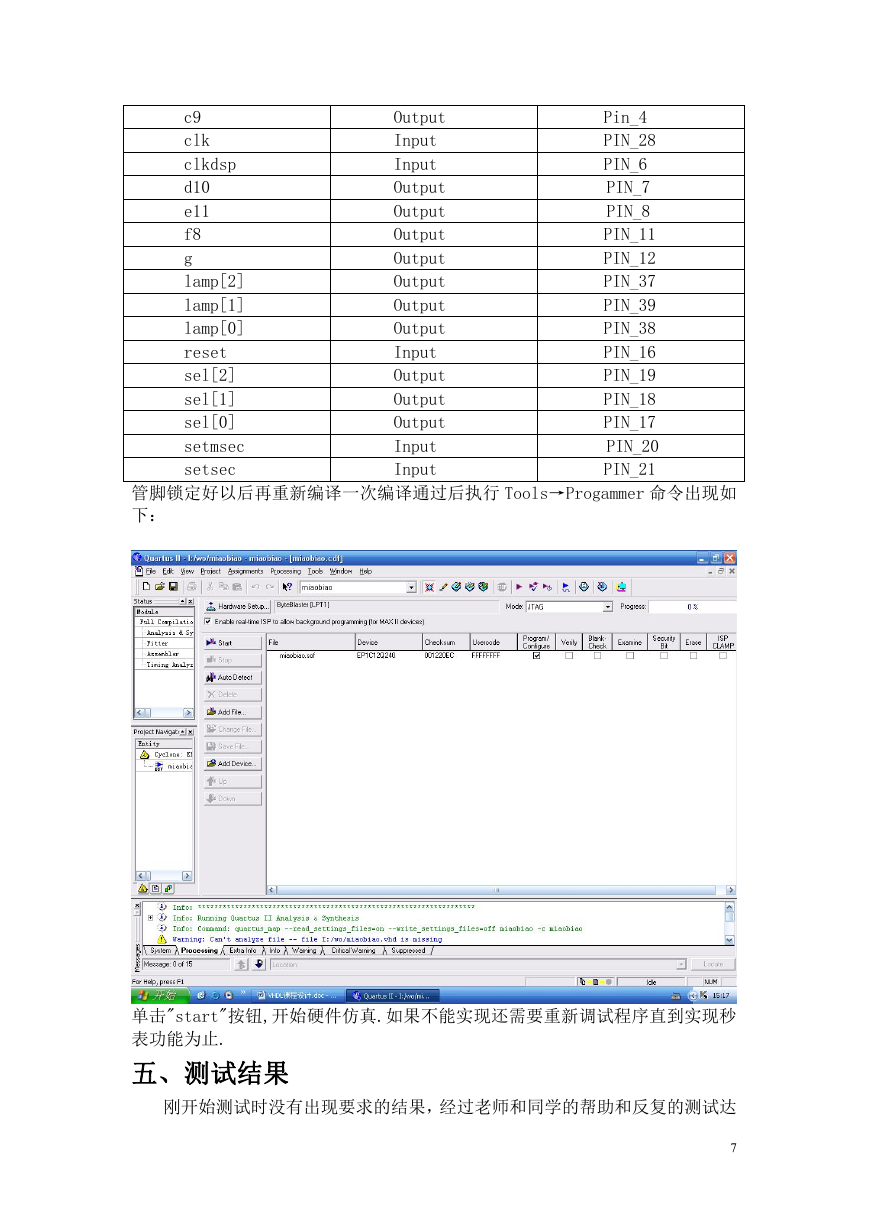

管脚锁定好以后再重新编译一次编译通过后执行 Tools→Progammer 命令出现如

下:

单击"start"按钮,开始硬件仿真.如果不能实现还需要重新调试程序直到实现秒

表功能为止.

五、测试结果

刚开始测试时没有出现要求的结果,经过老师和同学的帮助和反复的测试达

7

�

到了老师题目中要求的结果,即 4 位数码管显示,精度 0.1 秒,实现 100—0 倒

计时。

六、遇到的问题以及解决方法

在绘制原理图遇到的问题及解决方法上面已经提到过,在焊接的过程中,由

于没看板子上的标记,焊错了位置,上面一共有几十个焊点,我还很实在地全部

焊上了,导致了取也取不下来,无奈,只好找领导再要块板子了,最后小心再小

心,终于是没出错,成功地焊好了正确的电路板。

七、总结

经过了两周的课程设计,现在终于有了一点的心得,原本以为我对 VHDL 还是

比较的了解的,所以一向以为 VHDL 的课程设计应该不会觉得很难,可是事实并不

是我所想的那样,如果老师不给我们框架的话,我想就算给我两个月的时间我也

不可能做的出来.通过这次课程设计,对 VHDL 的语言有了更深刻的认识,对课题

设计的基本流程有了一定的认识,同时也是一次把原来所学的书本知识和实践相

联系的过程。并通过实践,建立起了学习 EDA 的浓厚兴趣。在设计中也深刻体会

到了团队精神的重要性!同时我认为我们的工作是一个团队的工作,团队需要个

人,个人也离不开团队,必须发扬团结协作的精神。某个人的离群都可能导致导

致整项工作的失败。设计中只有一个人知道原理是远远不够的,必须让每个人都

知道,否则一个人的错误,就有可能导致整个工作失败。团结协作是我们实习成

功的一项非常重要的保证。而这次实习也正好锻炼我们这一点,这也是非常宝贵

的。对 EDA 的设计平台 QuartusⅡ有了熟练的使用。掌握了本次设计所用的 EDA

试验箱用法,为以后更好的学习 EDA 打下了基础。

通过这次课程设计,我意识到了我对这门课掌握还有一定的不足,还有许

多的知识我不了解;有的是一知半解;有的即使原理懂了,但在应用方面却是丝

毫不知。所以在今后的学习中,我会更加努力,不仅要学好理论知识,还要把它

应用到实践中去,使两者很好的结合起来,互补互助。

对于 Quartus II 的带计时器功能的秒表系统设计与实现是一个技术难点。通过对

Quartus II 的带计时器功能的秒表系统现状以及发展的陈述,讨论了带计时器功

能的秒表系统的原理结构和个模块的功能以及技术路线。

八、参考文献

[1] 杜敬仓,史小军. 基于计算机并口的时序模拟及其在单片机 ISP 中的应用[J]电

子工程师 , 2007,(01) .

[2] 李文涛,丁美新,何斌. 计算机高速并行通信的实现方案[J]电子工程师 ,

2004,(02) .

[3] 聂辉. CPLD 数字频率计系统的研究与设计[J]重庆科技学院学报(自然科学

版) , 2005,(01) .

[4] 宋泽明,陈文楷. 基于 VHDL 的有限状态机设计[J]北京工业大学学报 ,

2005,(01) .

8

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc