JESD204B IP 内核用户指南

订阅

反馈

Quartus Prime 设计套件的最后更新 : 15.1

UG-01142

2015.11.02

101 Innovation Drive

San Jose, CA 95134

www.altera.com

�

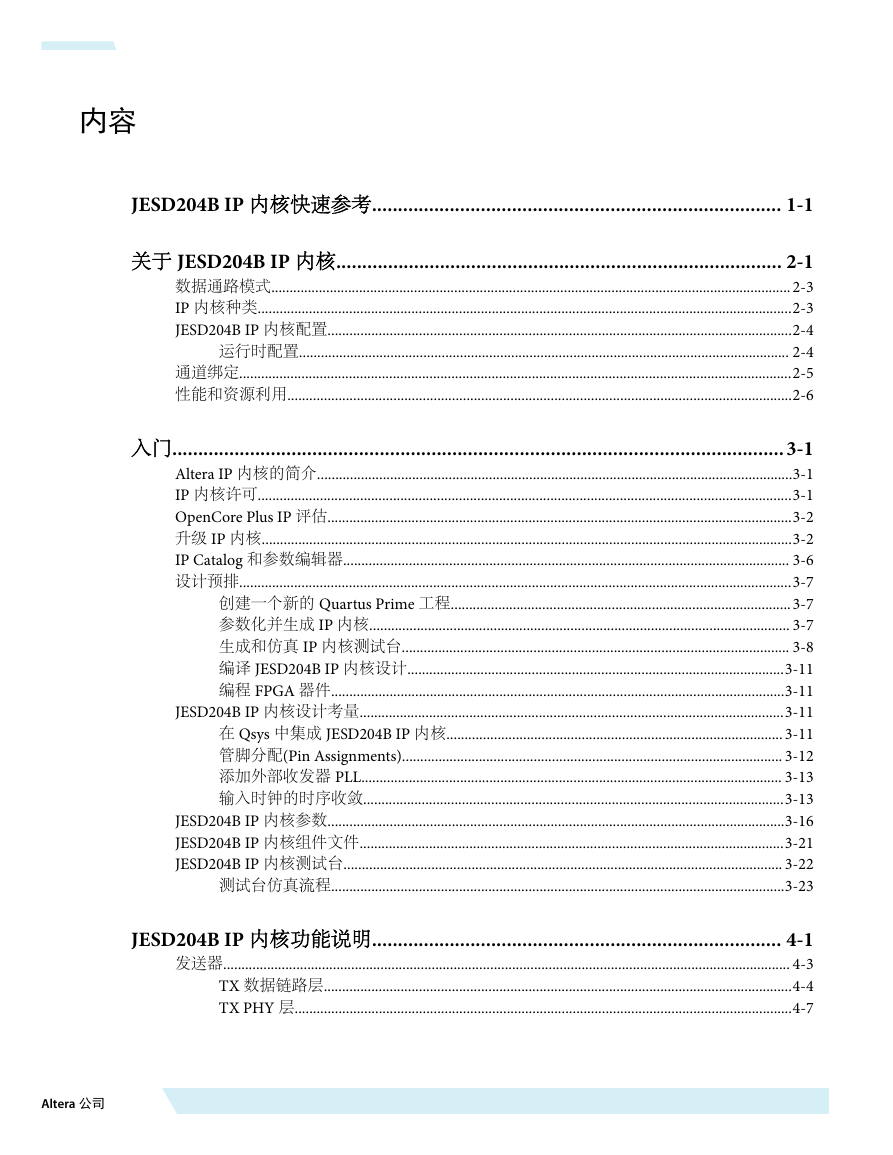

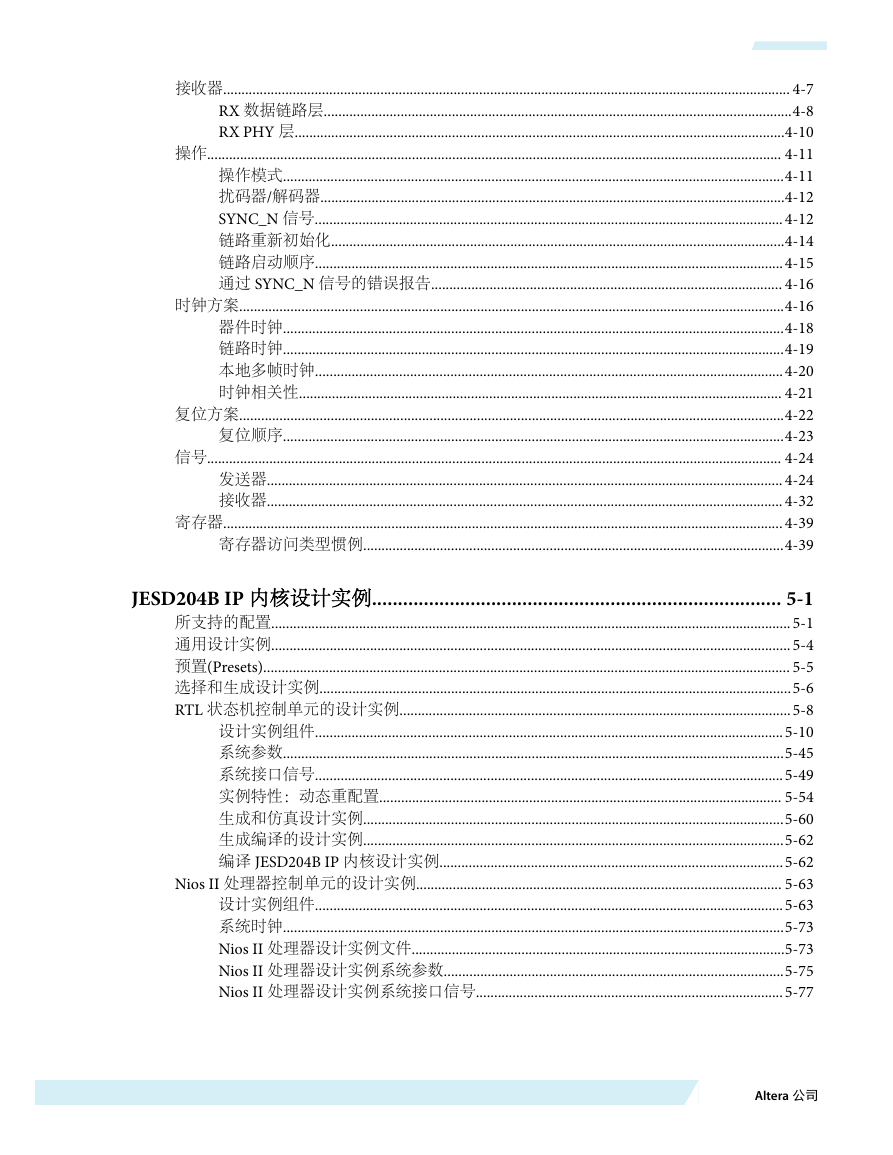

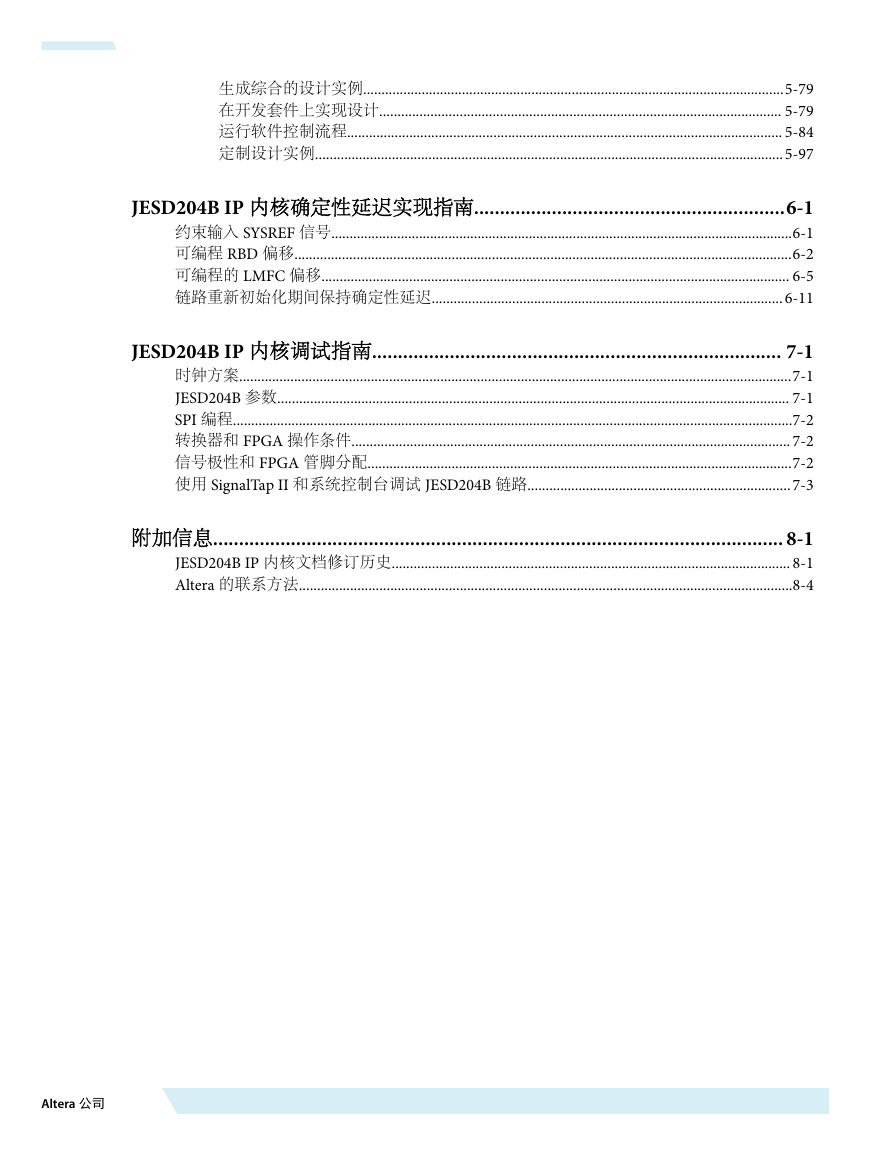

内容

JESD204B IP 内核快速参考............................................................................... 1-1

关于 JESD204B IP 内核...................................................................................... 2-1

数据通路模式..............................................................................................................................................2-3

IP 内核种类..................................................................................................................................................2-3

JESD204B IP 内核配置...............................................................................................................................2-4

运行时配置...................................................................................................................................... 2-4

通道绑定.......................................................................................................................................................2-5

性能和资源利用..........................................................................................................................................2-6

入门......................................................................................................................3-1

Altera IP 内核的简介..................................................................................................................................3-1

IP 内核许可..................................................................................................................................................3-1

OpenCore Plus IP 评估...............................................................................................................................3-2

升级 IP 内核.................................................................................................................................................3-2

IP Catalog 和参数编辑器.......................................................................................................................... 3-6

设计预排.......................................................................................................................................................3-7

创建一个新的 Quartus Prime 工程.............................................................................................3-7

参数化并生成 IP 内核................................................................................................................... 3-7

生成和仿真 IP 内核测试台.......................................................................................................... 3-8

编译 JESD204B IP 内核设计.......................................................................................................3-11

编程 FPGA 器件............................................................................................................................3-11

JESD204B IP 内核设计考量....................................................................................................................3-11

在 Qsys 中集成 JESD204B IP 内核............................................................................................3-11

管脚分配(Pin Assignments)........................................................................................................ 3-12

添加外部收发器 PLL................................................................................................................... 3-13

输入时钟的时序收敛...................................................................................................................3-13

JESD204B IP 内核参数.............................................................................................................................3-16

JESD204B IP 内核组件文件....................................................................................................................3-21

JESD204B IP 内核测试台........................................................................................................................ 3-22

测试台仿真流程............................................................................................................................3-23

JESD204B IP 内核功能说明............................................................................... 4-1

发送器........................................................................................................................................................... 4-3

TX 数据链路层................................................................................................................................4-4

TX PHY 层........................................................................................................................................4-7

Altera 公司

�

接收器........................................................................................................................................................... 4-7

RX 数据链路层................................................................................................................................4-8

RX PHY 层......................................................................................................................................4-10

操作............................................................................................................................................................. 4-11

操作模式.........................................................................................................................................4-11

扰码器/解码器...............................................................................................................................4-12

SYNC_N 信号................................................................................................................................4-12

链路重新初始化............................................................................................................................4-14

链路启动顺序................................................................................................................................4-15

通过 SYNC_N 信号的错误报告................................................................................................ 4-16

时钟方案.....................................................................................................................................................4-16

器件时钟.........................................................................................................................................4-18

链路时钟.........................................................................................................................................4-19

本地多帧时钟................................................................................................................................4-20

时钟相关性.................................................................................................................................... 4-21

复位方案.....................................................................................................................................................4-22

复位顺序.........................................................................................................................................4-23

信号............................................................................................................................................................. 4-24

发送器............................................................................................................................................. 4-24

接收器............................................................................................................................................. 4-32

寄存器......................................................................................................................................................... 4-39

寄存器访问类型惯例...................................................................................................................4-39

JESD204B IP 内核设计实例............................................................................... 5-1

所支持的配置..............................................................................................................................................5-1

通用设计实例..............................................................................................................................................5-4

预置(Presets)................................................................................................................................................ 5-5

选择和生成设计实例.................................................................................................................................5-6

RTL 状态机控制单元的设计实例...........................................................................................................5-8

设计实例组件................................................................................................................................5-10

系统参数.........................................................................................................................................5-45

系统接口信号................................................................................................................................5-49

实例特性:动态重配置.............................................................................................................. 5-54

生成和仿真设计实例...................................................................................................................5-60

生成编译的设计实例...................................................................................................................5-62

编译 JESD204B IP 内核设计实例..............................................................................................5-62

Nios II 处理器控制单元的设计实例.................................................................................................... 5-63

设计实例组件................................................................................................................................5-63

系统时钟.........................................................................................................................................5-73

Nios II 处理器设计实例文件......................................................................................................5-73

Nios II 处理器设计实例系统参数.............................................................................................5-75

Nios II 处理器设计实例系统接口信号....................................................................................5-77

Altera 公司

�

生成综合的设计实例...................................................................................................................5-79

在开发套件上实现设计.............................................................................................................. 5-79

运行软件控制流程....................................................................................................................... 5-84

定制设计实例................................................................................................................................5-97

JESD204B IP 内核确定性延迟实现指南............................................................6-1

约束输入 SYSREF 信号..............................................................................................................................6-1

可编程 RBD 偏移........................................................................................................................................6-2

可编程的 LMFC 偏移................................................................................................................................ 6-5

链路重新初始化期间保持确定性延迟................................................................................................6-11

JESD204B IP 内核调试指南............................................................................... 7-1

时钟方案.......................................................................................................................................................7-1

JESD204B 参数............................................................................................................................................ 7-1

SPI 编程.........................................................................................................................................................7-2

转换器和 FPGA 操作条件........................................................................................................................ 7-2

信号极性和 FPGA 管脚分配....................................................................................................................7-2

使用 SignalTap II 和系统控制台调试 JESD204B 链路........................................................................7-3

附加信息.............................................................................................................. 8-1

JESD204B IP 内核文档修订历史............................................................................................................. 8-1

Altera 的联系方法.......................................................................................................................................8-4

Altera 公司

�

JESD204B IP 内核快速参考 1

2015.11.02

UG-01142

订阅

反馈

Altera JESD204B MegaCore®功能是一种高速点对点串行接口知识产权(IP)。

JESD204B MegaCore 功能是 MegaCore IP 库的一部分,它与 Quartus® Prime 软件一起发布,可以从

Altera 网站(www.altera.com)中下载该软件。

注意: 有关系统要求和安装说明信息,请参考 Altera 软件安装和许可。

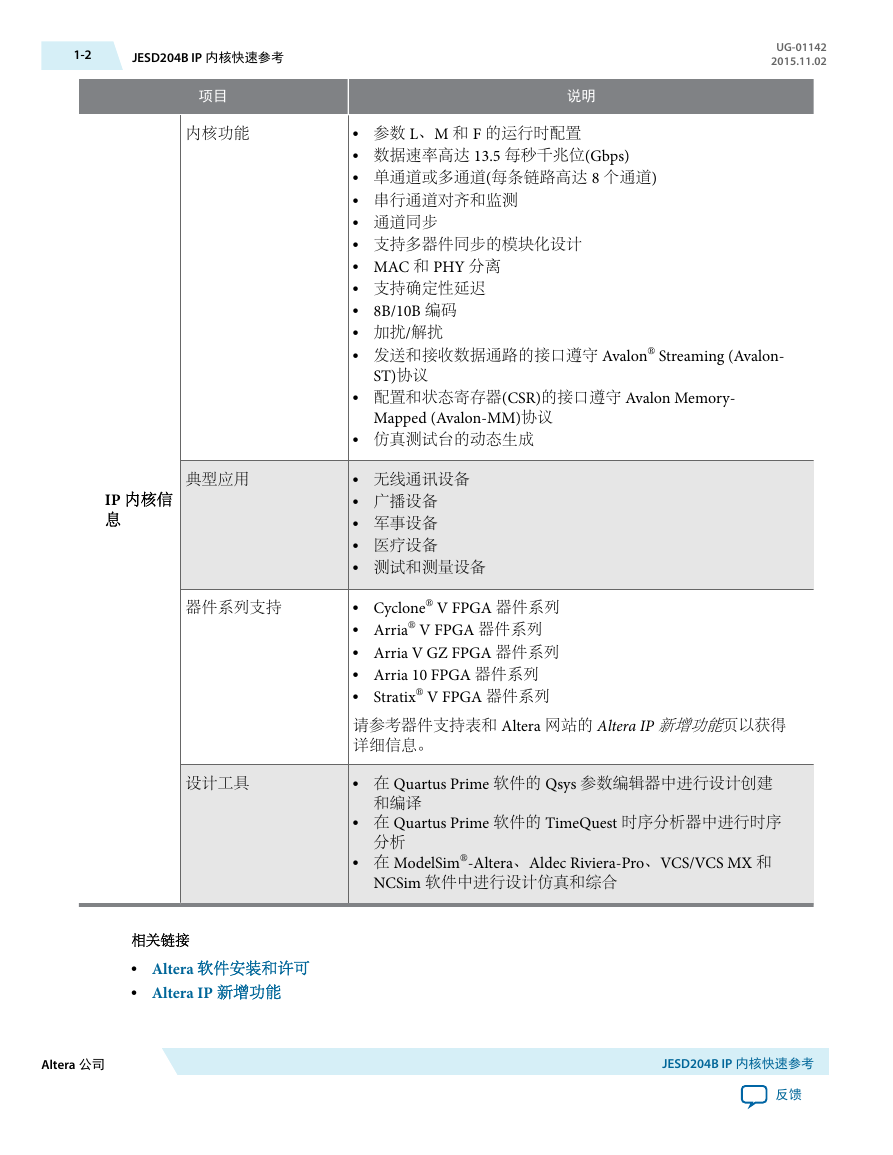

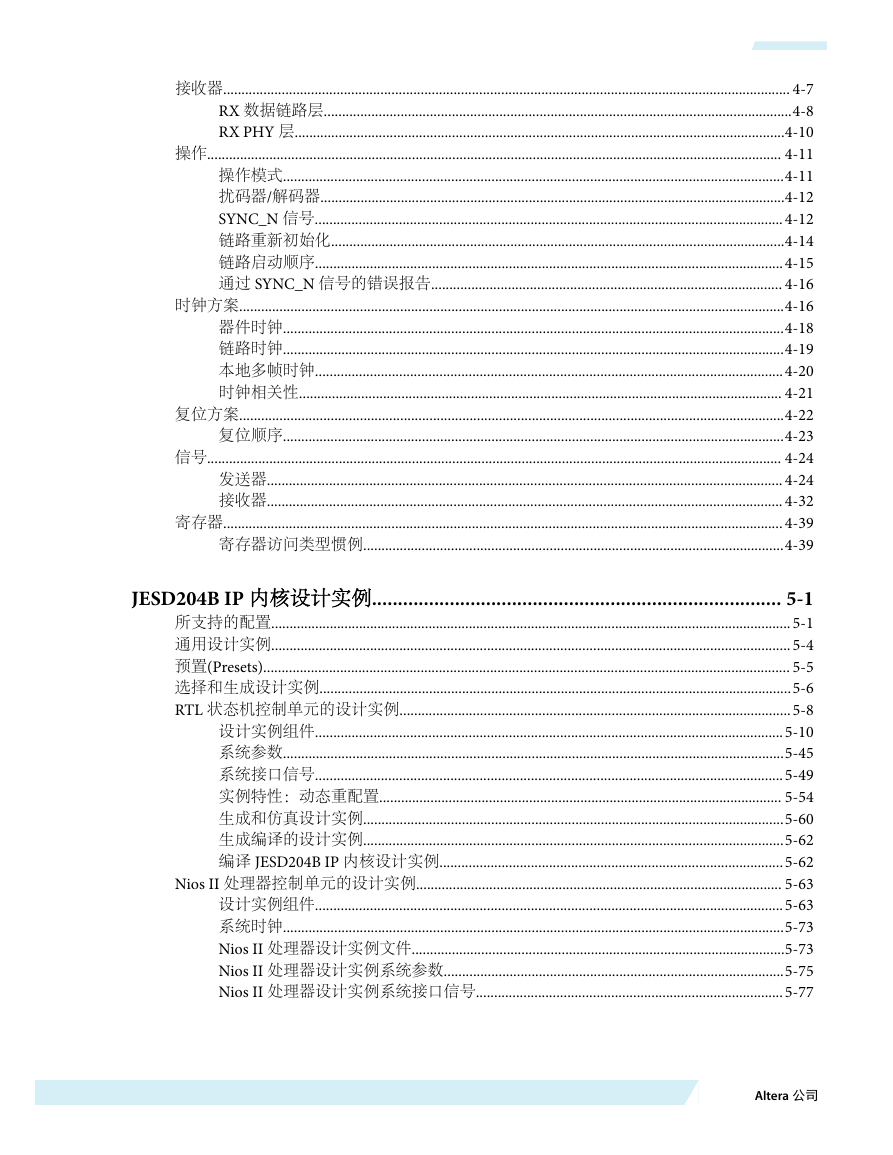

表 1-1: JESD204B IP 内核的简要信息

项目

版本

发布日期

发布信息

订购代码

产品 ID

供应商 ID

IP 内核信

息

协议功能

说明

15.1

2015 年 11 月

IP-JESD204B

0116

6AF7

• 联合电子器件工程委员会(JEDEC) JESD204B。01,2012 标

准发布规范

• 器件子类(subclass):

• Subclass 0 — 向后兼容 JESD204A。

• Subclass 1 — 使用 SYSREF 信号来支持确定性延迟。

• Subclass 2 — 使用 SYNC_N 检测来支持确定性延迟。

© 2016 Intel Corporation. All rights reserved. Intel, the Intel logo, Altera, Arria, Cyclone, Enpirion, MAX, NIOS, Quartus and Stratix words and logos are

trademarks of Intel Corporation in the US and/or other countries. Other marks and brands may be claimed as the property of others. Intel warrants

performance of its FPGA and semiconductor products to current specifications in accordance with Intel's standard warranty, but reserves the right to make

changes to any products and services at any time without notice. Intel assumes no responsibility or liability arising out of the application or use of any

information, product, or service described herein except as expressly agreed to in writing by Intel. Intel customers are advised to obtain the latest version of

device specifications before relying on any published information and before placing orders for products or services.

ISO

9001:2008

Registered

www.altera.com

101 Innovation Drive, San Jose, CA 95134

�

1-2

JESD204B IP 内核快速参考

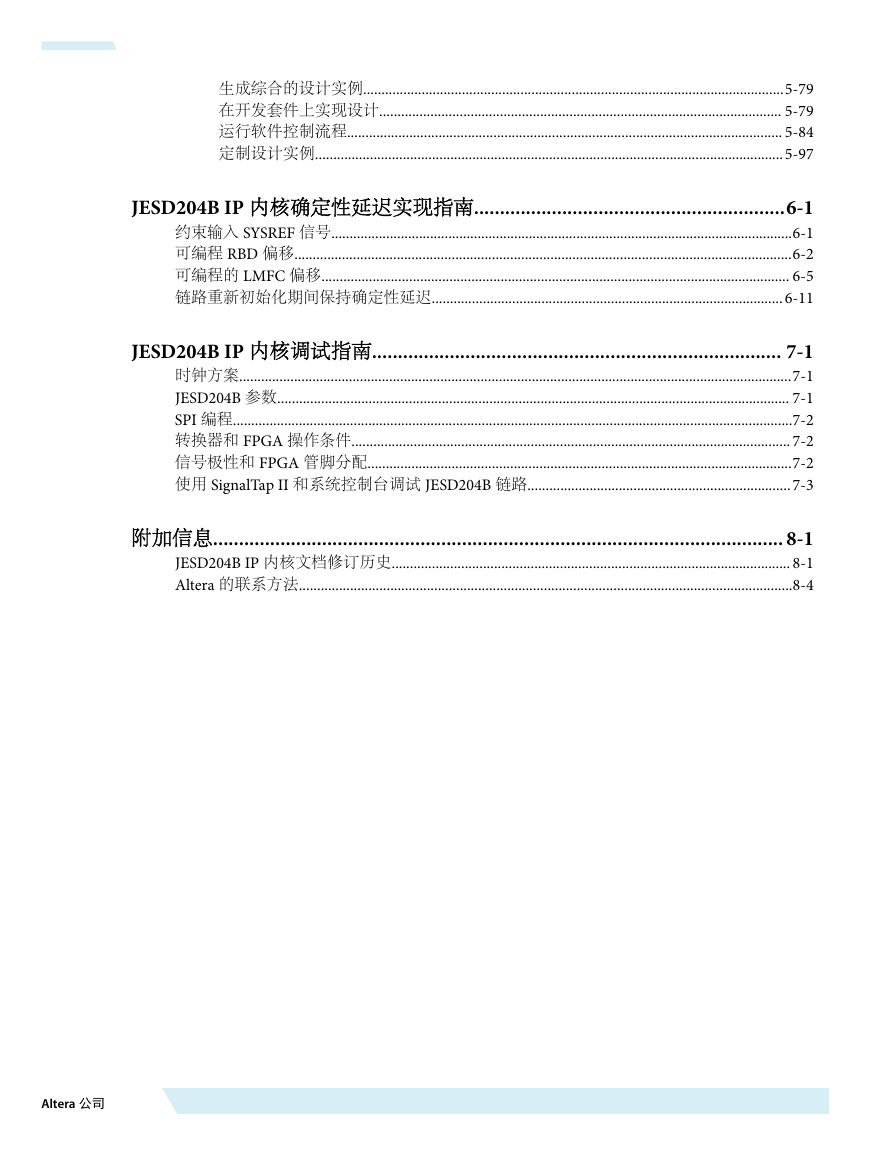

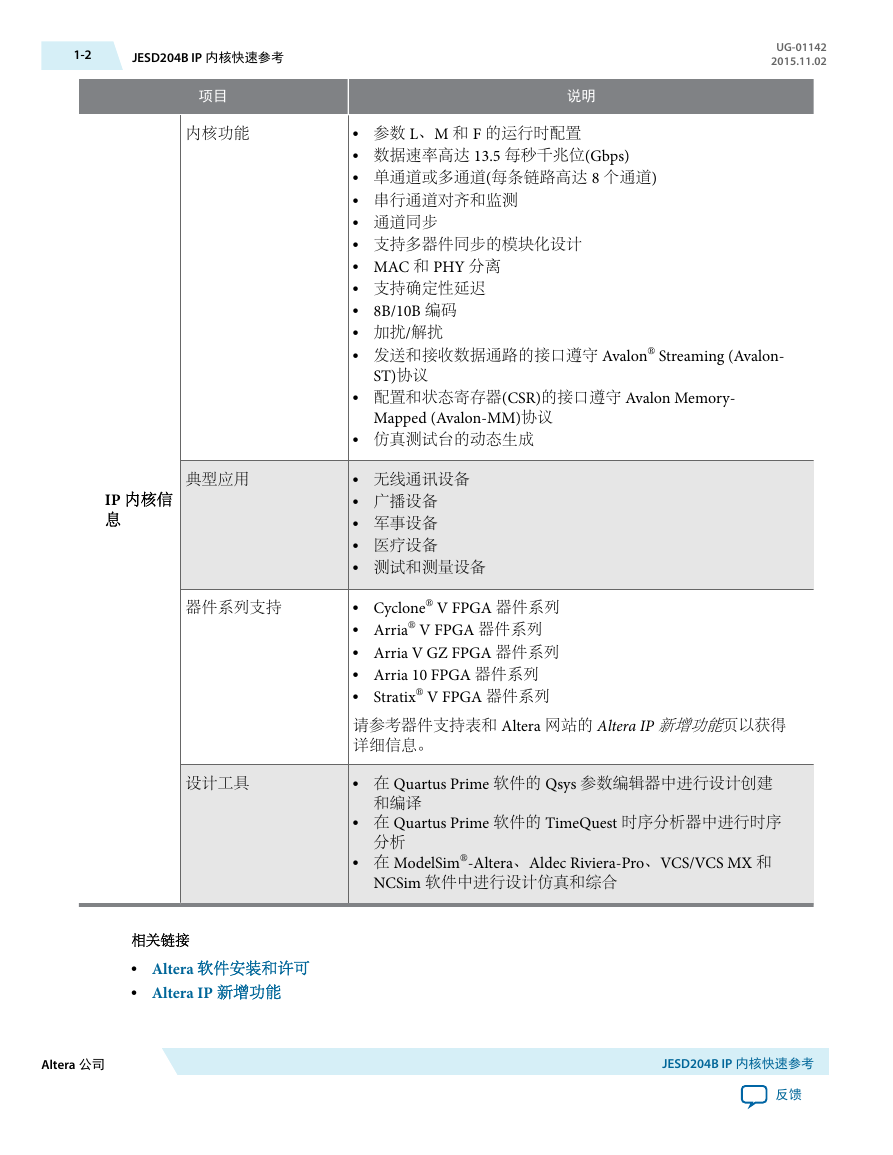

项目

内核功能

UG-01142

2015.11.02

说明

• 参数 L、M 和 F 的运行时配置

• 数据速率高达 13.5 每秒千兆位(Gbps)

• 单通道或多通道(每条链路高达 8 个通道)

• 串行通道对齐和监测

• 通道同步

• 支持多器件同步的模块化设计

• MAC 和 PHY 分离

• 支持确定性延迟

• 8B/10B 编码

• 加扰/解扰

• 发送和接收数据通路的接口遵守 Avalon® Streaming (Avalon-

ST)协议

• 配置和状态寄存器(CSR)的接口遵守 Avalon Memory-

Mapped (Avalon-MM)协议

• 仿真测试台的动态生成

典型应用

IP 内核信

息

• 无线通讯设备

• 广播设备

• 军事设备

• 医疗设备

• 测试和测量设备

器件系列支持

设计工具

相关链接

• Altera 软件安装和许可

• Altera IP 新增功能

Altera 公司

• Cyclone® V FPGA 器件系列

• Arria® V FPGA 器件系列

• Arria V GZ FPGA 器件系列

• Arria 10 FPGA 器件系列

• Stratix® V FPGA 器件系列

请参考器件支持表和 Altera 网站的 Altera IP 新增功能页以获得

详细信息。

• 在 Quartus Prime 软件的 Qsys 参数编辑器中进行设计创建

和编译

分析

• 在 Quartus Prime 软件的 TimeQuest 时序分析器中进行时序

• 在 ModelSim®-Altera、Aldec Riviera-Pro、VCS/VCS MX 和

NCSim 软件中进行设计仿真和综合

JESD204B IP 内核快速参考

反馈

�

UG-01142

2015.11.02

JESD204B IP 内核快速参考

1-3

JESD204B IP 内核发布说明

•

• 知识库中 JESD204B IP 内核的勘误表

JESD204B IP 内核快速参考

反馈

Altera 公司

�

关于 JESD204B IP 内核 2

2015.11.02

UG-01142

订阅

反馈

Altera JESD204B IP 内核是数模(DAC)或模数(ADC)转换器的一种高速点对点串行接口,用于传输

数据到 FPGA 器件。这种单向串行接口运行在 13.5 Gbps 的最大数据速率上。该协议提供了较高的

带宽、低 I/O 数并且支持通道数和数据速率的可扩展性。JESD204B IP 内核通过引进 Subclass 1 和

Subclass 2 以实现了确定性延迟,从而解决了多器件同步。

JESD204B IP 内核包含:

• 介质访问控制(MAC) — 控制链路状态和字符替换的数据链路层(DLL)模块。

• 物理层(PHY) — 物理编码子层(PCS)和物理介质附加子层(PMA)模块。

JESD204B IP 内核不包含控制帧装配和拆卸的传输层(TL)。TL 和测试组件提供为设计实例组件的

一部分,该设计实例组件可以对不同的转换器件定制设计。

© 2016 Intel Corporation. All rights reserved. Intel, the Intel logo, Altera, Arria, Cyclone, Enpirion, MAX, NIOS, Quartus and Stratix words and logos are

trademarks of Intel Corporation in the US and/or other countries. Other marks and brands may be claimed as the property of others. Intel warrants

performance of its FPGA and semiconductor products to current specifications in accordance with Intel's standard warranty, but reserves the right to make

changes to any products and services at any time without notice. Intel assumes no responsibility or liability arising out of the application or use of any

information, product, or service described herein except as expressly agreed to in writing by Intel. Intel customers are advised to obtain the latest version of

device specifications before relying on any published information and before placing orders for products or services.

ISO

9001:2008

Registered

www.altera.com

101 Innovation Drive, San Jose, CA 95134

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc