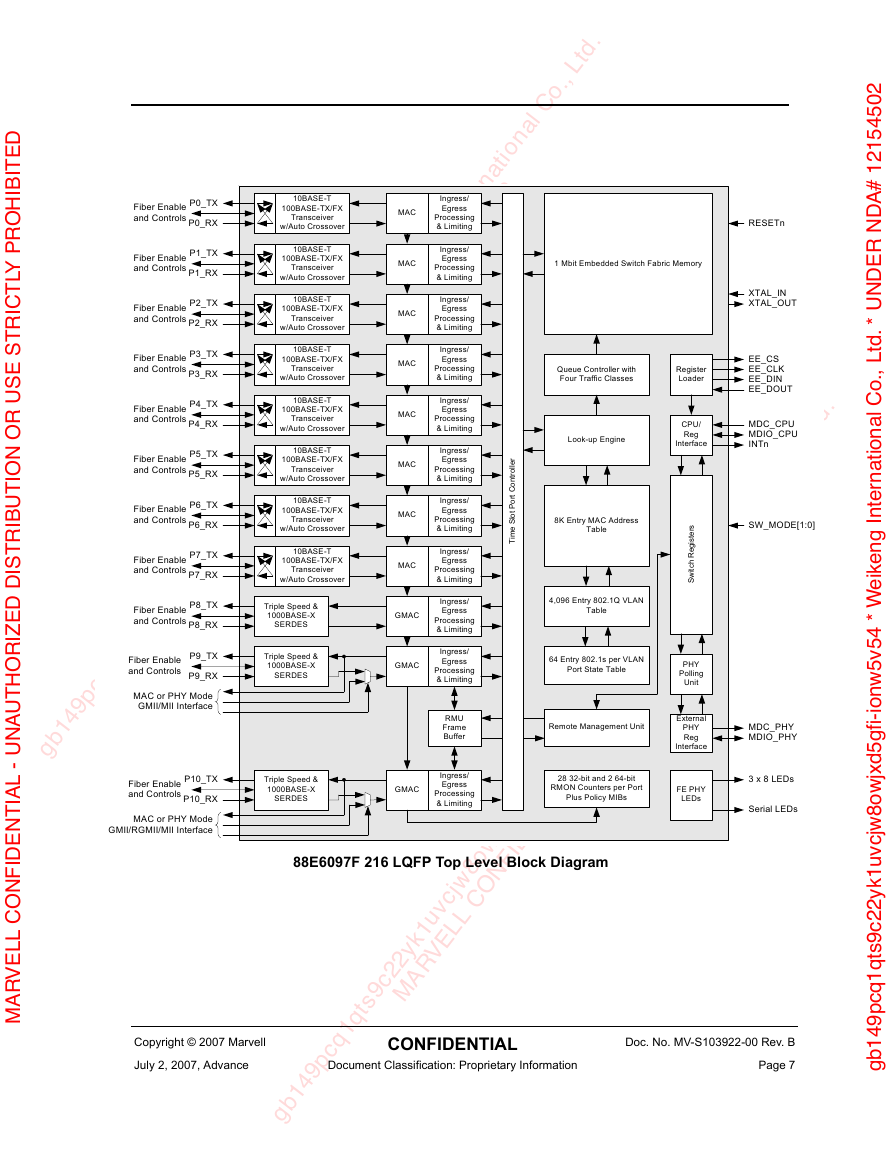

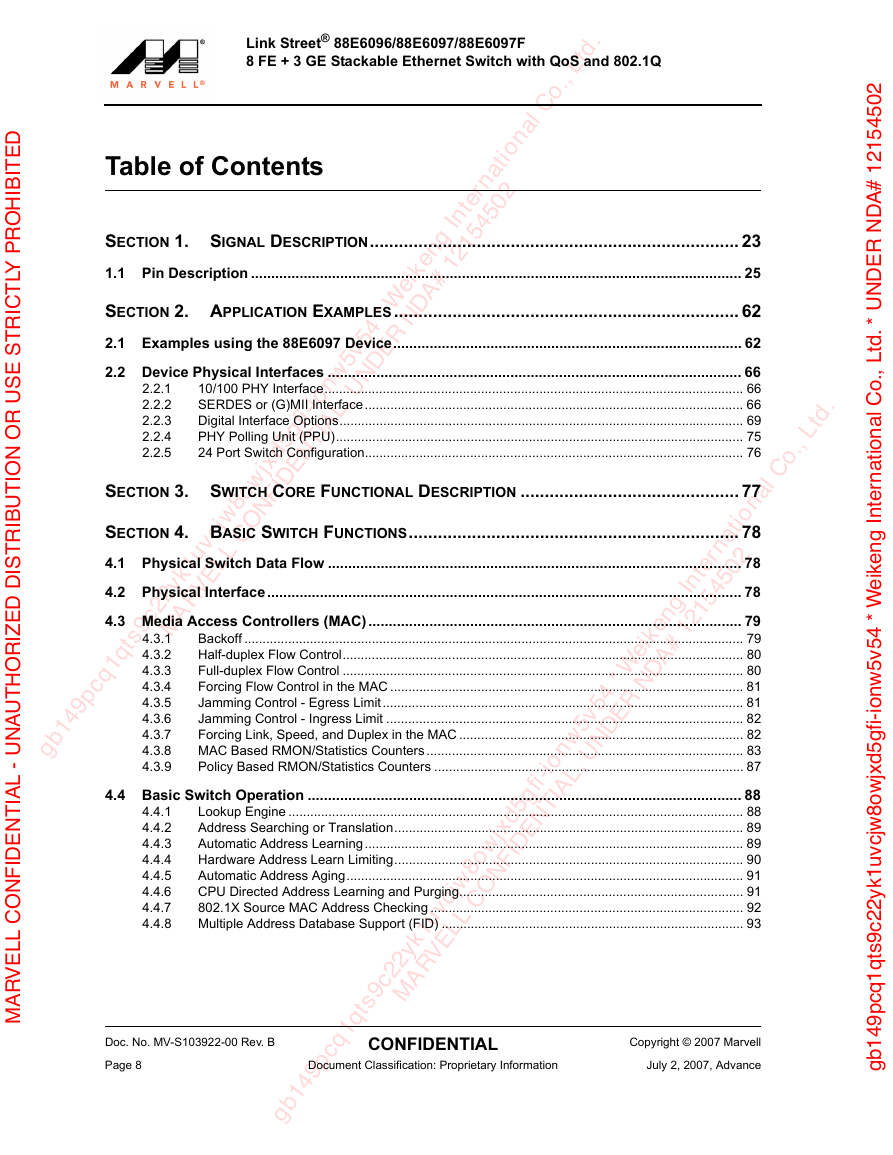

Section 1. Signal Description

1.1 Pin Description

Section 2. Application Examples

2.1 Examples using the 88E6097 Device

2.2 Device Physical Interfaces

2.2.1 10/100 PHY Interface

2.2.2 SERDES or (G)MII Interface

2.2.3 Digital Interface Options

2.2.4 PHY Polling Unit (PPU)

2.2.5 24 Port Switch Configuration

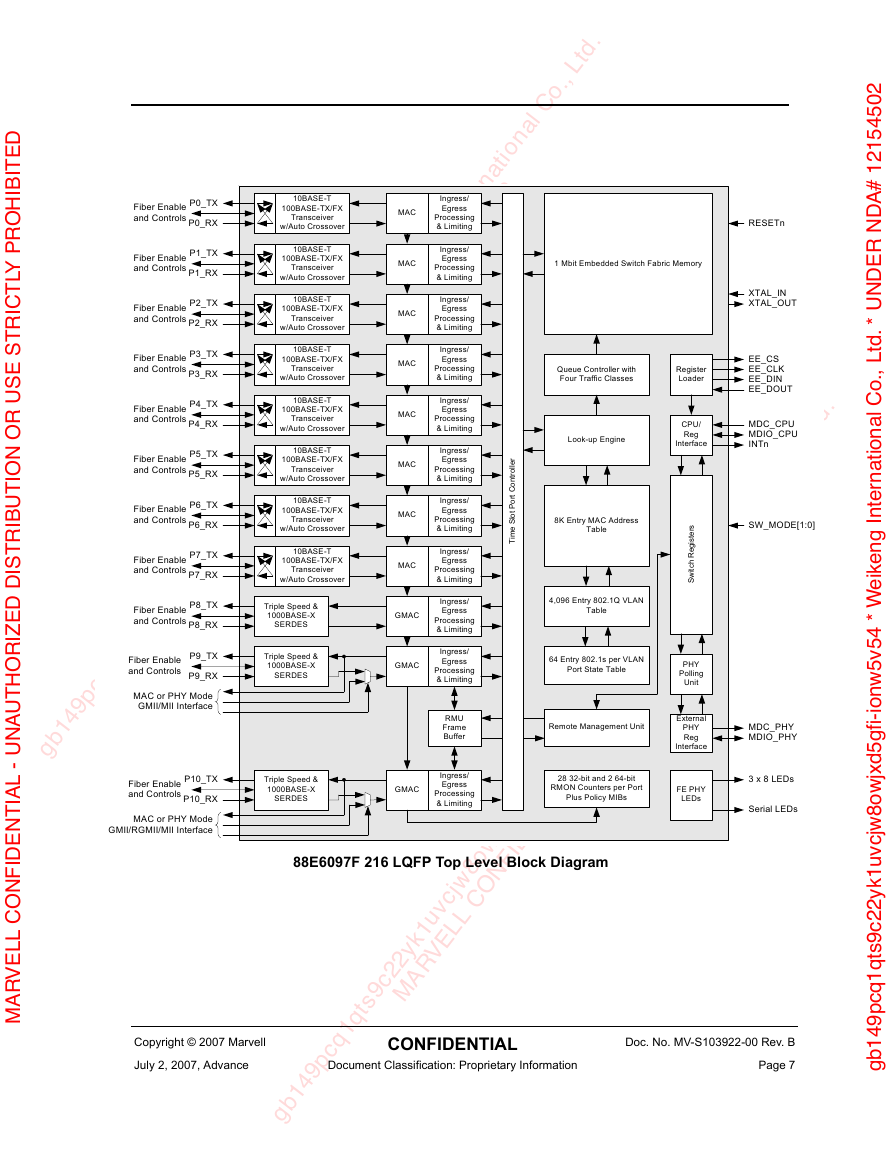

Section 3. Switch Core Functional Description

Section 4. Basic Switch Functions

4.1 Physical Switch Data Flow

4.2 Physical Interface

4.3 Media Access Controllers (MAC)

4.3.1 Backoff

4.3.2 Half-duplex Flow Control

4.3.3 Full-duplex Flow Control

4.3.4 Forcing Flow Control in the MAC

4.3.5 Jamming Control - Egress Limit

4.3.6 Jamming Control - Ingress Limit

4.3.7 Forcing Link, Speed, and Duplex in the MAC

4.3.8 MAC Based RMON/Statistics Counters

4.3.9 Policy Based RMON/Statistics Counters

4.4 Basic Switch Operation

4.4.1 Lookup Engine

4.4.2 Address Searching or Translation

4.4.3 Automatic Address Learning

4.4.4 Hardware Address Learn Limiting

4.4.5 Automatic Address Aging

4.4.6 CPU Directed Address Learning and Purging

4.4.7 802.1X Source MAC Address Checking

4.4.8 Multiple Address Database Support (FID)

Section 5. Normal Network Ports

5.1 Ingress Policy

5.1.1 Port States Filtering for 802.1D Spanning Tree

5.1.2 Source Address Filtering

5.1.3 Layer 2 Policy Control Lists (88E6097 Only)

5.2 VLANS

5.2.1 Port Based VLANs

5.2.2 802.1Q VLANs

5.2.3 802.1s Per VLAN Spanning Tree

5.3 Special Frame Handling

5.3.1 Switching Frames Back to their Source Port

5.3.2 Tunneling Frames through VLANs

5.3.3 ARP Mirroring

5.3.4 IGMP/MLD Trapping or Snooping

5.4 Quality of Service (QoS) Classification

5.4.1 IEEE Tagged Frame Priority Extraction

5.4.2 IPv4 and IPv6 Frame Priority Extraction

5.4.3 Default Priority

5.4.4 Initial Priority Selection

5.4.5 Frame Type Priority Override

5.4.6 Layer 2 Priority Override

5.5 Port Based Ingress Rate Limiting (PIRL)

5.6 Queue Controller

5.6.1 Frame Latencies

5.6.2 No Head-of-Line Blocking

5.6.3 QoS with and without Flow Control

5.6.4 Guaranteed Frame Delivery without Flow Control

5.6.5 The Queues

5.6.6 Per Port Fixed or Weighted Priority

5.6.7 Programmable Weighting Table (88E6097 Only)

5.7 Embedded Memory

5.8 Egress Policy

5.8.1 Forward Unknown/Secure Port

5.8.2 Forward Unknown for Multicasts

5.8.3 Secure 802.1Q VLANs

5.8.4 Tagging and Untagging Frames

5.8.5 Egress Rate Shaping

Section 6. Provider Mode Ports

6.1 Customer to Provider

6.2 Provider to Customer

6.2.1 Provider VID Processing

6.2.2 Provider QoS Processing

6.3 Customer to Customer

6.4 Provider to Provider

6.5 Recursive Provider Tag Stripping

6.6 Restrictions on Provider Ports

6.7 Restrictions on Customer Ports

Section 7. Distributed Switch Architecture (DSA) Ports

7.1 Forward DSA Tag

7.2 To_CPU DSA Tag

7.3 From_CPU DSA Tags

7.4 To_Sniffer DSA Tag

7.5 Cross-chip Features Using DSA Links

7.5.1 Cross-chip Flow Control

7.5.2 Cross-chip 802.1Q VLANs

7.5.3 Cross-chip Port Based VLANs

7.6 Switch Handling of DSA MGMT Frames

7.7 Proper Usage of DSA Tag Ports

7.8 Secure Control Technology (SCT)

7.9 Ether Type DSA Tag

Section 8. Advanced Switch Functions

8.1 Management Frames to and from the CPU

8.2 Spanning Tree Support

8.3 Ingress MGMT/BPDU Frame Detection

8.3.1 Reserved Multicast Address Support

8.3.2 New and Proprietary Protocol Support

8.4 Other Ingress MGMT Frame Detection

8.5 MGMT Frames to Normal or Provider Egress

8.6 Proper Connection to a Management CPU

8.7 Proper Connection to a Router

8.7.1 Switch Ingress Header for CPU Routers

8.7.2 Switch Egress Header for CPU Routers

8.8 MUX’ing or Ignoring Address Translation

8.8.1 Passing Frames to a Router

8.8.2 Operational, Administration, and Maintenance (OAM) Loopback

8.9 Port Mirroring Support

8.10 Port Trunking Support

8.10.1 Trunk Address Learning

8.10.2 Trunk Address Searching

8.10.3 Trunk Mapping

8.10.4 Load Balancing

8.11 Interrupt Controller

8.11.1 Device Interrupts

Section 9. Accessing Data Structures

9.1 Address Translation Unit Operations

9.1.1 Format of the ATU Database

9.1.2 Reading the Address Database

9.1.3 Loading & Purging an Entry in the Address Database

9.1.4 Flushing Entries

9.1.5 Moving or Removing Single Port Mappings

9.1.6 Servicing ATU Violations

9.1.7 ATU Statistics

9.2 VLAN Translation Unit Operations

9.2.1 Format of the VTU Database

9.2.2 Reading the VLAN Database

9.2.3 Loading and Purging an Entry in the VLAN Database

9.2.4 Flushing Entries

9.2.5 Servicing VTU Violations

9.2.6 Format of the STU Database

9.2.7 Reading the SID Database

9.2.8 Loading and Purging an Entry in the STU Database

9.2.9 Flushing Entries

Section 10. Remote Management

10.1 Request for Frame Format - Layer 2 and DSA Portion

10.1.1 RMU and Ether type DSA

10.1.2 RMU and Marvell® Header

10.2 Response Frame Format - Layer 2 and DSA Portion

10.2.1 Restrictions of Remote Management

10.3 Request Frame Format - Layer 3

10.3.1 The Initial Request Frame - GetID

10.4 Response Frame Format - Layer 3

10.4.1 The Initial Response Frame - GotID

10.4.2 Error Handling

10.5 Supported Requests and Responses

10.5.1 GetID (non-destructive)

10.5.2 Dump ATU (non-destructive)

10.5.3 Dump MIBs (non-destructive)

10.5.4 Dump MIBs and Clear (destructive)

10.5.5 Read/Write Register (may be destructive)

10.5.6 Error Response Frame (non-destructive)

Section 11. Physical Interface (PHY) Functional Description (P0 to P7)

11.1 Transmit PCS and PMA

11.1.1 100BASE-TX Transmitter

11.1.2 4B/5B Encoding

11.1.3 Scrambler

11.1.4 NRZ to NRZI Conversion

11.1.5 Pre-Driver and Transmit Clock

11.1.6 Multimode Transmit DAC

11.2 Receive PCS and PMA

11.2.1 10-BASE-T/100BASE-TX Receiver

11.2.2 AGC and Baseline Wander

11.2.3 ADC and Digital Adaptive Equalizer

11.2.4 Digital Phased Locked Loop (DPLL)

11.2.5 NRZI to NRZ Conversion

11.2.6 Descrambler

11.2.7 Serial to Parallel Conversion and 5B/4B Code-Group Alignment

11.2.8 5B/4B Decoder

11.2.8.1 FIFO

11.2.8.2 100BASE-FX Receiver

11.2.8.3 Far End Fault Indication (FEFI)

11.2.8.4 10BASE-T Receiver

11.2.9 Setting Cable Characteristics

11.2.10 Scrambler/Descrambler

11.2.11 Link Monitor

11.2.12 Auto-Negotiation

11.2.13 Register Update

11.2.14 Next Page Support

11.2.15 Status Registers

11.3 Power Management

11.3.1 Low Power Modes

11.3.2 MAC Interface and PHY Configuration for Low Power Modes

11.3.3 IEEE Power Down Mode

11.3.3.1 Energy Detect +TM

11.4 Far End Fault Indication (FEFI)

11.5 Virtual Cable Tester® Feature

11.6 Data Terminal Equipment (DTE) Detect

11.7 Auto MDI/MDIX Crossover

11.8 Copper Line Loopback

11.9 LED Interface

11.9.1 Parallel LED Interface

11.9.2 Using Two Color LEDs

11.9.3 Serial LED Interface (88E6097F Device Only)

11.9.4 Single and Dual LED Modes

11.9.4.1 Single LED Display Mode

11.9.4.2 Dual LED Display Mode

Section 12. Serial Management Interface (SMI)

12.1 MDC/MDIO Read and Write Operations

Section 13. Switch Register Description

13.1 Register Types

13.2 Multi-chip Addressing Mode

13.3 Single-chip Addressing Mode

13.4 Switch Port Registers

13.5 Switch Global Registers

13.6 Switch Global 2 Registers

13.6.1 PIRL Registers

Section 14. EEPROM Programming Format

Section 15. PHY Register Description

Section 16. Electrical Specifications

16.1 Absolute Maximum Ratings

16.2 Recommended Operating Conditions

16.3 Thermal Conditions for 88E6096/88E6097 devices 176-pin TQFP Package

16.4 Thermal Conditions for 88E6097F device 216-pin LQFP Package

16.5 Current Consumption

16.6 DC Electrical Characteristics

16.6.1 Digital Operating Conditions

16.6.2 SERDES Electrical Specifications

16.6.3 IEEE DC Transceiver Parameters

16.7 AC Electrical Specifications

16.7.1 Receiver AC Characteristics

16.7.2 Clock Timing

16.8 GMII Timing

16.8.1 GMII Transmit Timing

16.8.2 GMII Receive Timing

16.9 RGMII Timing

16.9.1 RGMII Timing for Different RGMII Modes

16.10 MII Timing

16.10.1 MII MAC Mode Clock Timing

16.10.2 MII Receive Timing - MAC Mode

16.10.3 MII Transmit Timing - MAC Mode

16.11 Serial Management Interface (SMI) Timing

16.11.1 SMI Clock Timing (CPU Set)

16.11.2 SMI Data Timing (CPU Set)

16.11.3 SMI Timing (PHY Set)

16.12 EEPROM Timing

16.12.1 2-Wire EEPROM Timing

16.12.2 4-Wire EEPROM Timing

16.13 SERDES (Serial Interface) Timing

16.14 IEEE AC Parameters (Ports 0-7)

Section 17. Package Mechanical Dimensions

Section 18. Ordering Information

18.1 Ordering Part Numbers and Package Markings

18.1.1 RoHS 6/6 Compliant Marking Examples

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc