CYGNAL 应 用 笔 记

AN005

通过 JTAG 接口对 FLASH 编程

相关器件

本应用笔记适用于下列器件

C8051F000 C8051F001 C8051F002 C8051F005 C8051F006 C8051F010 C8051F011 和

C8051F012

引言

本文介绍如何通过 JTAG 接口对 C8051 器件的 FLASH 存储器编程 在本应用笔记的最后提供

了示例源代码

通过 JTAG 接口对 FLASH 编程所需要的信息可以分为三大类

1

2

3

JTAG 接口信息

a

4 脚物理层接口 TCK TMS TDI 和

TDO

测试访问端口 TAP 状态机

TAP 复位 指令寄存器扫描和数据寄存

器扫描基本操作

b

c

JTAG 间接寄存器操作

a

b

c

读间接寄存器

写间接寄存器

查询 忙 标志位看读或写操作是否完

成

FLASH 编程操作

a

b

c

d

读一个 FLASH 字节

写一个 FLASH 字节

擦除一个 FLASH 页

擦除整个 FLASH

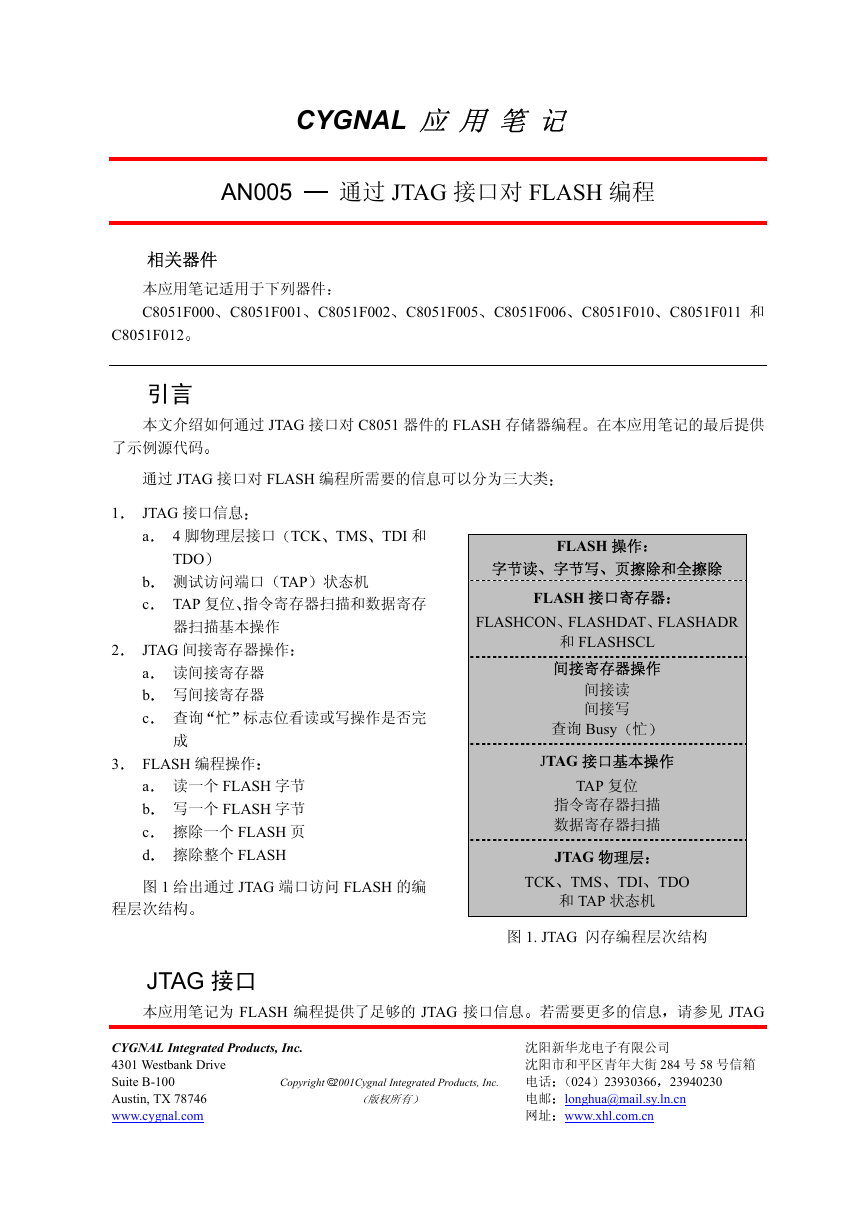

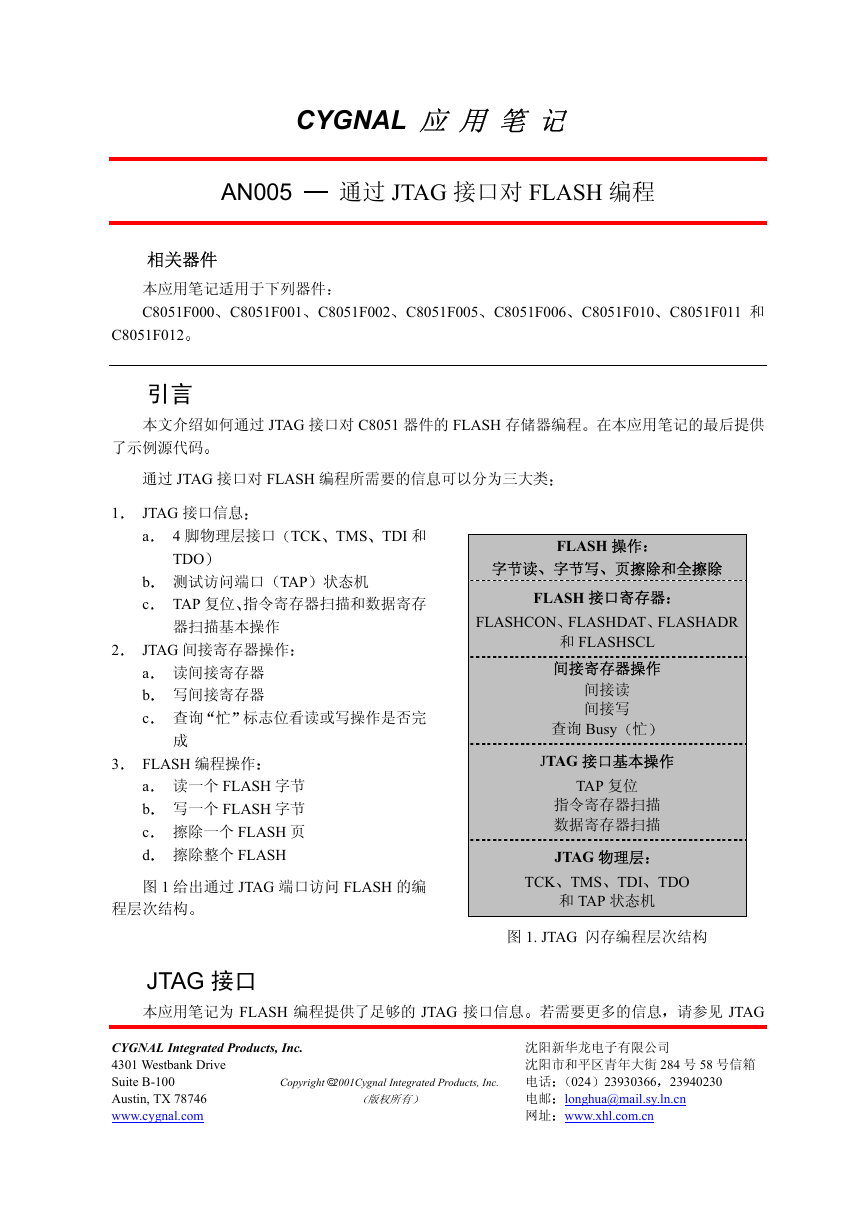

图 1 给出通过 JTAG 端口访问 FLASH 的编

程层次结构

FLASH 操作

字节读 字节写 页擦除和全擦除

FLASH 接口寄存器

FLASHCON FLASHDAT FLASHADR

和 FLASHSCL

间接寄存器操作

间接读

间接写

查询 Busy 忙

JTAG 接口基本操作

TAP 复位

指令寄存器扫描

数据寄存器扫描

JTAG 物理层

TCK TMS TDI TDO

和 TAP 状态机

图 1. JTAG 闪存编程层次结构

JTAG 接口

本应用笔记为 FLASH 编程提供了足够的 JTAG 接口信息 若需要更多的信息 请参见 JTAG

CYGNAL Integrated Products, Inc.

4301 Westbank Drive

Suite B-100

Austin, TX 78746

www.cygnal.com

Copyright ©2001Cygnal Integrated Products, Inc. 电话 024

23930366

23940230

沈阳新华龙电子有限公司

沈阳市和平区青年大街 284 号 58 号信箱

版权所有

电邮 longhua@mail.sy.ln.cn

网址 www.xhl.com.cn

�

AN005

通过 JTAG 接口对 FLASH 编程

IEEE 1149.1-1990 该标准可以从 电气与电子工程师协会 得到 更多的信息见 http

C8051 系列器件的 JTAG 接口完全符合 IEEE 1149.1 规范 已经熟悉 JTAG 接

标准

//standards.ieee.org

口的读者可跳到第 7 页的 C8051 器件指令寄存器 一节

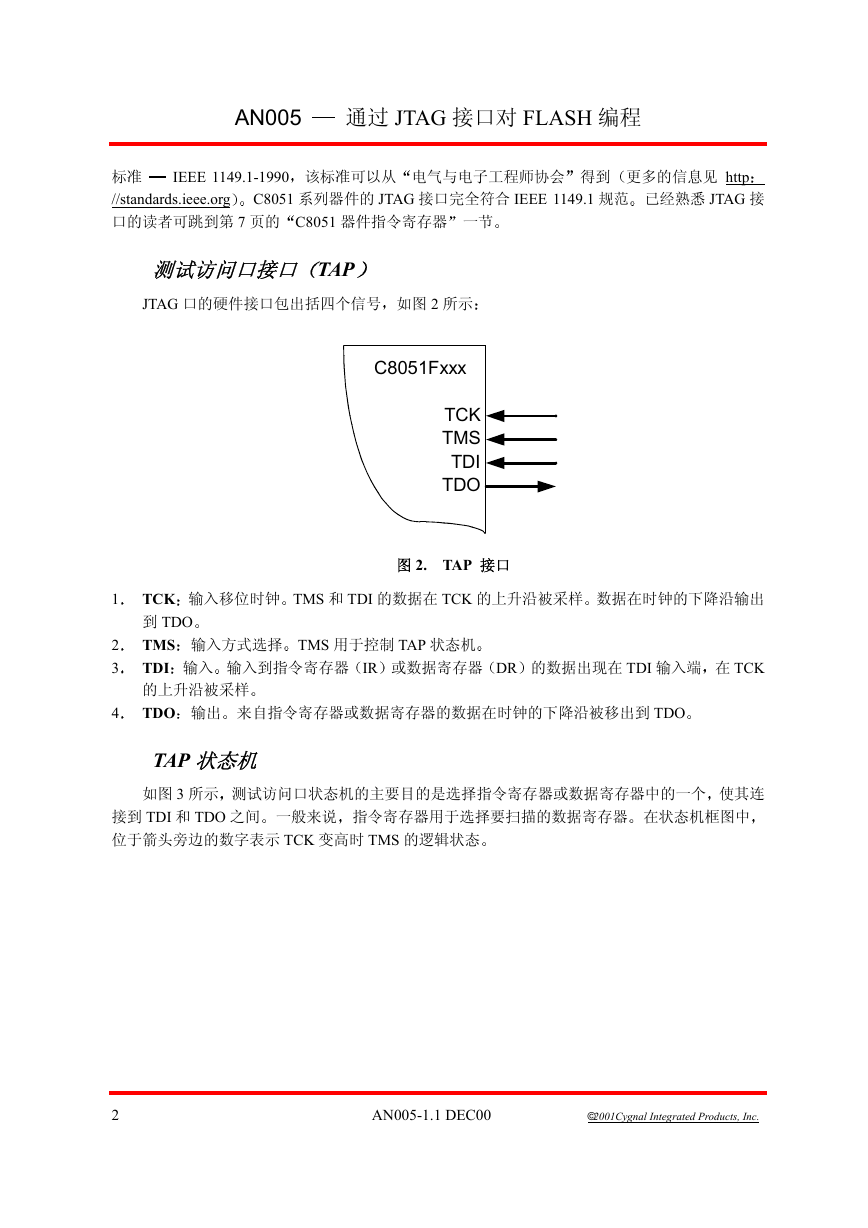

测试访问口接口 TAP

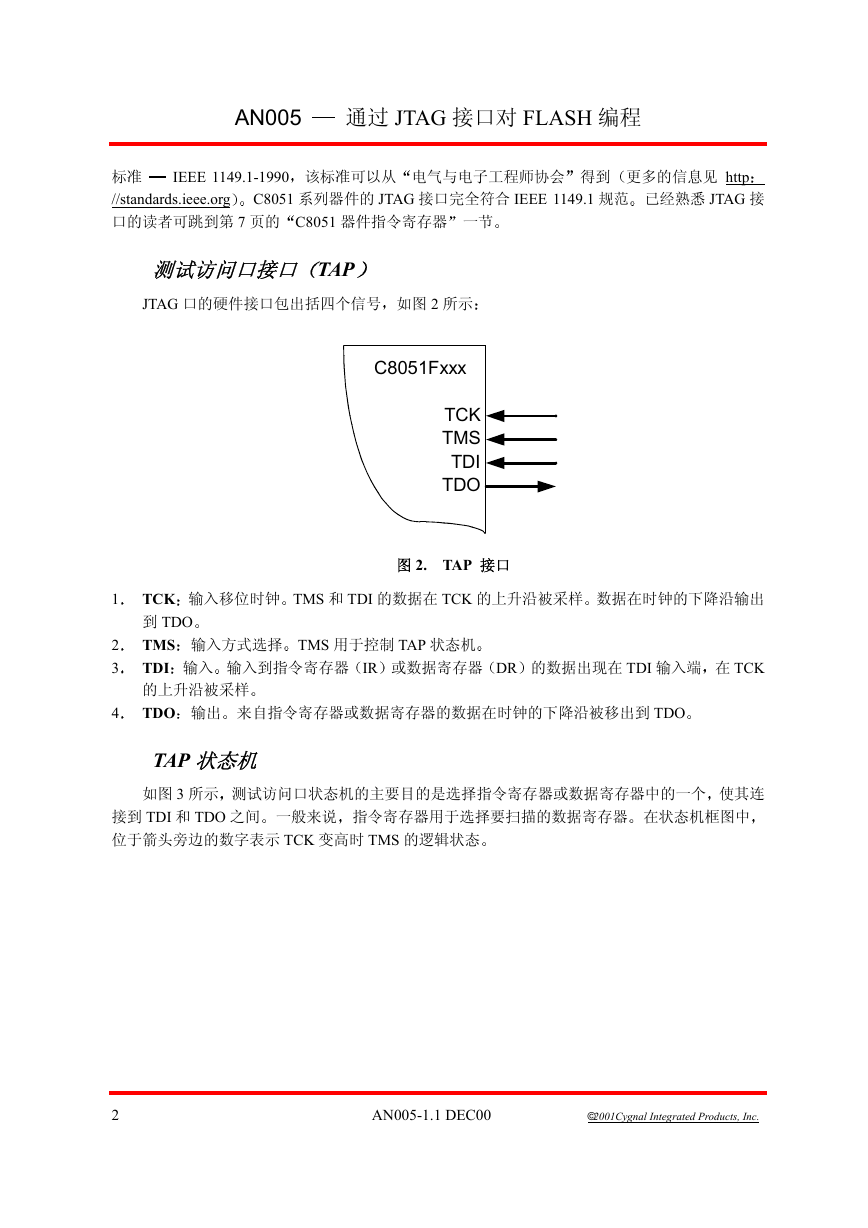

JTAG 口的硬件接口包出括四个信号 如图 2 所示

C8051Fxxx

TCK

TMS

TDI

TDO

图 2. TAP 接口

1

2

3

4

TCK 输入移位时钟 TMS 和 TDI 的数据在 TCK 的上升沿被采样 数据在时钟的下降沿输出

到 TDO

TMS 输入方式选择 TMS 用于控制 TAP 状态机

TDI 输入 输入到指令寄存器 IR 或数据寄存器 DR 的数据出现在 TDI 输入端 在 TCK

的上升沿被采样

TDO 输出 来自指令寄存器或数据寄存器的数据在时钟的下降沿被移出到 TDO

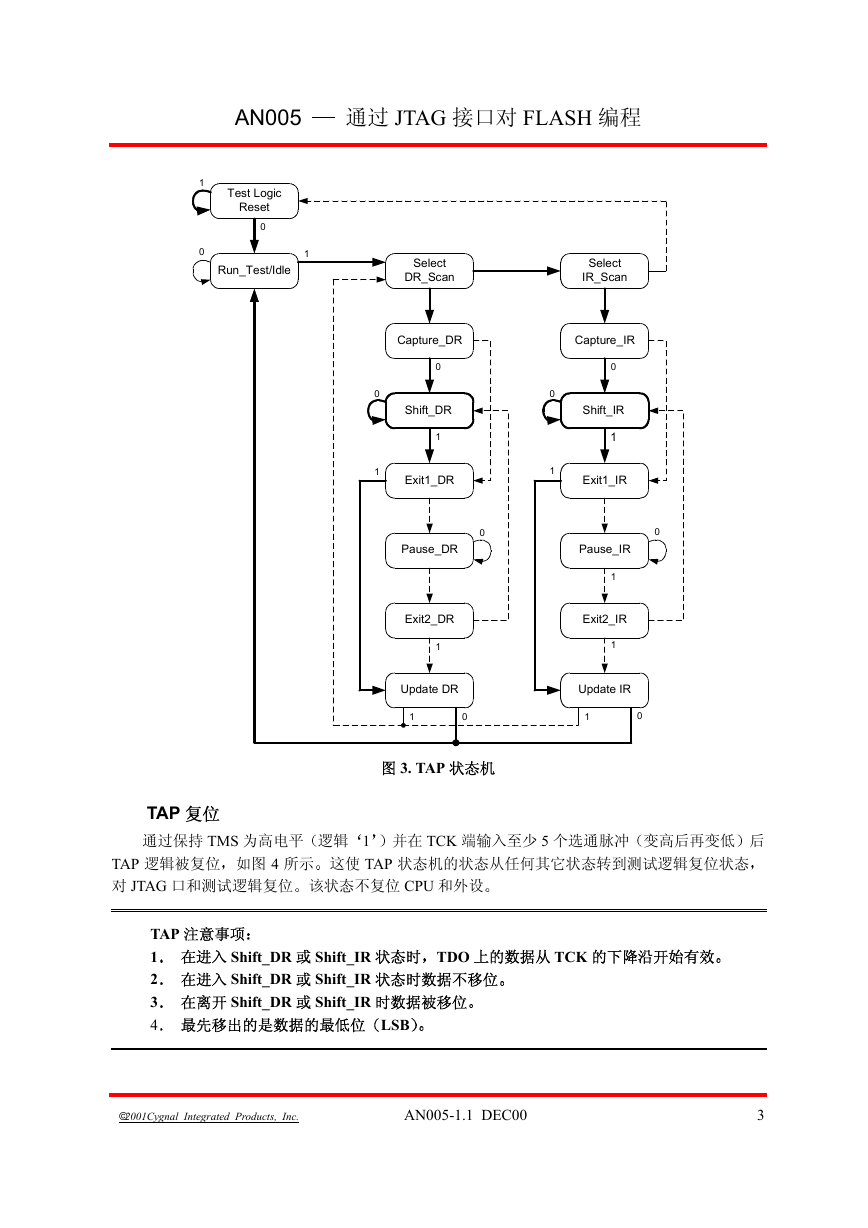

TAP 状态机

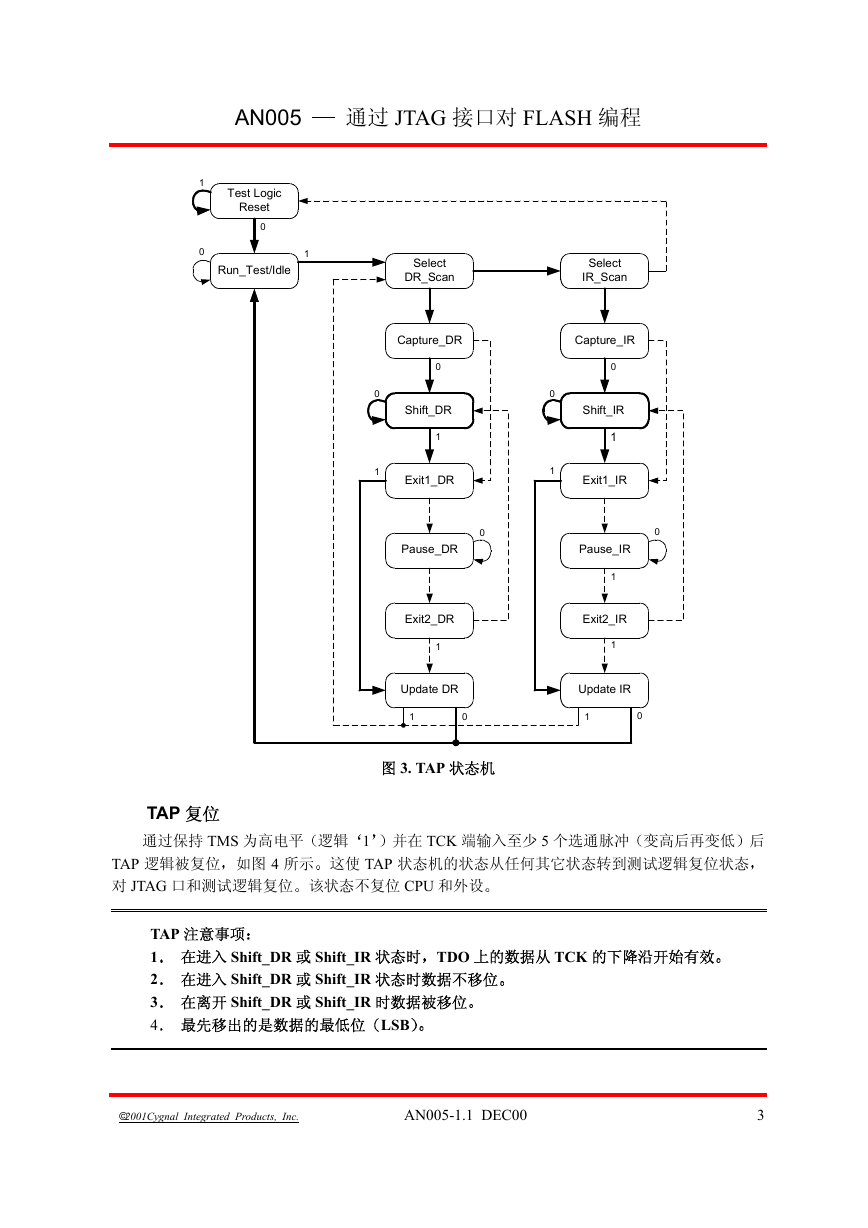

如图 3 所示 测试访问口状态机的主要目的是选择指令寄存器或数据寄存器中的一个 使其连

接到 TDI 和 TDO 之间 一般来说 指令寄存器用于选择要扫描的数据寄存器 在状态机框图中

位于箭头旁边的数字表示 TCK 变高时 TMS 的逻辑状态

2

AN005-1.1 DEC00 ©2001Cygnal Integrated Products, Inc.

�

AN005

通过 JTAG 接口对 FLASH 编程

1

0

Test Logic

Reset

0

1

Run_Test/Idle

Select

DR_Scan

Capture_DR

0

Shift_DR

1

Exit1_DR

0

1

0

Pause_DR

Exit2_DR

1

Update DR

1

0

图 3. TAP 状态机

Select

IR_Scan

Capture_IR

0

Shift_IR

1

Exit1_IR

0

1

0

Pause_IR

1

Exit2_IR

1

Update IR

1

0

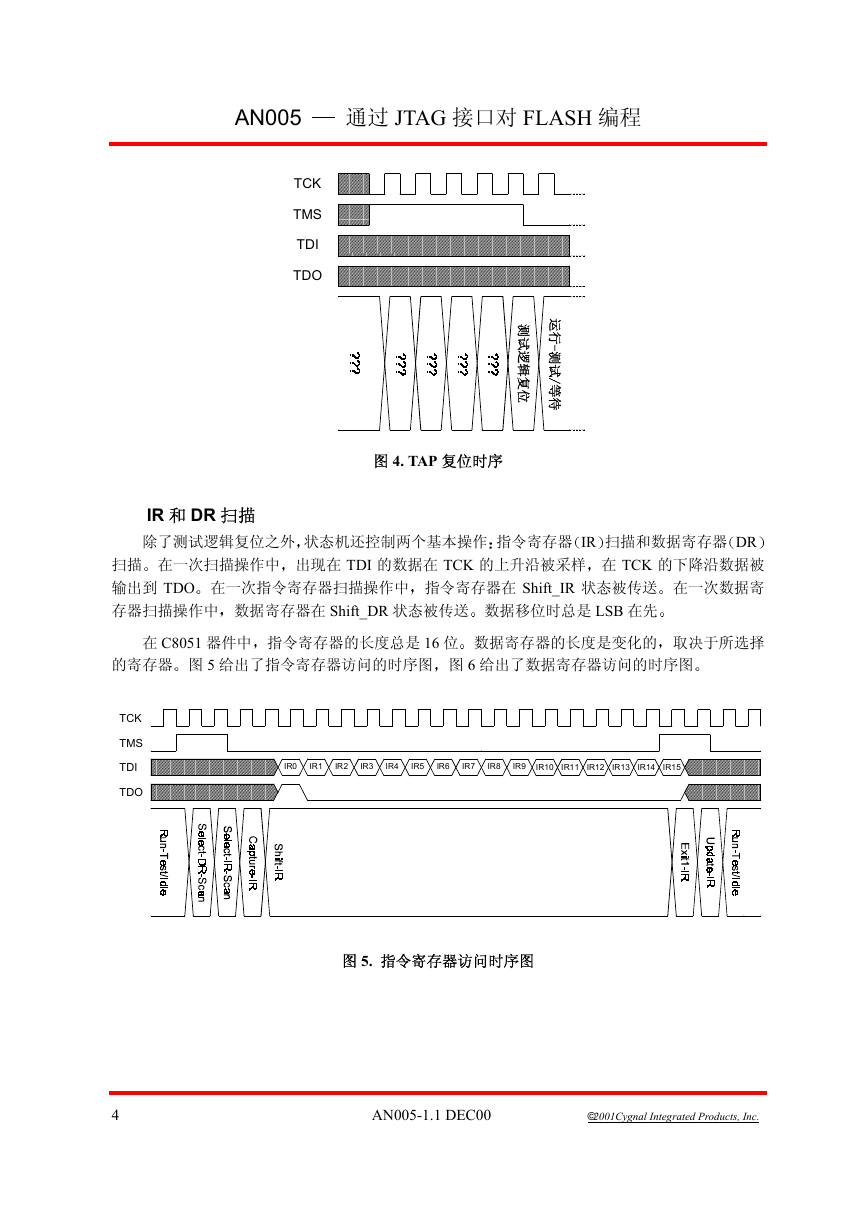

TAP 复位

通过保持 TMS 为高电平 逻辑 1 并在 TCK 端输入至少 5 个选通脉冲 变高后再变低 后

TAP 逻辑被复位 如图 4 所示 这使 TAP 状态机的状态从任何其它状态转到测试逻辑复位状态

对 JTAG 口和测试逻辑复位 该状态不复位 CPU 和外设

TAP 注意事项

1

2

3

4

在进入 Shift_DR 或 Shift_IR 状态时 TDO 上的数据从 TCK 的下降沿开始有效

在进入 Shift_DR 或 Shift_IR 状态时数据不移位

在离开 Shift_DR 或 Shift_IR 时数据被移位

最先移出的是数据的最低位 LSB

©2001Cygnal Integrated Products, Inc. AN005-1.1 DEC00 3

�

AN005

通过 JTAG 接口对 FLASH 编程

TCK

TMS

TDI

TDO

������������

������������

������������

������������

������������������������������������������������������������������������������������

������������������������������������������������������������������������������������

������������������������������������������������������������������������������������

������������������������������������������������������������������������������������

������������������������������������������������������������������������������������

测

试

逻

辑

复

位

运

行

-

测

试

/

等

待

图 4. TAP 复位时序

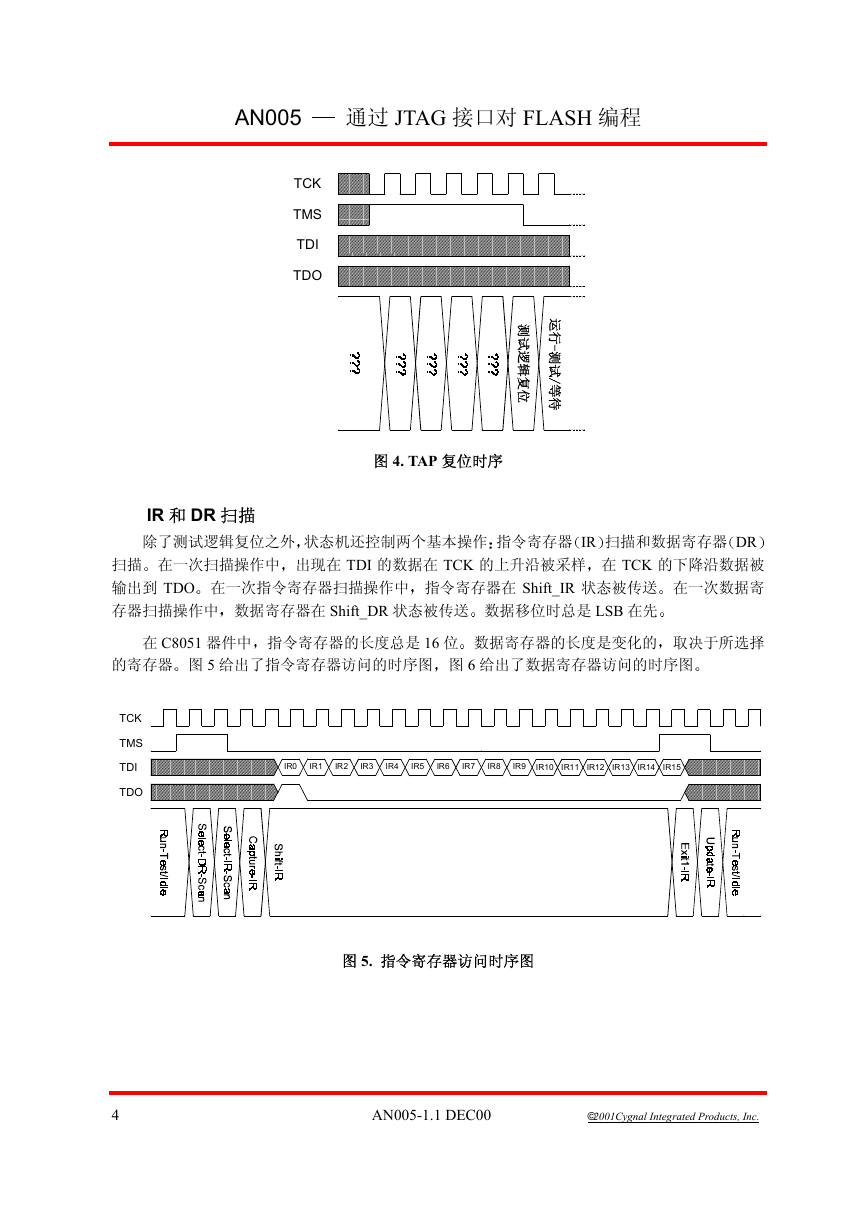

IR 和 DR 扫描

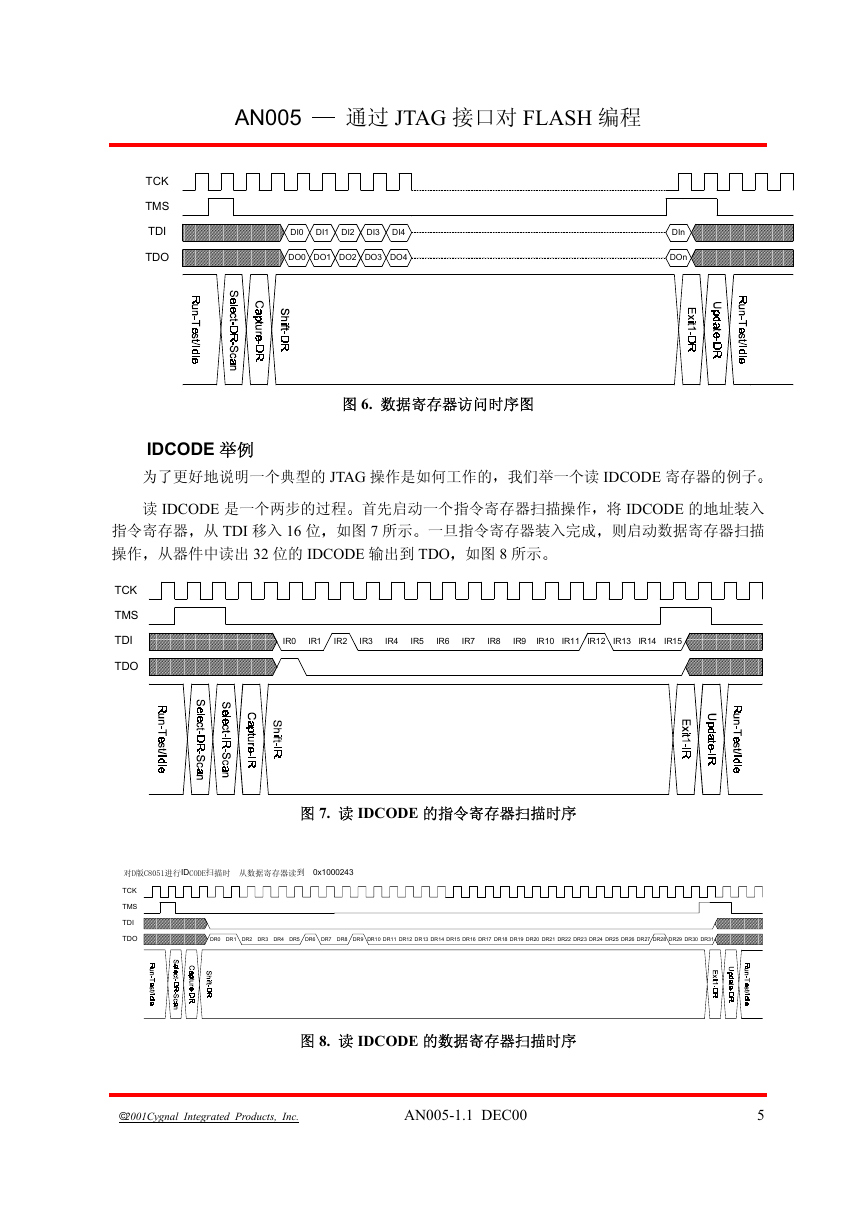

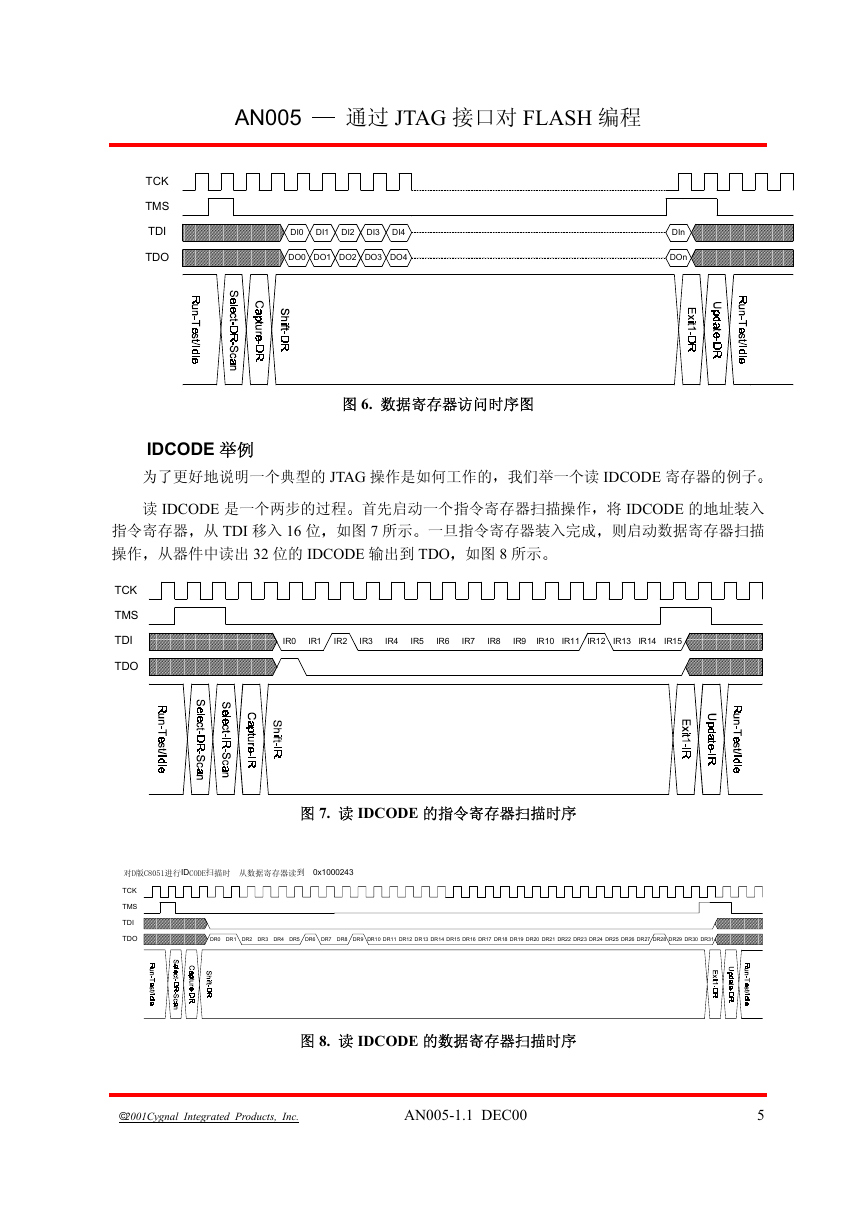

除了测试逻辑复位之外 状态机还控制两个基本操作 指令寄存器 IR 扫描和数据寄存器 DR

扫描 在一次扫描操作中 出现在 TDI 的数据在 TCK 的上升沿被采样 在 TCK 的下降沿数据被

输出到 TDO 在一次指令寄存器扫描操作中 指令寄存器在 Shift_IR 状态被传送 在一次数据寄

存器扫描操作中 数据寄存器在 Shift_DR 状态被传送 数据移位时总是 LSB 在先

在 C8051 器件中 指令寄存器的长度总是 16 位 数据寄存器的长度是变化的 取决于所选择

的寄存器 图 5 给出了指令寄存器访问的时序图 图 6 给出了数据寄存器访问的时序图

TCK

TMS

TDI

TDO

4

�����������������������������������������������

�����������������������������������������������

�����������������������������������������������

�����������������������������������������������

IR0

IR1

IR2

IR3

IR4

IR5

IR6

IR7

IR8

IR9

IR10 IR11 IR12 IR13 IR14 IR15 ����������������������������

����������������������������

����������������������������

����������������������������

图 5. 指令寄存器访问时序图

AN005-1.1 DEC00 ©2001Cygnal Integrated Products, Inc.

�

AN005

通过 JTAG 接口对 FLASH 编程

TCK

TMS

TDI

TDO

�������������������������������������

�������������������������������������

�������������������������������������

������������������������������������� DO0 DO1 DO2 DO3 DO4

DI2 DI3 DI4

DI0

DI1

DIn ��������������������������������������

��������������������������������������

��������������������������������������

��������������������������������������

DOn

图 6. 数据寄存器访问时序图

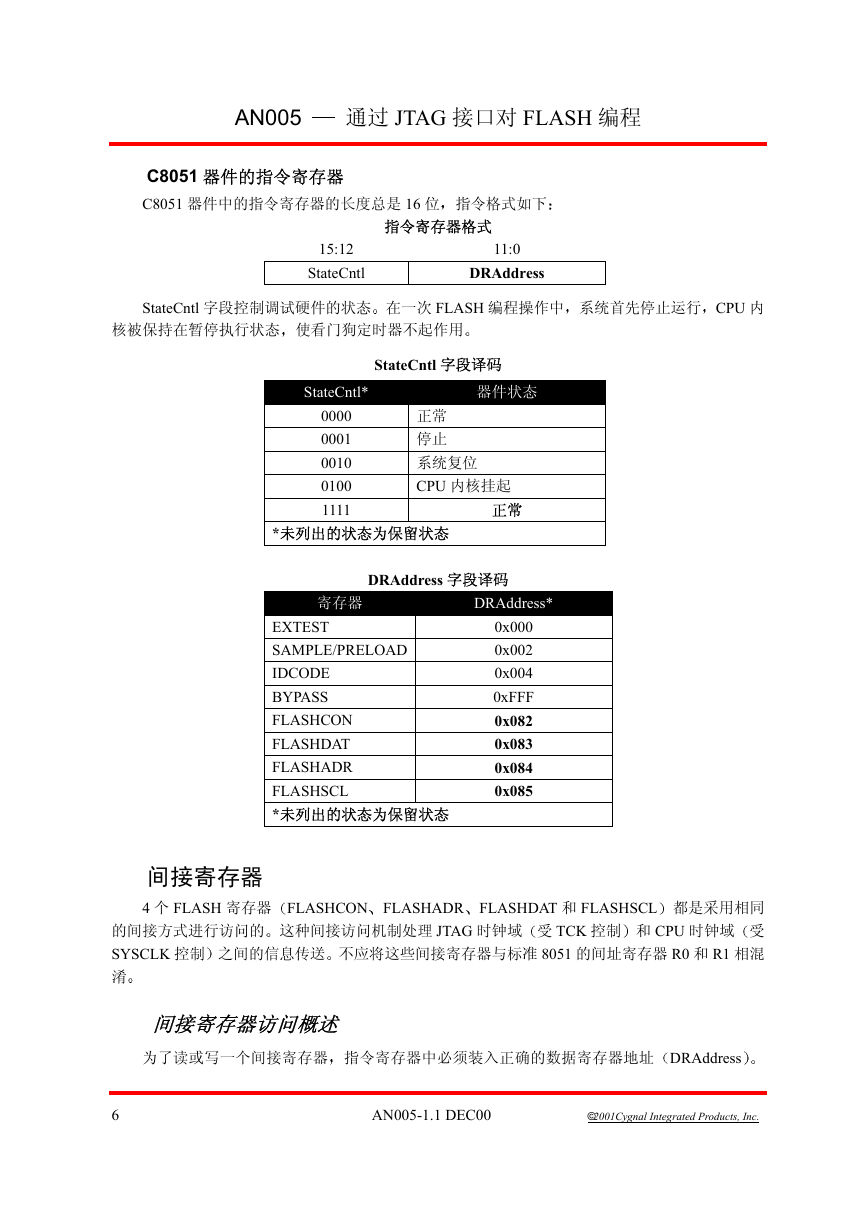

IDCODE 举例

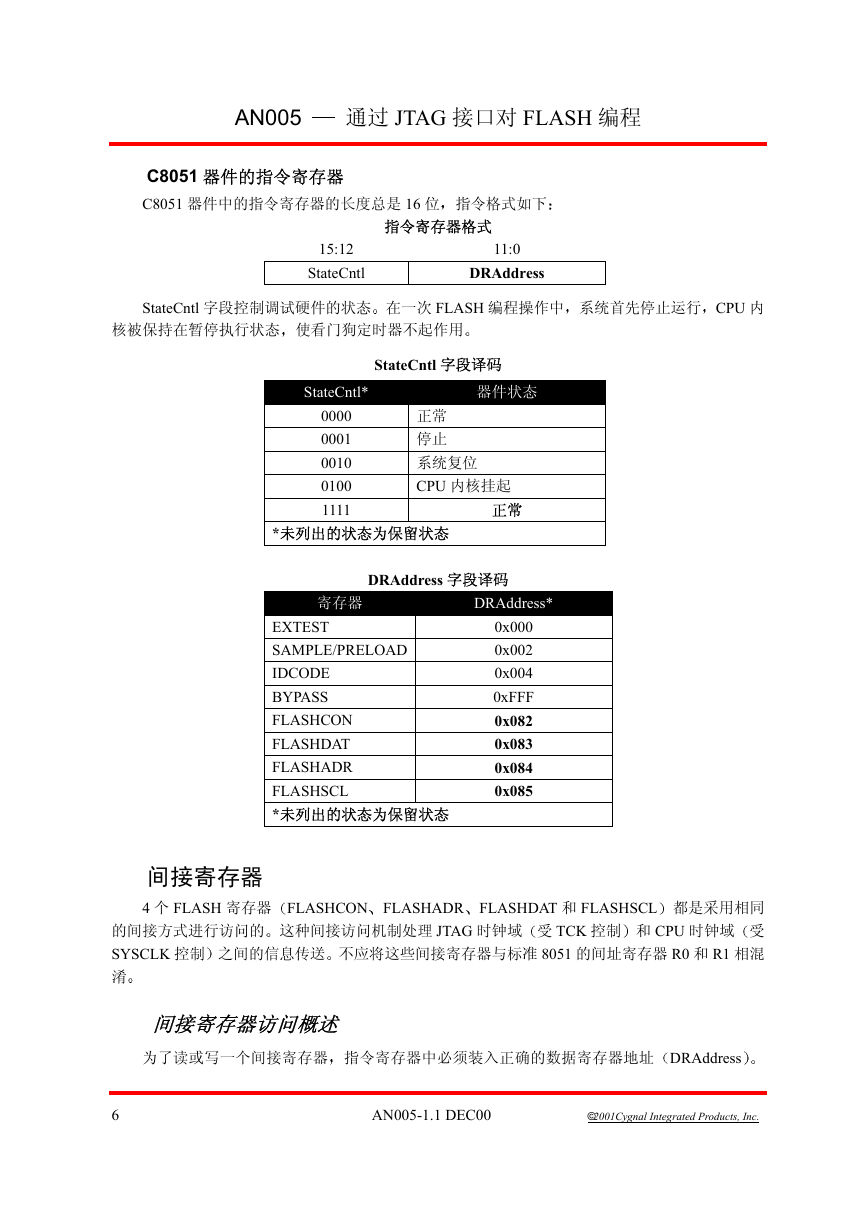

为了更好地说明一个典型的 JTAG 操作是如何工作的 我们举一个读 IDCODE 寄存器的例子

读 IDCODE 是一个两步的过程 首先启动一个指令寄存器扫描操作 将 IDCODE 的地址装入

指令寄存器 从 TDI 移入 16 位 如图 7 所示 一旦指令寄存器装入完成 则启动数据寄存器扫描

操作 从器件中读出 32 位的 IDCODE 输出到 TDO 如图 8 所示

TCK

TMS

TDI

TDO

����������������������������������������������

����������������������������������������������

����������������������������������������������

����������������������������������������������

IR0

IR1

IR2

IR3

IR4

IR5

IR6

IR7

IR8

IR9

IR10 IR11 IR12 IR13 IR14 IR15

�����������������������������

�����������������������������

�����������������������������

�����������������������������

图 7. 读 IDCODE 的指令寄存器扫描时序

对D版C8051进行IDCODE扫描时从数据寄存器读到0x1000243

TCK

TMS

TDI

TDO

������������������������

������������������������

������������������������

������������������������

DR0 DR1 DR2 DR3 DR4 DR5 DR6 DR7 DR8 DR9 DR10 DR11 DR12 DR13 DR14

DR15

DR16 DR17 DR18 DR19 DR20 DR21 DR22 DR23 DR24 DR25 DR26 DR27 DR28 DR29 DR30 DR31

图 8. 读 IDCODE 的数据寄存器扫描时序

������������������

������������������

������������������

������������������

©2001Cygnal Integrated Products, Inc. AN005-1.1 DEC00 5

�

AN005

通过 JTAG 接口对 FLASH 编程

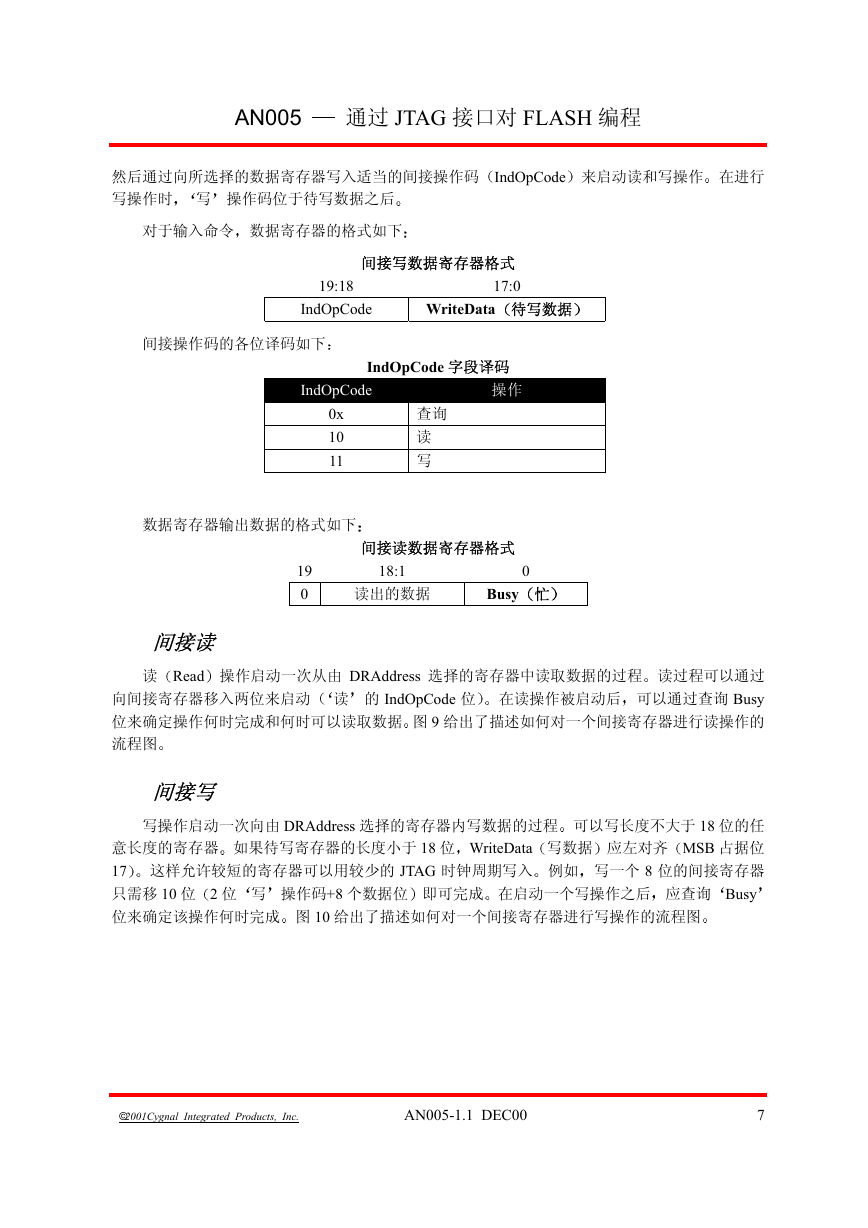

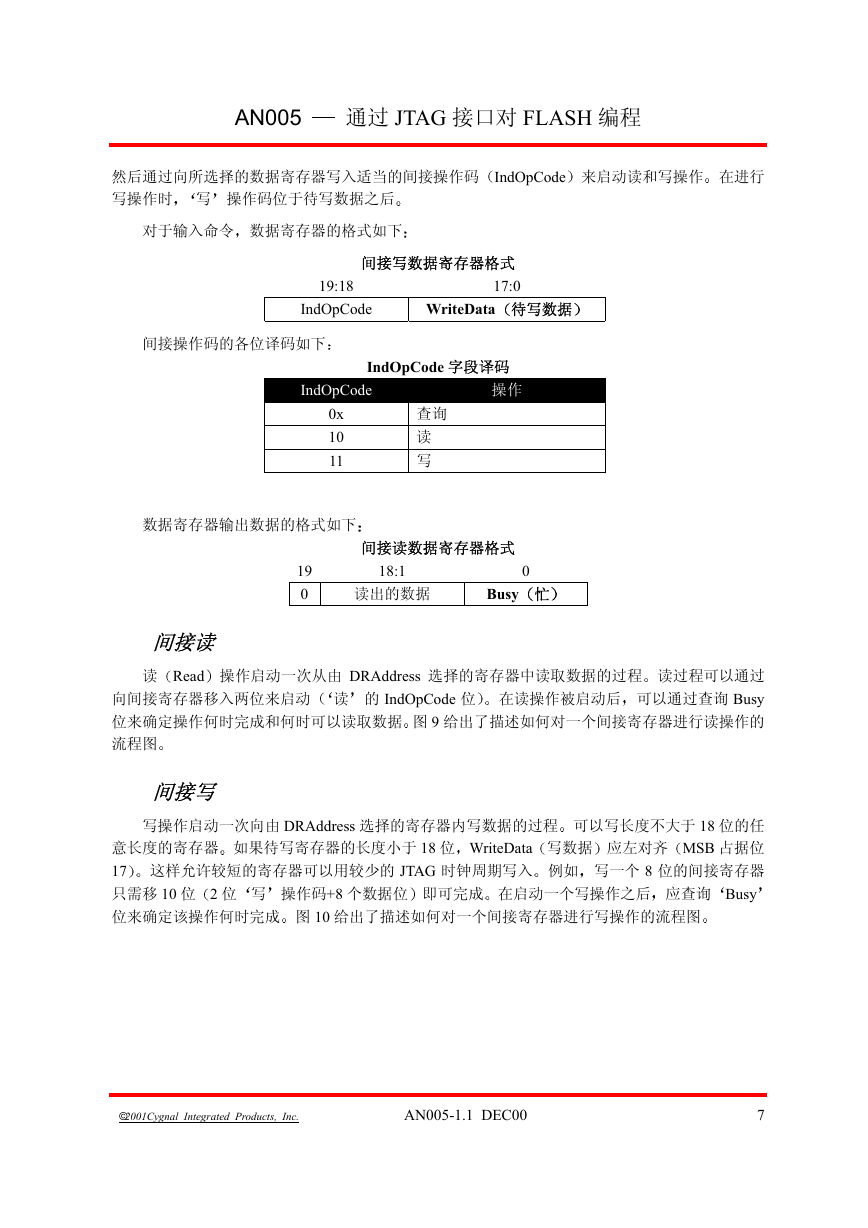

C8051 器件的指令寄存器

C8051 器件中的指令寄存器的长度总是 16 位 指令格式如下

指令寄存器格式

15:12

StateCntl

11:0

DRAddress

StateCntl 字段控制调试硬件的状态 在一次 FLASH 编程操作中 系统首先停止运行 CPU 内

核被保持在暂停执行状态 使看门狗定时器不起作用

StateCntl 字段译码

StateCntl*

器件状态

0000

0001

0010

0100

1111

正常

停止

系统复位

CPU 内核挂起

正常

*未列出的状态为保留状态

DRAddress 字段译码

寄存器

DRAddress*

EXTEST

SAMPLE/PRELOAD

IDCODE

BYPASS

FLASHCON

FLASHDAT

FLASHADR

FLASHSCL

*未列出的状态为保留状态

0x000

0x002

0x004

0xFFF

0x082

0x083

0x084

0x085

间接寄存器

4 个 FLASH 寄存器 FLASHCON FLASHADR FLASHDAT 和 FLASHSCL 都是采用相同

的间接方式进行访问的 这种间接访问机制处理 JTAG 时钟域 受 TCK 控制 和 CPU 时钟域 受

SYSCLK 控制 之间的信息传送 不应将这些间接寄存器与标准 8051 的间址寄存器 R0 和 R1 相混

淆

间接寄存器访问概述

为了读或写一个间接寄存器 指令寄存器中必须装入正确的数据寄存器地址 DRAddress

6

AN005-1.1 DEC00 ©2001Cygnal Integrated Products, Inc.

�

AN005

通过 JTAG 接口对 FLASH 编程

然后通过向所选择的数据寄存器写入适当的间接操作码 IndOpCode 来启动读和写操作 在进行

写操作时 写 操作码位于待写数据之后

对于输入命令 数据寄存器的格式如下

间接写数据寄存器格式

17:0

19:18

IndOpCode

WriteData 待写数据

间接操作码的各位译码如下

IndOpCode 字段译码

IndOpCode

操作

0x

10

11

查询

读

写

数据寄存器输出数据的格式如下

间接读数据寄存器格式

18:1

0

读出的数据

Busy 忙

19

0

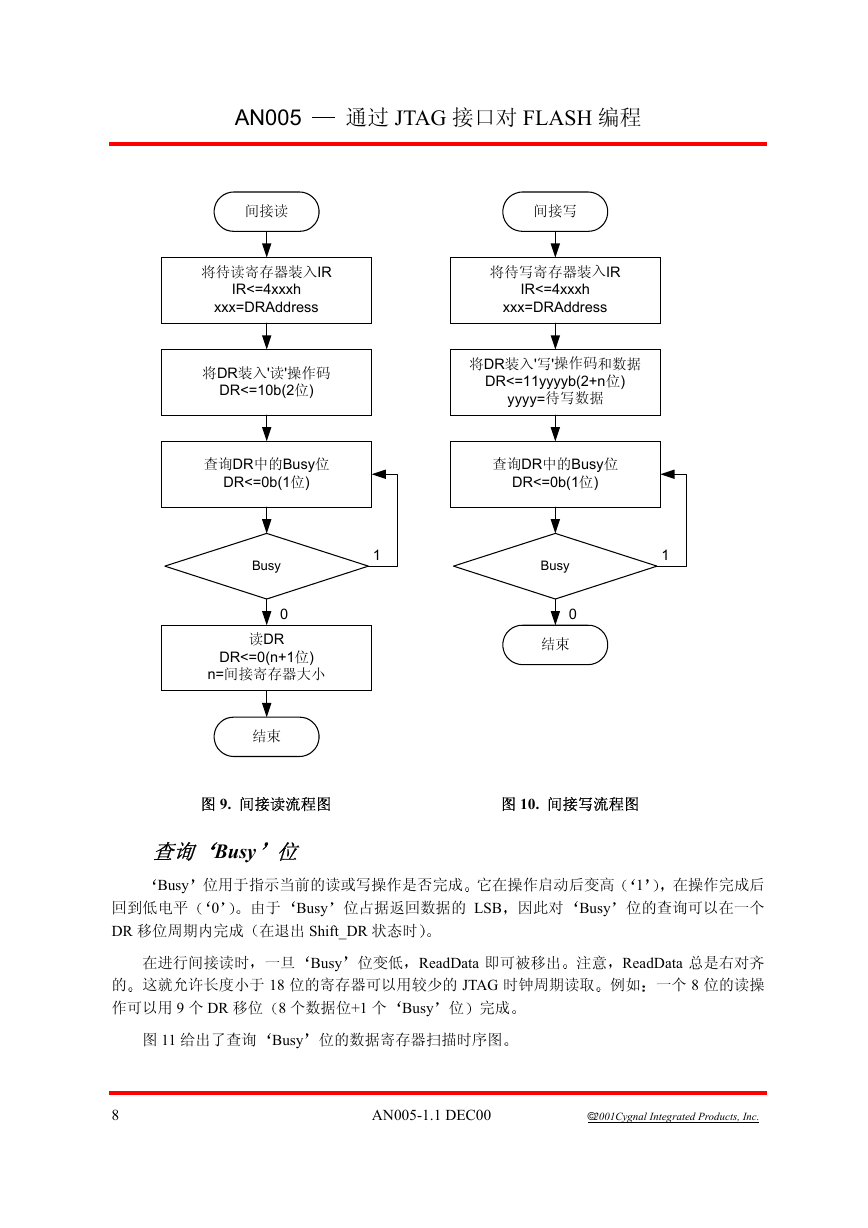

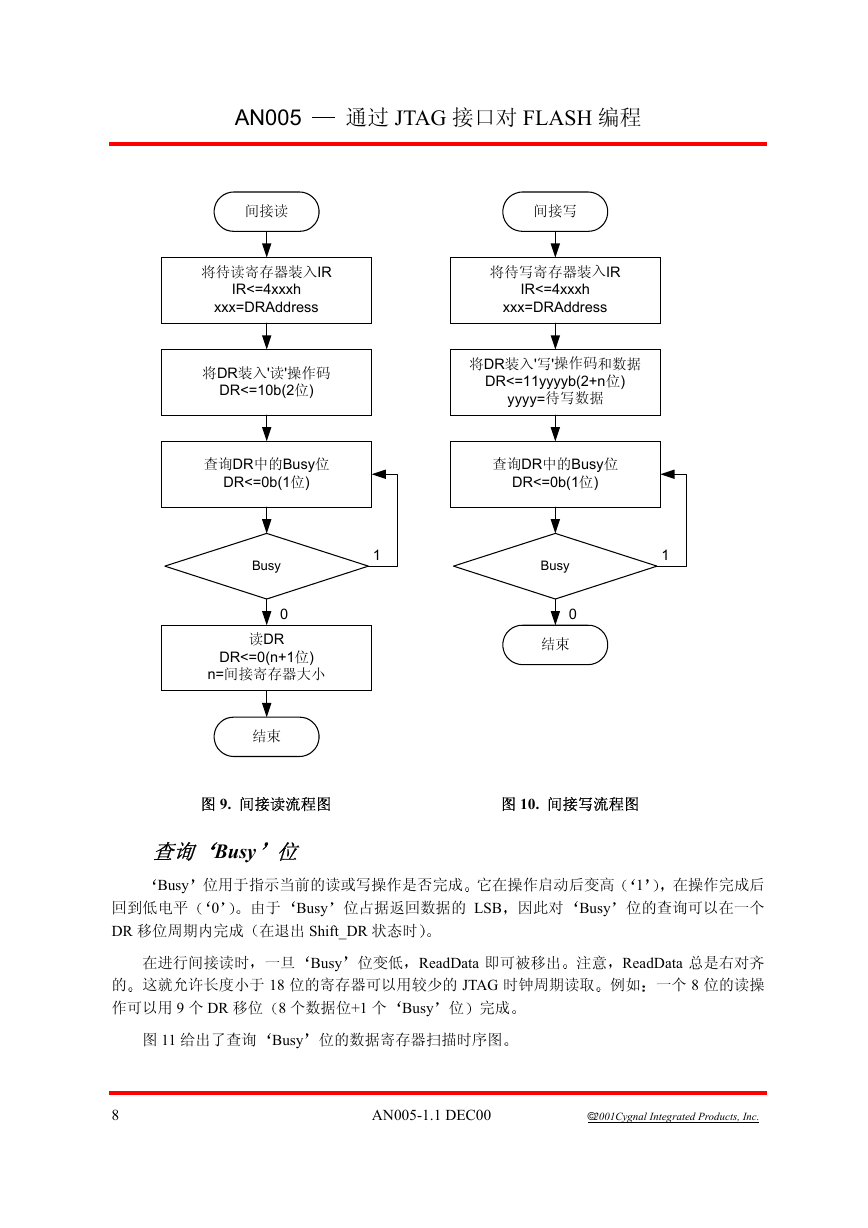

间接读

读 Read 操作启动一次从由 DRAddress 选择的寄存器中读取数据的过程 读过程可以通过

向间接寄存器移入两位来启动 读 的 IndOpCode 位 在读操作被启动后 可以通过查询 Busy

位来确定操作何时完成和何时可以读取数据 图 9 给出了描述如何对一个间接寄存器进行读操作的

流程图

间接写

写操作启动一次向由 DRAddress 选择的寄存器内写数据的过程 可以写长度不大于 18 位的任

意长度的寄存器 如果待写寄存器的长度小于 18 位 WriteData 写数据 应左对齐 MSB 占据位

17 这样允许较短的寄存器可以用较少的 JTAG 时钟周期写入 例如 写一个 8 位的间接寄存器

只需移 10 位 2 位 写 操作码+8 个数据位 即可完成 在启动一个写操作之后 应查询 Busy

位来确定该操作何时完成 图 10 给出了描述如何对一个间接寄存器进行写操作的流程图

©2001Cygnal Integrated Products, Inc. AN005-1.1 DEC00 7

�

AN005

通过 JTAG 接口对 FLASH 编程

间接读

间接写

将待读寄存器装入IR

IR<=4xxxh

xxx=DRAddress

将待写寄存器装入IR

IR<=4xxxh

xxx=DRAddress

将DR装入'读'操作码

DR<=10b(2位)

将DR装入'写'操作码和数据

DR<=11yyyyb(2+n位)

yyyy=待写数据

查询DR中的Busy位

DR<=0b(1位)

查询DR中的Busy位

DR<=0b(1位)

Busy

1

0

读DR

DR<=0(n+1位)

n=间接寄存器大小

1

Busy

0

结束

结束

图 9. 间接读流程图 图 10. 间接写流程图

查询 Busy 位

Busy 位用于指示当前的读或写操作是否完成 它在操作启动后变高 1 在操作完成后

由于 Busy 位占据返回数据的 LSB 因此对 Busy 位的查询可以在一个

回到低电平 0

DR 移位周期内完成 在退出 Shift_DR 状态时

在进行间接读时 一旦 Busy 位变低 ReadData 即可被移出 注意 ReadData 总是右对齐

的 这就允许长度小于 18 位的寄存器可以用较少的 JTAG 时钟周期读取 例如 一个 8 位的读操

作可以用 9 个 DR 移位 8 个数据位+1 个 Busy 位 完成

图 11 给出了查询 Busy 位的数据寄存器扫描时序图

8

AN005-1.1 DEC00 ©2001Cygnal Integrated Products, Inc.

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc