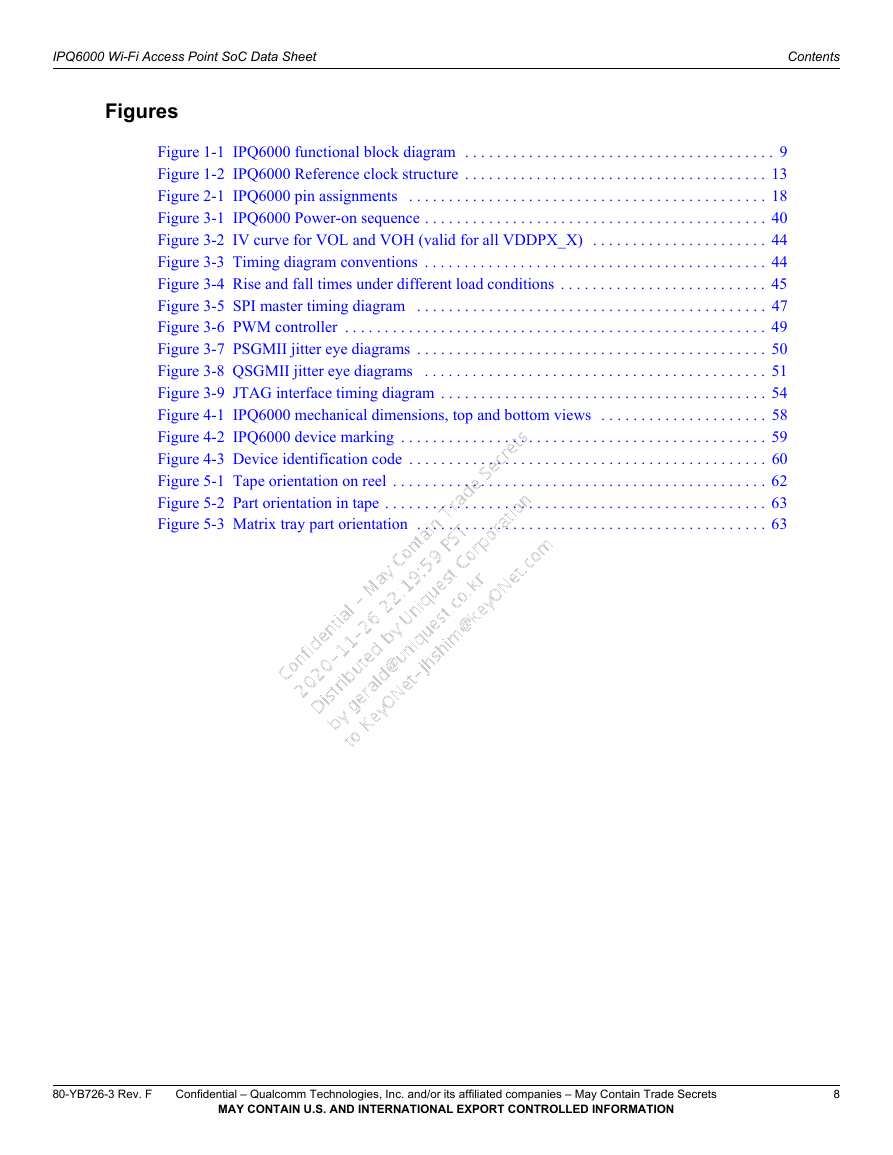

1 Introduction

1.1 Functional block diagram

1.2 Interfaces and power management

1.3 Features

1.3.1 Wi-Fi subsystem

1.3.2 Networking subsystem

1.3.3 CPU subsystem

1.3.4 Reference clock structure

1.3.5 Peripherals/interfaces

1.3.6 Power management

1.3.7 Platform extension options

1.4 Terms and abbreviations

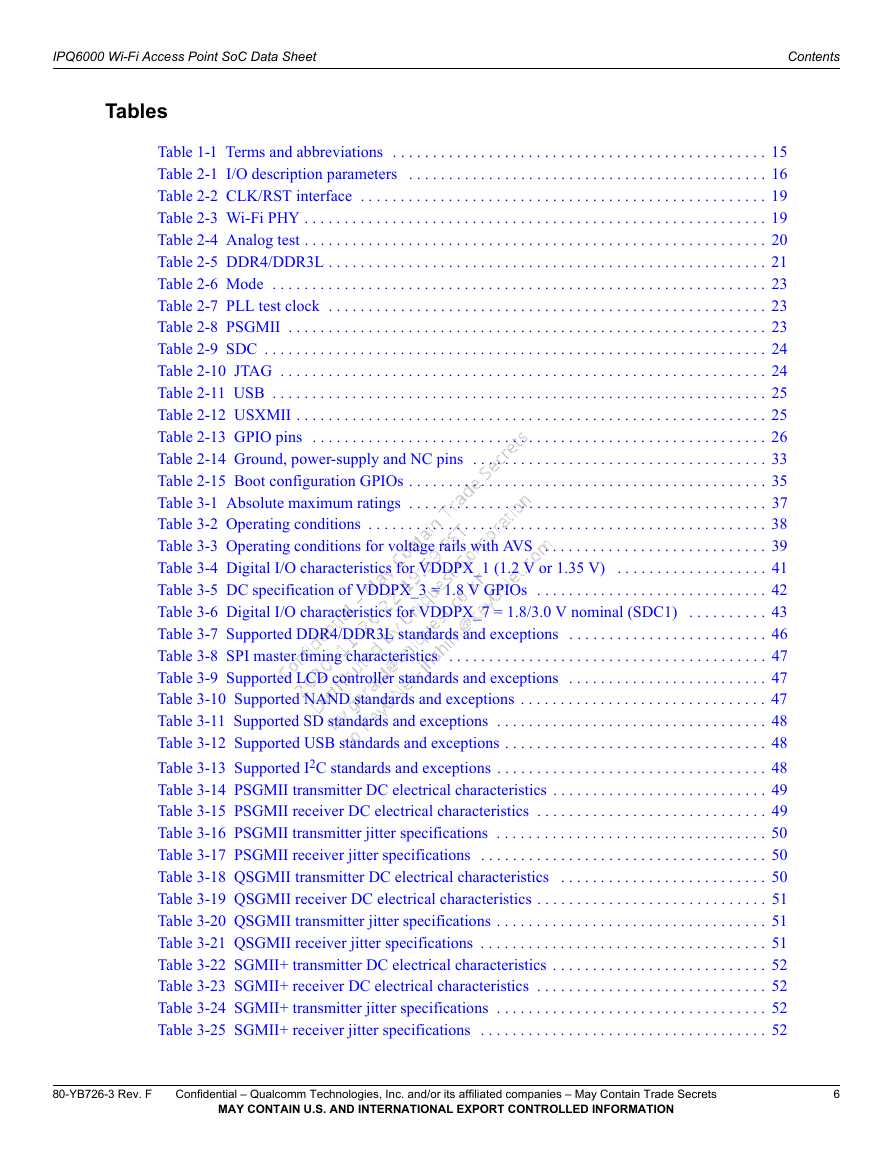

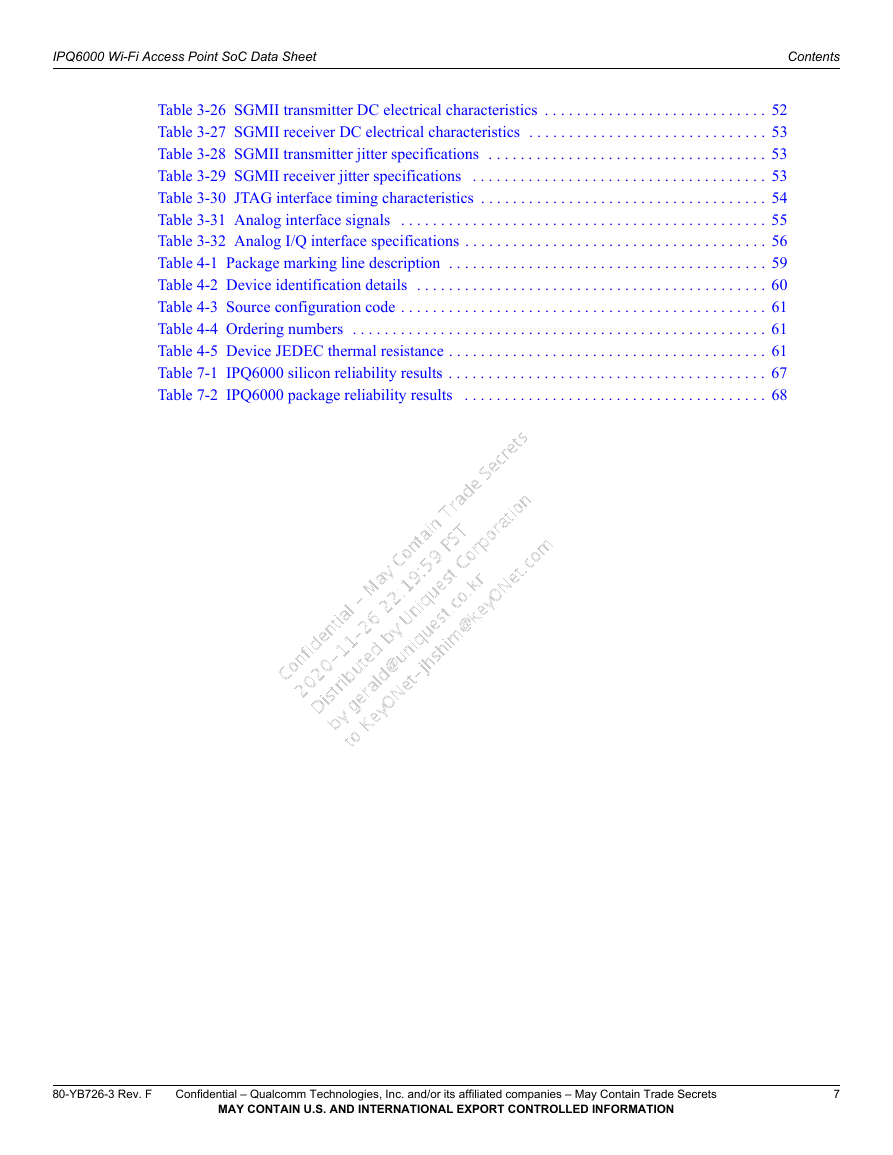

2 Pin definitions

2.1 I/O parameter definitions

2.2 Pin map

2.3 Pin descriptions

2.3.1 CLK/RST and PMIC interface

2.3.2 Wi-Fi PHY

2.3.3 Analog test

2.3.4 DDR4/DDR3L

2.3.5 Mode

2.3.6 PLL test clock

2.3.7 PSGMII

2.3.8 SDC

2.3.9 JTAG

2.3.10 USB

2.3.11 USXGMII

2.3.12 GPIO

2.3.13 Ground, power-supply and NC

2.3.14 Boot configuration GPIOs

3 Electrical specifications

3.1 Absolute maximum ratings

3.2 Operating conditions

3.3 Power sequencing

3.4 Digital-logic characteristics

3.5 Timing characteristics

3.5.1 Timing diagram conventions

3.5.2 Rise and fall time specifications

3.6 Memory support

3.6.1 DDR4/DDR3L

3.6.2 eMMC on SDC1

3.6.3 NOR memory on SPI

3.7 Connectivity

3.7.1 Serial peripheral interface

3.7.2 Parallel NAND and display interface

3.7.3 SD interfaces

3.7.4 USB interfaces

3.7.5 I2C interface

3.7.6 PWM interfaces

3.8 UniPHY interfaces

3.8.1 PSGMII interface

3.8.2 QSGMII interface

3.8.3 SGMII+ interface

3.8.4 SGMII interface

3.9 Internal functions

3.9.1 Clocks

3.9.2 Modes and resets

3.9.3 JTAG

3.10 Analog IQ interfaces

4 Mechanical information

4.1 Device physical dimensions

4.2 Part marking

4.3 Device ordering information

4.4 Device moisture-sensitivity level

4.5 Thermal characteristics

5 Carrier, storage, and handling information

5.1 Carrier

5.1.1 Tape and reel information

5.1.2 Matrix tray information

5.2 Storage

5.2.1 Bag storage conditions

5.2.2 Out of bag duration

5.3 Handling

5.3.1 Baking

5.3.2 Electrostatic discharge

5.4 Barcode label and packing for shipment

6 PCB mounting guidelines

6.1 RoHS compliance

6.2 SMT assembly guidelines

6.3 High-temperature warpage

7 Part reliability

7.1 Reliability qualifications summary

7.2 Qualification sample description

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc