8.10 FSK 调制与解调 VHDL 程序及仿真

1. FSK 调制 VHDL 程序

--文件名:PL_FSK

--功能:基于 VHDL 硬件描述语言,对基带信号进行 FSK 调制

--最后修改日期:2004.3.16

library ieee;

use ieee.std_logic_arith.all;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity PL_FSK is

port(clk

:in std_logic;

--系统时钟

start

:in std_logic;

--开始调制信号

x

y

:in std_logic;

:out std_logic);

--基带信号

--调制信号

end PL_FSK;

architecture behav of PL_FSK is

signal q1:integer range 0 to 11;

--载波信号 f1 的分频计数器

signal q2:integer range 0 to 3;

--载波信号 f2 的分频计数器

signal f1,f2:std_logic;

--载波信号 f1,f2

begin

process(clk)

begin

if clk'event and clk='1' then

if start='0' then q1<=0;

--此进程通过对系统时钟 clk 的分频,得到载波 f1

elsif q1<=5 then f1<='1';q1<=q1+1; --改变 q1 后面的数字可以改变,载波 f1 的占空比

elsif q1=11 then f1<='0';q1<=0;

--改变 q1 后面的数字可以改变,载波 f1 的频率

else

f1<='0';q1<=q1+1;

end if;

end if;

10

�

end process;

process(clk)

begin

if clk'event and clk='1' then

if start='0' then q2<=0;

--此进程通过对系统时钟 clk 的分频,得到载波 f2

elsif q2<=0 then f2<='1';q2<=q2+1; --改变 q2 后面的数字可以改变,载波 f2 的占空比

elsif q2=1 then f2<='0';q2<=0;

--改变 q2 后面的数字可以改变,载波 f2 的频率

else f2<='0';q2<=q2+1;

end if;

end if;

end process;

process(clk,x)

begin

if clk'event and clk='1' then

--此进程完成对基带信号的 FSK 调制

if x='0' then y<=f1;

--当输入的基带信号 x=‘0’时,输出的调制信号 y 为 f1

--当输入的基带信号 x=‘1’时,输出的调制信号 y 为 f2

else y<=f2;

end if;

end if;

end process;

end behav;

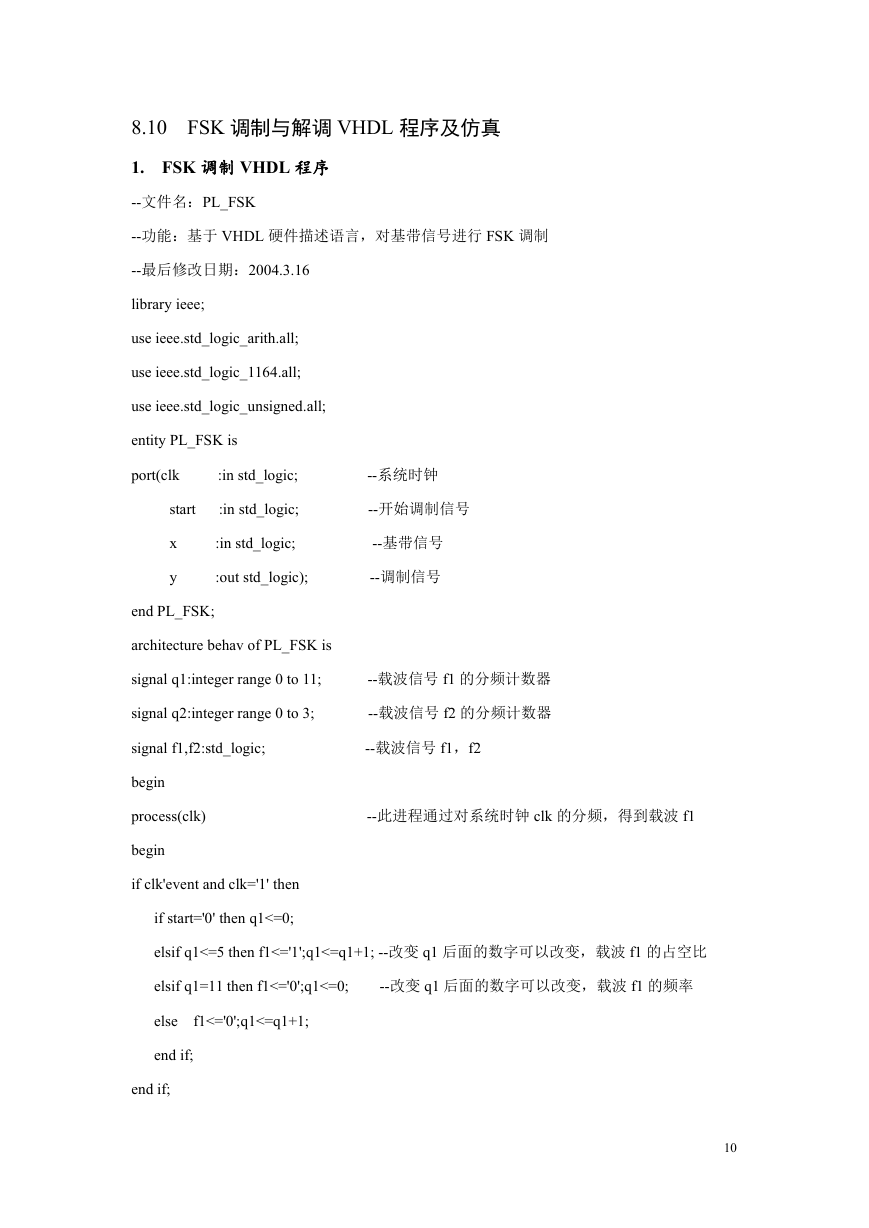

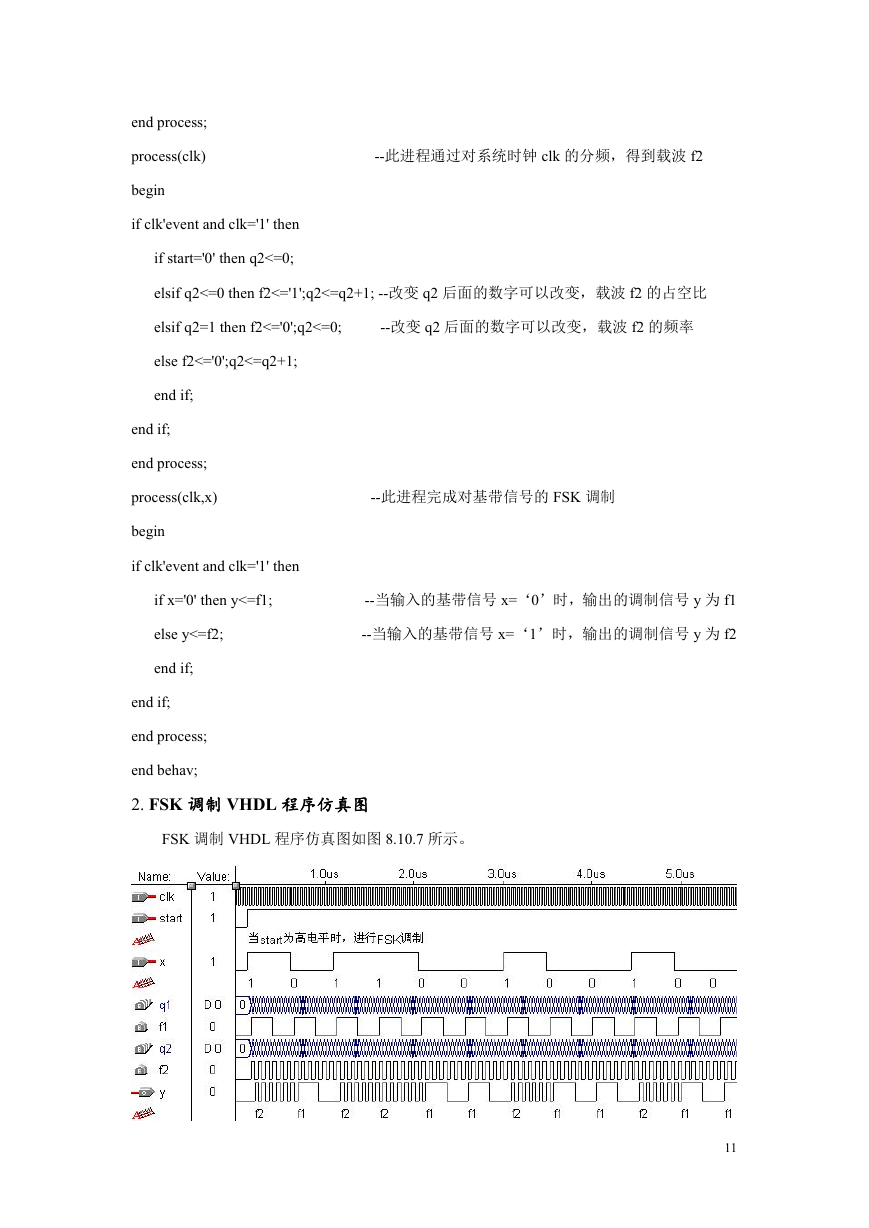

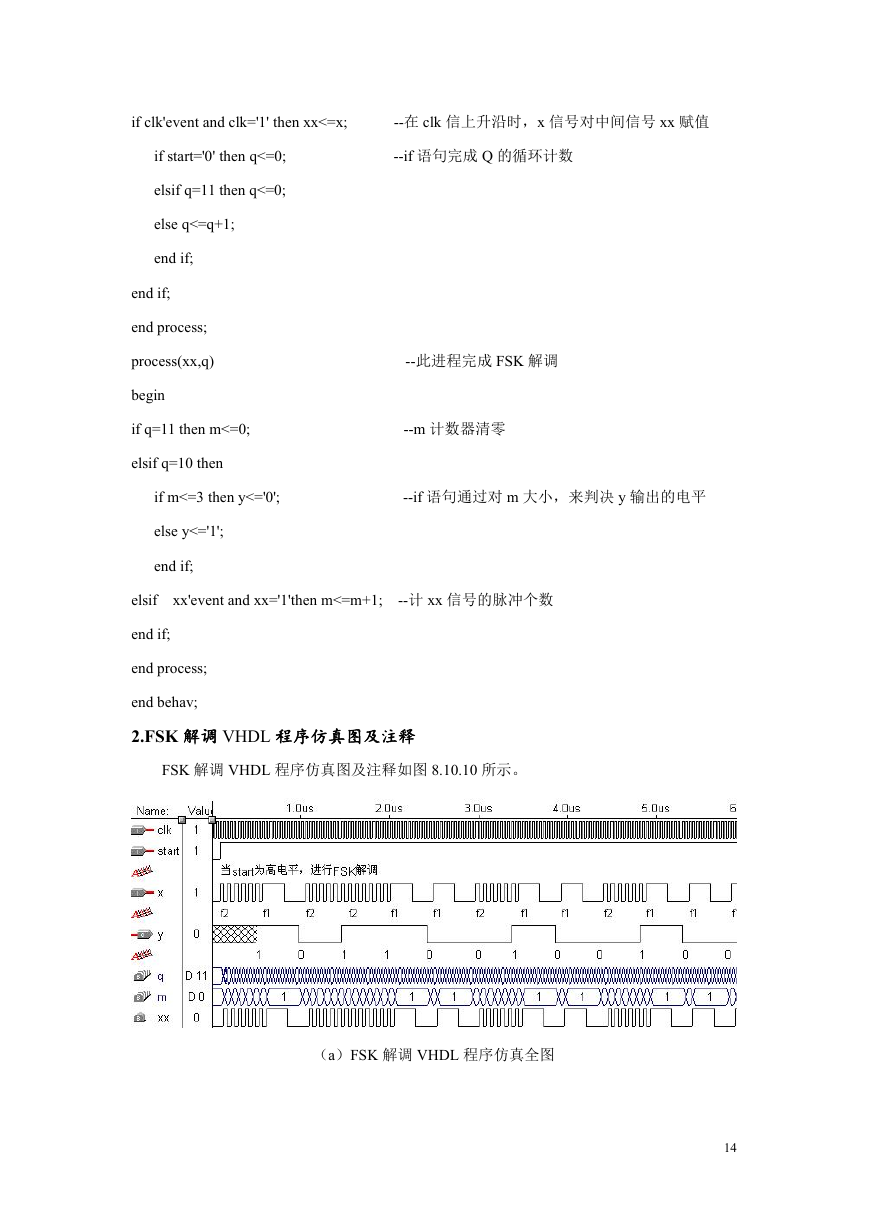

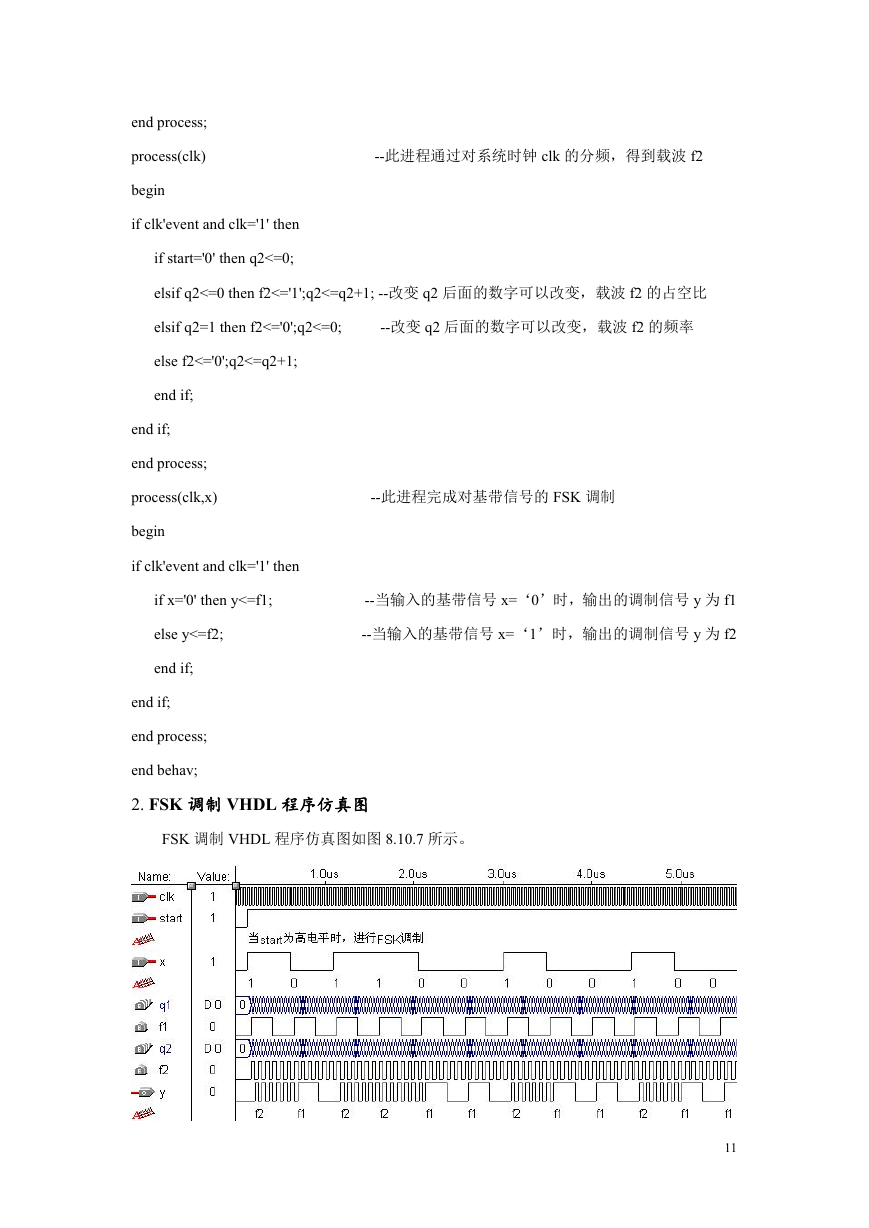

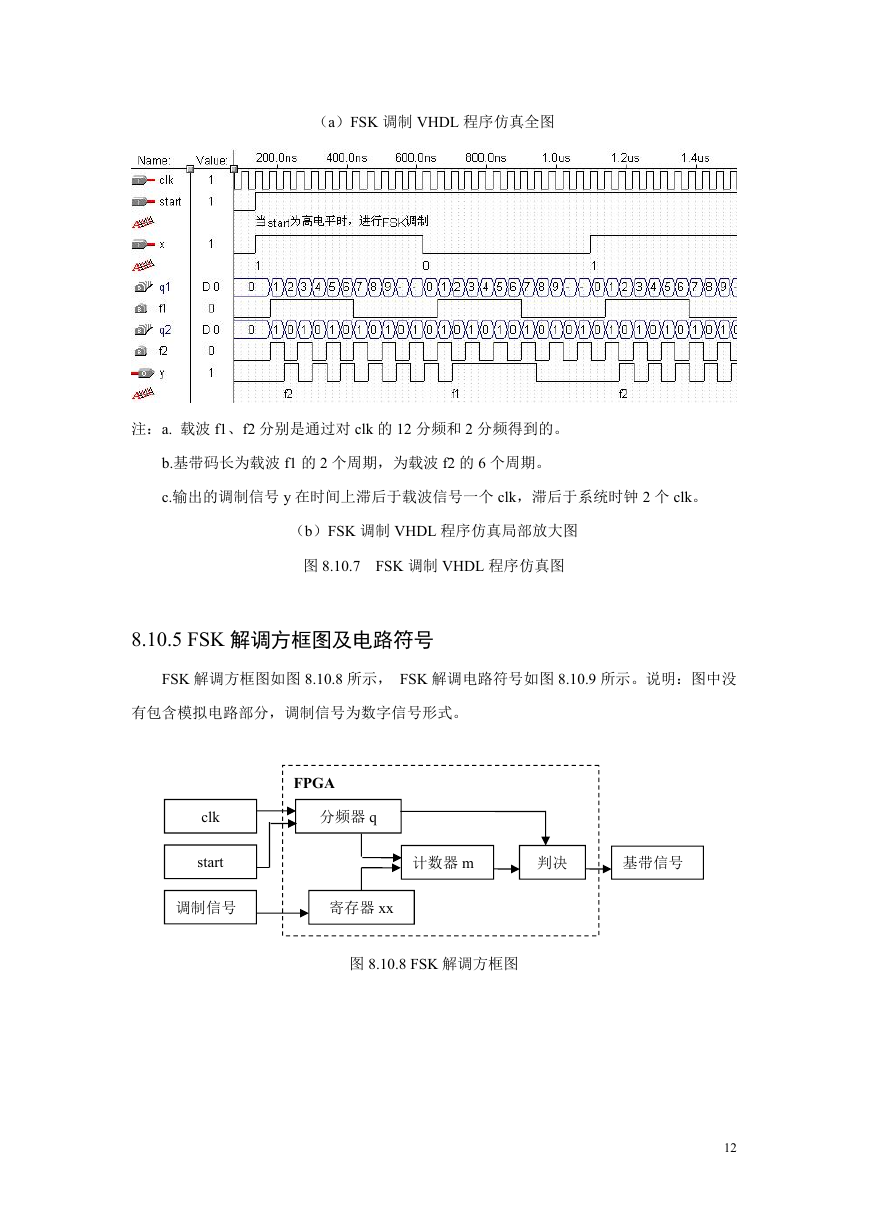

2. FSK 调制 VHDL 程序仿真图

FSK 调制 VHDL 程序仿真图如图 8.10.7 所示。

11

�

(a)FSK 调制 VHDL 程序仿真全图

注:a. 载波 f1、f2 分别是通过对 clk 的 12 分频和 2 分频得到的。

b.基带码长为载波 f1 的 2 个周期,为载波 f2 的 6 个周期。

c.输出的调制信号 y 在时间上滞后于载波信号一个 clk,滞后于系统时钟 2 个 clk。

(b)FSK 调制 VHDL 程序仿真局部放大图

图 8.10.7 FSK 调制 VHDL 程序仿真图

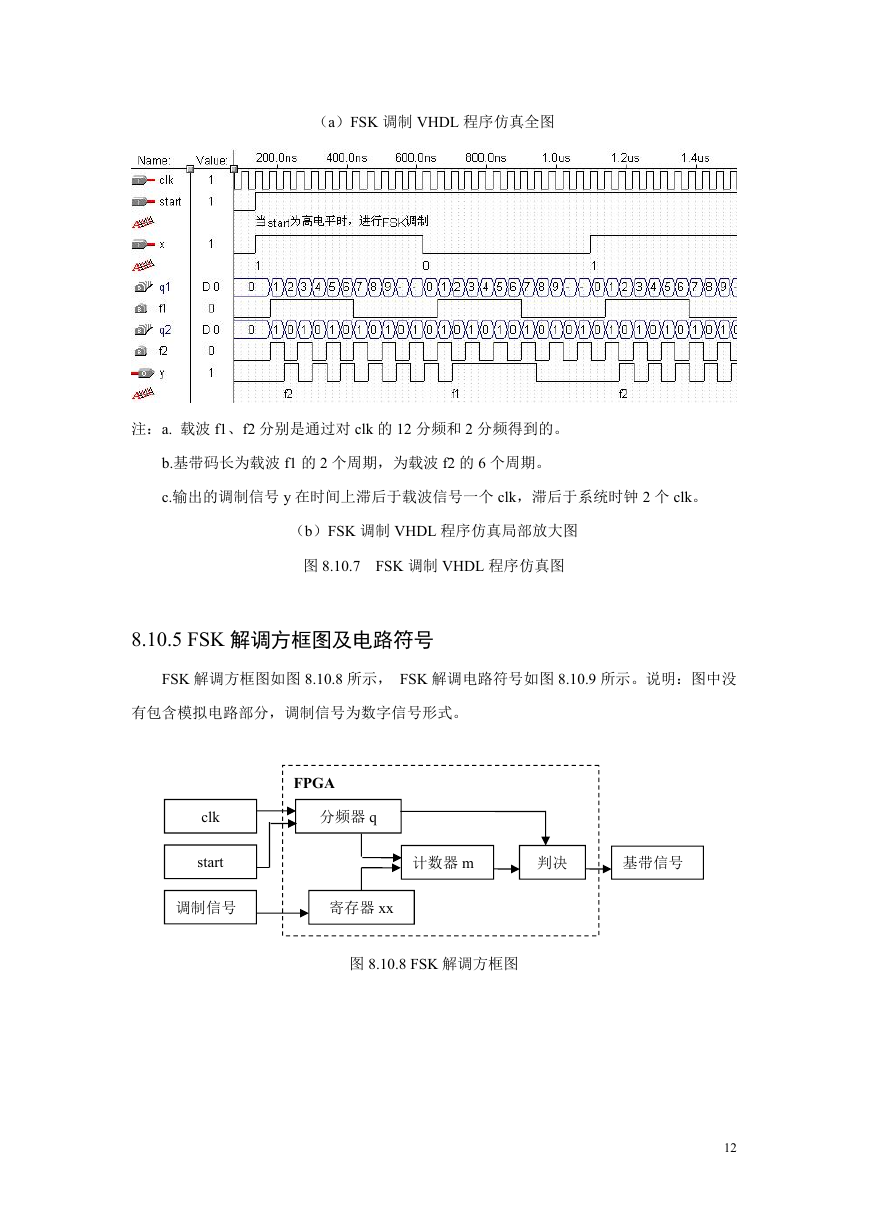

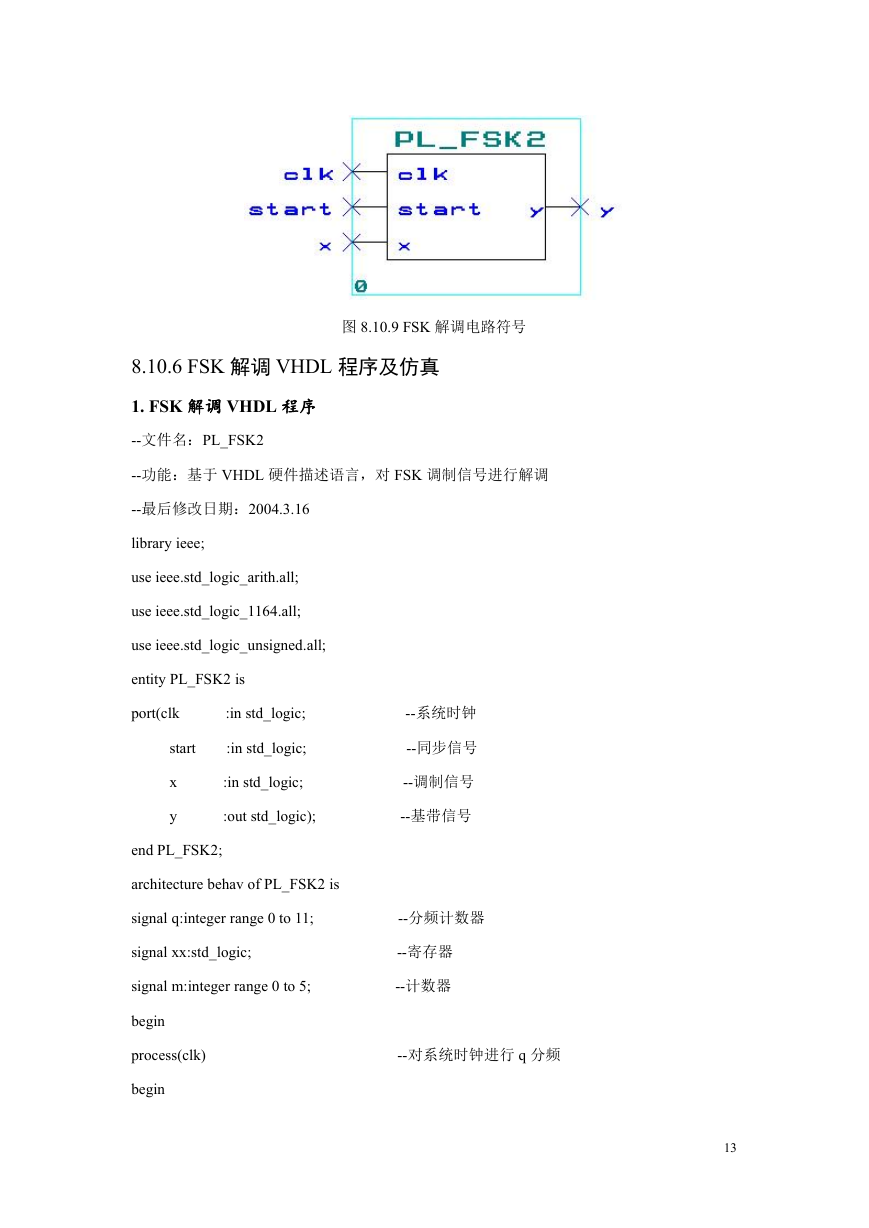

8.10.5 FSK 解调方框图及电路符号

FSK 解调方框图如图 8.10.8 所示, FSK 解调电路符号如图 8.10.9 所示。说明:图中没

有包含模拟电路部分,调制信号为数字信号形式。

FPGA

分频器 q

clk

start

调制信号

寄存器 xx

计数器 m

判决

基带信号

图 8.10.8 FSK 解调方框图

12

�

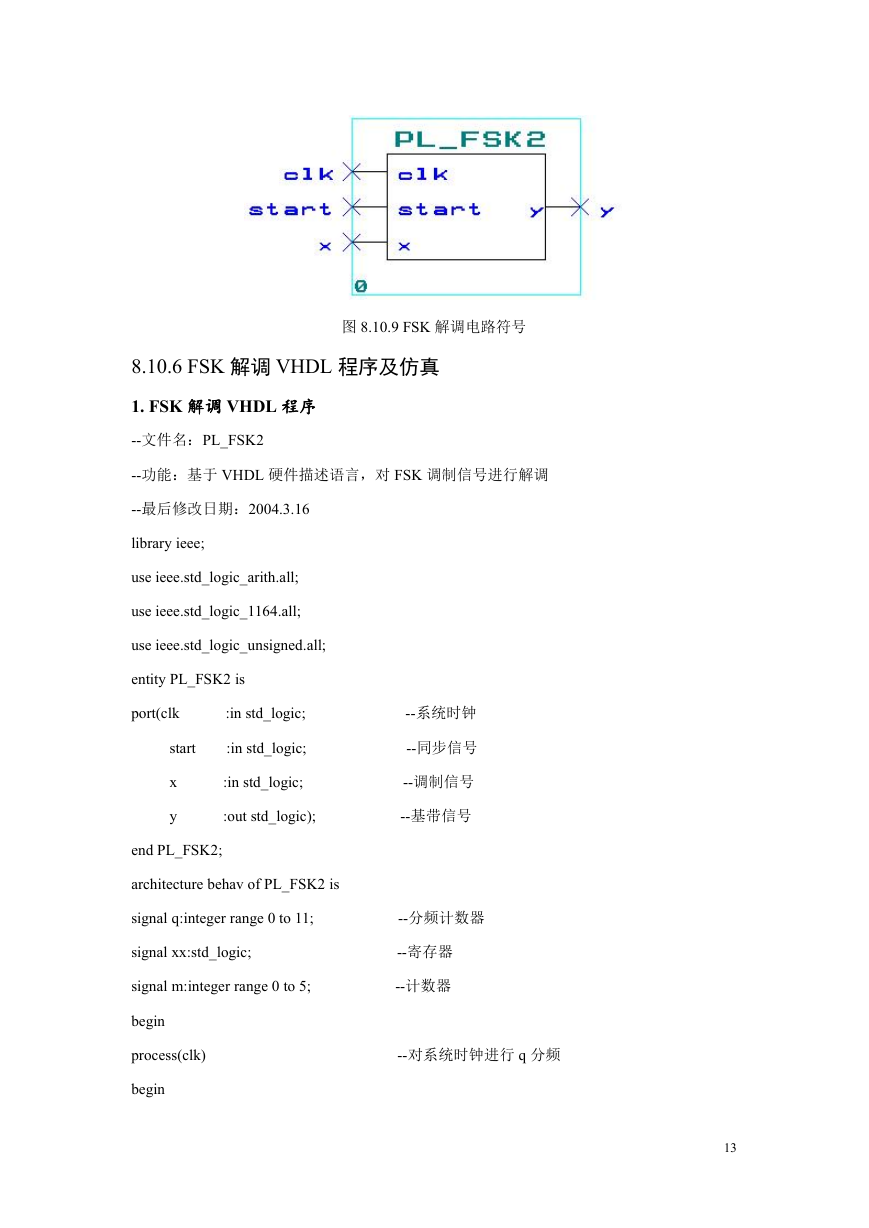

图 8.10.9 FSK 解调电路符号

8.10.6 FSK 解调 VHDL 程序及仿真

1. FSK 解调 VHDL 程序

--文件名:PL_FSK2

--功能:基于 VHDL 硬件描述语言,对 FSK 调制信号进行解调

--最后修改日期:2004.3.16

library ieee;

use ieee.std_logic_arith.all;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity PL_FSK2 is

port(clk

:in std_logic;

start

:in std_logic;

x

y

:in std_logic;

:out std_logic);

end PL_FSK2;

architecture behav of PL_FSK2 is

--系统时钟

--同步信号

--调制信号

--基带信号

signal q:integer range 0 to 11;

--分频计数器

signal xx:std_logic;

signal m:integer range 0 to 5;

--寄存器

--计数器

begin

process(clk)

begin

--对系统时钟进行 q 分频

13

�

if clk'event and clk='1' then xx<=x;

--在 clk 信上升沿时,x 信号对中间信号 xx 赋值

if start='0' then q<=0;

elsif q=11 then q<=0;

else q<=q+1;

end if;

end if;

end process;

process(xx,q)

begin

if q=11 then m<=0;

elsif q=10 then

--if 语句完成 Q 的循环计数

--此进程完成 FSK 解调

--m 计数器清零

if m<=3 then y<='0';

--if 语句通过对 m 大小,来判决 y 输出的电平

else y<='1';

end if;

elsif

xx'event and xx='1'then m<=m+1;

--计 xx 信号的脉冲个数

end if;

end process;

end behav;

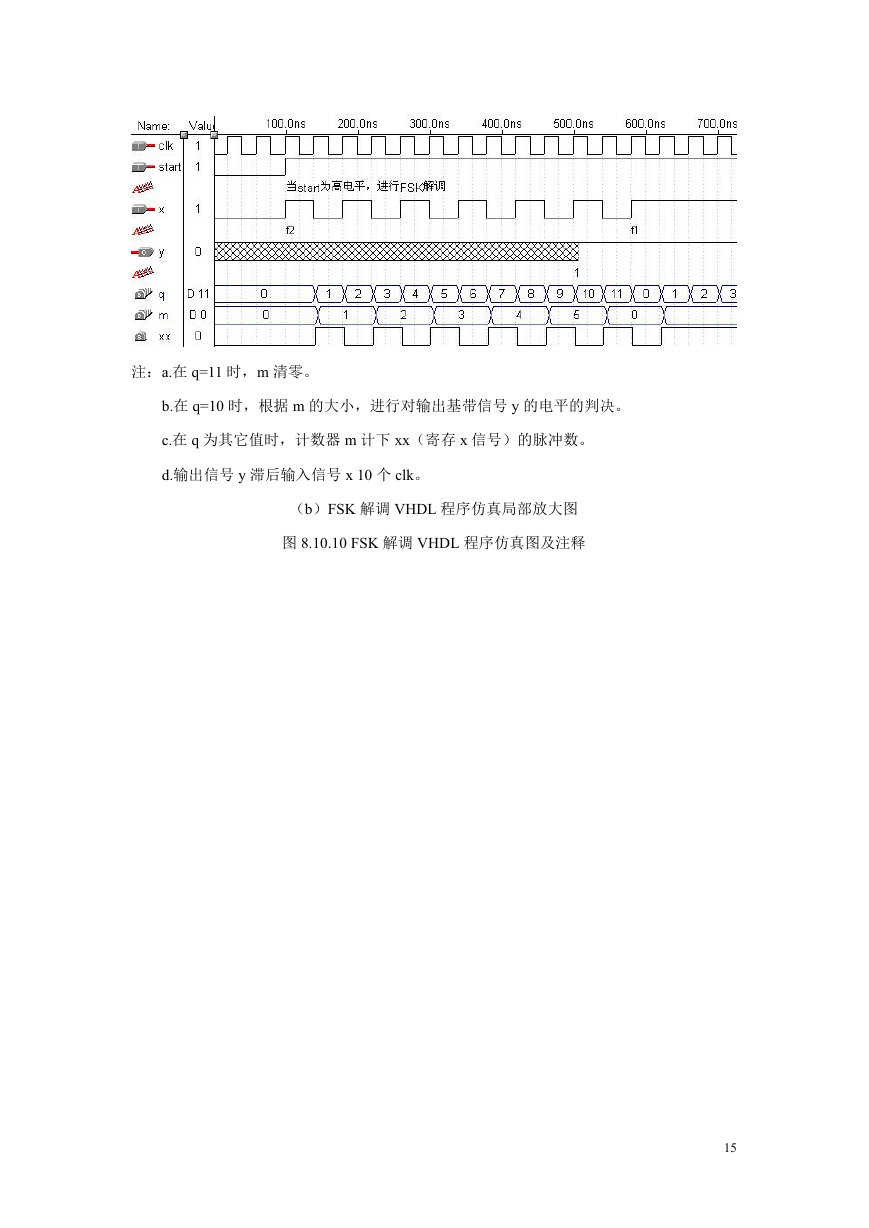

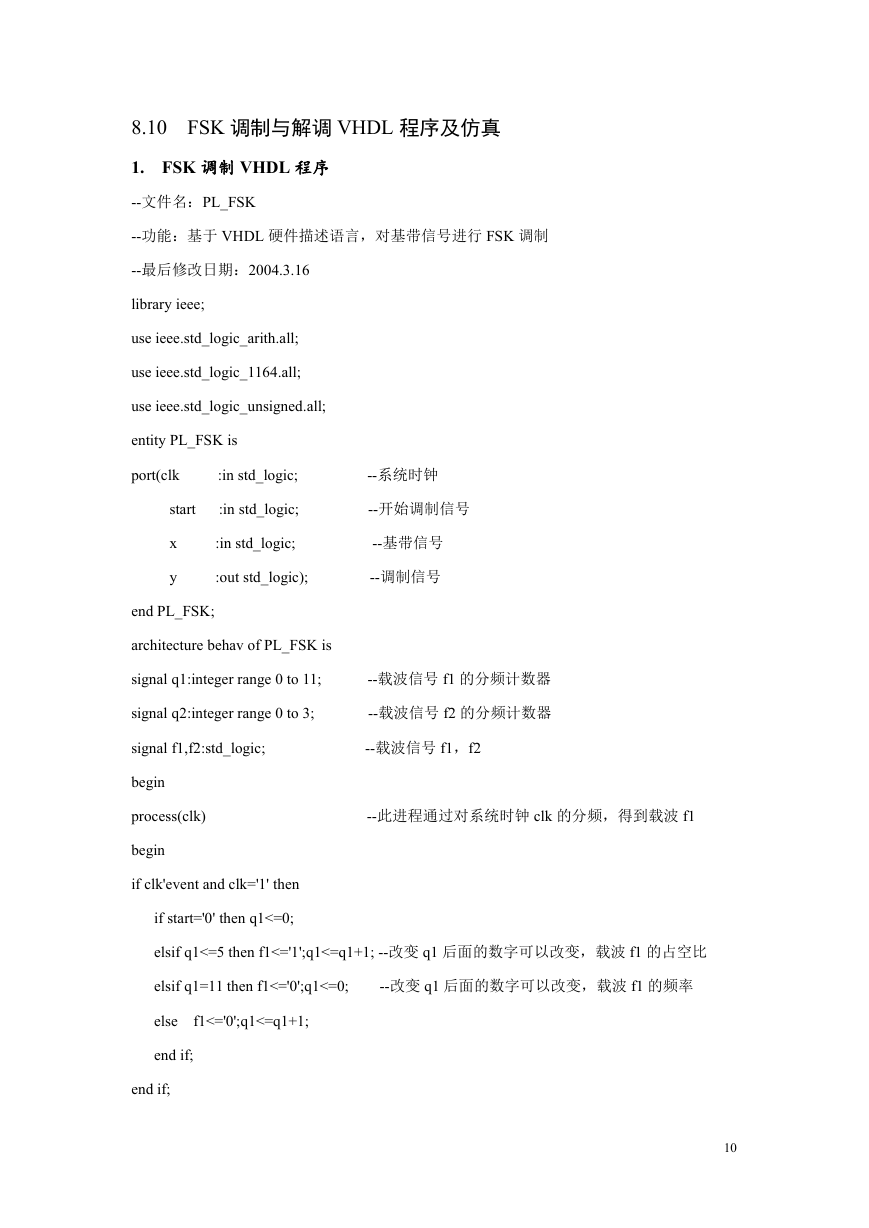

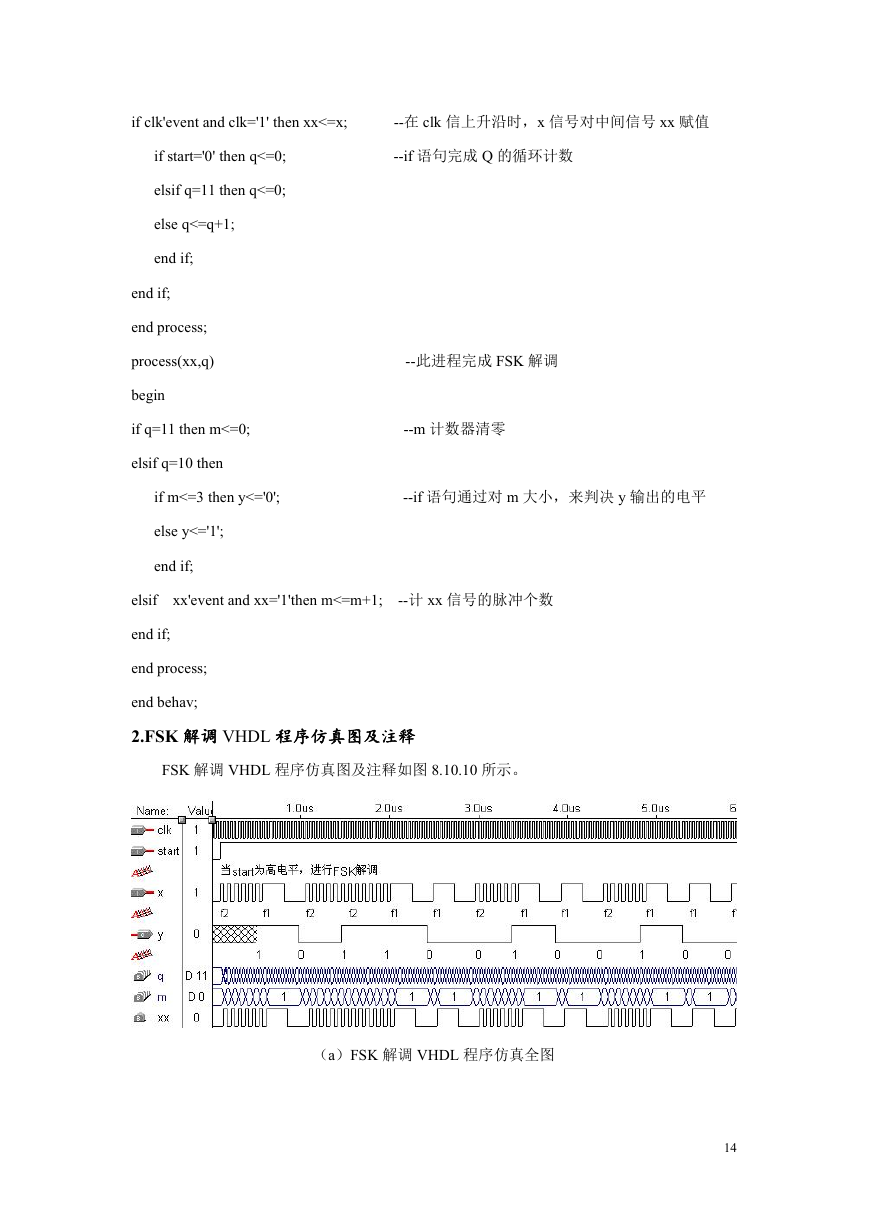

2.FSK 解调 VHDL 程序仿真图及注释

FSK 解调 VHDL 程序仿真图及注释如图 8.10.10 所示。

(a)FSK 解调 VHDL 程序仿真全图

14

�

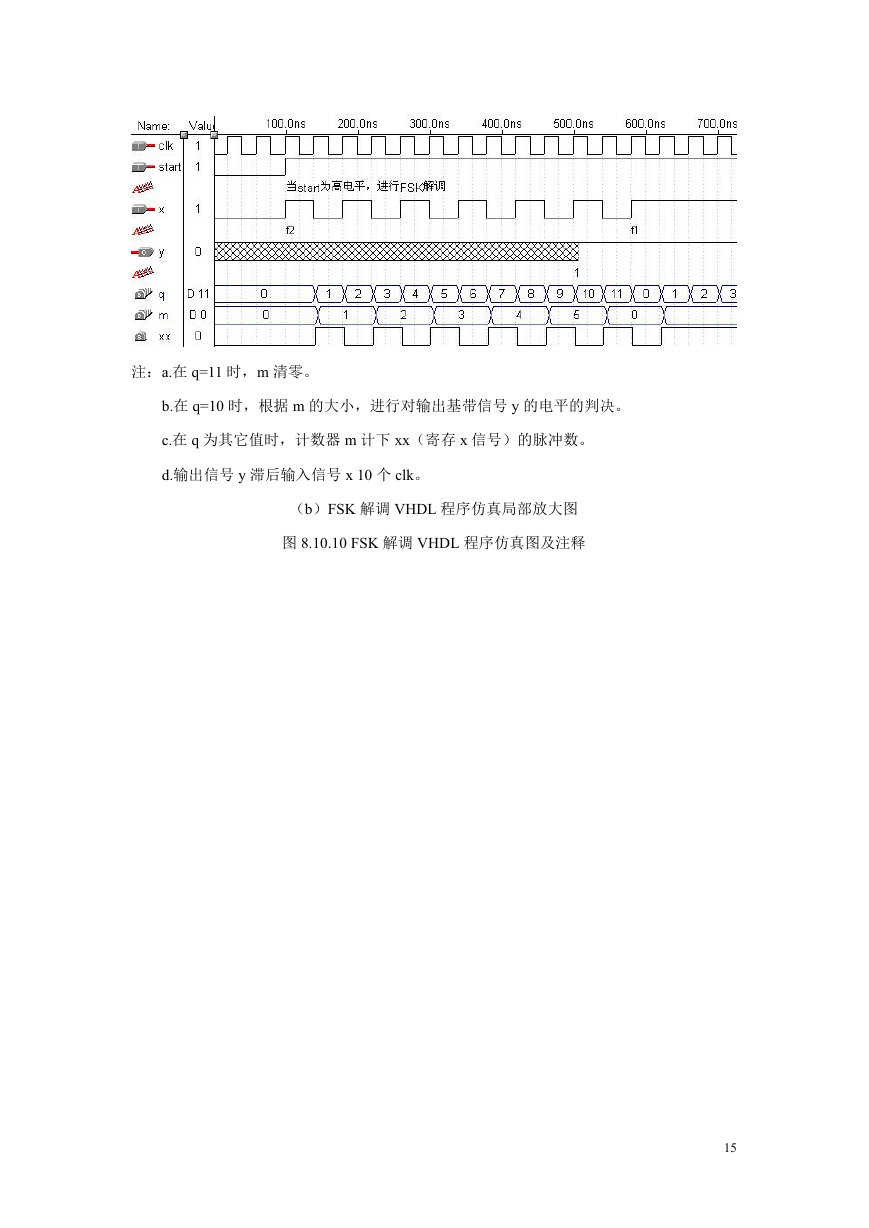

注:a.在 q=11 时,m 清零。

b.在 q=10 时,根据 m 的大小,进行对输出基带信号 y 的电平的判决。

c.在 q 为其它值时,计数器 m 计下 xx(寄存 x 信号)的脉冲数。

d.输出信号 y 滞后输入信号 x 10 个 clk。

(b)FSK 解调 VHDL 程序仿真局部放大图

图 8.10.10 FSK 解调 VHDL 程序仿真图及注释

15

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc