QCA7500 IEEE 1901 and HomePlug®

AV2 Compliant MAC/PHY Transceiver

Preliminary Data Sheet

80-Y5258-1 Rev. C

November 1, 2013

Q ualco m m Atheros Confidential

NO PUBLIC DISCLOSURE PERMITTED – Please report postings of this document on public servers or websites

to: DocCtrlAgent@qualcomm.com.

Restricted Distribution. Not to be distributed to anyone who is not an employee of either Qualcomm or its

subsidiaries without the express approval of Qualcomm’s Configuration Management.

Not to be used, copied, reproduced, or modified in whole or in part, nor its contents revealed in any manner to others

without the express written permission of Qualcomm Atheros, Inc.

Qualcomm is a registered trademark of QUALCOMM Incorporated. Atheros is a registered trademark of Qualcomm

Atheros, Inc. Atheros is a trademark of Qualcomm Atheros, registered in the United States and other countries.. All

other registered and unregistered trademarks are the property of QUALCOMM Incorporated, Qualcomm Atheros,

Inc., or their respective owners and used with permission. Registered marks owned by QUALCOMM Incorporated

and Qualcomm Atheros, Inc. are registered in the United States and may be registered in other countries.

This technical data may be subject to U.S. and international export, re-export, or transfer (“export”) laws. Diversion

contrary to U.S. and international law is strictly prohibited.

Confidential and Proprietary - Qualcomm Atheros, Inc.

Qualcomm Atheros, Inc.

1700 Technology Drive

San Jose, CA 95110

U.S.A.

© 2013 Qualcomm Atheros, Inc.

�

Revision History

Rev. C

Description

Date

June 2013

August 2013

Revision

Rev. A

Rev. B

November 2013 PL41 (QCA7500) ES Release

QCA7500 Preliminary Data Sheet

Updated QCA7500 Block Diagram and GPIO content throughout the

document. Updated Package Dimensions.

Q ualco m m Atheros Confidential

80-Y5258-1 Rev. C

MAY CONTAIN U.S. AND INTERNATIONAL EXPORT CONTROLLED INFORMATION

2

Confidential and Proprietary - Qualcomm Atheros, Inc.

�

Contents

Q ualco m m Atheros Confidential

1 General Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5

1.1 Applications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5

Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5

1.2

Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6

1.3

1.4

Conventions used in this Data Sheet . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7

2 Pin Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

2.1 QCA7500 Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

2.1.1 QCA7500 Pin Assignments . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

2.2

Signal-to-Pin Relationships and Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

2.3 QCA7500 Configuration Straps and Defaults . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

3 Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

3.1 Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

3.1.1 QCA7500 On-board System Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

3.1.2 Simple Wall Adapter Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

System Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

3.2.1 Power Management Unit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

3.3

External Memory Interface (DDR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26

3.4 GPIO Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26

Serial Interfaces . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

3.5

3.5.1 Boot Options . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

Reduced Gigabit Media Independent Interface (RGMII) and Reduced Media Independent

Interface (RMII) 27

System Components . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28

3.7.1 Powerline Connections . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28

Core Voltage Power Supply . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28

4 Electrical Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

4.1 Absolute Maximum Ratings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

4.2

Recommended Operating Conditions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30

4.3 QCA7500 Power Supply Requirements . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30

4.4 DC Switching Thresholds . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31

4.5

Crystal Specifications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31

4.6 Oscillator CMOS Inverter Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31

3.8

3.6

3.7

3.2

80-Y5258-1 Rev. C

MAY CONTAIN U.S. AND INTERNATIONAL EXPORT CONTROLLED INFORMATION

3

Confidential and Proprietary - Qualcomm Atheros, Inc.

�

QCA7500 IEEE 1901 and HomePlug® AV2 Compliant MAC/PHY Transceiver Preliminary Data Sheet

Contents

5 Ethernet Management Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32

Ethernet PHY Control Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 33

5.1

5.2

Ethernet PHY MII Status Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 35

5.3 OUI Register (LSB) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 37

5.4 OUI Register (MSB) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 37

5.5 Auto-negotiate Advertize Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38

5.6 Auto-negotiate Link Partner Ability Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39

5.7 Auto-Negotiation Expansion Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 41

5.8 Next Page Transmit Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 42

5.9

Link Partner Received Next Page Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 43

5.10 THOUSAND BASE-T Control Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 44

5.11 THOUSANDBASE-T Status Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 45

5.12 Extended Status Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 46

6 Timing Constraints . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 47

System Clock and Reset Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 47

6.1

Zero Crossing Detector Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 48

6.2

RGMII Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 49

6.3

RGMII MDIO Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 51

6.4

6.5

SPI (Boot FLASH) Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 52

6.6 DDR Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 53

7 Package Dimensions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 54

8 Ordering Information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 58

Q ualco m m Atheros Confidential

80-Y5258-1 Rev. C

MAY CONTAIN U.S. AND INTERNATIONAL EXPORT CONTROLLED INFORMATION

4

Confidential and Proprietary - Qualcomm Atheros, Inc.

�

1.1 Applications

1 General Description

The QCA7500 HPAV2 Compliant MAC/PHY Transceiver is a System-on-Chip (SoC) designed to

bridge multi-stream Ethernet content from a powerline network to an Ethernet 802.3 network.

Examples include high and standard definition television (HDTV, SDTV), and other digital

multimedia file sharing and data applications. The powerline communications (PLC) specific

MAC manages network admission and service flows to maximize the quality of service (QoS)

over the powerline network.

Q ualco m m Atheros Confidential

High Definition (HD) and Standard Definition (SD) video distribution

Internet Protocol Television (IPTV) distribution

Home networking backbone for Hy-Fi, Wi-Fi, and Wireless USB

High speed broadband sharing

Audio and video streaming and internet downloading

Voice over Internet Protocol (VoIP)

PC files and applications sharing

Printer and peripheral sharing

Network and interactive online gaming

SecurityHy-Fi cameras

IEEE 1901, IEEE 1905.1 and HomePlug AV Compliant

Coexistence with HomePlug 1.0/Turbo nodes

Integrated MAC/PHY, analog front end and line driver

Supports RGMII/RMII Ethernet with both MAC and PHY mode

Supports DDR2/3 Memory

Powered from a single 3.3VDC rail with an integrated power management unit

1.2 Features

HomePlug® AV2 Compliant

AV2 30MHz and 67MHz MIMO profiles

AV2 30MHz and 67MHz SISO profiles

Power Save Mode

80-Y5258-1 Rev. C

MAY CONTAIN U.S. AND INTERNATIONAL EXPORT CONTROLLED INFORMATION

5

Confidential and Proprietary - Qualcomm Atheros, Inc.

�

QCA7500 IEEE 1901 and HomePlug® AV2 Compliant MAC/PHY Transceiver Preliminary Data Sheet

General

HomePlug AV2 Compliant PHY:

Supports OFDM 4096/1024/256/64/16/8-QAM, QPSK, BPSK, ROBO, HS-ROBO, Mini-

ROBO

Number

Supports IGMP managed multicast sessions

HomePlug AV2 Compliant MAC:

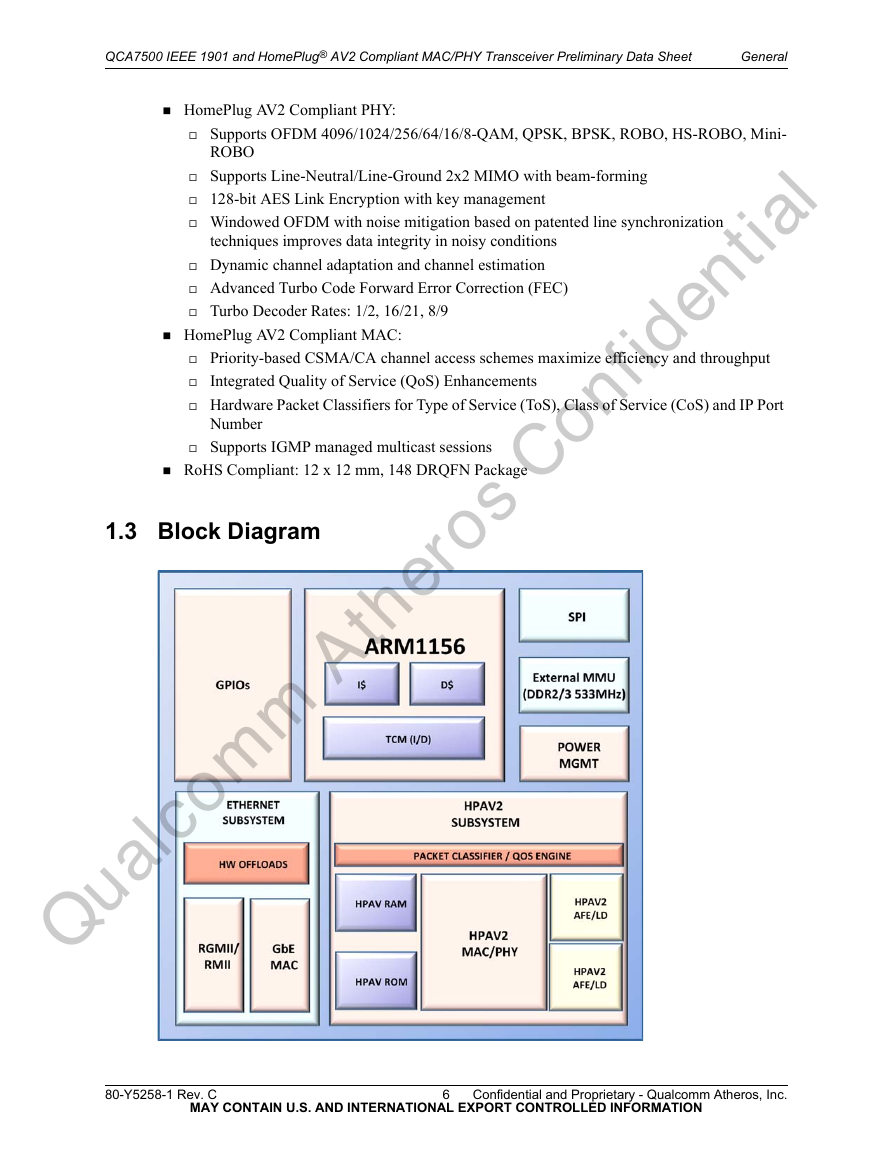

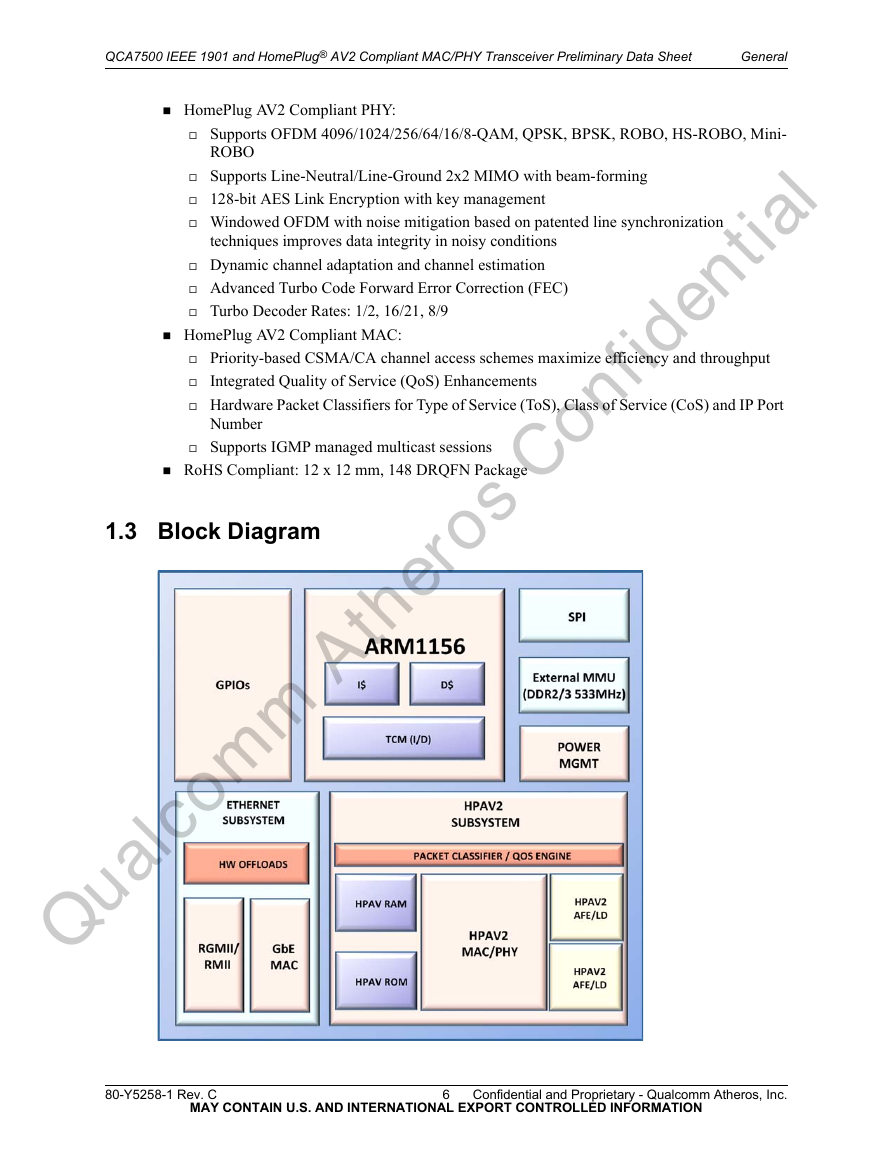

1.3 Block Diagram

techniques improves data integrity in noisy conditions

Dynamic channel adaptation and channel estimation

Advanced Turbo Code Forward Error Correction (FEC)

Turbo Decoder Rates: 1/2, 16/21, 8/9

RoHS Compliant: 12 x 12 mm, 148 DRQFN Package

Supports Line-Neutral/Line-Ground 2x2 MIMO with beam-forming

128-bit AES Link Encryption with key management

Windowed OFDM with noise mitigation based on patented line synchronization

Priority-based CSMA/CA channel access schemes maximize efficiency and throughput

Integrated Quality of Service (QoS) Enhancements

Hardware Packet Classifiers for Type of Service (ToS), Class of Service (CoS) and IP Port

Q ualco m m Atheros Confidential

80-Y5258-1 Rev. C

MAY CONTAIN U.S. AND INTERNATIONAL EXPORT CONTROLLED INFORMATION

6

Confidential and Proprietary - Qualcomm Atheros, Inc.

�

QCA7500 IEEE 1901 and HomePlug® AV2 Compliant MAC/PHY Transceiver Preliminary Data Sheet

General

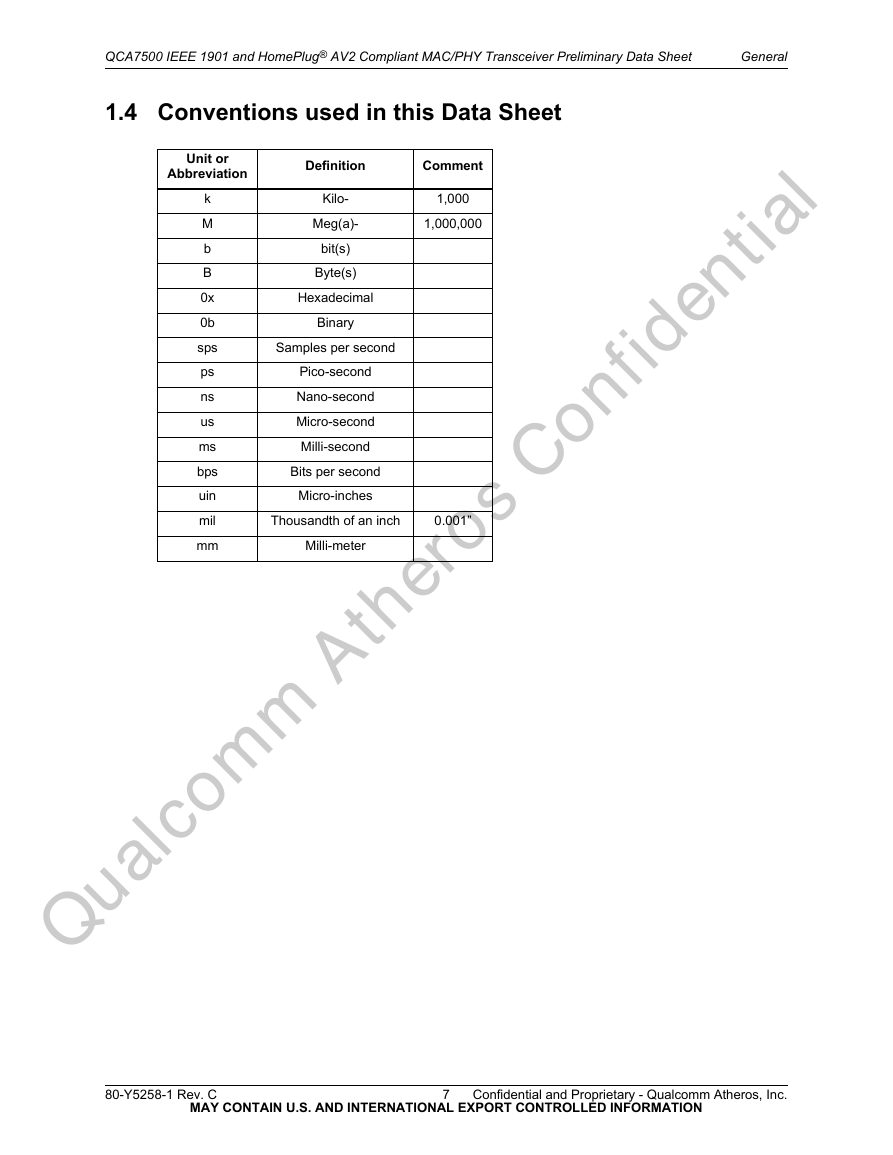

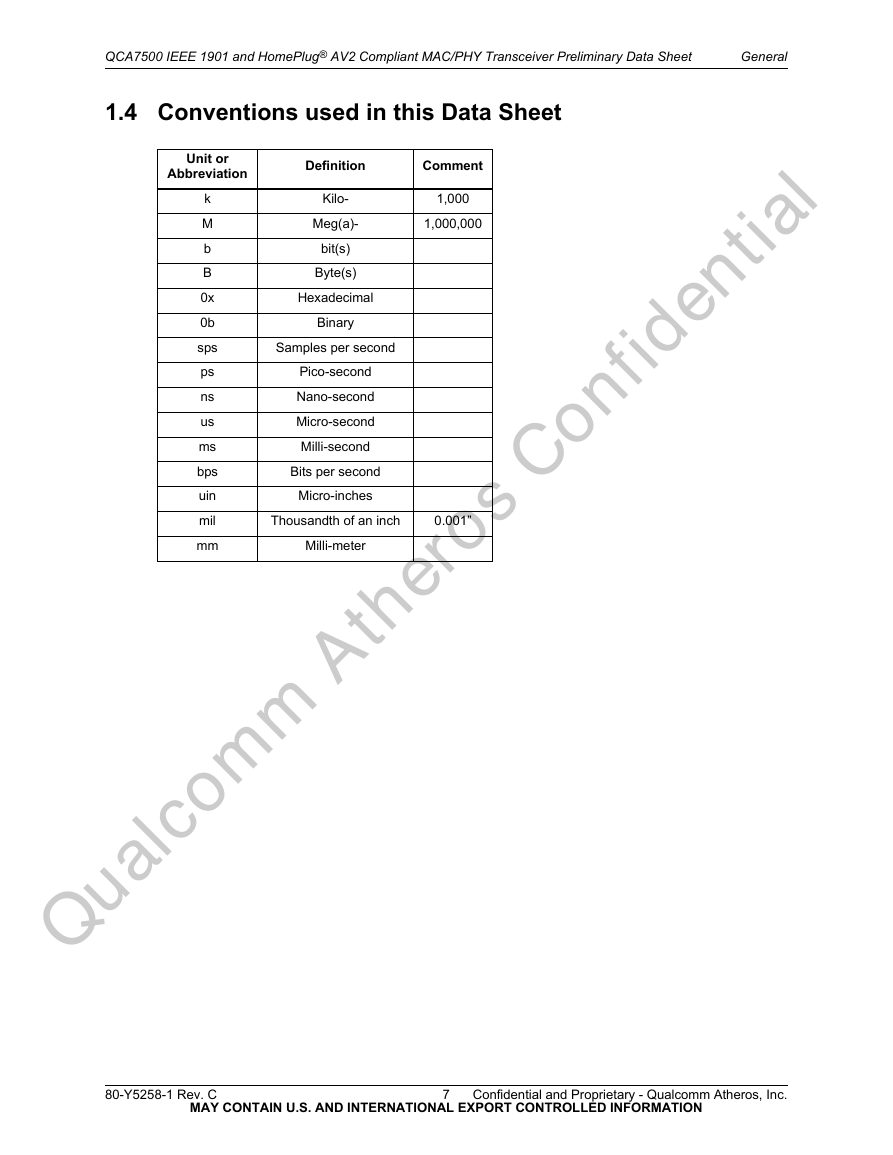

1.4 Conventions used in this Data Sheet

Unit or

Abbreviation

Definition

Kilo-

Hexadecimal

Binary

Comment

1,000

1,000,000

Samples per second

Thousandth of an inch

0.001”

Meg(a)-

bit(s)

Byte(s)

Bits per second

Micro-inches

Pico-second

Nano-second

Micro-second

Milli-second

k

M

b

B

0x

0b

sps

ps

ns

us

ms

bps

uin

mil

mm

Q ualco m m Atheros Confidential

Milli-meter

80-Y5258-1 Rev. C

MAY CONTAIN U.S. AND INTERNATIONAL EXPORT CONTROLLED INFORMATION

7

Confidential and Proprietary - Qualcomm Atheros, Inc.

�

2 Pin Descriptions

DNC

_L

P

N

GND

I

I/O

IA

IH

The following nomenclature is used for signal names:

This section contains both a package pinout (see Figure 2-1, Table 2-1and Table 2-2) and tabular

listings of the signal descriptions.

No connection should be made to this pin

At the end of the signal name, indicates active low signals

At the end of the signal name, indicates the positive side of a differential signal

At the end of the signal name indicates the negative side of a differential signal

Q ualco m m Atheros Confidential

A ground signal

Digital input signal

A digital bidirectional signal

Analog input signal

Input signals with weak internal pull-up, to prevent signals from floating when left

open

Input signals with weak internal pull-down, to prevent signals from floating when left

open

Power Input

A digital output signal

An analog output signal

Power Output

A power signal

The following nomenclature is used for signal types:

IL

IP

O

OA

OP

P

80-Y5258-1 Rev. C

MAY CONTAIN U.S. AND INTERNATIONAL EXPORT CONTROLLED INFORMATION

8

Confidential and Proprietary - Qualcomm Atheros, Inc.

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc