一、coresight

coresight 是 ARM 公司提出的,用于对复杂的 SOC,实现 debug 和 trace 的架构。

该架构,包含了多个 coresight 组件。众多的 coresight 组件,构成了一个

coresight 系统。我们也可以根据 coresight 架构,实现自己的 coresight 组件。

每个 coresight 的组件(component),都要遵循 coresight 架构的要求。

1、 典型的一个 coresight 的环境

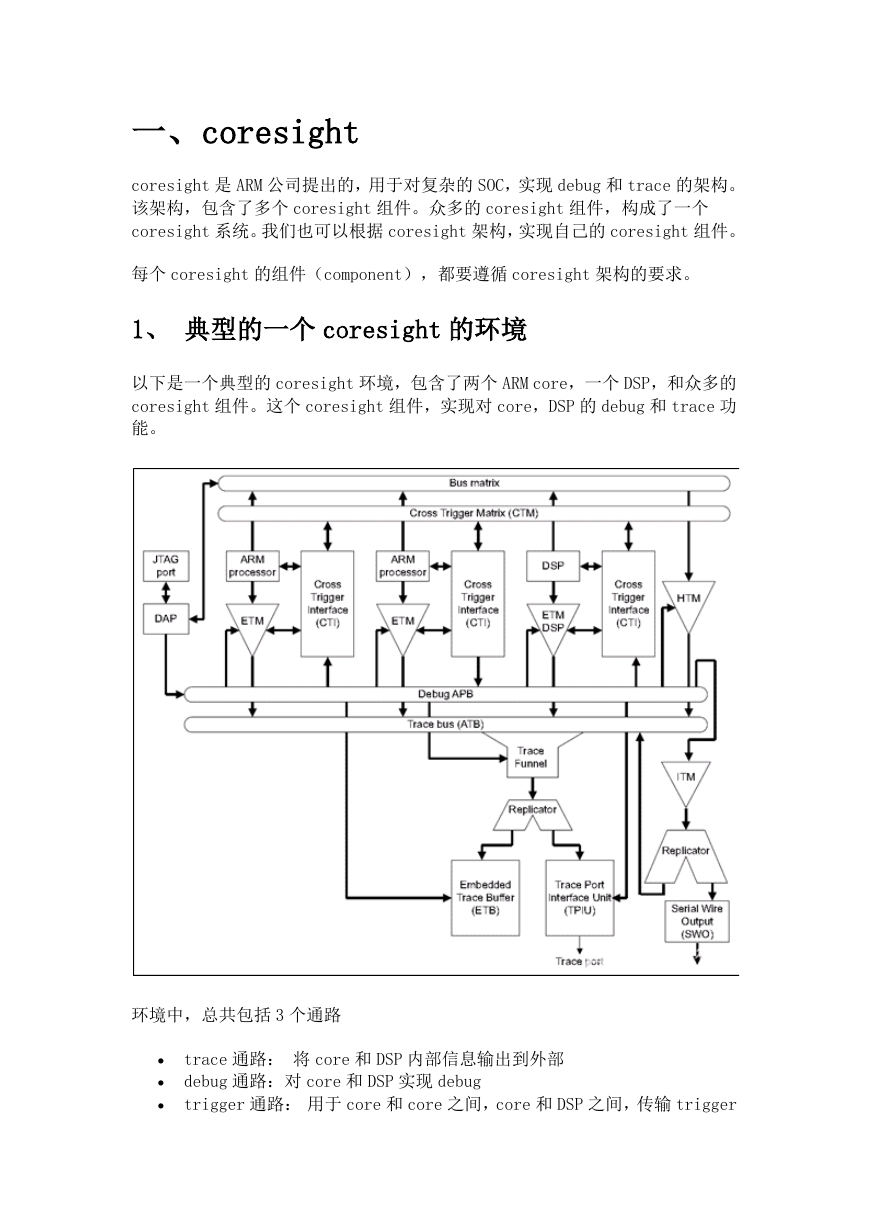

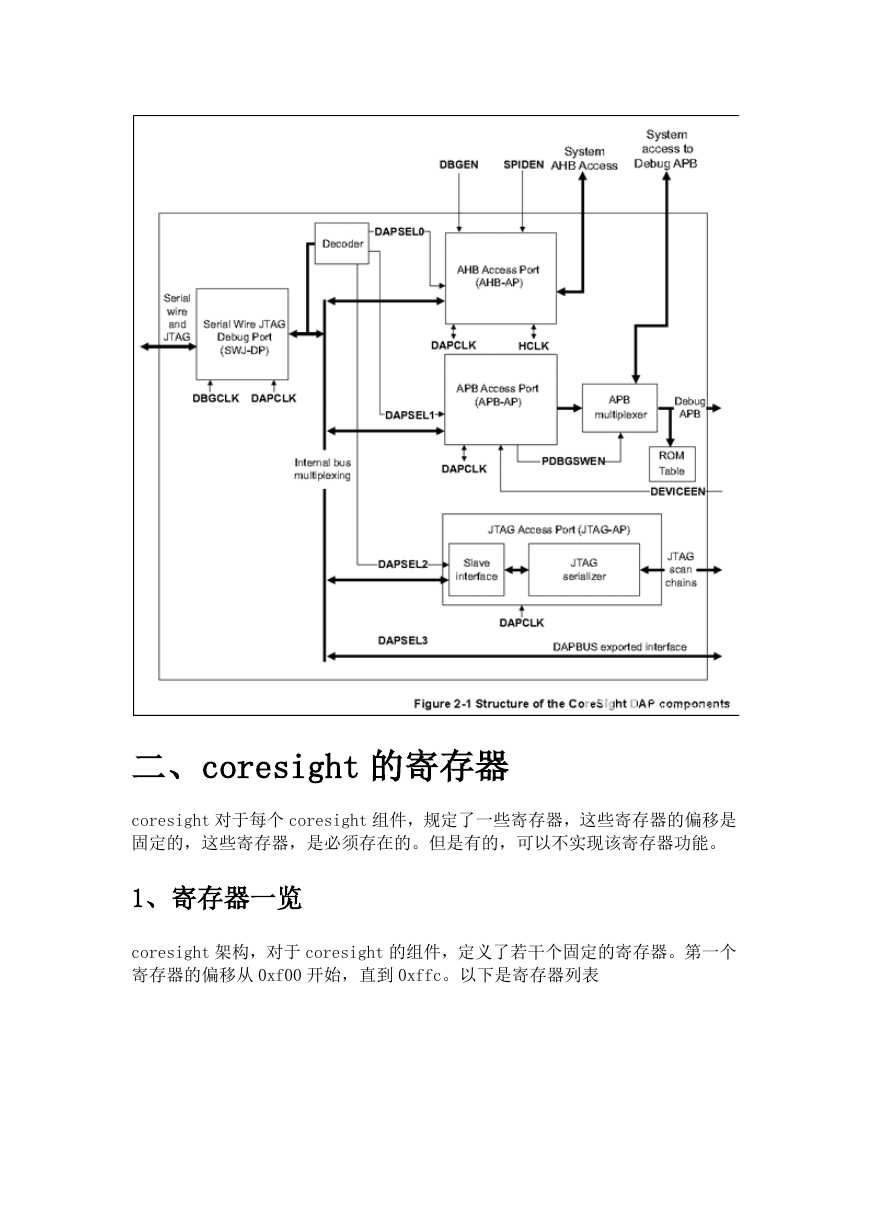

以下是一个典型的 coresight 环境,包含了两个 ARM core,一个 DSP,和众多的

coresight 组件。这个 coresight 组件,实现对 core,DSP 的 debug 和 trace 功

能。

环境中,总共包括 3 个通路

trace 通路: 将 core 和 DSP 内部信息输出到外部

debug 通路:对 core 和 DSP 实现 debug

trigger 通路: 用于 core 和 core 之间,core 和 DSP 之间,传输 trigger

�

信号

1.1、trace 通路

trace 通路,实现对 master 组件的数据追踪功能,使用 ETM 来追踪。

ETM 负责追踪处理器和 DSP 的信息,将信息打包,通过 ATB 总线发送到 trace bus

上。trace bus 上有 trace funnel,funnel 接收多个 ATB 总线数据,然后合并

成一个 ATB 总线数据,发送给 replicator。

replicator 接收到 ATB 数据,根据配置,将 ATB 数据发送给 ETB 和 TPIU。

1.2、debug 的通路

debug 通路,用于外部的 debugger,对 ARM core 和 DSP 进行调试功能。

上图中,只考虑了 JTAG 的 port。其实还有 SW 的 port。

DAP 接收外部端口的 JTAG 数据,然后转化成对 DAP 内部的 AP 的访问,然后 AP

再转化为 memory-mapped 的总线访问,去访问 soc 内部的资源。

上图中,DAP 输出两个 memory-mapped 总线,一个是 debug apb 总线,连接到 debug

APB 互联上,用于访问 debug 组件的寄存器,一个是 system bus,连接到 bus

matrix,用于访问 soc 的内部的资源。

debug APB 互联,连接了有 CTI,ETM,HTM,ITM,ETB,TPIU 等 coresight 组件,

因此外部的 debugger 可以通过 JTAG port,对这些 coresight 组件进行访问。

bus matrix 一般是连接 soc 的一些外设,如 memory,串口等,因此外部的 debugger

可以通过 JTAG port 对这些外设设备进行访问。

1.3、trigger 通路

trigger 通路,用于给指定的组件发送 trigger 信号,或者接收指定的组件的

trigger 信号。这个功能由 CTI 和 CTM 来实现。

每个 core 和 DSP 都有一个 CTI 组件相连,CTI 可以给处理器(DSP)发送 trigger

信号,也可以接收处理器(DSP)的 trigger 信号。

所有的 CTI 和 CTM 相连,因此可以实现多个 CTI 之间的 trigger 信号的相互发送

与接收。

�

2、coresight 组件的种类

2.1、control component

trigger 的 coresight 组件

ECT(embedded cross trigger)

o CTI(cross trigger interface):接收和发送 trigger 信号

o CTM(cross trigger matrix):CTI 之间的 trigger 信号传递

2.2、trace sources

trace 的 coresight 组件:

ETM(embedded trace macrocells):追踪指定设备(处理器,DSP)的

trace 信息,每个设备(处理器,DSP)均有自己的 ETM。

AMBA trace macrocells:追踪 AMBA 总线的 trace 信息。

PTM(program flow trace macrocells):

STM(system trace macrocells):追踪总线互联上的 trace 信息

2.3、trace links

trace 信息传递过程中所需要的中间 coresight 组件:

trace funnel : 将接收的多个 ATB 总线数据合并成一个 ATB 总线数据

replicator: 将一个 ATB 总线数据,分发成多个 ATB 总线数据发送

ATB bridge: ATB 桥,用于两个不同的 ATB 域之间数据传输

2.4、trace sinks

最终接收 trace 信息的 coresight 组件

TPIU(trace port interface units):将 ATB 数据通过 trace port 发

送给外界

ETB(embedded trace buffers): 存储 ATB 数据的 buffer

TMC(trace memory controller):

每个 trace sink 可以有一个 trace formatter。

�

2.5、debug access port

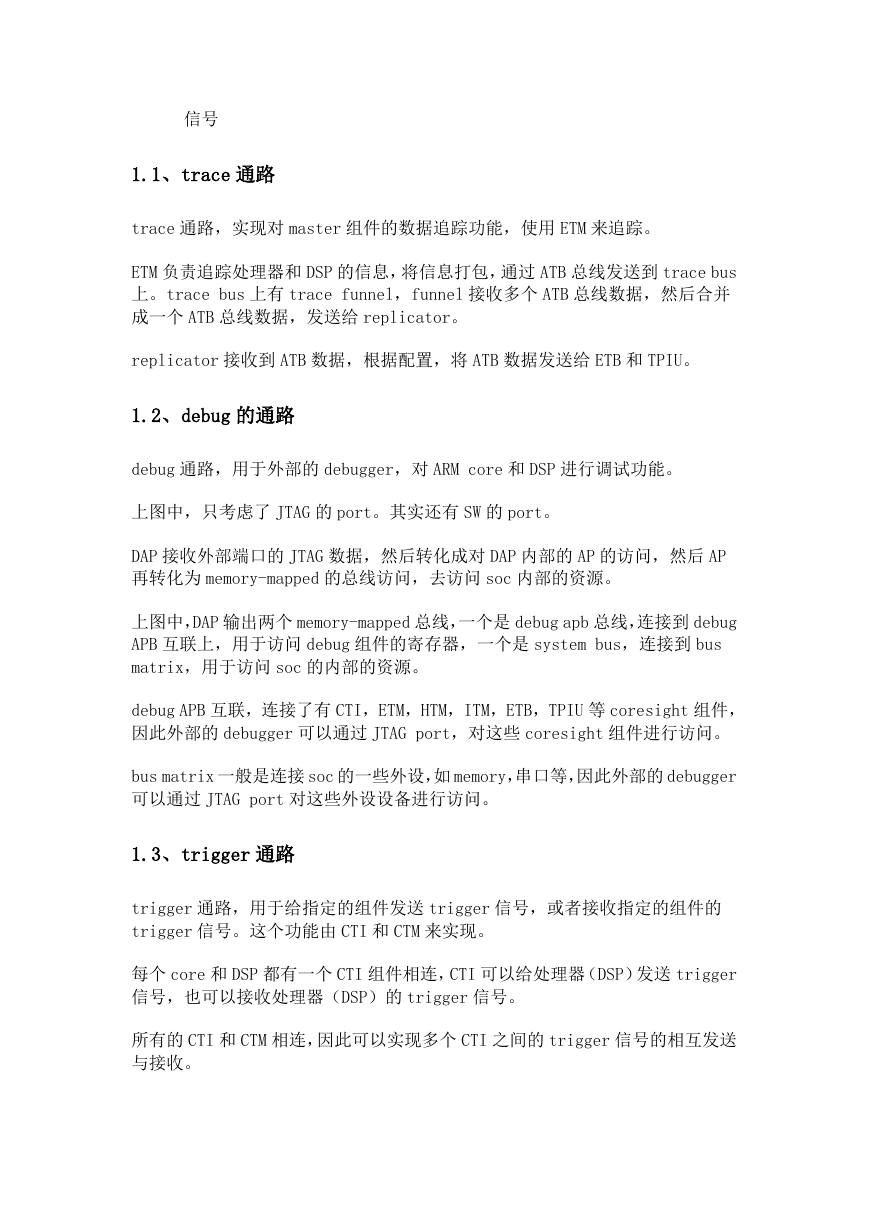

DAP 不属于 coresight 的组件,但是我们会通过 DAP 来对 coresight 的组件进行

访问。

DAP 包括以下:

APB access port(APB-AP)

AHB access port(AHB-AP)

AXI access port(AXI-AP)

JTAG access port(JTAG-AP)

serial wire JTAG debug port(SWJ-DP)

JTAG debug port(JTAG-DP)

ROM table

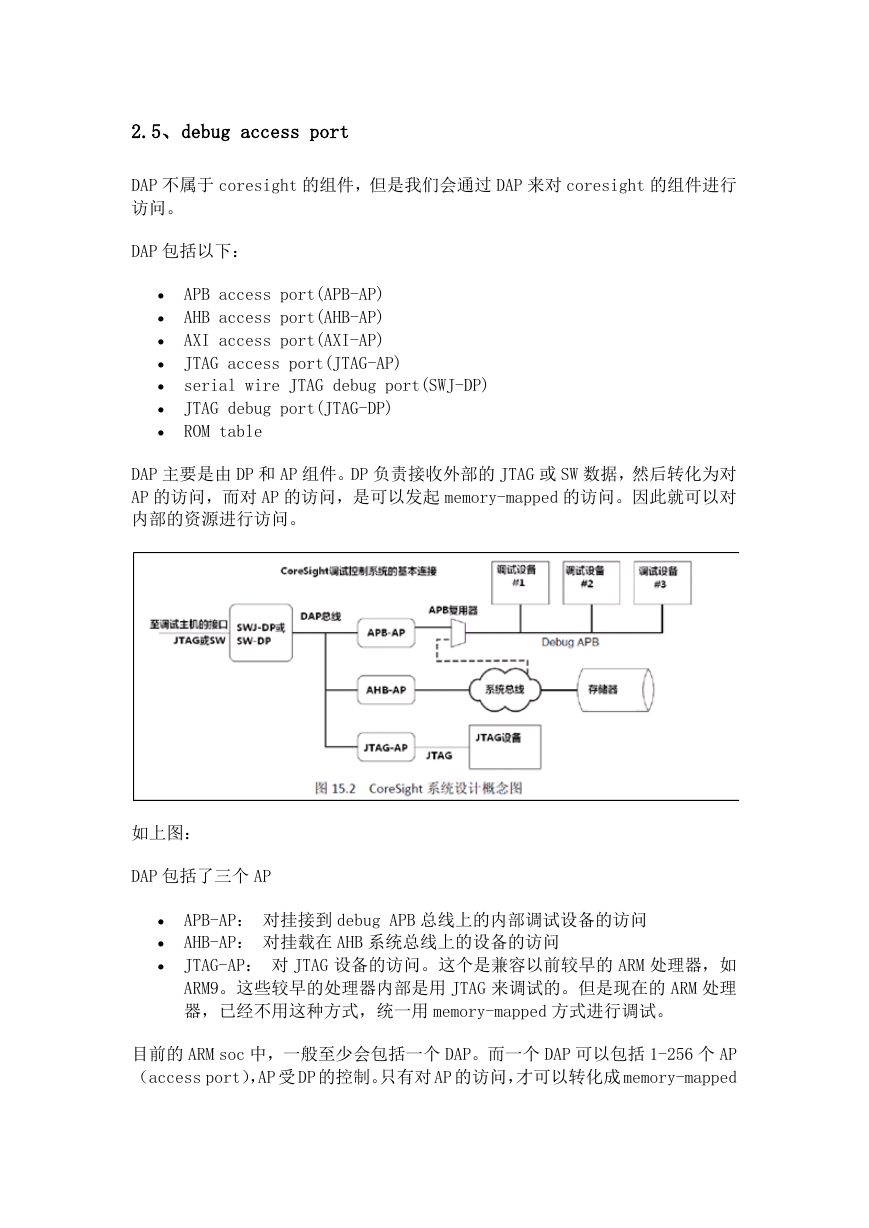

DAP 主要是由 DP 和 AP 组件。DP 负责接收外部的 JTAG 或 SW 数据,然后转化为对

AP 的访问,而对 AP 的访问,是可以发起 memory-mapped 的访问。因此就可以对

内部的资源进行访问。

如上图:

DAP 包括了三个 AP

APB-AP: 对挂接到 debug APB 总线上的内部调试设备的访问

AHB-AP: 对挂载在 AHB 系统总线上的设备的访问

JTAG-AP: 对 JTAG 设备的访问。这个是兼容以前较早的 ARM 处理器,如

ARM9。这些较早的处理器内部是用 JTAG 来调试的。但是现在的 ARM 处理

器,已经不用这种方式,统一用 memory-mapped 方式进行调试。

目前的 ARM soc 中,一般至少会包括一个 DAP。而一个 DAP 可以包括 1-256 个 AP

(access port),AP 受 DP 的控制。只有对 AP 的访问,才可以转化成 memory-mapped

�

总线,对 soc 的内部资源进行访问。

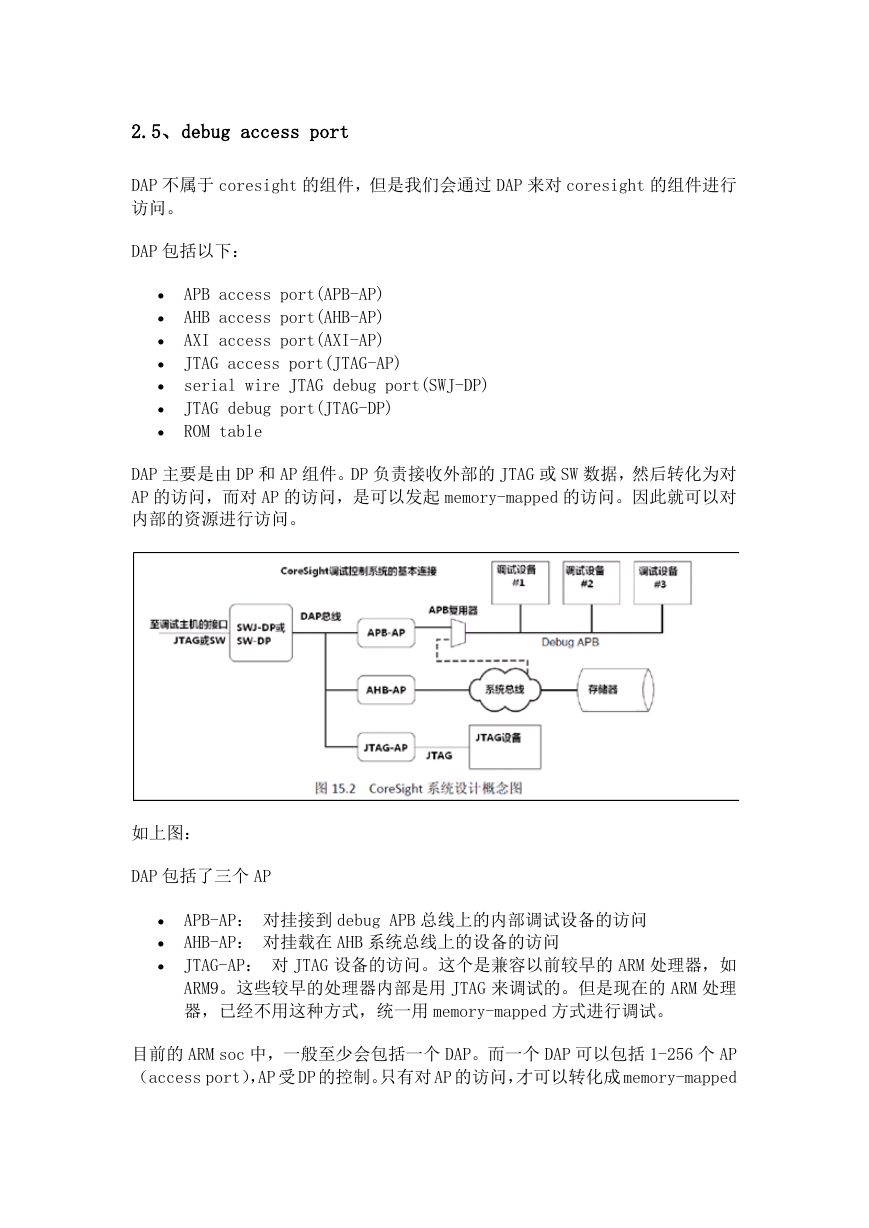

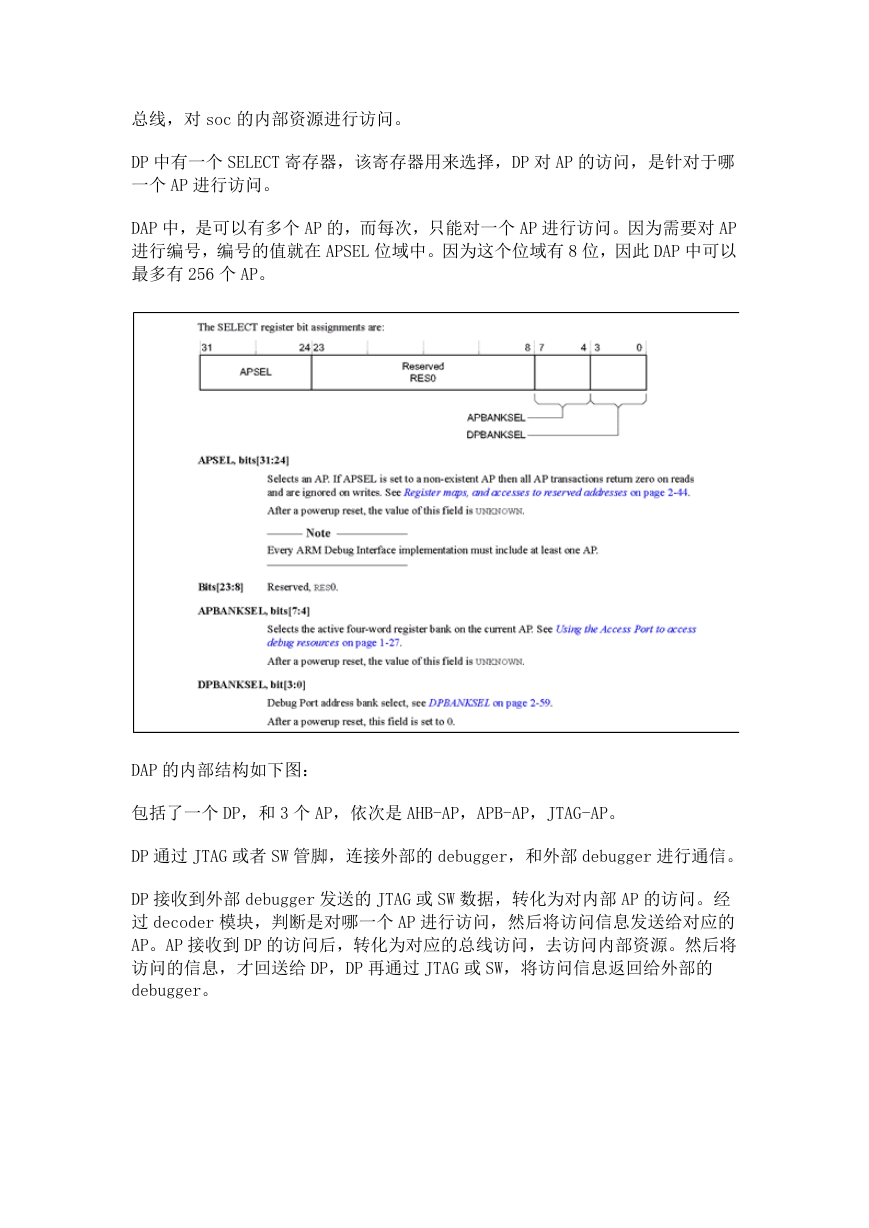

DP 中有一个 SELECT 寄存器,该寄存器用来选择,DP 对 AP 的访问,是针对于哪

一个 AP 进行访问。

DAP 中,是可以有多个 AP 的,而每次,只能对一个 AP 进行访问。因为需要对 AP

进行编号,编号的值就在 APSEL 位域中。因为这个位域有 8 位,因此 DAP 中可以

最多有 256 个 AP。

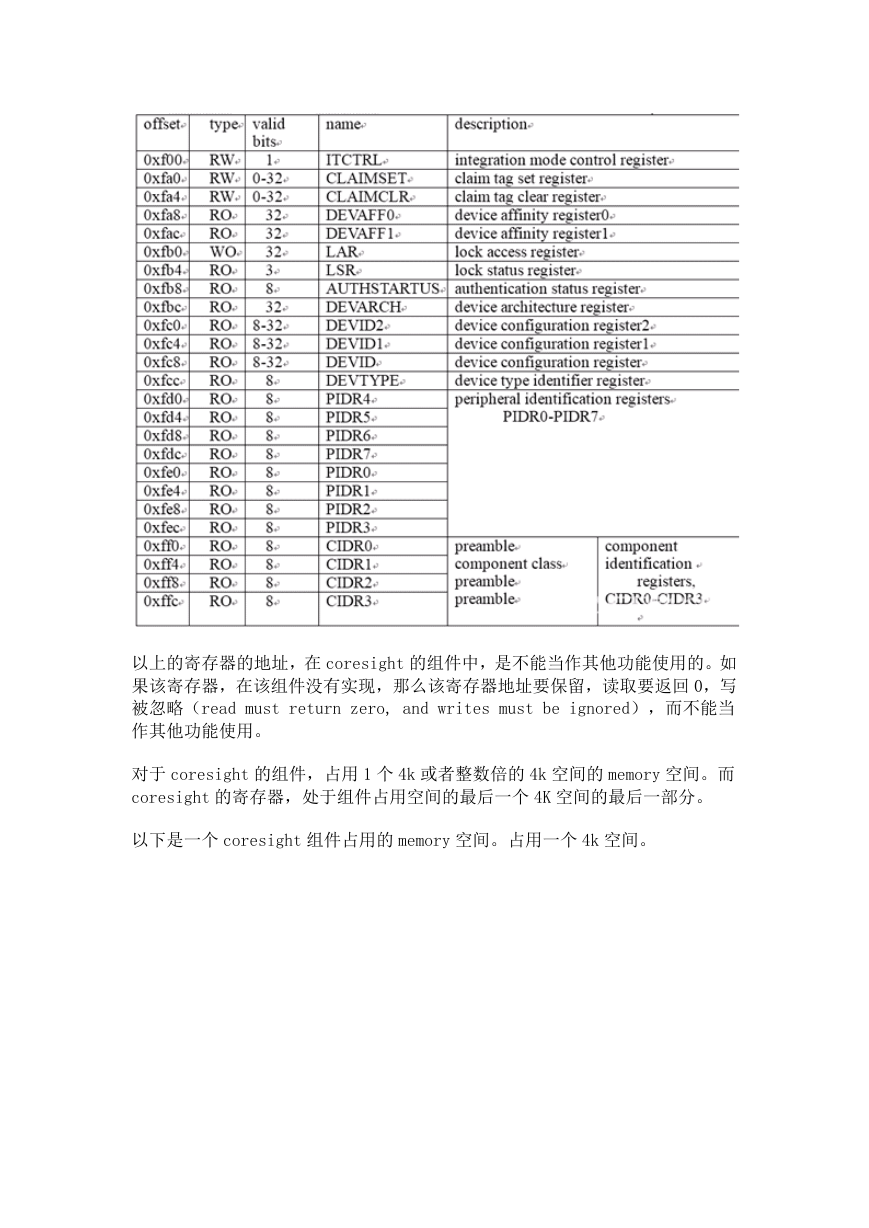

DAP 的内部结构如下图:

包括了一个 DP,和 3 个 AP,依次是 AHB-AP,APB-AP,JTAG-AP。

DP 通过 JTAG 或者 SW 管脚,连接外部的 debugger,和外部 debugger 进行通信。

DP 接收到外部 debugger 发送的 JTAG 或 SW 数据,转化为对内部 AP 的访问。经

过 decoder 模块,判断是对哪一个 AP 进行访问,然后将访问信息发送给对应的

AP。AP 接收到 DP 的访问后,转化为对应的总线访问,去访问内部资源。然后将

访问的信息,才回送给 DP,DP 再通过 JTAG 或 SW,将访问信息返回给外部的

debugger。

�

二、coresight 的寄存器

coresight 对于每个 coresight 组件,规定了一些寄存器,这些寄存器的偏移是

固定的,这些寄存器,是必须存在的。但是有的,可以不实现该寄存器功能。

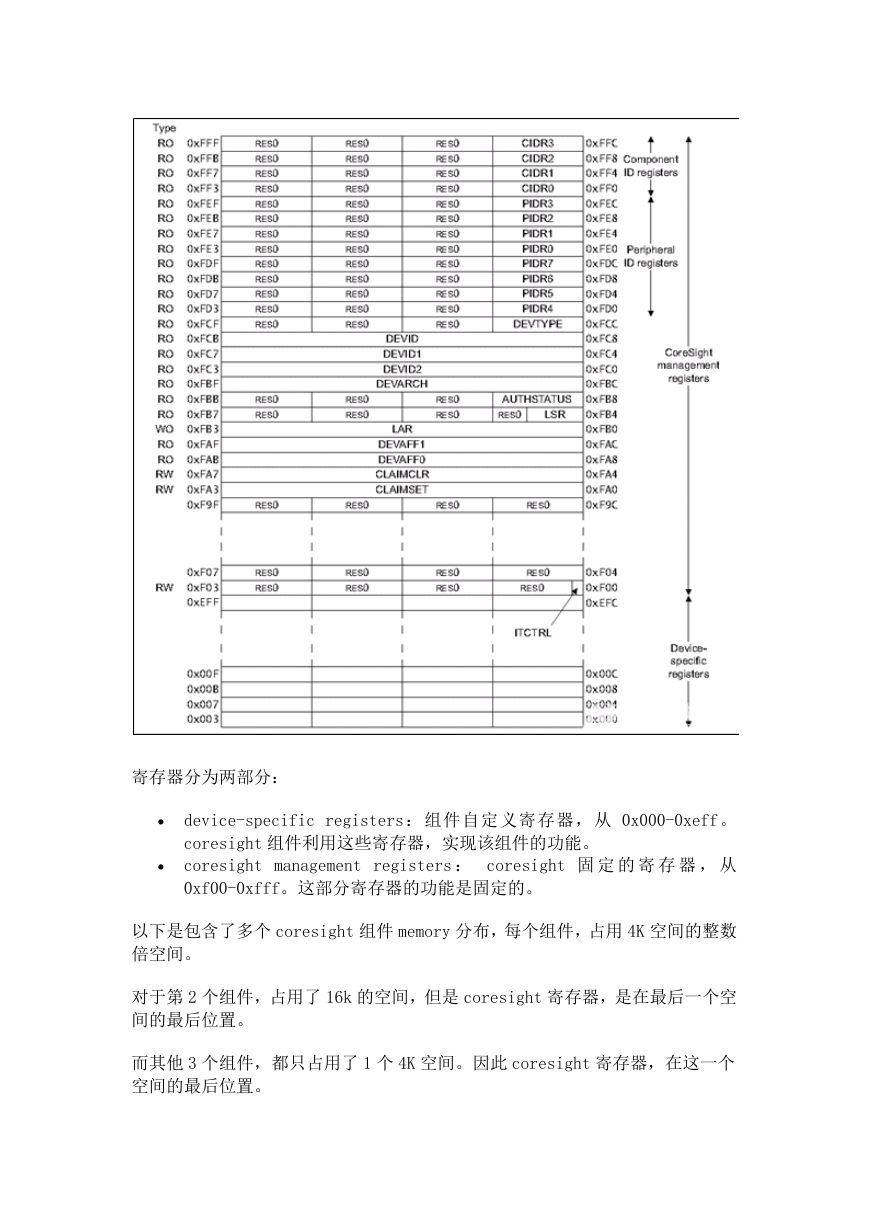

1、寄存器一览

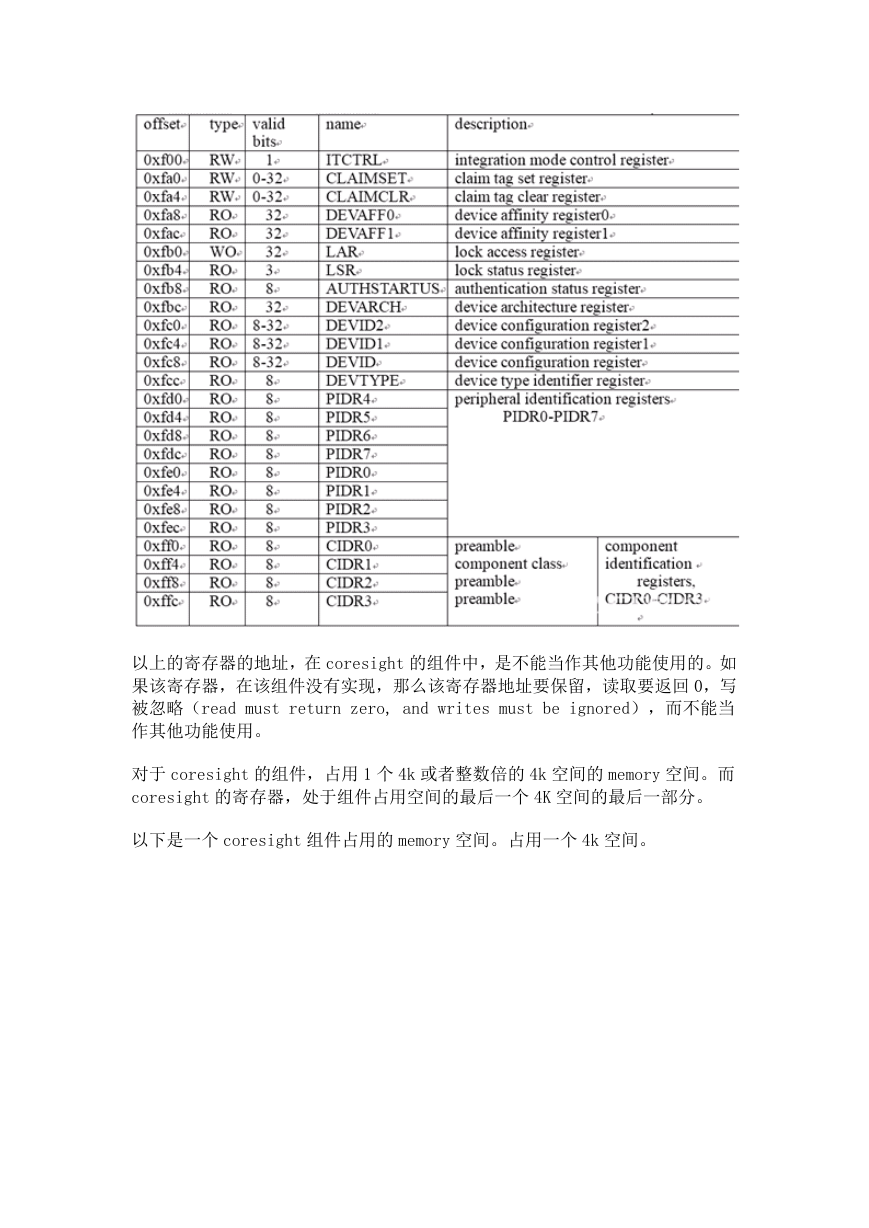

coresight 架构,对于 coresight 的组件,定义了若干个固定的寄存器。第一个

寄存器的偏移从 0xf00 开始,直到 0xffc。以下是寄存器列表

�

以上的寄存器的地址,在 coresight 的组件中,是不能当作其他功能使用的。如

果该寄存器,在该组件没有实现,那么该寄存器地址要保留,读取要返回 0,写

被忽略(read must return zero, and writes must be ignored),而不能当

作其他功能使用。

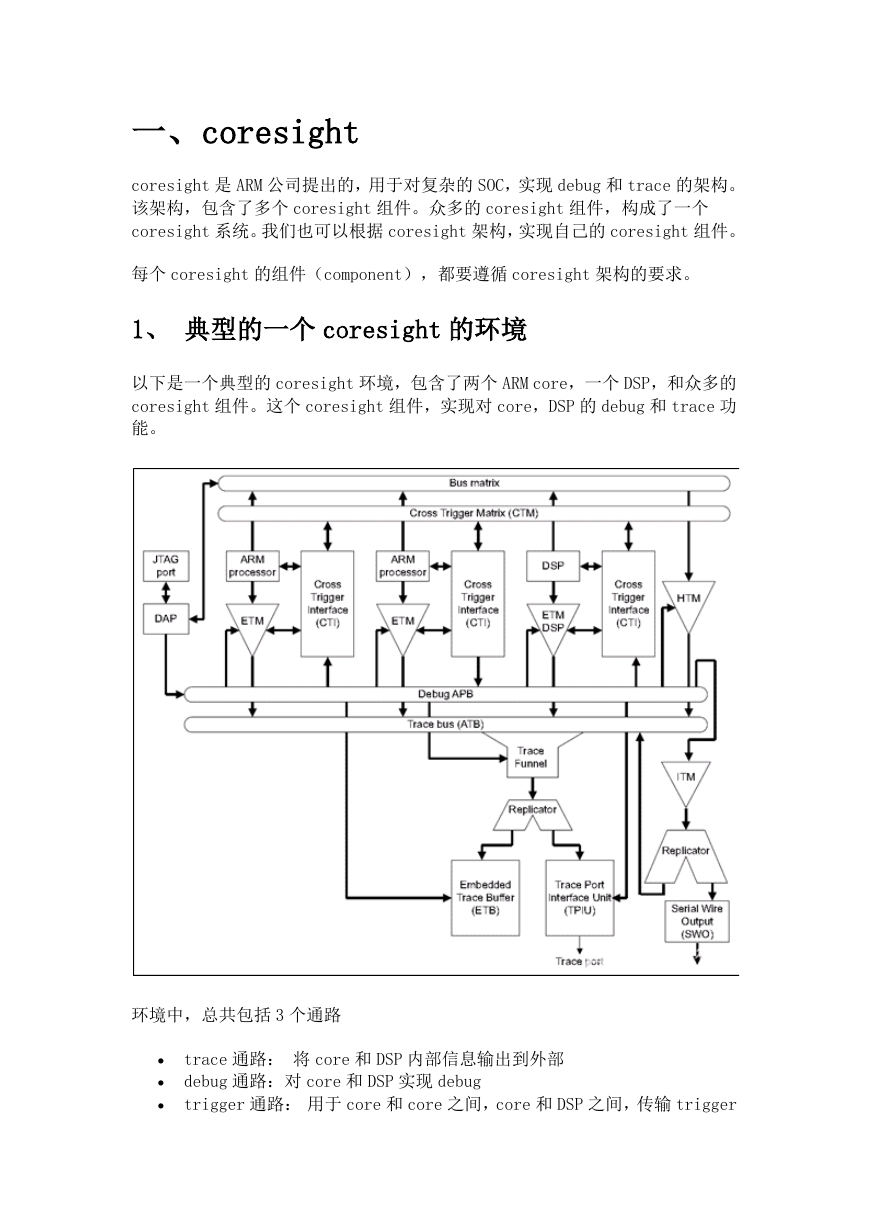

对于 coresight 的组件,占用 1 个 4k 或者整数倍的 4k 空间的 memory 空间。而

coresight 的寄存器,处于组件占用空间的最后一个 4K 空间的最后一部分。

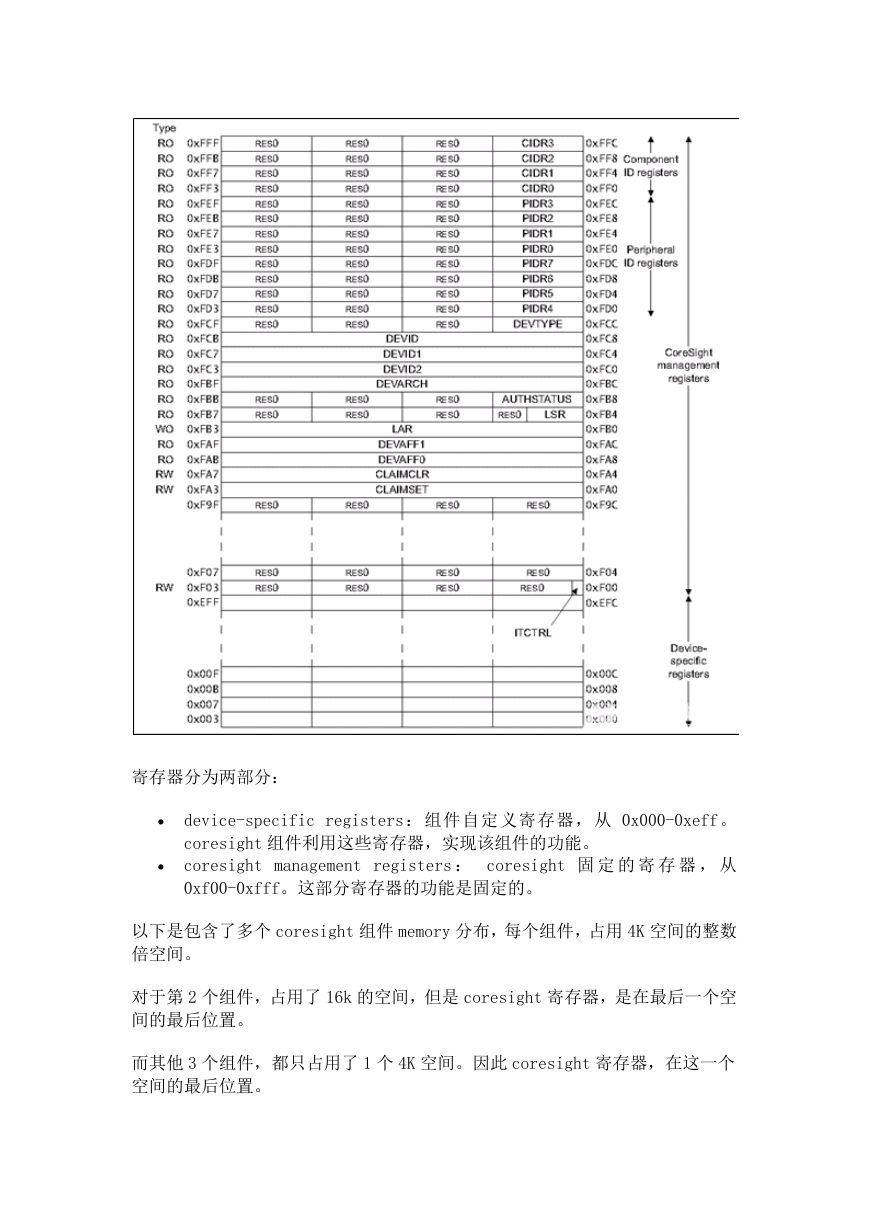

以下是一个 coresight 组件占用的 memory 空间。占用一个 4k 空间。

�

寄存器分为两部分:

device-specific registers:组件自定义寄存器,从 0x000-0xeff。

coresight 组件利用这些寄存器,实现该组件的功能。

coresight management registers : coresight 固 定 的 寄 存 器 , 从

0xf00-0xfff。这部分寄存器的功能是固定的。

以下是包含了多个 coresight 组件 memory 分布,每个组件,占用 4K 空间的整数

倍空间。

对于第 2 个组件,占用了 16k 的空间,但是 coresight 寄存器,是在最后一个空

间的最后位置。

而其他 3 个组件,都只占用了 1 个 4K 空间。因此 coresight 寄存器,在这一个

空间的最后位置。

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc