《电子技术应用》2018年第44卷第9期0引言边缘检测是图像特征提取、目标识别的基础,图像边缘提取的好坏直接影响后续处理的难易度和准确度。在众多边缘提取算法中,Canny边缘提取算法由于其良好的检测效果在图像处理中得到广泛应用。而现阶段的工业视觉检测中,图像处理多为PC平台或者ARM平台,在这些平台下,Canny边缘检测由于计算量大、耗时长,对平台本身性能要求也很高。FPGA凭借高速并行性的特性,在进行图像处理时能很好地保证系统的实时性,因此越来越多开发人员使用FPGA进行图像处理[1-3]。但在现有的文献中,有些受FPGA的历史功能设计局限,过多地关注FPGA底层设计,有些采用中值滤波、改进高斯滤波模板进行Canny边缘检测,设计周期较长,硬件加速效果不明显。武汉科技大学彭习武等采用了Xilinx公司的VivadoHLS(高层次综合)实现改进的Sobel边缘检测[4],取得了较好的实时检测效果,但需选择不同的结构元素对不同的目标图像进行膨胀腐蚀,算法占用硬件资源较多。本文采用VivadoHLS实现Canny边缘检测硬件加速实现方法,研究通用性好、设计周期短、硬件资源消耗少的FPGA加速算法。1Canny算法基本原理Canny边缘检测[5]算法是CANNYJ于1986年提出的,算法目标是在图像中找到最佳边缘。其主要步骤为:(1)图像高斯滤波:对原始图像进行高斯滤波,降低输入图像中的噪声对后续图像处理的干扰,有效提升算法抗噪能力。基于VivadoHLS的Canny算法实时加速设计谭检成1,2,吴定祥2,3,李明鑫1,2,唐立军1,2(1.长沙理工大学物理与电子科学学院,湖南长沙410114;2.近地空间电磁环境监测与建模湖南省普通高校重点实验室,湖南长沙410114;3.长沙亿旭智能科技有限公司,湖南长沙410004)摘要:针对Canny边缘检测算法在实时图像处理过程中运算耗时长、数据运算量大的缺点,研究了利用VivadoHLS实现Canny边缘检测算法的硬件加速方法。该方法由FPGA的逻辑资源生成算法对应的RTL级硬件电路,实现算法硬件加速。实验结果表明,该方法能快速实时检测图像边缘,有效降低FPGA设计图像算法的难度,可以应用到实时视频图像处理中。关键词:图像处理;VivadoHLS;边缘检测;硬件加速中图分类号:TN911.73文献标识码:ADOI:10.16157/j.issn.0258-7998.180429中文引用格式:谭检成,吴定祥,李明鑫,等.基于VivadoHLS的Canny算法实时加速设计[J].电子技术应用,2018,44(9):59-62,66.英文引用格式:TanJiancheng,WuDingxiang,LiMingxin,etal.Real-timeaccelerationdesignofCannyalgorithmbasedonVivadoHLS[J].ApplicationofElectronicTechnique,2018,44(9):59-62,66.Real-timeaccelerationdesignofCannyalgorithmbasedonVivadoHLSTanJiancheng1,2,WuDingxiang2,3,LiMingxin1,2,TangLijun1,2(1.SchoolofPhysicsandElectronicSciences,ChangshaUniversityofScience&Technology,Changsha410114,China;2.HunanProvinceHigherEducationKeyLaboratoryofModelingandMonitoringontheNear-EarthElectromagneticEnvironments,Changsha410114,China;3.ChangshaBillionSetIntelligentTechnologyCo.,Ltd.,Changsha410004,China)Abstract:OntheshortcomingsofCannyedgedetectionalgorithminthereal-timeimageprocessingtime-consumingandlargeamountofdataforcomputation,thehardwareaccelerationmethodofCannyedgedetectionalgorithmusingVivadoHLSisproposed.Themethod,implementedhardwareacceleration,generatestheRTLlevelhardwarecircuitcorrespondingtothealgorithmoftheFP-GAlogicresources.TheresultsshowthatthemethodcanquicklydetecttheedgeoftheimageandeffectivelyreducethedifficultyofFPGAdesignimagealgorithm,whichcanbeappliedtothereal-timevideoimageprocessing.Keywords:imageprocessing;VivadoHLS;edgedetection;hardwareacceleration嵌入式技术EmbeddedTechnology59�

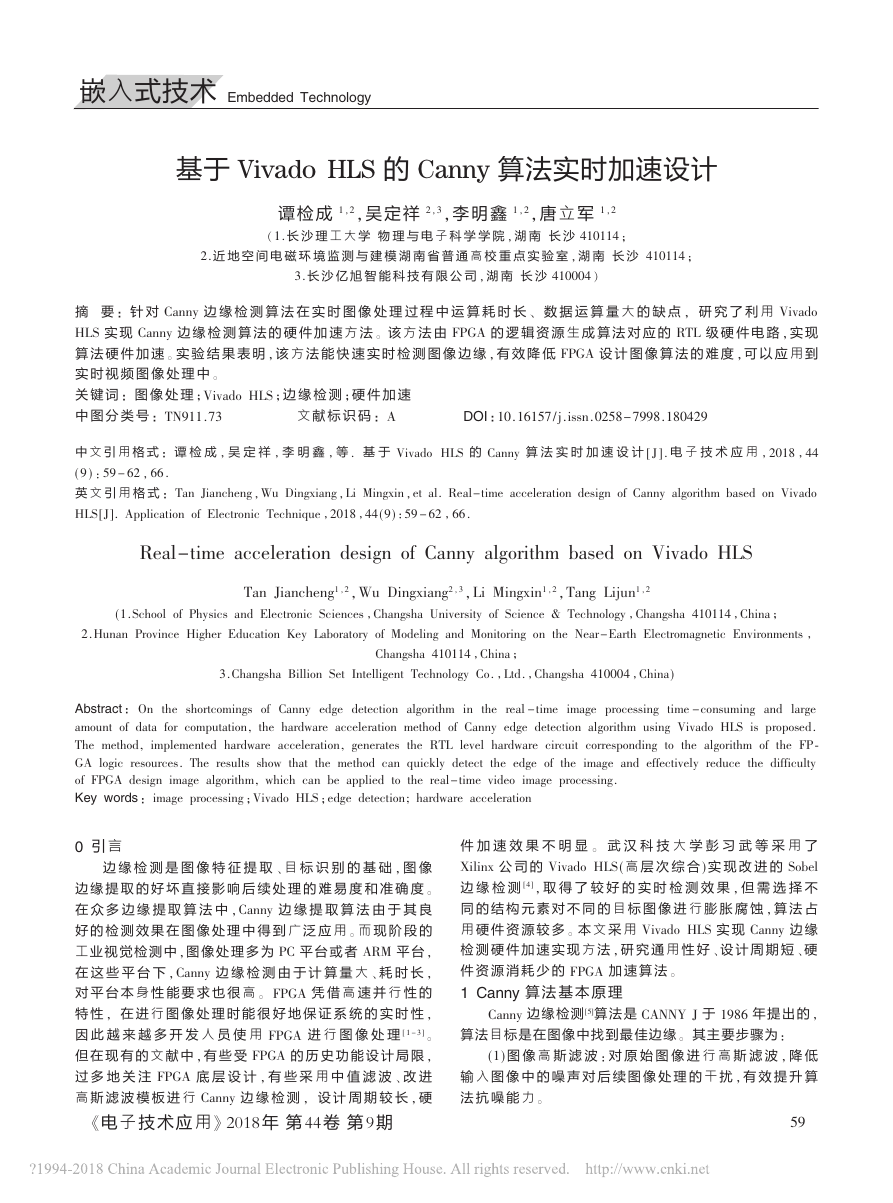

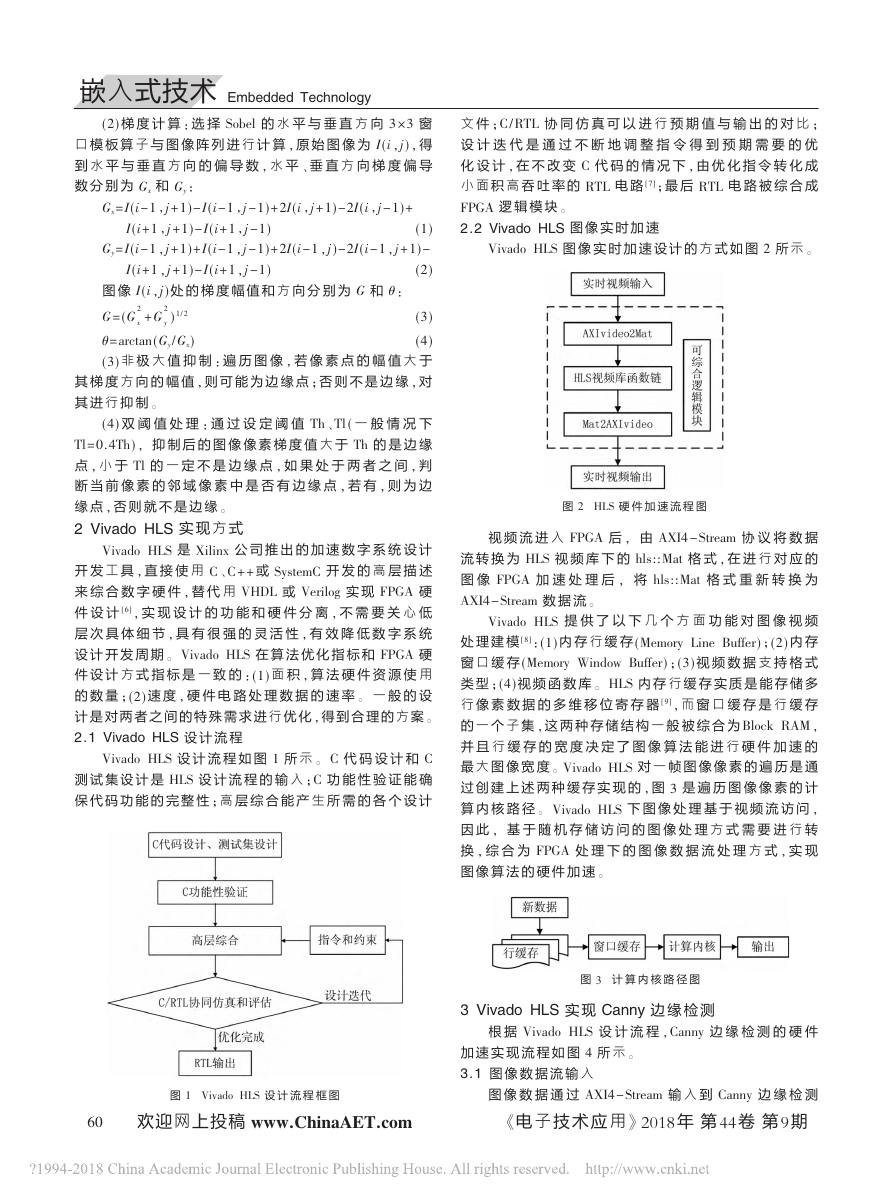

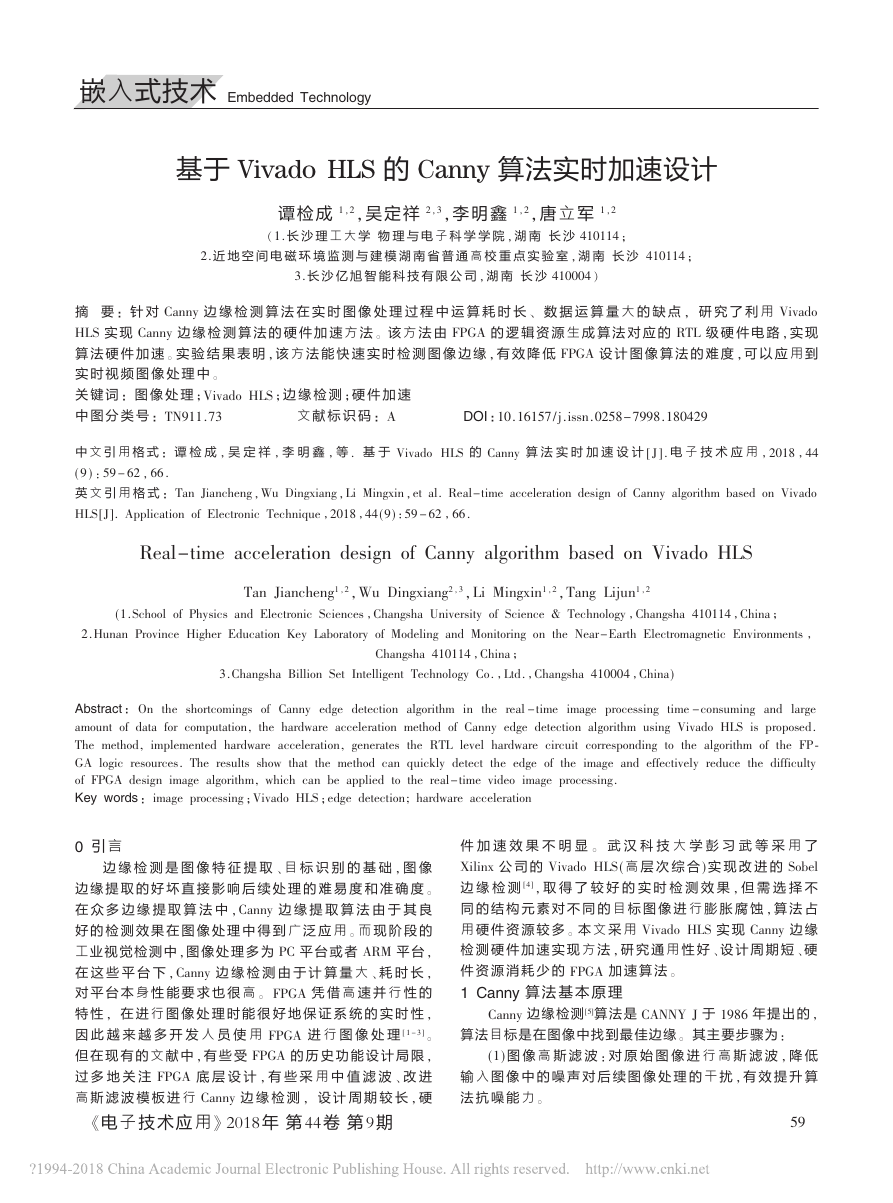

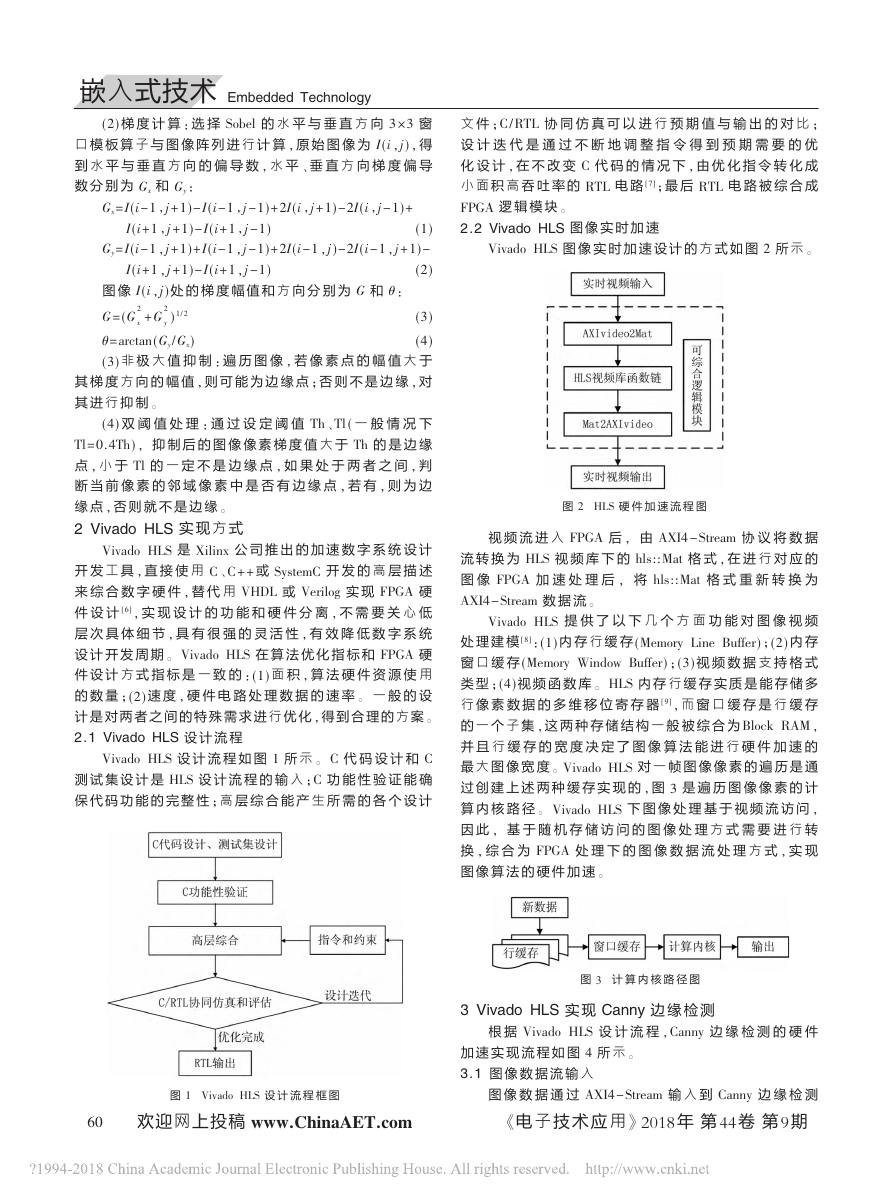

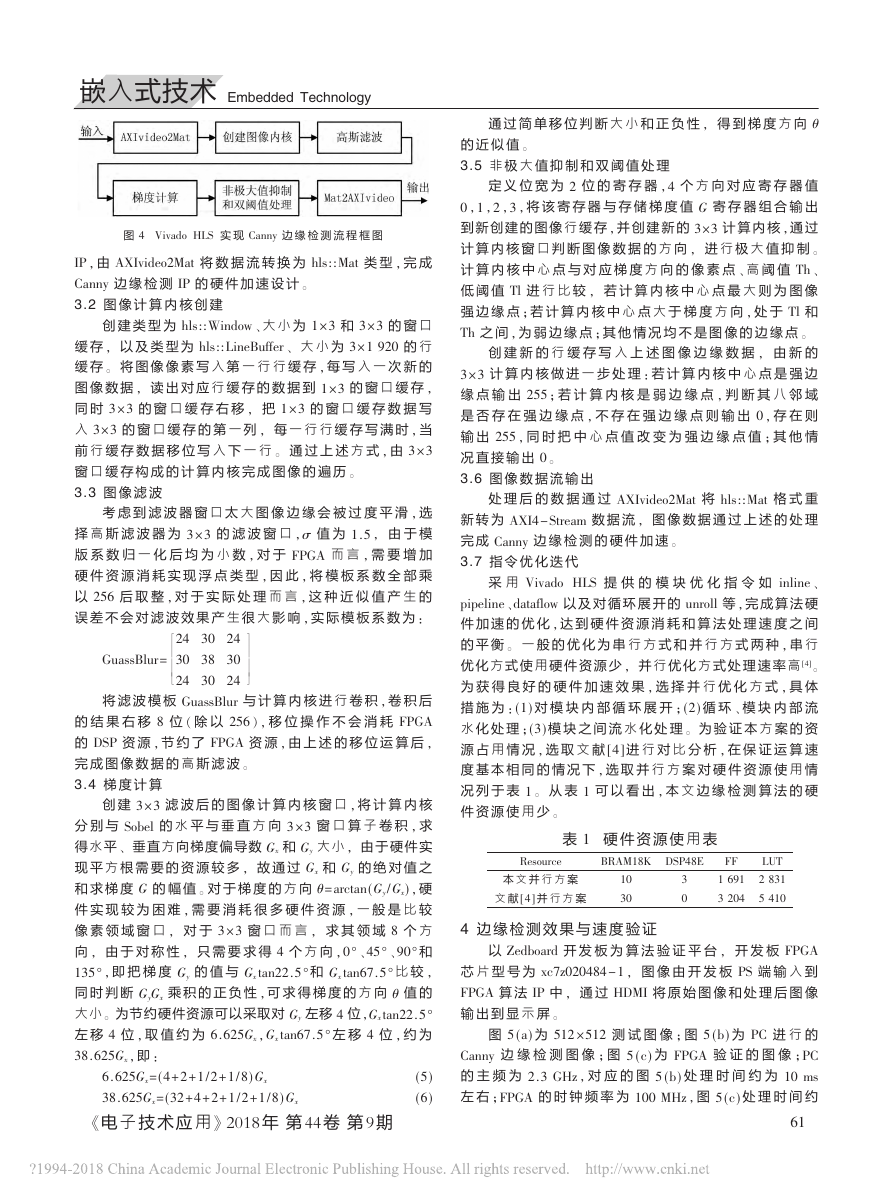

《电子技术应用》2018年第44卷第9期欢迎网上投稿www.ChinaAET.com(2)梯度计算:选择Sobel的水平与垂直方向3×3窗口模板算子与图像阵列进行计算,原始图像为I(i,j),得到水平与垂直方向的偏导数,水平、垂直方向梯度偏导数分别为Gx和Gy:Gx=I(i-1,j+1)-I(i-1,j-1)+2I(i,j+1)-2I(i,j-1)+I(i+1,j+1)-I(i+1,j-1)(1)Gy=I(i-1,j+1)+I(i-1,j-1)+2I(i-1,j)-2I(i-1,j+1)-I(i+1,j+1)-I(i+1,j-1)(2)图像I(i,j)处的梯度幅值和方向分别为G和θ:G=(G2x+G2y)1/2(3)θ=arctan(Gy/Gx)(4)(3)非极大值抑制:遍历图像,若像素点的幅值大于其梯度方向的幅值,则可能为边缘点;否则不是边缘,对其进行抑制。(4)双阈值处理:通过设定阈值Th、Tl(一般情况下Tl=0.4Th),抑制后的图像像素梯度值大于Th的是边缘点,小于Tl的一定不是边缘点,如果处于两者之间,判断当前像素的邻域像素中是否有边缘点,若有,则为边缘点,否则就不是边缘。2VivadoHLS实现方式VivadoHLS是Xilinx公司推出的加速数字系统设计开发工具,直接使用C、C++或SystemC开发的高层描述来综合数字硬件,替代用VHDL或Verilog实现FPGA硬件设计[6],实现设计的功能和硬件分离,不需要关心低层次具体细节,具有很强的灵活性,有效降低数字系统设计开发周期。VivadoHLS在算法优化指标和FPGA硬件设计方式指标是一致的:(1)面积,算法硬件资源使用的数量;(2)速度,硬件电路处理数据的速率。一般的设计是对两者之间的特殊需求进行优化,得到合理的方案。2.1VivadoHLS设计流程VivadoHLS设计流程如图1所示。C代码设计和C测试集设计是HLS设计流程的输入;C功能性验证能确保代码功能的完整性;高层综合能产生所需的各个设计文件;C/RTL协同仿真可以进行预期值与输出的对比;设计迭代是通过不断地调整指令得到预期需要的优化设计,在不改变C代码的情况下,由优化指令转化成小面积高吞吐率的RTL电路[7];最后RTL电路被综合成FPGA逻辑模块。2.2VivadoHLS图像实时加速VivadoHLS图像实时加速设计的方式如图2所示。视频流进入FPGA后,由AXI4-Stream协议将数据流转换为HLS视频库下的hls::Mat格式,在进行对应的图像FPGA加速处理后,将hls::Mat格式重新转换为AXI4-Stream数据流。VivadoHLS提供了以下几个方面功能对图像视频处理建模[8]:(1)内存行缓存(MemoryLineBuffer);(2)内存窗口缓存(MemoryWindowBuffer);(3)视频数据支持格式类型;(4)视频函数库。HLS内存行缓存实质是能存储多行像素数据的多维移位寄存器[9],而窗口缓存是行缓存的一个子集,这两种存储结构一般被综合为BlockRAM,并且行缓存的宽度决定了图像算法能进行硬件加速的最大图像宽度。VivadoHLS对一帧图像像素的遍历是通过创建上述两种缓存实现的,图3是遍历图像像素的计算内核路径。VivadoHLS下图像处理基于视频流访问,因此,基于随机存储访问的图像处理方式需要进行转换,综合为FPGA处理下的图像数据流处理方式,实现图像算法的硬件加速。3VivadoHLS实现Canny边缘检测根据VivadoHLS设计流程,Canny边缘检测的硬件加速实现流程如图4所示。3.1图像数据流输入图像数据通过AXI4-Stream输入到Canny边缘检测图1VivadoHLS设计流程框图图2HLS硬件加速流程图图3计算内核路径图嵌入式技术EmbeddedTechnology60�

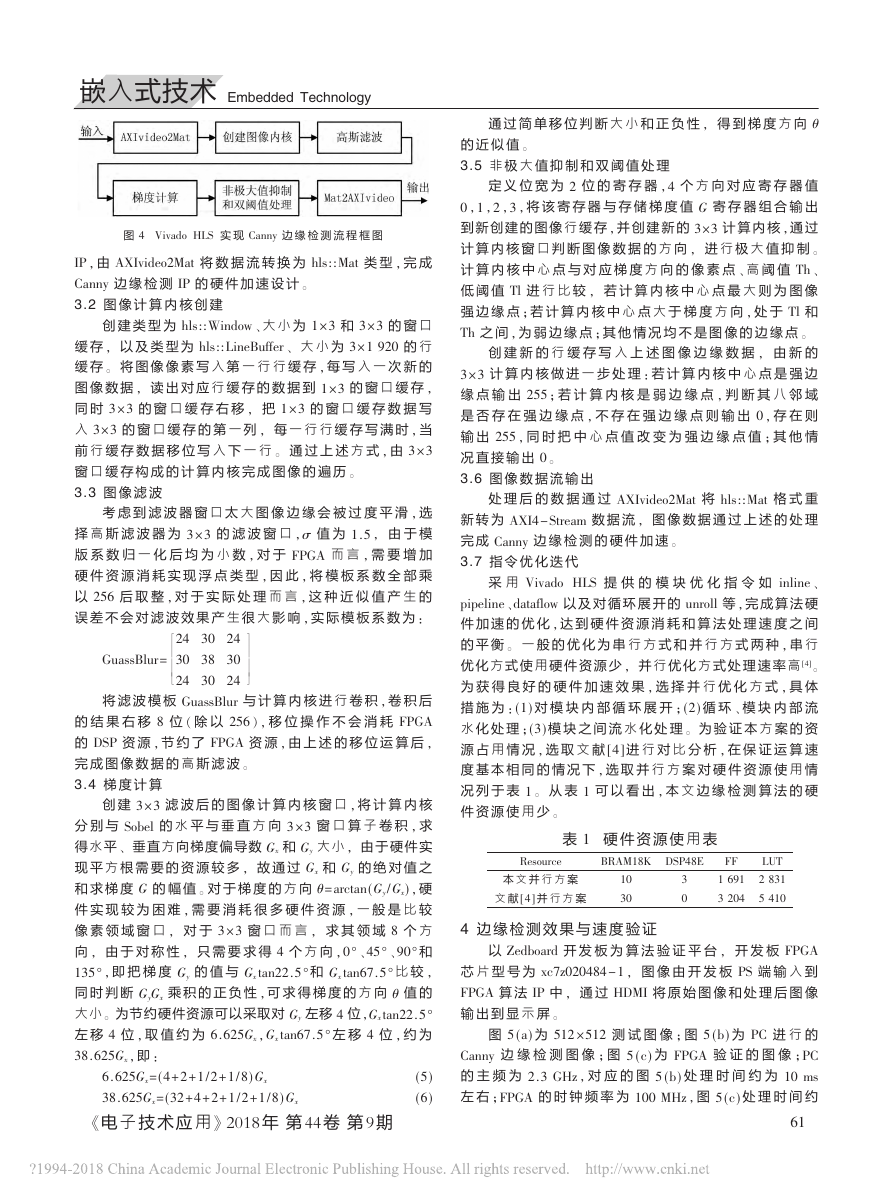

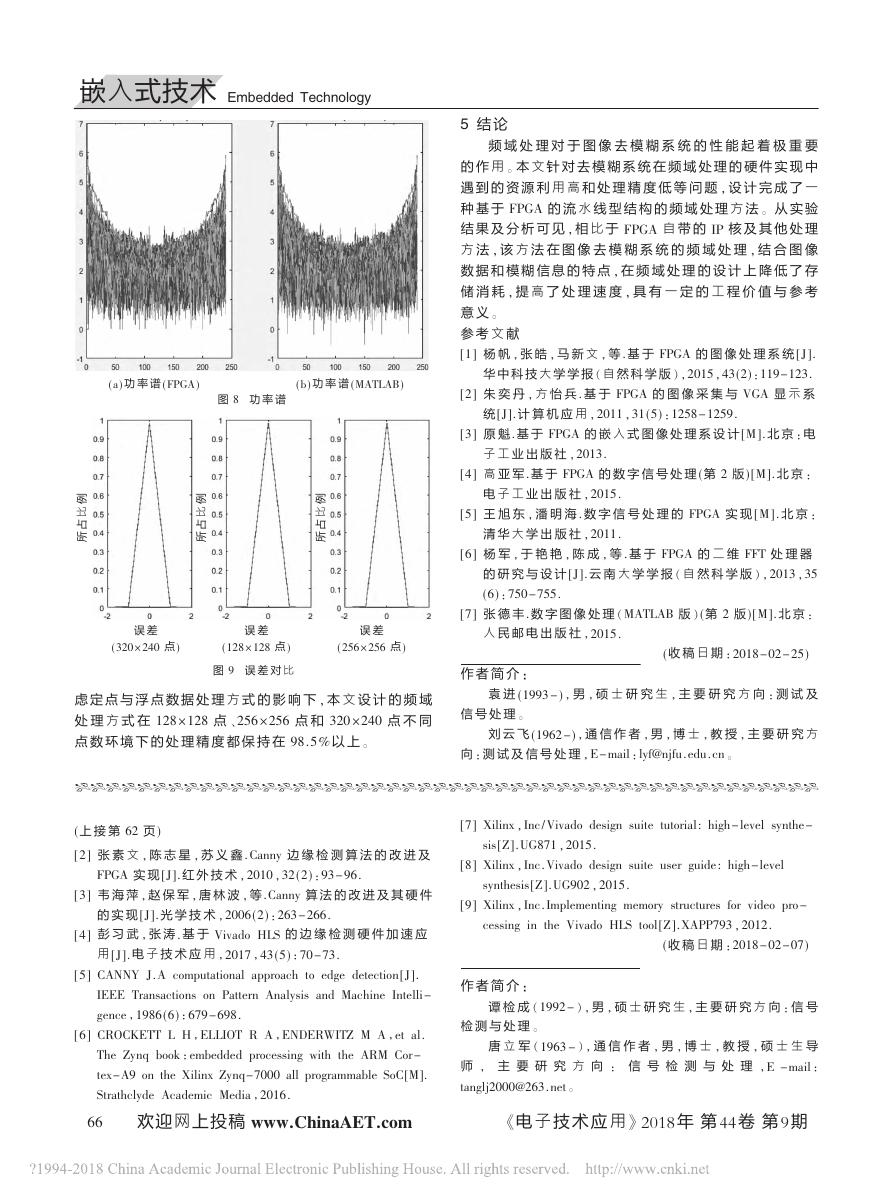

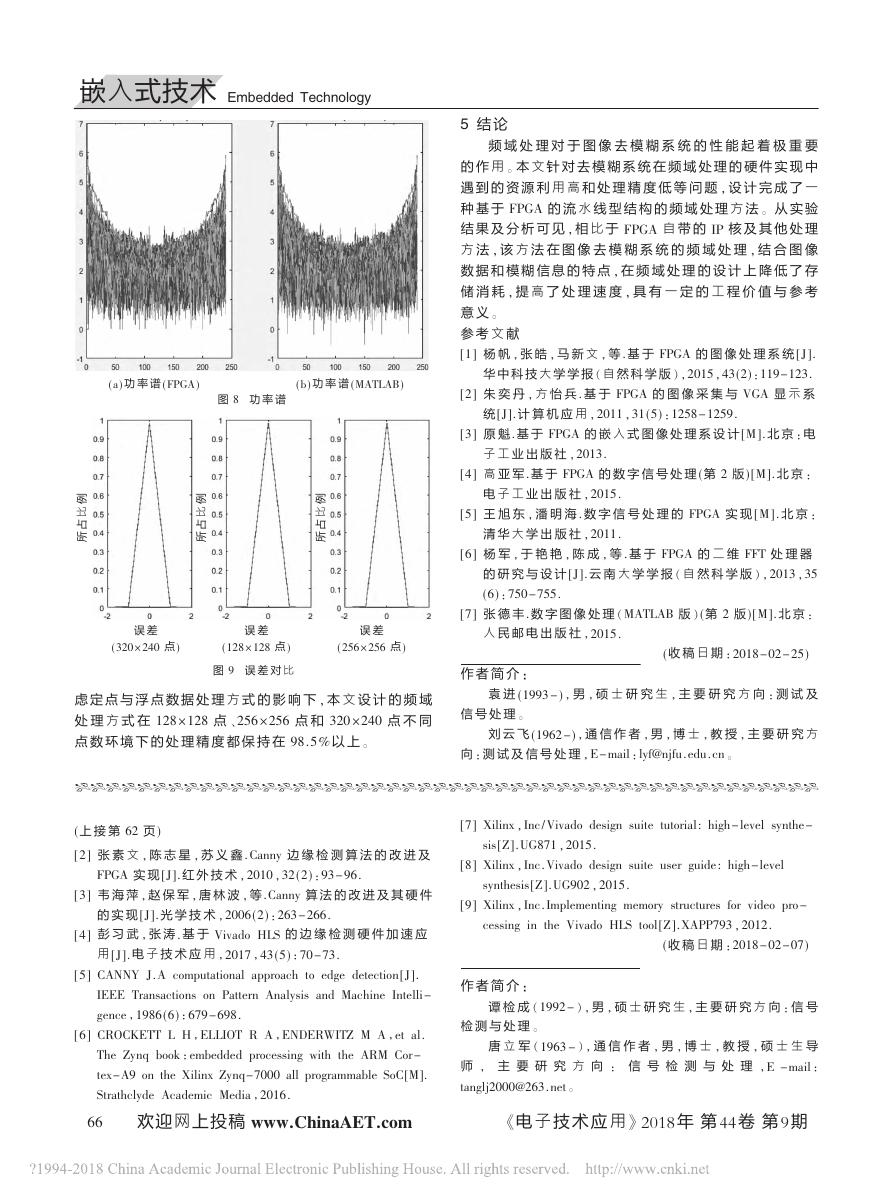

《电子技术应用》2018年第44卷第9期IP,由AXIvideo2Mat将数据流转换为hls::Mat类型,完成Canny边缘检测IP的硬件加速设计。3.2图像计算内核创建创建类型为hls::Window、大小为1×3和3×3的窗口缓存,以及类型为hls::LineBuffer、大小为3×1920的行缓存。将图像像素写入第一行行缓存,每写入一次新的图像数据,读出对应行缓存的数据到1×3的窗口缓存,同时3×3的窗口缓存右移,把1×3的窗口缓存数据写入3×3的窗口缓存的第一列,每一行行缓存写满时,当前行缓存数据移位写入下一行。通过上述方式,由3×3窗口缓存构成的计算内核完成图像的遍历。3.3图像滤波考虑到滤波器窗口太大图像边缘会被过度平滑,选择高斯滤波器为3×3的滤波窗口,σ值为1.5,由于模版系数归一化后均为小数,对于FPGA而言,需要增加硬件资源消耗实现浮点类型,因此,将模板系数全部乘以256后取整,对于实际处理而言,这种近似值产生的误差不会对滤波效果产生很大影响,实际模板系数为:GuassBlur=24302430383024302!"""""""#$%%%%%%%&4将滤波模板GuassBlur与计算内核进行卷积,卷积后的结果右移8位(除以256),移位操作不会消耗FPGA的DSP资源,节约了FPGA资源,由上述的移位运算后,完成图像数据的高斯滤波。3.4梯度计算创建3×3滤波后的图像计算内核窗口,将计算内核分别与Sobel的水平与垂直方向3×3窗口算子卷积,求得水平、垂直方向梯度偏导数Gx和Gy大小,由于硬件实现平方根需要的资源较多,故通过Gx和Gy的绝对值之和求梯度G的幅值。对于梯度的方向θ=arctan(Gy/Gx),硬件实现较为困难,需要消耗很多硬件资源,一般是比较像素领域窗口,对于3×3窗口而言,求其领域8个方向,由于对称性,只需要求得4个方向,0°、45°、90°和135°,即把梯度Gy的值与Gxtan22.5°和Gxtan67.5°比较,同时判断GyGx乘积的正负性,可求得梯度的方向θ值的大小。为节约硬件资源可以采取对Gy左移4位,Gxtan22.5°左移4位,取值约为6.625Gx,Gxtan67.5°左移4位,约为38.625Gx,即:6.625Gx=(4+2+1/2+1/8)Gx(5)38.625Gx=(32+4+2+1/2+1/8)Gx(6)通过简单移位判断大小和正负性,得到梯度方向θ的近似值。3.5非极大值抑制和双阈值处理定义位宽为2位的寄存器,4个方向对应寄存器值0,1,2,3,将该寄存器与存储梯度值G寄存器组合输出到新创建的图像行缓存,并创建新的3×3计算内核,通过计算内核窗口判断图像数据的方向,进行极大值抑制。计算内核中心点与对应梯度方向的像素点、高阈值Th、低阈值Tl进行比较,若计算内核中心点最大则为图像强边缘点;若计算内核中心点大于梯度方向,处于Tl和Th之间,为弱边缘点;其他情况均不是图像的边缘点。创建新的行缓存写入上述图像边缘数据,由新的3×3计算内核做进一步处理:若计算内核中心点是强边缘点输出255;若计算内核是弱边缘点,判断其八邻域是否存在强边缘点,不存在强边缘点则输出0,存在则输出255,同时把中心点值改变为强边缘点值;其他情况直接输出0。3.6图像数据流输出处理后的数据通过AXIvideo2Mat将hls::Mat格式重新转为AXI4-Stream数据流,图像数据通过上述的处理完成Canny边缘检测的硬件加速。3.7指令优化迭代采用VivadoHLS提供的模块优化指令如inline、pipeline、dataflow以及对循环展开的unroll等,完成算法硬件加速的优化,达到硬件资源消耗和算法处理速度之间的平衡。一般的优化为串行方式和并行方式两种,串行优化方式使用硬件资源少,并行优化方式处理速率高[4]。为获得良好的硬件加速效果,选择并行优化方式,具体措施为:(1)对模块内部循环展开;(2)循环、模块内部流水化处理;(3)模块之间流水化处理。为验证本方案的资源占用情况,选取文献[4]进行对比分析,在保证运算速度基本相同的情况下,选取并行方案对硬件资源使用情况列于表1。从表1可以看出,本文边缘检测算法的硬件资源使用少。4边缘检测效果与速度验证以Zedboard开发板为算法验证平台,开发板FPGA芯片型号为xc7z020484-1,图像由开发板PS端输入到FPGA算法IP中,通过HDMI将原始图像和处理后图像输出到显示屏。图5(a)为512×512测试图像;图5(b)为PC进行的Canny边缘检测图像;图5(c)为FPGA验证的图像;PC的主频为2.3GHz,对应的图5(b)处理时间约为10ms左右;FPGA的时钟频率为100MHz,图5(c)处理时间约图4VivadoHLS实现Canny边缘检测流程框图表1硬件资源使用表Resource本文并行方案文献[4]并行方案BRAM18K1030DSP48E30FF16913204LUT28315410嵌入式技术EmbeddedTechnology61�

《电子技术应用》2018年第44卷第9期欢迎网上投稿www.ChinaAET.com对于短约束长度的卷积码,如(2,1,3)、(2,1,5)采用全寄存器交换资源消耗不会增加太多,但译码延时比交换长度为3时又减少50%,更具实用价值。而对于长约束长度的卷积码,如(2,1,7)、(2,1,9)采用全寄存器交换资源消耗增加太多,选用寄存器交换长度为4或6时较合适,此时的时延与完全寄存器交换相近,但消耗的逻辑资源与简单回溯模式相当,存储器单元比简单回溯小很多(小50%或62.5%),虽然在本文中的FPGA下实现时消耗的存储块数更多,但那是由于CycloneIII的每块存储块比较大(深度大而宽度受限),若采用最小深度为16的小存储块时(比如定制ASIC技术)其优势将明显显现出来。参考文献[1]TRUONGTK,SHIHMT,REEDIS,etal.AVLSIdesignforatrace-backViterbidecoder[J].IEEETransac-tiononCommuications,1992,40(3):616-624.[2]FEYGING,GULAKPG.ArchitecturaltradeoffsforsurvivorsequencememorymanagementinViterbidecoders[J].IEEETransonCommun,1993,41(3):425–429.[3]GOOYJ,LEEH.Twobit-levelpipelinedviterbidecoderforhigh-performanceUWBapplications[C].IEEEInternationalSymposiumonCircuitsandSystems,ISCAS2008,2008:1012-1015.[4]BRUELSN,SICHENEDERE,LOEWM,etal.A2.8Gb/s,32-state,radix-4Viterbidecoderadd-compare-selectunit[C].2004SymposiumonVLSICircuits,2004:170-173.[5]YangMin.DesignoptimizationofFPGAbasedViterbidecoder[C].2011InternationalConferenceonElectricInformationandControlEngineering,2001,5:4129-4131.[6]TangJiuling.DesignandFPGAimplementationofaViterbidecoder:acasestudyusingsystemVerilogandco-simula-tion[C].2009IEEEInternationalSymposiumonSignalProcessingandInformationTechnology(ISSPIT),2009:1-6.[7]AlteraCooperation.ViterbiCompilerv9.1UserGuide[Z].2009.[8]夏宇闻.Verilog数字系统设计教程(第二版)[M].北京:北京航空航天大学出版社,2008.(收稿日期:2017-12-26)作者简介:杨敏(1973-),通信作者,女,硕士,讲师,主要研究方向:移动通信、纠错码,E-mail:yangmin@hust.edu.cn。(上接第58页)注:文献[6]及本文b采用EP3SL50F484C2,本文a采用EP3C10F256C6-:表示不详模式RE长度组合LUTs寄存器存储单元bitM9KfMAX/MHz时延/CLK41642642138322095377619741481848488728438902845-6144061440-110110510161146263232V7V/5V7V/5V表6与其他文献的(2,1,7)全并行译码器性能对比来源文献[6]本文a本文a本文b本文b(下转第66页)为3ms。由图5(c)和图5(b)处理时间的对比可知,图5(c)算法处理时间不到图5(b)的1/3,说明加速效果明显。从文献[1]中可知,在相同系统时钟下处理512×512的图像,时间约为20ms,远小于图5(c)的处理速度。因此,VivadoHLS实现的Canny边缘检测算法能在较复杂的情况下检测到图像边缘,且运算速度快。5结论由VivadoHLS进行FPGA图像算法硬件加速设计方式,既避免了传统FPGA图像算法开发中过于关注底层细节,又能有效地缩短开发周期。通过仿真与FPGA验证,采用VivadoHLS实现的Canny边缘检测算法能在较复杂的情况下检测到图像边缘,运算速度快,资源消耗少,可以应用到实时视觉检测中。参考文献[1]肖国尧,曲仕茹.基于FPGA视频图像的Canny算法加速器设计[J].现代电子技术,2012(9):91-94.图5算法对比图(a)原始图像(b)PC下Canny边缘检测结果(c)开发板硬件加速结果!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!嵌入式技术EmbeddedTechnology62�

《电子技术应用》2018年第44卷第9期欢迎网上投稿www.ChinaAET.com[2]张素文,陈志星,苏义鑫.Canny边缘检测算法的改进及FPGA实现[J].红外技术,2010,32(2):93-96.[3]韦海萍,赵保军,唐林波,等.Canny算法的改进及其硬件的实现[J].光学技术,2006(2):263-266.[4]彭习武,张涛.基于VivadoHLS的边缘检测硬件加速应用[J].电子技术应用,2017,43(5):70-73.[5]CANNYJ.Acomputationalapproachtoedgedetection[J].IEEETransactionsonPatternAnalysisandMachineIntelli-gence,1986(6):679-698.[6]CROCKETTLH,ELLIOTRA,ENDERWITZMA,etal.TheZynqbook:embeddedprocessingwiththeARMCor-tex-A9ontheXilinxZynq-7000allprogrammableSoC[M].StrathclydeAcademicMedia,2016.[7]Xilinx,Inc/Vivadodesignsuitetutorial:high-levelsynthe-sis[Z].UG871,2015.[8]Xilinx,Inc.Vivadodesignsuiteuserguide:high-levelsynthesis[Z].UG902,2015.[9]Xilinx,Inc.Implementingmemorystructuresforvideopro-cessingintheVivadoHLStool[Z].XAPP793,2012.(收稿日期:2018-02-07)作者简介:谭检成(1992-),男,硕士研究生,主要研究方向:信号检测与处理。唐立军(1963-),通信作者,男,博士,教授,硕士生导师,主要研究方向:信号检测与处理,E-mail:tanglj2000@263.net。(上接第62页)图9误差对比(a)功率谱(FPGA)(b)功率谱(MATLAB)图8功率谱虑定点与浮点数据处理方式的影响下,本文设计的频域处理方式在128×128点、256×256点和320×240点不同点数环境下的处理精度都保持在98.5%以上。5结论频域处理对于图像去模糊系统的性能起着极重要的作用。本文针对去模糊系统在频域处理的硬件实现中遇到的资源利用高和处理精度低等问题,设计完成了一种基于FPGA的流水线型结构的频域处理方法。从实验结果及分析可见,相比于FPGA自带的IP核及其他处理方法,该方法在图像去模糊系统的频域处理,结合图像数据和模糊信息的特点,在频域处理的设计上降低了存储消耗,提高了处理速度,具有一定的工程价值与参考意义。参考文献[1]杨帆,张皓,马新文,等.基于FPGA的图像处理系统[J].华中科技大学学报(自然科学版),2015,43(2):119-123.[2]朱奕丹,方怡兵.基于FPGA的图像采集与VGA显示系统[J].计算机应用,2011,31(5):1258-1259.[3]原魁.基于FPGA的嵌入式图像处理系设计[M].北京:电子工业出版社,2013.[4]高亚军.基于FPGA的数字信号处理(第2版)[M].北京:电子工业出版社,2015.[5]王旭东,潘明海.数字信号处理的FPGA实现[M].北京:清华大学出版社,2011.[6]杨军,于艳艳,陈成,等.基于FPGA的二维FFT处理器的研究与设计[J].云南大学学报(自然科学版),2013,35(6):750-755.[7]张德丰.数字图像处理(MATLAB版)(第2版)[M].北京:人民邮电出版社,2015.(收稿日期:2018-02-25)作者简介:袁进(1993-),男,硕士研究生,主要研究方向:测试及信号处理。刘云飞(1962-),通信作者,男,博士,教授,主要研究方向:测试及信号处理,E-mail:lyf@njfu.edu.cn。所占比例所占比例所占比例误差(320×240点)误差(128×128点)误差(256×256点)!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!嵌入式技术EmbeddedTechnology66�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc