目 录

1.1

1.2

1.3

1.2.1

1.2.2

第 1 章 Zynq-7000&ZynqMP 启动配置和启动文件 ····································· 1

启动过程······················································································· 1

启动模式配置引脚 ·········································································· 1

Zynq-7000 SoC ········································································· 1

Zynq UltraScale+ MPSoC ····························································· 2

BOOT.bin 文件的生成 ······································································ 4

1.3.1 生成 FSBL 文件(bootloader) ····················································· 4

1.3.2 生成 R5.elf ·············································································· 6

1.3.3 生成 PMU 文件 ········································································ 6

1.3.4 生成 ATF 文件 ·········································································· 7

u-boot 文件生成 ········································································ 7

1.3.5

pl.bit 文件················································································ 8

1.3.6

1.3.7 生成 BOOT.bin 文件 ·································································· 9

Image 的生成 ················································································ 11

设备树文件的生成 ········································································ 12

1.5.1 基于 SDK 生成设备树 ······························································ 12

Linux 设备树单独编译版本 ······················································· 15

1.5.2

Linux 设备树编译命令加入 Makefile 之后的版本 ···························· 16

1.5.3

使用 BusyBox 制作根文件系统 ······················································· 16

BusyBox 介绍 ········································································· 16

1.6.1

1.6.2 交叉编译 BosyBox··································································· 16

1.6.3 配置 Busybox ········································································ 17

1.6.4 构建根文件系统 ····································································· 18

1.6.5 根文件系统的生成 ·································································· 21

1.6.6 压缩根文件系统 ····································································· 22

image.ub 的生成 ············································································ 22

第 2 章 FIT Image 介绍 ······································································· 24

前言 ··························································································· 24

Legacy uImage ·············································································· 24

FIT uImage ·················································································· 25

2.3.1 简介 ····················································································· 25

2.3.2 思路 ····················································································· 25

image source file 的语法 ···························································· 25

2.3.3

Image 的编译和使用 ································································ 27

2.3.4

参考文献 ························································································· 28

2.1

2.2

2.3

1.4

1.5

1.6

1.7

1

�

第1章 Zynq-7000&ZynqMP 启动配置和启动文件

1.1 启动过程

设备配置包含用于初始化和配置 PS 和 PL 的所有方法及过程。在软件的控制下,PS 内

的 DevC 提供用于初始化和配置 PS 和 PL 的手段及方法。在 Zynq-7000 SoC/Zynq UltraScale+

MPSoC 内提供两个主要模块用于控制配置过程。

1. BootROM。静态存储模块。当上电复位和暖复位后,由 APU(双核 A9—Zynq-7000;

四核 A53—MPSoC)执行它。

2. 设备配置单元(Device Configuration Unit,DevC):用于控制 JTAG 调试访问和提

供链接到 AES、HMAC 和 PCAP 模块的接口,用于实现 SoC 内 PL 的配置及数据

的解密。

在 PS 的控制下,可以实现安全或非安全的配置所有 PS 和 PL。通过 SOC 提供的 JTAG

接口,用户可以在外部主机的控制下对 SOC 进行配置。与 Xilinx 其他 FPGA 器件不同的是,

SOC 并不支持先开始 PL 控制配置的过程。

对 Zynq-7000 SoC 和 Zynq UltraScale+ MPSoC 的配置过程通常要求 3 个阶段。

1. 阶段 0:该阶段也成为 BootROM。该阶段控制初始化设备的启动。BootROM 是上

电复位或暖复位后,处理器所执行的用户不可修改的代码,该代码已经固化到器件

内的 BootROM 中。

2. 阶段 1:在该阶段,通过执行第一级启动引导程序(First Stage Boot Loader,FSBL)。

但是,它是可以是任意用户控制的代码。

3. 阶段 2:在该阶段,通常执行用户自己编写的软件程序。但是,也可以是第二级的

启动引导程序(Second Stage Boot Loader,SSBL)。该阶段完全在用户的控制下实

现的,如 Linux 的 u-boot。

在阶段 2 里面是可以添加很多文件,如 ZYNQ UltraScale+ MPSoC 可以添加 PMU,PL.bit,

ATF,R5.elf,a53.elf,u-boot.elf 等,总是是按照用户需求进行添加。

1.2 启动模式配置引脚

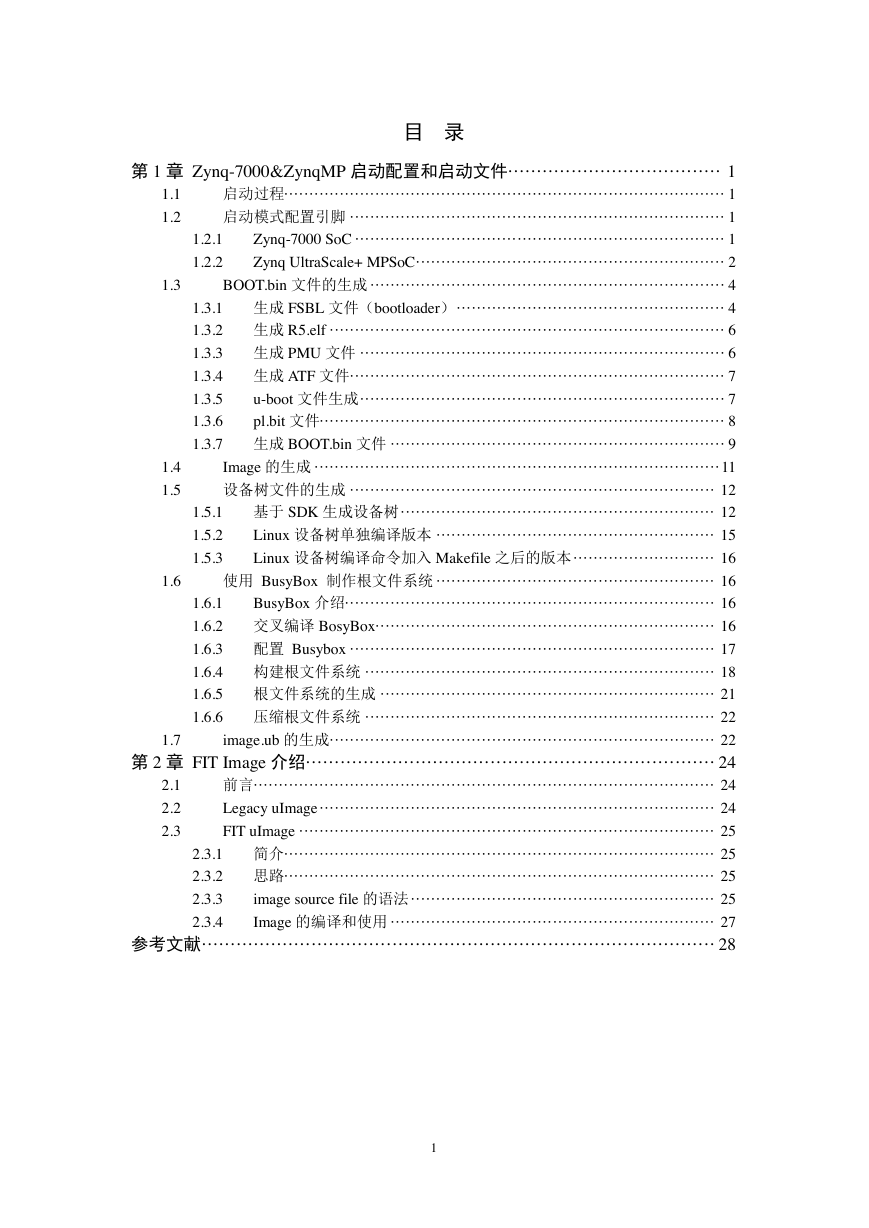

1.2.1 Zynq-7000 SoC

启动模式如表 1.1 所示。

表 1.1 BOOT_MODE 与 MIO 引脚关系

JTAG 方式

vmode[1] vmode[0] B_M[4] B_M[2] B_M[1] B_M[0] B_M[3]

MIO[8] MIO[7] MIO[6] MIO[5] MIO[4] MIO[3] MIO[2]

级联 JTAG

独立 JTAG

JATG

NOR

NAND

保留

Quad_SPI

__

__

启动设备

0

1

0

__

__

0

0

1

1

0

0

0

0

0

1

0

1

0

1

0

1

�

1

1

1

PLL 模式

0

1

MIO 第 0 组电压

MIO 第 1 组电压

__

1

0

1

__

0

1

1

__

保留

SD

保留

使用 PLL

旁路 PLL

__

2.5V/3.3V

__

1.8V

0

1

2.5V/3.3V

1.8V

0

1

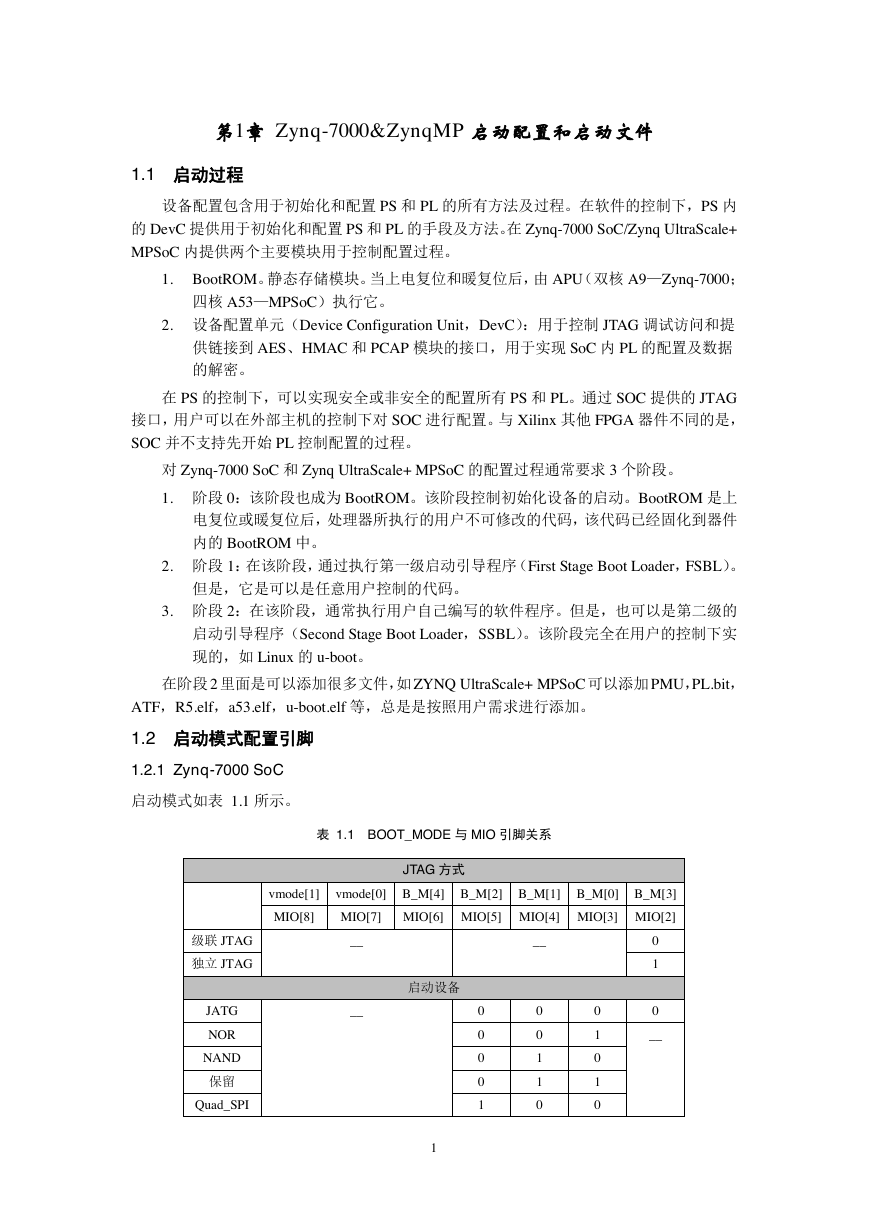

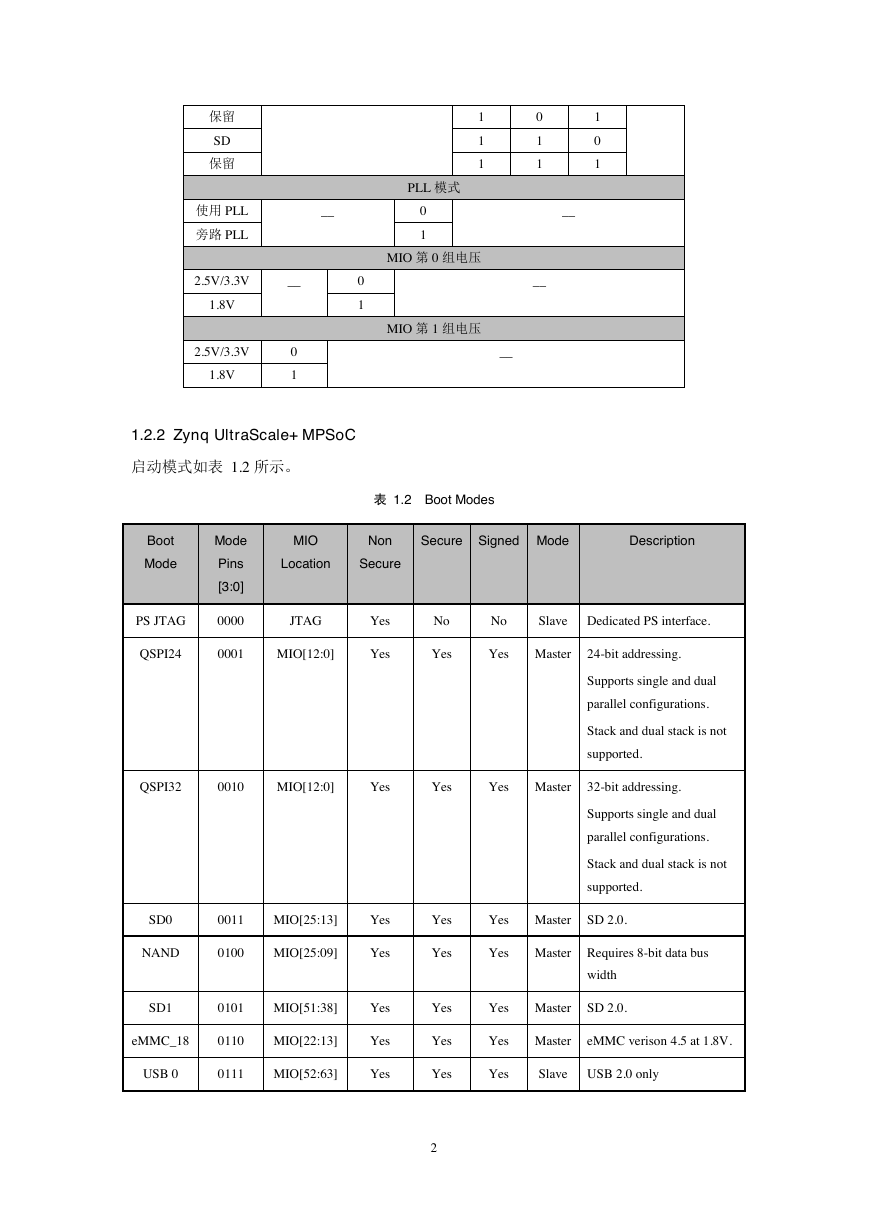

1.2.2 Zynq UltraScale+ MPSoC

启动模式如表 1.2 所示。

表 1.2 Boot Modes

Boot

Mode

MIO

Non

Secure Signed Mode

Description

Mode

Pins

[3:0]

Location

Secure

PS JTAG

0000

JTAG

Yes

No

No

Slave Dedicated PS interface.

QSPI24

0001

MIO[12:0]

Yes

Yes

Yes Master 24-bit addressing.

Supports single and dual

parallel configurations.

Stack and dual stack is not

supported.

QSPI32

0010

MIO[12:0]

Yes

Yes

Yes Master 32-bit addressing.

Supports single and dual

parallel configurations.

Stack and dual stack is not

supported.

SD0

0011

MIO[25:13]

Yes

Yes

Yes Master SD 2.0.

NAND

0100

MIO[25:09]

Yes

Yes

Yes Master Requires 8-bit data bus

width

SD1

0101

MIO[51:38]

Yes

Yes

Yes Master SD 2.0.

eMMC_18

0110

MIO[22:13]

Yes

Yes

Yes Master eMMC verison 4.5 at 1.8V.

USB 0

0111

MIO[52:63]

Yes

Yes

Yes

Slave USB 2.0 only

2

�

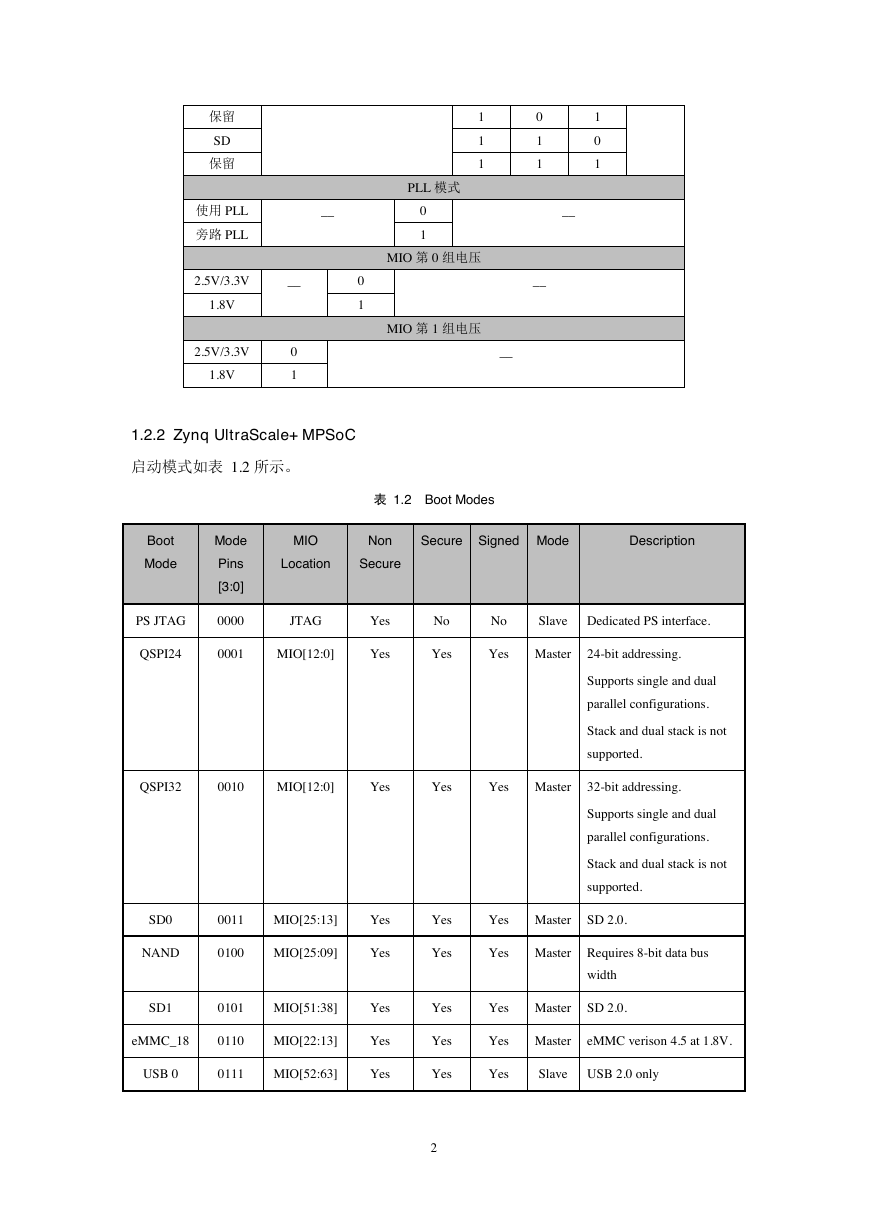

Boot

Mode

MIO

Non

Secure Signed Mode

Description

Mode

Pins

[3:0]

Location

Secure

PJTAG_0

1000

MIO[29:26]

Yes

No

No

Slave PS JTAG connection 0

option.

PJTAG_1

1001

MIO[15:12]

Yes

No

No

Slave PS JTAG connection 1

option.

SD1-LS

1110

MIO[51:39]

Yes

Yes

Yes Master SD 3.0 with a required SD

3.0 compliant voltage level

shifter.

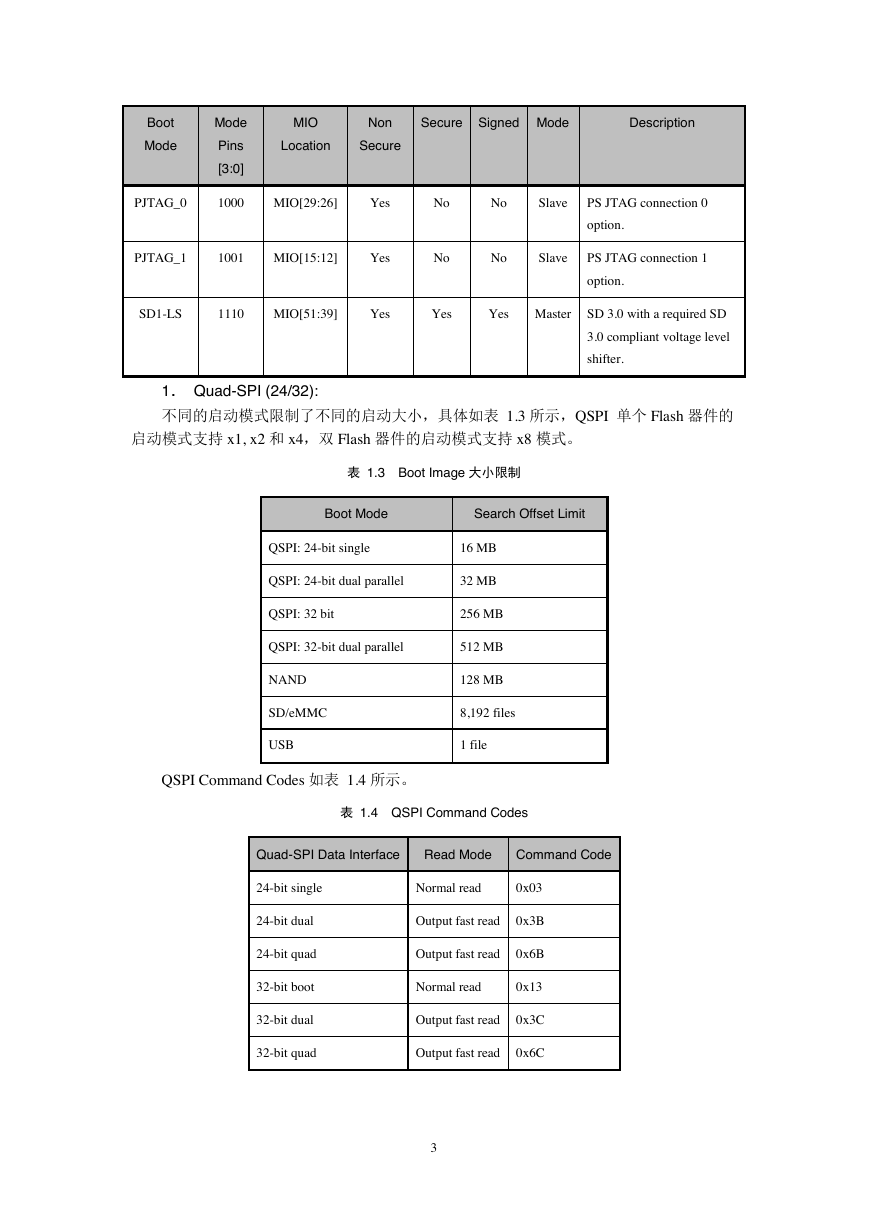

1. Quad-SPI (24/32):

不同的启动模式限制了不同的启动大小,具体如表 1.3 所示,QSPI 单个 Flash 器件的

启动模式支持 x1, x2 和 x4,双 Flash 器件的启动模式支持 x8 模式。

表 1.3 Boot Image 大小限制

Boot Mode

Search Offset Limit

QSPI: 24-bit single

16 MB

QSPI: 24-bit dual parallel

32 MB

QSPI: 32 bit

256 MB

QSPI: 32-bit dual parallel

512 MB

NAND

SD/eMMC

USB

128 MB

8,192 files

1 file

QSPI Command Codes 如表 1.4 所示。

表 1.4 QSPI Command Codes

Quad-SPI Data Interface Read Mode Command Code

24-bit single

Normal read

0x03

24-bit dual

Output fast read 0x3B

24-bit quad

Output fast read 0x6B

32-bit boot

Normal read

0x13

32-bit dual

Output fast read 0x3C

32-bit quad

Output fast read 0x6C

3

�

1. NAND:

NAND 启动模式仅仅支持 8 位方式,支持 multi-boot 方式。

2. SD0/SD1:

启动方式支持 FAT16/32 文件系统,支持 multi-boot 方式,multi-boot 方式最大的文件个

数为 8192,支持的 SD 版本为 2.0,3.3V 和 4bit 的 I/O 接口,文件名字支持 boot.bin,

boot0001.bin 和 boot0002.bin 到 boot8190.bin。

3. SD1-LS:

SD1-LS 模式和 SD0/SD1 一样,只是 SD 版本为 3.0。

4. eMMC18:

eMMC18 模式和 SD0/SD1 一样,除了 I/O 接口是 1.8V 电平和 8bit 数据位。

5. USB0

USB controller 0 支持 USB boot,并且 USB Host 协议为 DFU。USB Host 的 FSBL 文件

下载到 OCM,其他所有压缩 boot 文件下载到 DDR,因此 USB boot 文件取决于 OCM 和 DDR

的大小。USB boot 不支持 multi-boot、image fallback 和 XIP。

6. 具体引脚

表 1.2 只给出了 MIO 是那些引脚,并没有标注具体引脚和外设 IO 的对应关系,具体的

文档详见《ug1085-zynq-ultrascale+Technical Reference Manual》的第 28 章,第 779~787 页

的表格,里面列举了所有外设的 IO 到 MIO 上的映射,包含 BOOT 外设。

1.3 BOOT.bin 文件的生成

BOOT.bin 为 Zynq-7000&Zynq UltraScale+ MPSoC 的启动文件,里面包含 FSBL,PMU,

PL.bit,ATF,R5.elf,u-boot.elf 文件,其中每个文件都是需要单独生成的。Vivado 工程可

以是任意一个,如只有 GPIO 的工程,有了 vivado 工程之后,编译生成 bit 文件,如果导出

bit 文件,Launch SDK,后面的 FSBL,PMU,R5.elf 都是通过 SDK(Windows 环境)生成

的。当然 ATF 和 u-boot.elf 是 Linux 环境下的 SDK 生成的,可以直接采用官方的。

1.3.1 生成 FSBL 文件(bootloader)

在对应的 vivado 工程,使用 SDK 生成。

1. 打开对应的 SDK 工程,只需要包含 xxx_hw_platform 即可。

2. 在 SDK 主菜单下,选择 File→New→Application Project。

3. 弹出“New Project”对话框,参数设置如表 1.5 所示。

表 1.5 FSBL_A53 工程的设置

Wizard Screen

System Properties

Setting or Command

Application Project

Project Name

fsbl_a53

Use Default Location

Select this option

OS Platform

Standalone

Hardware Platform

xxx_hw_platform_0

Processor

Language

Compiler

psu_cortexa53_0

C

64-bit

Hypervisor Guest

No

4

�

Board Support Package Select Create New and provide the name of a53_bsp

Click Next

Templates

Available Templates

Zynq MP FSBL

4. 选择 Zynq MP FSBL 模板,如图 1.1 所示。

图 1.1 FSBL 模板选择

5. 完成,编译即可,fsbl_a53 > debug > fsbl_a53.elf 为所需要的文件。

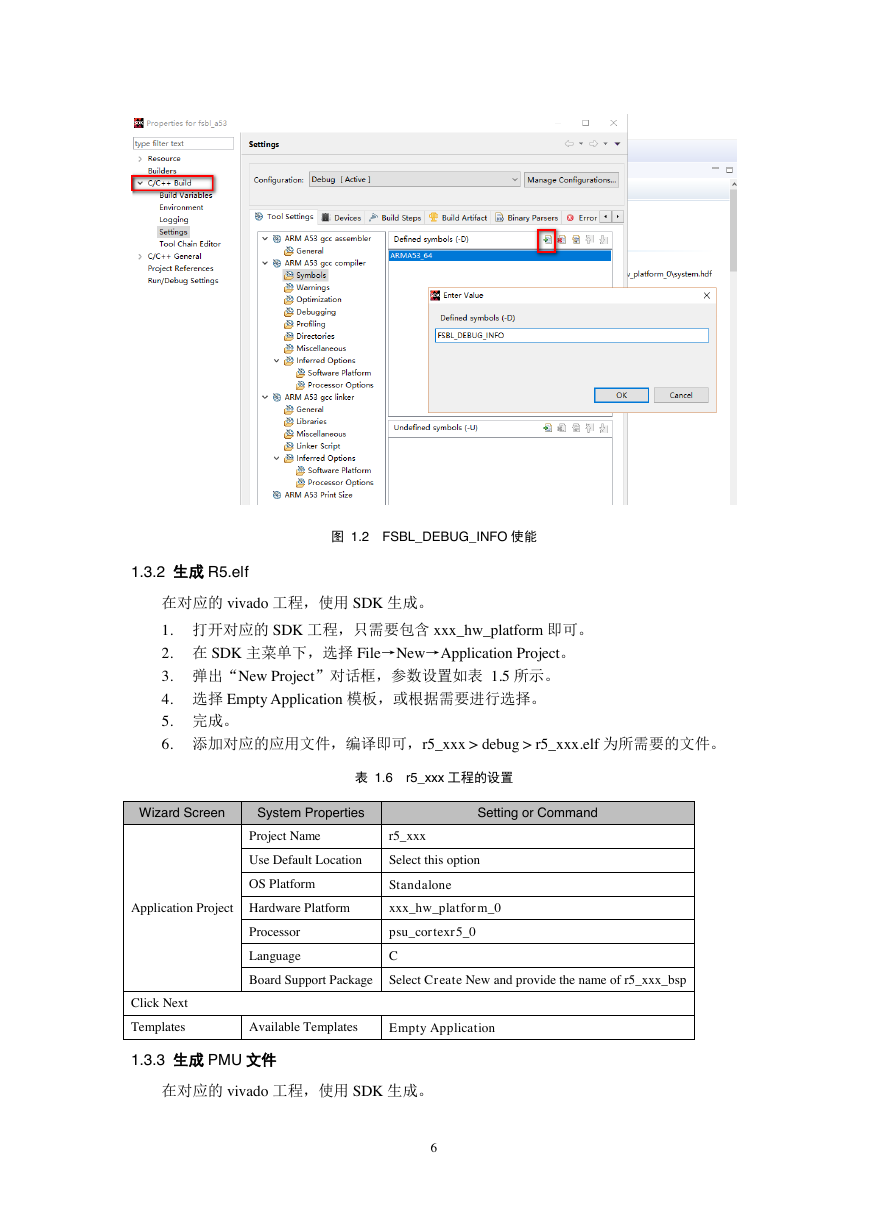

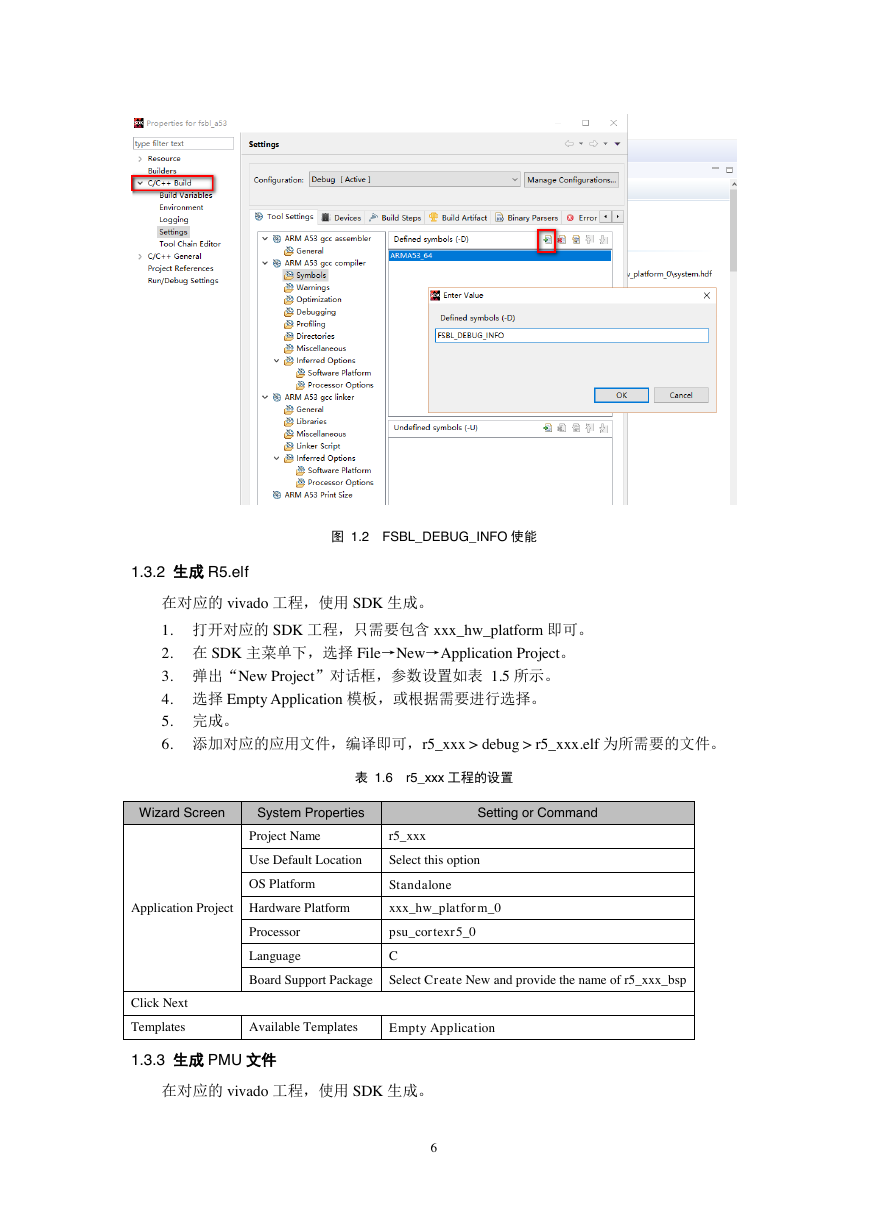

如果需要在启动阶段,打印 FSBL 相关信息,可以设置 FSBL_DEBUG_INFO 使能,步

骤如下,软件界面如图 1.2 所示:

1. 打开 Project Explorer,右键点击 fsbl_a53 应用。

2. 点击 C/C++ Build Settings。

3. 选择 Settings→Tool Settings→Symbols。

4. 点击 Add。

5. 输入 FSBL_DEBUG_INFO。

6. Clean 工程,自动重新编译即可。

5

�

图 1.2 FSBL_DEBUG_INFO 使能

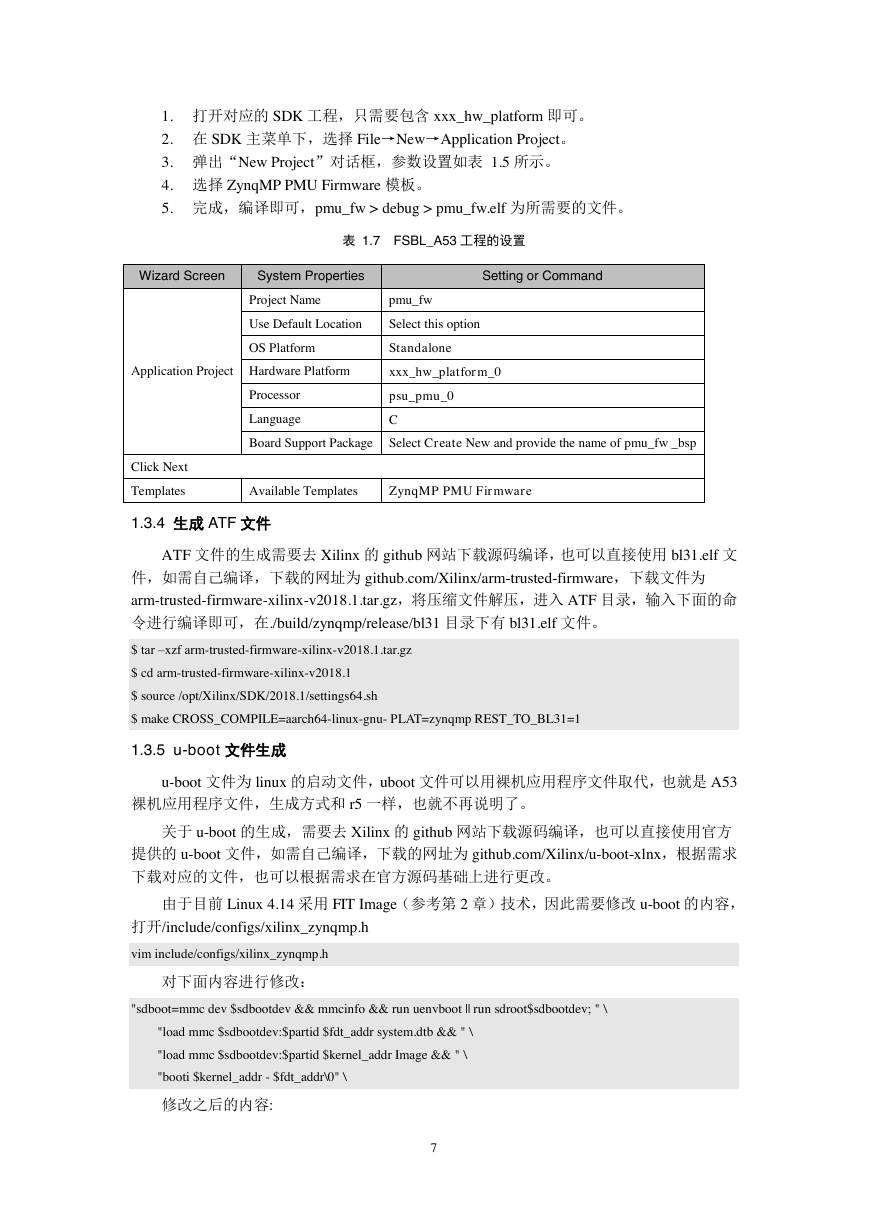

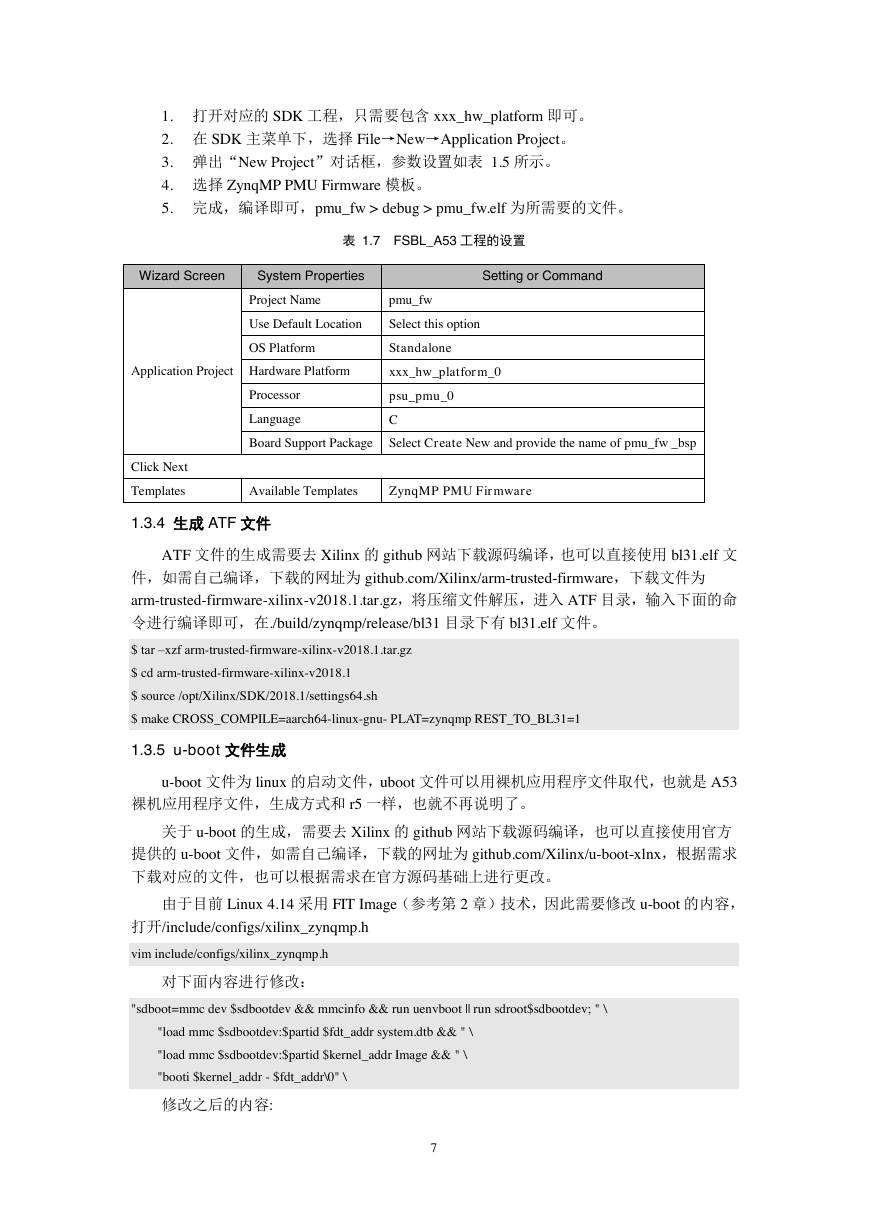

1.3.2 生成 R5.elf

在对应的 vivado 工程,使用 SDK 生成。

1. 打开对应的 SDK 工程,只需要包含 xxx_hw_platform 即可。

2. 在 SDK 主菜单下,选择 File→New→Application Project。

3. 弹出“New Project”对话框,参数设置如表 1.5 所示。

4. 选择 Empty Application 模板,或根据需要进行选择。

5. 完成。

6. 添加对应的应用文件,编译即可,r5_xxx > debug > r5_xxx.elf 为所需要的文件。

表 1.6 r5_xxx 工程的设置

Wizard Screen

System Properties

Setting or Command

Project Name

r5_xxx

Use Default Location

Select this option

OS Platform

Standalone

Application Project

Hardware Platform

xxx_hw_platform_0

Processor

Language

psu_cortexr5_0

C

Board Support Package Select Create New and provide the name of r5_xxx_bsp

Click Next

Templates

Available Templates

Empty Application

1.3.3 生成 PMU 文件

在对应的 vivado 工程,使用 SDK 生成。

6

�

1. 打开对应的 SDK 工程,只需要包含 xxx_hw_platform 即可。

2. 在 SDK 主菜单下,选择 File→New→Application Project。

3. 弹出“New Project”对话框,参数设置如表 1.5 所示。

4. 选择 ZynqMP PMU Firmware 模板。

5. 完成,编译即可,pmu_fw > debug > pmu_fw.elf 为所需要的文件。

表 1.7 FSBL_A53 工程的设置

Wizard Screen

System Properties

Setting or Command

Project Name

pmu_fw

Use Default Location

Select this option

OS Platform

Standalone

Application Project

Hardware Platform

xxx_hw_platform_0

Processor

Language

psu_pmu_0

C

Board Support Package Select Create New and provide the name of pmu_fw _bsp

Click Next

Templates

Available Templates

ZynqMP PMU Firmware

1.3.4 生成 ATF 文件

ATF 文件的生成需要去 Xilinx 的 github 网站下载源码编译,也可以直接使用 bl31.elf 文

件,如需自己编译,下载的网址为 github.com/Xilinx/arm-trusted-firmware,下载文件为

arm-trusted-firmware-xilinx-v2018.1.tar.gz,将压缩文件解压,进入 ATF 目录,输入下面的命

令进行编译即可,在./build/zynqmp/release/bl31 目录下有 bl31.elf 文件。

$ tar –xzf arm-trusted-firmware-xilinx-v2018.1.tar.gz

$ cd arm-trusted-firmware-xilinx-v2018.1

$ source /opt/Xilinx/SDK/2018.1/settings64.sh

$ make CROSS_COMPILE=aarch64-linux-gnu- PLAT=zynqmp REST_TO_BL31=1

1.3.5 u-boot 文件生成

u-boot 文件为 linux 的启动文件,uboot 文件可以用裸机应用程序文件取代,也就是 A53

裸机应用程序文件,生成方式和 r5 一样,也就不再说明了。

关于 u-boot 的生成,需要去 Xilinx 的 github 网站下载源码编译,也可以直接使用官方

提供的 u-boot 文件,如需自己编译,下载的网址为 github.com/Xilinx/u-boot-xlnx,根据需求

下载对应的文件,也可以根据需求在官方源码基础上进行更改。

由于目前 Linux 4.14 采用 FIT Image(参考第 2 章)技术,因此需要修改 u-boot 的内容,

打开/include/configs/xilinx_zynqmp.h

vim include/configs/xilinx_zynqmp.h

对下面内容进行修改:

"sdboot=mmc dev $sdbootdev && mmcinfo && run uenvboot || run sdroot$sdbootdev; " \

"load mmc $sdbootdev:$partid $fdt_addr system.dtb && " \

"load mmc $sdbootdev:$partid $kernel_addr Image && " \

"booti $kernel_addr - $fdt_addr\0" \

修改之后的内容:

7

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc