D

C

B

A

5

4

3

C1

C4

DVDD

1uF

VDS18

0.1uF

E5

E1

E3

VDDA_SEN

C6

2.2uF

C7

C8

0.1uF

0.1uF

4.7K

4.7K

SDA

SCL

A1

A4

B1

C1

A5

A2

B3

B4

DGND

SGND

VDS18

R5

R6

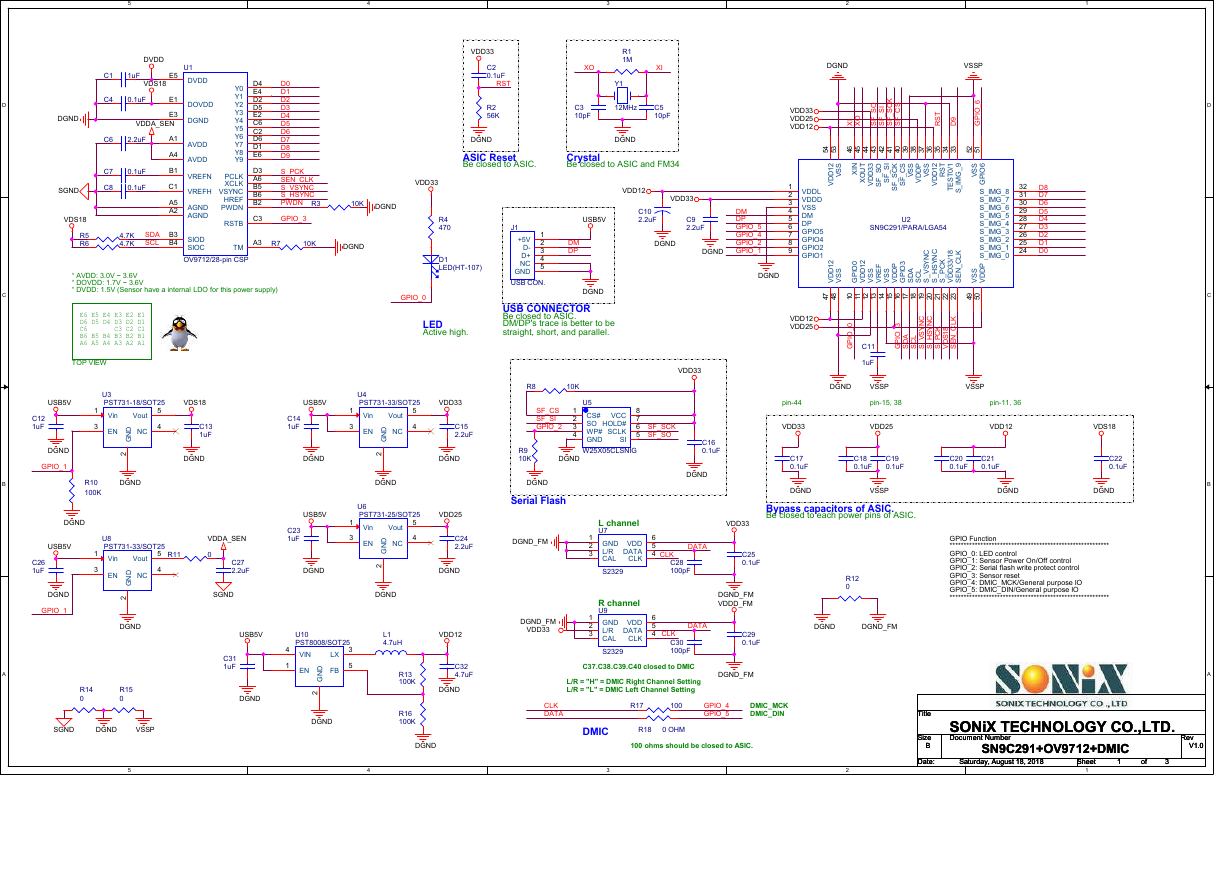

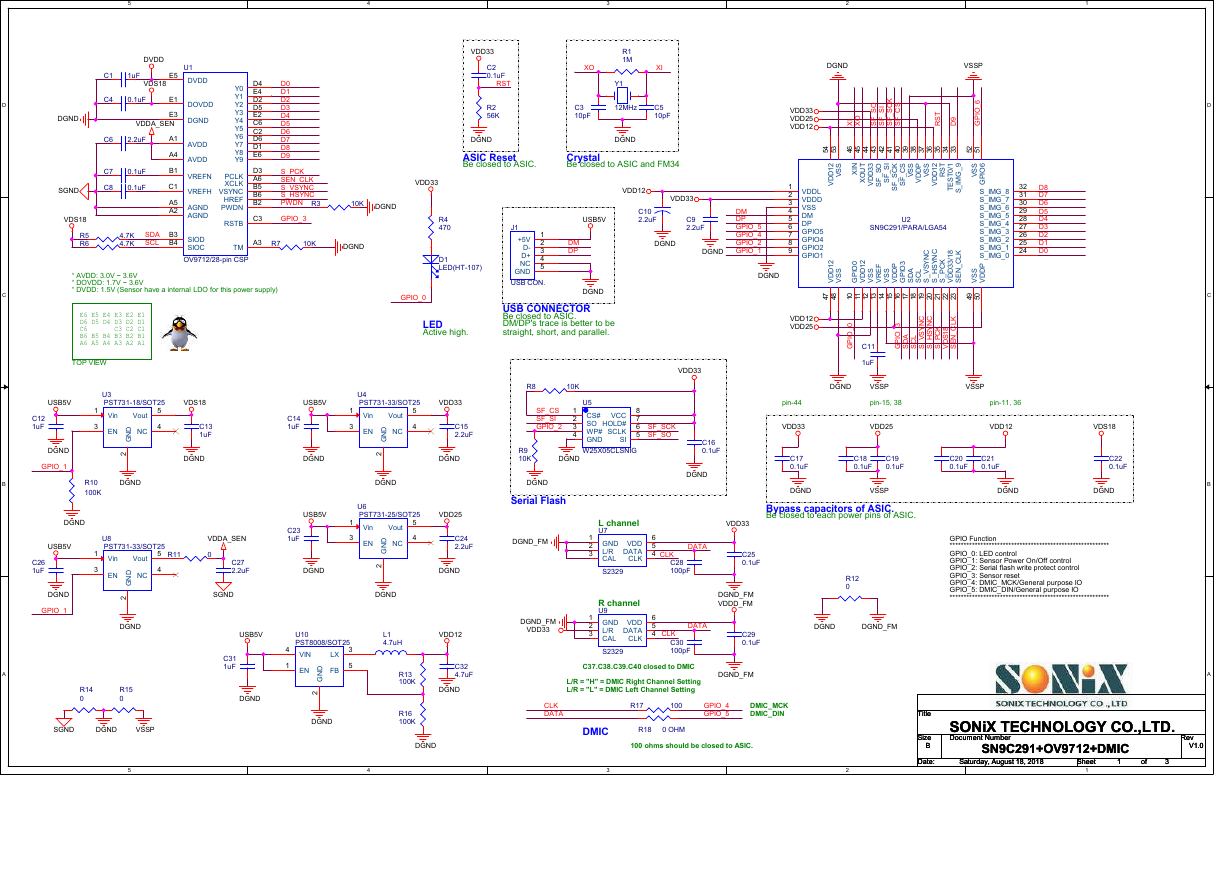

U1

DVDD

DOVDD

DGND

AVDD

AVDD

VREFN

VREFH

AGND

AGND

Y0

Y1

Y2

Y3

Y4

Y5

Y6

Y7

Y8

Y9

PCLK

XCLK

VSYNC

HREF

PWDN

RSTB

D4

E4

D2

D5

E2

C6

C2

D6

D1

E6

D3

A6

B5

B6

B2

C3

D0

D1

D2

D3

D4

D5

D6

D7

D8

D9

S_PCK

SEN_CLK

S_VSYNC

S_HSYNC

PWDN

R3

GPIO_3

SIOD

SIOC

OV9712/28-pin CSP

TM

A3

R7

10K

DGND

“ AVDD: 3.0V ~ 3.6V

“ DOVDD: 1.7V ~ 3.6V

“ DVDD: 1.5V (Sensor have a internal LDO for this power supply)

VDD33

C2

0.1uF

RST

R2

56K

DGND

XO

C3

10pF

R1

1M

Y1

12MHz

DGND

XI

C5

10pF

ASIC Reset

Be closed to ASIC.

Crystal

Be closed to ASIC and FM34

VDD33

10K

DGND

R4

470

J1

VDD12

USB5V

C10

2.2uF

VDD33

C9

2.2uF

DM

DP

DGND

DGND

DGND

1

2

3

4

5

+5V

D-

D+

NC

GND

USB CON.

USB CONNECTOR

Be closed to ASIC.

DM/DP's trace is better to be

straight, short, and parallel.

D1

LED(HT-107)

GPIO_0

LED

Active high.

E6 E5 E4 E3 E2 E1

D6 D5 D4 D3 D2 D1

C6 C3 C2 C1

B6 B5 B4 B3 B2 B1

A6 A5 A4 A3 A2 A1

TOP VIEW

USB5V

C12

1uF

DGND

GPIO_1

U3

PST731-18/SOT25

5

Vin

Vout

4

EN

NC

D

N

G

1

3

2

DGND

R10

100K

DGND

USB5V

C26

1uF

DGND

GPIO_1

U8

PST731-33/SOT25

5

Vin

Vout

4

EN

NC

D

N

G

1

3

2

DGND

R14

0

R15

0

SGND

DGND

VSSP

VDS18

C13

1uF

DGND

VDDA_SEN

R11

0

C27

2.2uF

SGND

USB5V

C14

1uF

DGND

USB5V

C23

1uF

DGND

U4

PST731-33/SOT25

5

Vin

Vout

4

EN

NC

D

N

G

2

DGND

U6

PST731-25/SOT25

5

Vin

Vout

4

EN

NC

D

N

G

1

3

1

3

2

DGND

VDD33

C15

2.2uF

DGND

VDD25

C24

2.2uF

DGND

USB5V

C31

1uF

DGND

U10

PST8008/SOT25

3

VIN

LX

5

EN

D

N

G

FB

4

1

2

DGND

L1

4.7uH

VDD12

C32

4.7uF

DGND

R13

100K

R16

100K

DGND

R8

10K

SF_CS

SF_SI

GPIO_2

1

2

3

4

R9

10K

DGND

DGND

Serial Flash

DGND_FM

DGND_FM

VDD33

U5

CS#

SO

WP#

GND

W25X05CLSNIG

VCC

HOLD#

SCLK

SI

8

7

6

5

VDD33

SF_SCK

SF_SO

C16

0.1uF

DGND

L channel

U7

1

2 GND

L/R

3

CAL

S2329

VDD

DATA

CLK

R channel

U9

1

2 GND

L/R

3

CAL

S2329

VDD

DATA

CLK

VDD33

C25

0.1uF

DGND_FM

VDDD_FM

C29

0.1uF

6

5

4

6

5

4

DATA

CLK

C28

100pF

DATA

CLK

C30

100pF

C37.C38.C39.C40 closed to DMIC

L/R = "H" = DMIC Right Channel Setting

L/R = "L" = DMIC Left Channel Setting

DGND_FM

CLK

DATA

R17

100

GPIO_4

GPIO_5

DMIC_MCK

DMIC_DIN

DMIC

R18

0 OHM

100 ohms should be closed to ASIC.

5

4

3

2

2

DGND

1

32

31

30

29

28

27

26

25

24

D8

D7

D6

D5

D4

D3

D2

D1

D0

VSSP

6

_

O

P

G

I

2

5

1

5

S

S

V

I

6

O

P

G

S_IMG_8

S_IMG_7

S_IMG_6

S_IMG_5

S_IMG_4

S_IMG_3

S_IMG_2

S_IMG_1

S_IMG_0

P

D

D

V

S

S

V

VDD33

VDD25

VDD12

1

2

3

4

5

6

7

8

9

DM

DP

GPIO_5

GPIO_4

GPIO_2

GPIO_1

DGND

4

5

3

5

S

S

V

2

1

D

D

V

VDDL

VDDD

VSS

DM

DP

GPIO5

GPIO4

GPIO2

GPIO1

2

1

D

D

V

S

S

V

7

4

8

4

O

S

_

F

S

I

S

_

F

S

K

C

S

_

F

S

S

C

_

F

S

O

X

I

X

T

S

R

9

D

6

4

5

4

4

4

3

4

2

4

1

4

0

4

9

3

8

3

7

3

6

3

5

3

4

3

3

3

N

X

I

T

U

O

X

3

3

D

D

V

O

S

_

F

S

I

S

_

F

S

S

C

_

F

S

K

C

S

_

F

S

S

S

V

S

S

V

P

D

D

V

T

S

R

2

1

D

D

V

/

1

0

T

S

E

T

9

_

G

M

_

S

I

U2

SN9C291/PARA/LGA54

0

O

P

G

2

1

D

D

V

I

F

E

R

V

S

S

V

S

S

V

P

D

D

V

I

3

O

P

G

A

D

S

L

C

S

C

N

Y

S

V

_

S

C

N

Y

S

H

_

S

8

1

/

K

C

P

_

S

3

3

D

D

V

K

L

C

_

N

E

S

0

1

1

1

2

1

3

1

4

1

5

1

6

1

7

1

8

1

9

1

0

2

1

2

2

2

3

2

9

4

0

5

VDD12

VDD25

0

_

O

P

G

I

C11

1uF

3

_

O

P

G

I

A

D

S

L

C

S

C

N

Y

S

V

_

S

C

N

Y

S

H

_

S

K

L

C

_

N

E

S

K

C

P

_

S

8

1

S

D

V

DGND

VSSP

VSSP

pin-44

VDD33

pin-15, 38

VDD25

pin-11, 36

VDD12

C17

0.1uF

C18

0.1uF

C19

0.1uF

C20

0.1uF

C21

0.1uF

VDS18

C22

0.1uF

DGND

VSSP

Bypass capacitors of ASIC.

Be closed to each power pins of ASIC.

DGND

DGND

GPIO Function

*********************************************************

GPIO_0: LED control

GPIO_1: Sensor Power On/Off control

GPIO_2: Serial flash write protect control

GPIO_3: Sensor reset

GPIO_4: DMIC_MCK/General purpose IO

GPIO_5: DMIC_DIN/General purpose IO

*********************************************************

R12

0

DGND

DGND_FM

Title

Title

Title

Size

Size

Size

B

B

B

Date:

Date:

Date:

SONiX TECHNOLOGY CO.,LTD.

SONiX TECHNOLOGY CO.,LTD.

SONiX TECHNOLOGY CO.,LTD.

Document Number

Document Number

Document Number

SN9C291+OV9712+DMIC

SN9C291+OV9712+DMIC

SN9C291+OV9712+DMIC

1

1

1

Saturday, August 18, 2018

Saturday, August 18, 2018

Saturday, August 18, 2018

Sheet

Sheet

Sheet

1

of

of

of

3

3

3

D

C

B

A

Rev

Rev

Rev

V1.0

V1.0

V1.0

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc