5

4

3

2

1

D

C

B

A

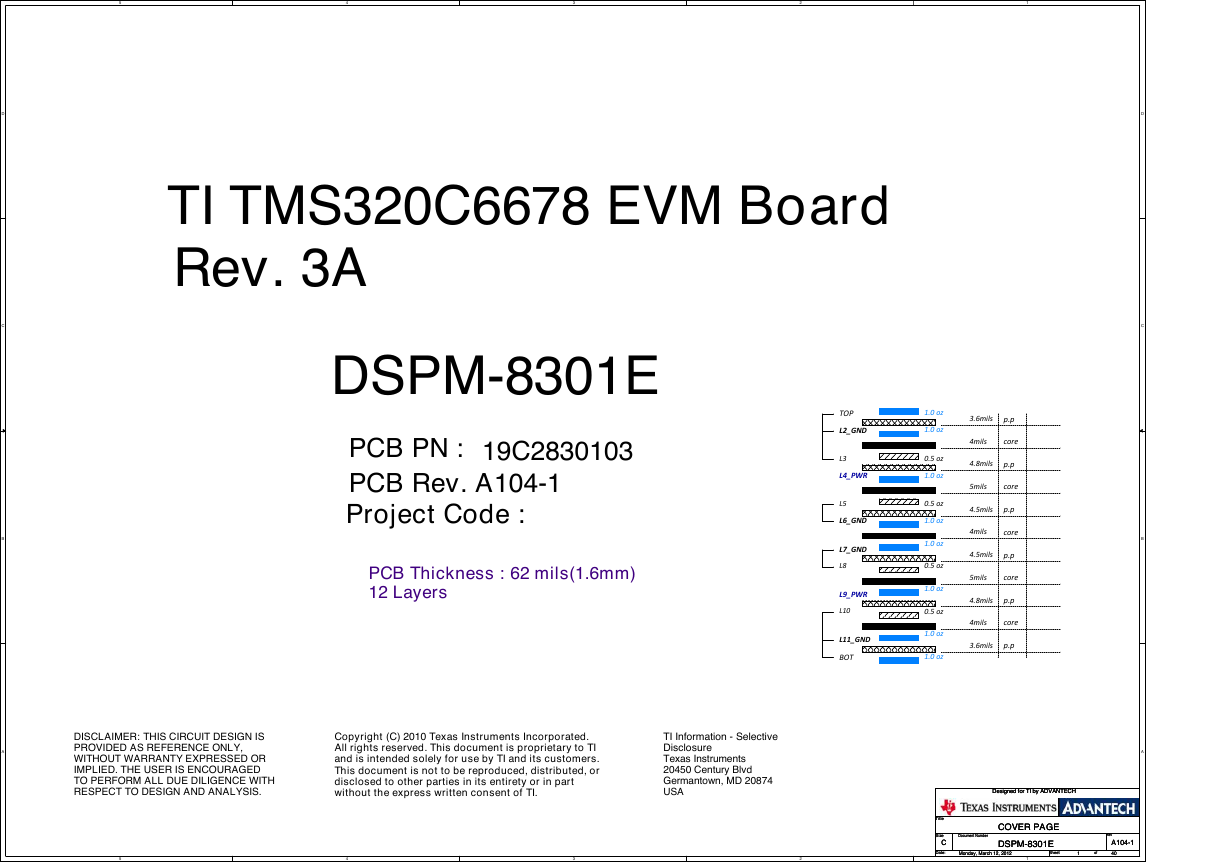

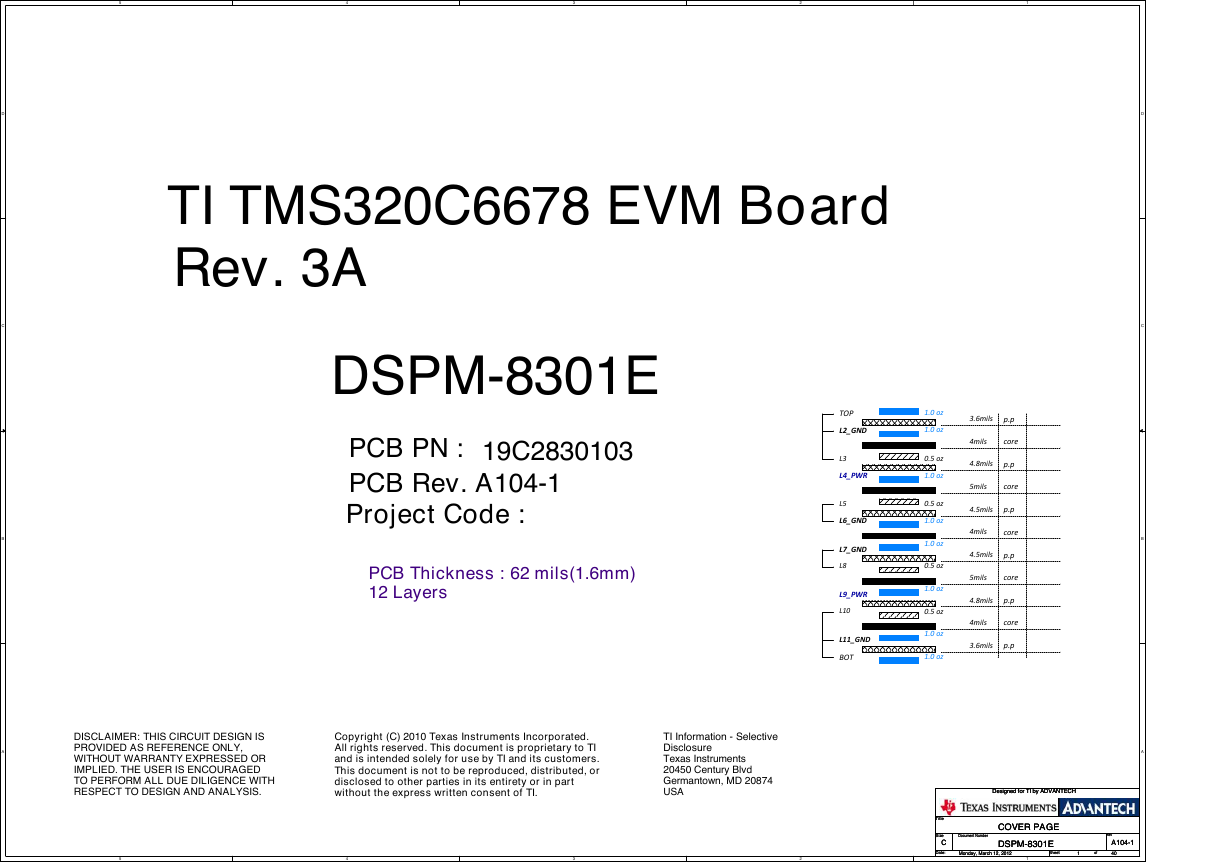

TI TMS320C6678 EVM Board

Rev. 3A

DSPM-8301E

19C2830103

PCB PN :

PCB Rev. A104-1

Project Code :

PCB Thickness : 62 mils(1.6mm)

12 Layers

TOP

L2_GND

L3

L4_PWR

L5

L6_GND

L7_GND

L8

L9_PWR

L10

L11_GND

BOT

1.0 oz

1.0 oz

0.5 oz

1.0 oz

0.5 oz

1.0 oz

1.0 oz

0.5 oz

1.0 oz

0.5 oz

1.0 oz

1.0 oz

3.6mils

p.p

4mils

core

4.8mils

p.p

5mils

core

4.5mils

p.p

4mils

core

4.5mils

p.p

5mils

core

4.8mils

p.p

4mils

core

3.6mils

p.p

DISCLAIMER: THIS CIRCUIT DESIGN IS

PROVIDED AS REFERENCE ONLY,

WITHOUT WARRANTY EXPRESSED OR

IMPLIED. THE USER IS ENCOURAGED

TO PERFORM ALL DUE DILIGENCE WITH

RESPECT TO DESIGN AND ANALYSIS.

Copyright (C) 2010 Texas Instruments Incorporated.

All rights reserved. This document is proprietary to TI

and is intended solely for use by TI and its customers.

This document is not to be reproduced, distributed, or

disclosed to other parties in its entirety or in part

without the express written consent of TI.

TI Information - Selective

Disclosure

Texas Instruments

20450 Century Blvd

Germantown, MD 20874

USA

5

4

3

2

Designed for TI by ADVANTECH

Designed for TI by ADVANTECH

Designed for TI by ADVANTECH

Title

Title

Title

Size

Size

Size

C

C

C

Date:

Date:

Date:

Document Number

Document Number

Document Number

COVER PAGE

COVER PAGE

COVER PAGE

DSPM-8301E

DSPM-8301E

DSPM-8301E

Monday, March 12, 2012

Monday, March 12, 2012

Monday, March 12, 2012

1

Sheet

Sheet

Sheet

1

1

1

of

of

of

Rev

Rev

Rev

A104-1

A104-1

A104-1

40

40

40

D

C

B

A

�

D

C

B

A

5

4

3

2

1

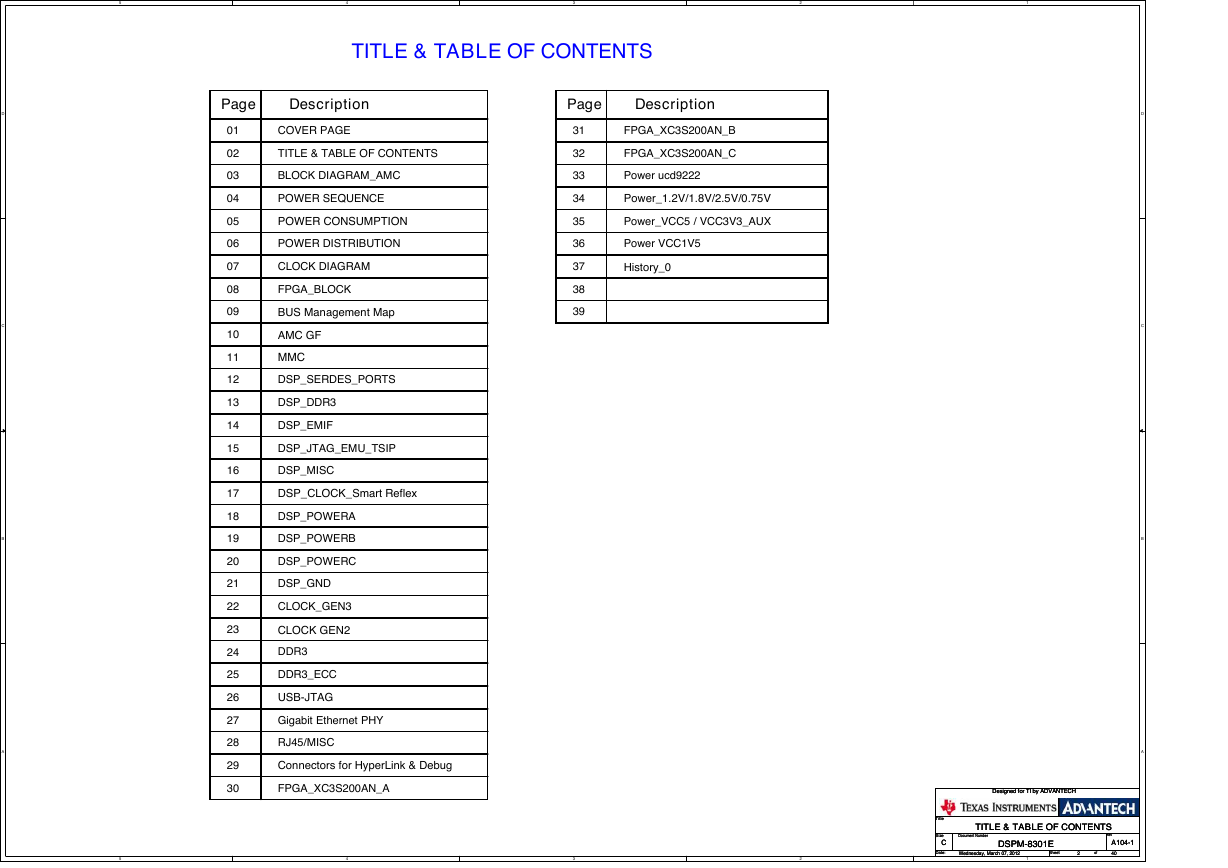

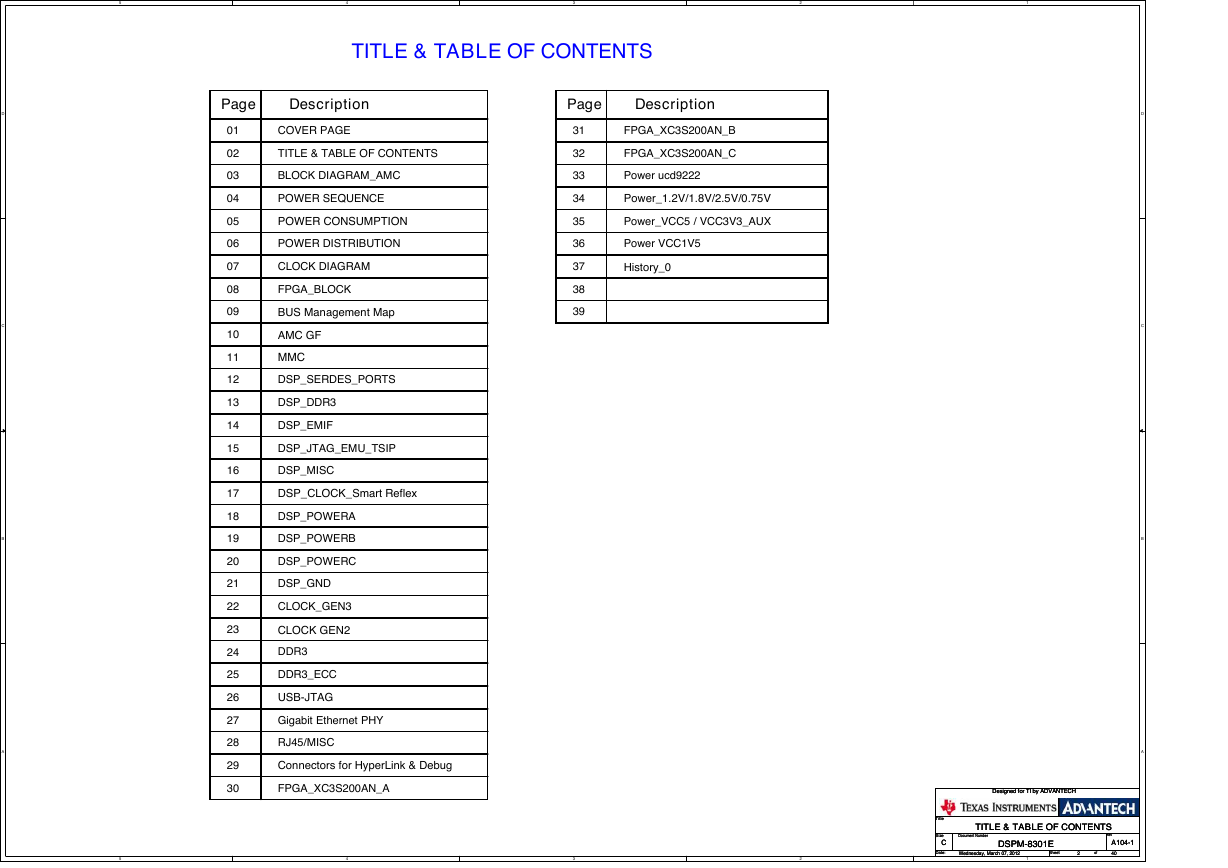

TITLE & TABLE OF CONTENTS

Page

Description

Page

Description

FPGA_XC3S200AN_B

FPGA_XC3S200AN_C

Power ucd9222

Power_1.2V/1.8V/2.5V/0.75V

Power_VCC5 / VCC3V3_AUX

Power VCC1V5

History_0

31

32

33

34

35

36

37

38

39

01

02

03

04

05

06

07

08

09

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

COVER PAGE

TITLE & TABLE OF CONTENTS

BLOCK DIAGRAM_AMC

POWER SEQUENCE

POWER CONSUMPTION

POWER DISTRIBUTION

CLOCK DIAGRAM

FPGA_BLOCK

BUS Management Map

AMC GF

MMC

DSP_SERDES_PORTS

DSP_DDR3

DSP_EMIF

DSP_JTAG_EMU_TSIP

DSP_MISC

DSP_CLOCK_Smart Reflex

DSP_POWERA

DSP_POWERB

DSP_POWERC

DSP_GND

CLOCK_GEN3

CLOCK GEN2

DDR3

DDR3_ECC

USB-JTAG

Gigabit Ethernet PHY

RJ45/MISC

Connectors for HyperLink & Debug

FPGA_XC3S200AN_A

5

4

3

2

Designed for TI by ADVANTECH

Designed for TI by ADVANTECH

Designed for TI by ADVANTECH

Title

Title

Title

Size

Size

Size

C

C

C

Date:

Date:

Date:

TITLE & TABLE OF CONTENTS

TITLE & TABLE OF CONTENTS

TITLE & TABLE OF CONTENTS

Document Number

Document Number

Document Number

DSPM-8301E

DSPM-8301E

DSPM-8301E

Wednesday, March 07, 2012

Wednesday, March 07, 2012

Wednesday, March 07, 2012

1

Sheet

Sheet

Sheet

2

2

2

of

of

of

Rev

Rev

Rev

A104-1

A104-1

A104-1

40

40

40

D

C

B

A

�

D

C

B

A

5

4

3

2

1

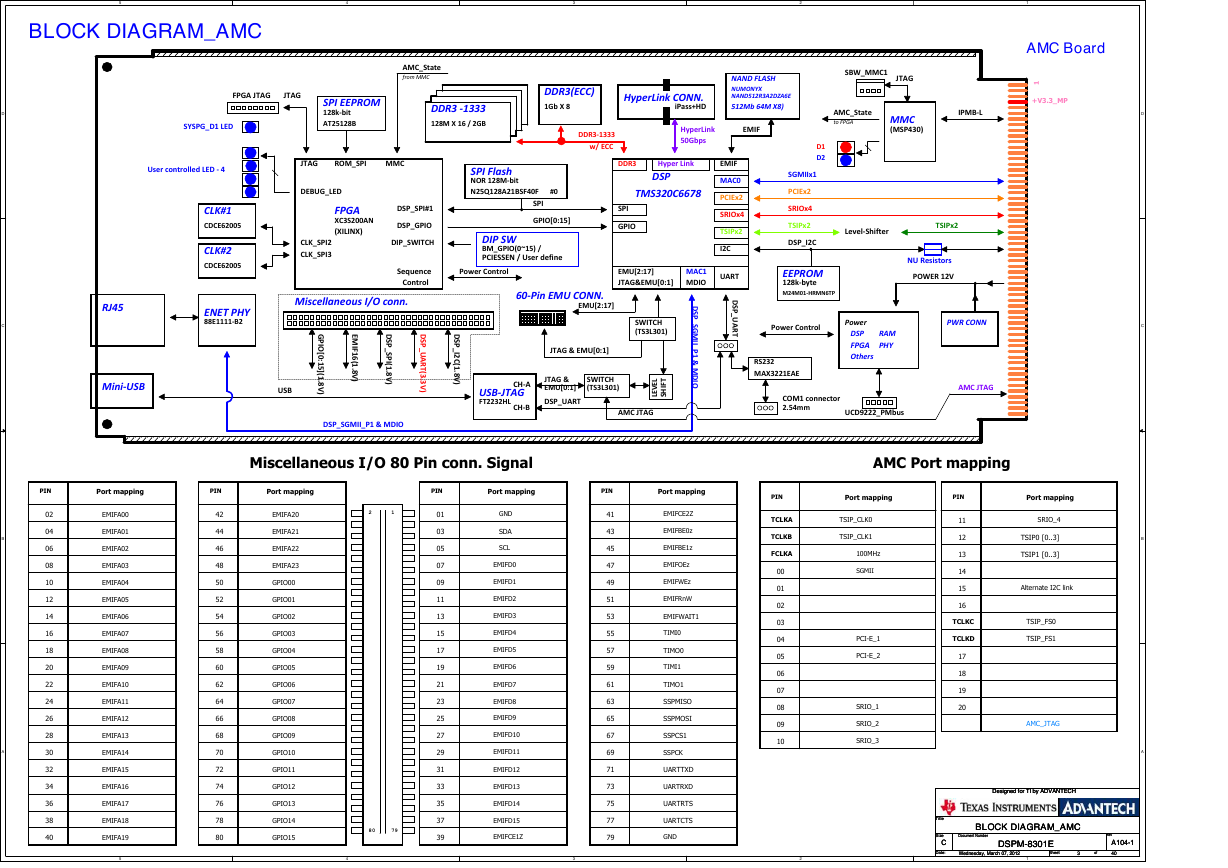

SBW_MMC1

JTAG

AMC_State

to FPGA

MMC

(MSP430)

IPMB-L

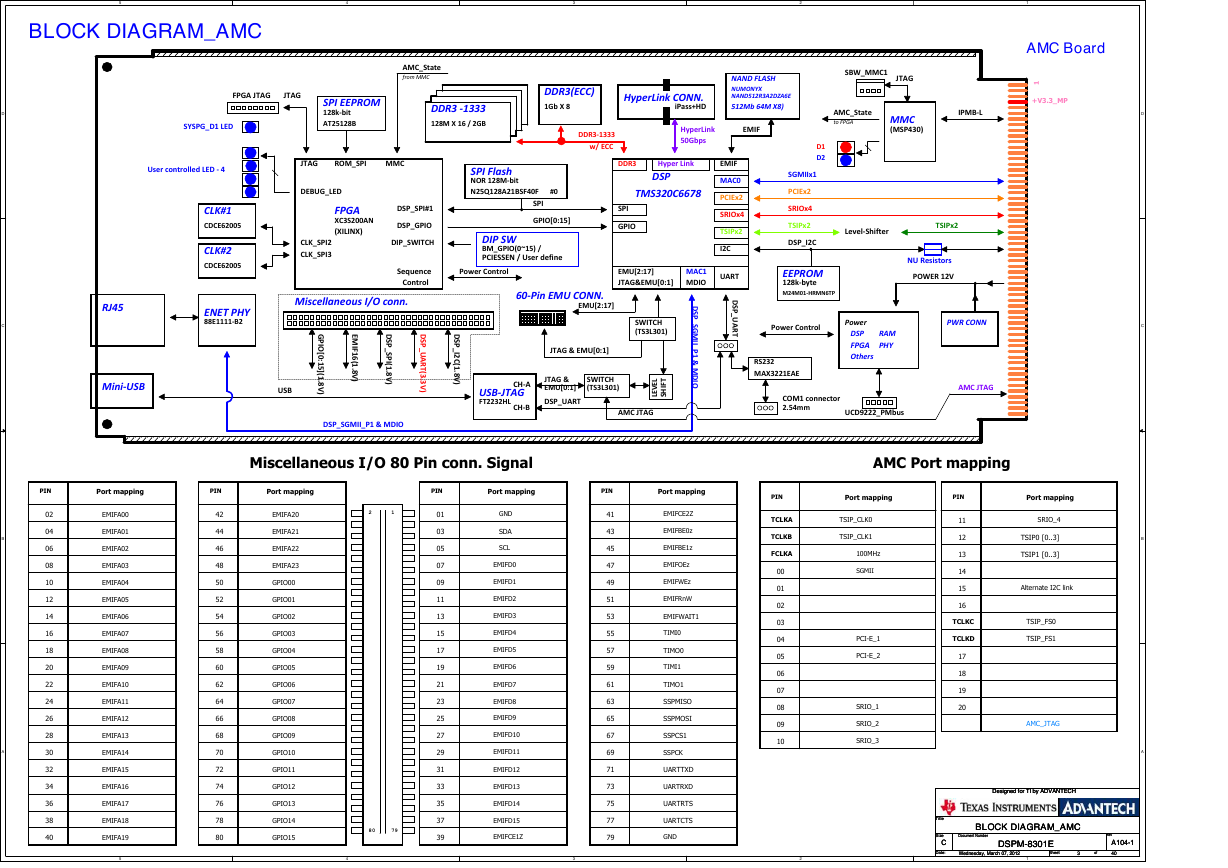

AMC Board

1

+V3.3_MP

BLOCK DIAGRAM_AMC

AMC_State

from MMC

FPGA JTAG

JTAG

SYSPG_D1 LED

SPI EEPROM

128k-bit

AT25128B

DDR3 -1333

128M X 16 / 2GB

User controlled LED - 4

JTAG

ROM_SPI

MMC

SPI Flash

NOR 128M-bit

DEBUG_LED

N25Q128A21BSF40F

#0

FPGA

XC3S200AN

(XILINX)

CLK_SPI2

CLK_SPI3

DSP_SPI#1

DSP_GPIO

DIP_SWITCH

Sequence

Control

SPI

GPIO[0:15]

SPI

GPIO

DIP SW

BM_GPIO(0~15) /

PCIESSEN / User define

Power Control

Miscellaneous I/O conn.

60-Pin EMU CONN.

EMU[2:17]

CLK#1

CDCE62005

CLK#2

CDCE62005

ENET PHY

88E1111-B2

RJ45

Mini-USB

USB

DDR3(ECC)

1Gb X 8

HyperLink CONN.

iPass+HD

NAND FLASH

NUMONYX

NAND512R3A2DZA6E

512Mb 64M X8)

DDR3-1333

w/ ECC

HyperLink

50Gbps

EMIF

DDR3

Hyper Link

EMIF

DSP

TMS320C6678

D1

D2

SGMIIx1

PCIEx2

SRIOx4

TSIPx2

DSP_I2C

MAC0

PCIEx2

SRIOx4

TSIPx2

I2C

EMU[2:17]

JTAG&EMU[0:1]

MAC1

MDIO

UART

SWITCH

(TS3L301)

D

S

P

_

S

G

M

D

S

P

_

U

A

R

T

EEPROM

128k-byte

M24M01-HRMN6TP

Power Control

G

P

I

O

[

0

:

1

5

]

(

1

.

8

V

)

E

M

I

F

1

6

(

1

.

8

V

)

D

S

P

_

S

P

I

(

1

.

8

V

)

D

S

P

_

U

A

R

T

(

3

.

3

V

)

D

S

P

_

I

2

C

(

1

.

8

V

)

DSP_SGMII_P1 & MDIO

JTAG & EMU[0:1]

JTAG &

EMU[0:1]

SWITCH

(TS3L301)

DSP_UART

L

E

V

E

L

T

F

I

H

S

AMC JTAG

I

I

_

P

1

&

M

D

O

I

USB-JTAG

FT2232HL

CH-A

CH-B

RS232

MAX3221EAE

COM1 connector

2.54mm

UCD9222_PMbus

Level-Shifter

TSIPx2

NU Resistors

POWER 12V

Power

DSP

FPGA

Others

RAM

PHY

PWR CONN

AMC JTAG

PIN

Port mapping

PIN

Port mapping

PIN

Port mapping

PIN

Port mapping

Miscellaneous I/O 80 Pin conn. Signal

AMC Port mapping

02

04

06

08

10

12

14

16

18

20

22

24

26

28

30

32

34

36

38

40

EMIFA00

EMIFA01

EMIFA02

EMIFA03

EMIFA04

EMIFA05

EMIFA06

EMIFA07

EMIFA08

EMIFA09

EMIFA10

EMIFA11

EMIFA12

EMIFA13

EMIFA14

EMIFA15

EMIFA16

EMIFA17

EMIFA18

EMIFA19

5

42

44

46

48

50

52

54

56

58

60

62

64

66

68

70

72

74

76

78

80

EMIFA20

EMIFA21

EMIFA22

EMIFA23

GPIO00

GPIO01

GPIO02

GPIO03

GPIO04

GPIO05

GPIO06

GPIO07

GPIO08

GPIO09

GPIO10

GPIO11

GPIO12

GPIO13

GPIO14

GPIO15

2

1

80

79

01

03

05

07

09

11

13

15

17

19

21

23

25

27

29

31

33

35

37

39

GND

SDA

SCL

EMIFD0

EMIFD1

EMIFD2

EMIFD3

EMIFD4

EMIFD5

EMIFD6

EMIFD7

EMIFD8

EMIFD9

EMIFD10

EMIFD11

EMIFD12

EMIFD13

EMIFD14

EMIFD15

EMIFCE1Z

41

43

45

47

49

51

53

55

57

59

61

63

65

67

69

71

73

75

77

79

EMIFCE2Z

EMIFBE0z

EMIFBE1z

EMIFOEz

EMIFWEz

EMIFRnW

EMIFWAIT1

TIMI0

TIMO0

TIMI1

TIMO1

SSPMISO

SSPMOSI

SSPCS1

SSPCK

UARTTXD

UARTRXD

UARTRTS

UARTCTS

GND

4

3

2

PIN

TCLKA

TCLKB

FCLKA

00

01

02

03

04

05

06

07

08

09

10

Port mapping

PIN

Port mapping

TSIP_CLK0

TSIP_CLK1

100MHz

SGMII

PCI-E_1

PCI-E_2

SRIO_1

SRIO_2

SRIO_3

11

12

13

14

15

16

TCLKC

TCLKD

17

18

19

20

SRIO_4

TSIP0 [0..3]

TSIP1 [0..3]

Alternate I2C link

TSIP_FS0

TSIP_FS1

AMC_JTAG

Designed for TI by ADVANTECH

Designed for TI by ADVANTECH

Designed for TI by ADVANTECH

Title

Title

Title

Size

Size

Size

C

C

C

Date:

Date:

Date:

BLOCK DIAGRAM_AMC

BLOCK DIAGRAM_AMC

BLOCK DIAGRAM_AMC

Document Number

Document Number

Document Number

DSPM-8301E

DSPM-8301E

DSPM-8301E

Wednesday, March 07, 2012

Wednesday, March 07, 2012

Wednesday, March 07, 2012

1

Sheet

Sheet

Sheet

3

3

3

of

of

of

Rev

Rev

Rev

A104-1

A104-1

A104-1

40

40

40

D

C

B

A

�

5

4

3

2

1

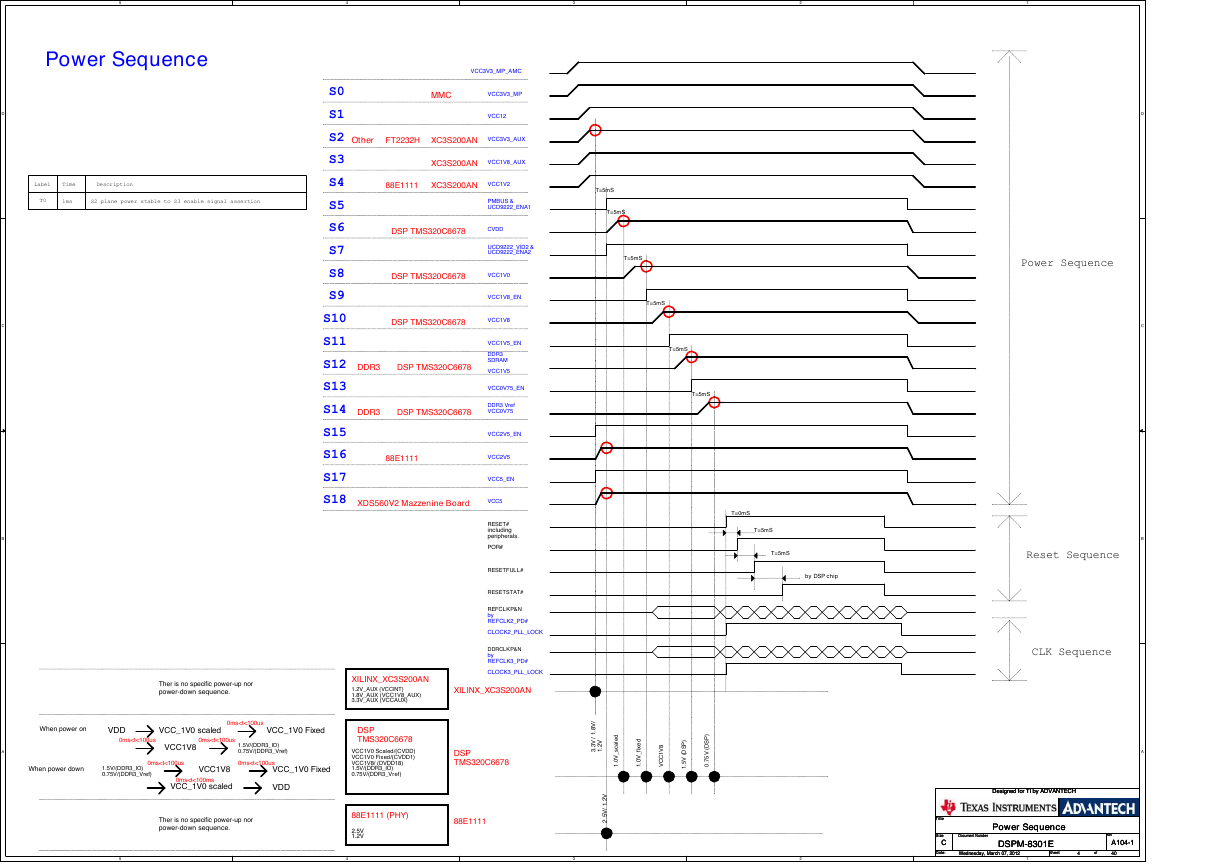

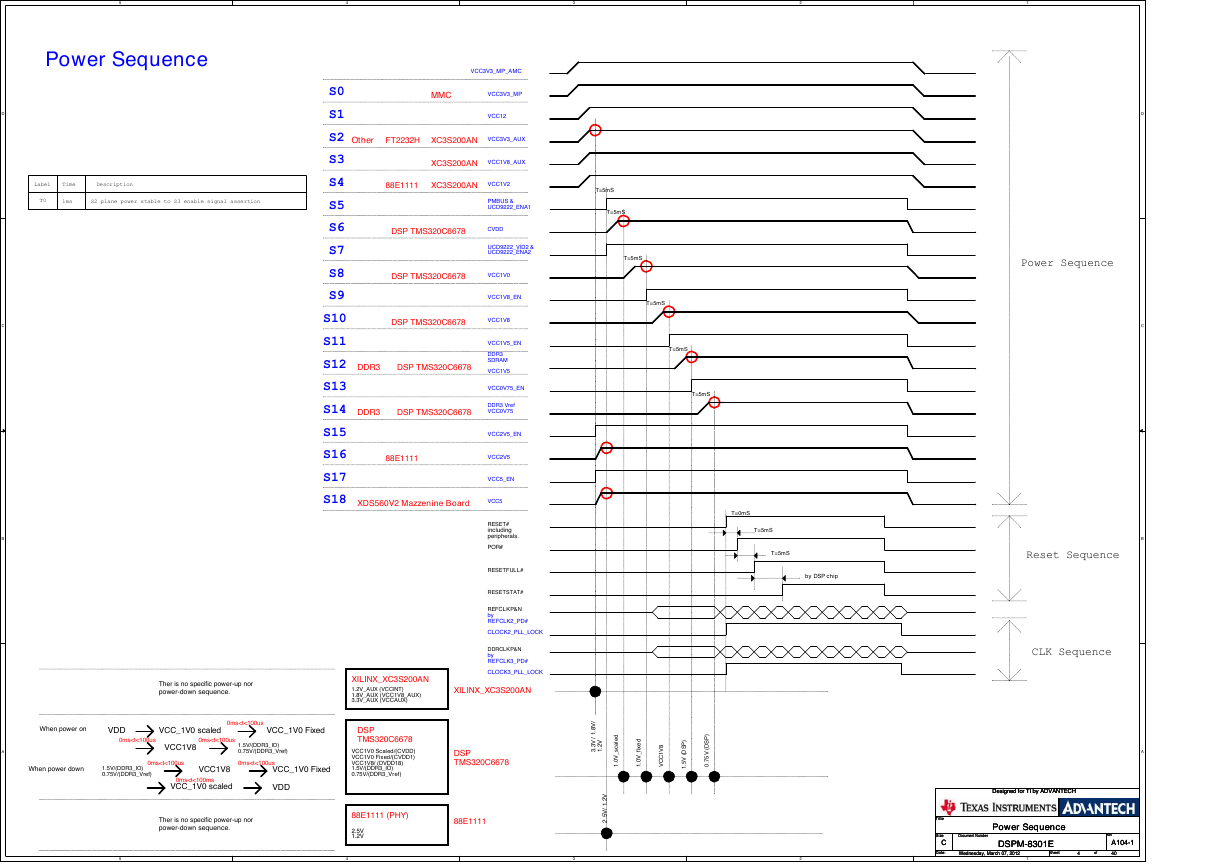

Power Sequence

Label

Time

Description

T0

1ms

S2 plane power stable to S3 enable signal assertion

VCC3V3_MP_AMC

MMC

VCC3V3_MP

VCC12

Other

FT2232H

XC3S200AN

VCC3V3_AUX

XC3S200AN

VCC1V8_AUX

88E1111

XC3S200AN

VCC1V2

PMBUS &

UCD9222_ENA1

DSP TMS320C6678

CVDD

T=5mS

T=5mS

UCD9222_VID2 &

UCD9222_ENA2

T=5mS

DSP TMS320C6678

VCC1V0

VCC1V8_EN

T=5mS

DSP TMS320C6678

VCC1V8

DDR3

DSP TMS320C6678

DDR3

DSP TMS320C6678

88E1111

VCC1V5_EN

DDR3

SDRAM

VCC1V5

VCC0V75_EN

DDR3 Vref

VCC0V75

VCC2V5_EN

VCC2V5

VCC5_EN

T=5mS

T=5mS

S0

S1

S2

S3

S4

S5

S6

S7

S8

S9

S10

S11

S12

S13

S14

S15

S16

S17

S18 XDS560V2 Mazzenine Board

VCC5

D

C

B

A

D

C

B

A

Power Sequence

Reset Sequence

CLK Sequence

RESET#

including

peripherals.

POR#

RESETFULL#

RESETSTAT#

REFCLKP&N

by

REFCLK2_PD#

CLOCK2_PLL_LOCK

DDRCLKP&N

by

REFCLK3_PD#

CLOCK3_PLL_LOCK

XILINX_XC3S200AN

DSP

TMS320C6678

XILINX_XC3S200AN

1.2V_AUX (VCCINT)

1.8V_AUX (VCC1V8_AUX)

3.3V_AUX (VCCAUX)

DSP

TMS320C6678

VCC1V0 Scaled/(CVDD)

VCC1V0 Fixed/(CVDD1)

VCC1V8/ (DVDD18)

1.5V/(DDR3_IO)

0.75V/(DDR3_Vref)

T=0mS

T=5mS

T=5mS

by DSP chip

)

P

S

D

(

V

5

7

0

.

l

d

e

a

c

s

_

V

0

1

.

d

e

x

i

f

_

V

0

1

.

8

V

1

C

C

V

)

P

S

D

(

V

5

1

.

/

V

8

1

.

/

V

3

3

.

V

2

.

1

88E1111 (PHY)

88E1111

2.5V

1.2V

4

V

2

.

1

/

V

5

.

2

3

2

Designed for TI by ADVANTECH

Designed for TI by ADVANTECH

Designed for TI by ADVANTECH

Title

Title

Title

Size

Size

Size

C

C

C

Date:

Date:

Date:

Document Number

Document Number

Document Number

Power Sequence

Power Sequence

Power Sequence

DSPM-8301E

DSPM-8301E

DSPM-8301E

Wednesday, March 07, 2012

Wednesday, March 07, 2012

Wednesday, March 07, 2012

1

Sheet

Sheet

Sheet

4

4

4

of

of

of

Rev

Rev

Rev

A104-1

A104-1

A104-1

40

40

40

Ther is no specific power-up nor

power-down sequence.

When power on

VDD

VCC_1V0 scaled

0ms

5

4

3

2

1

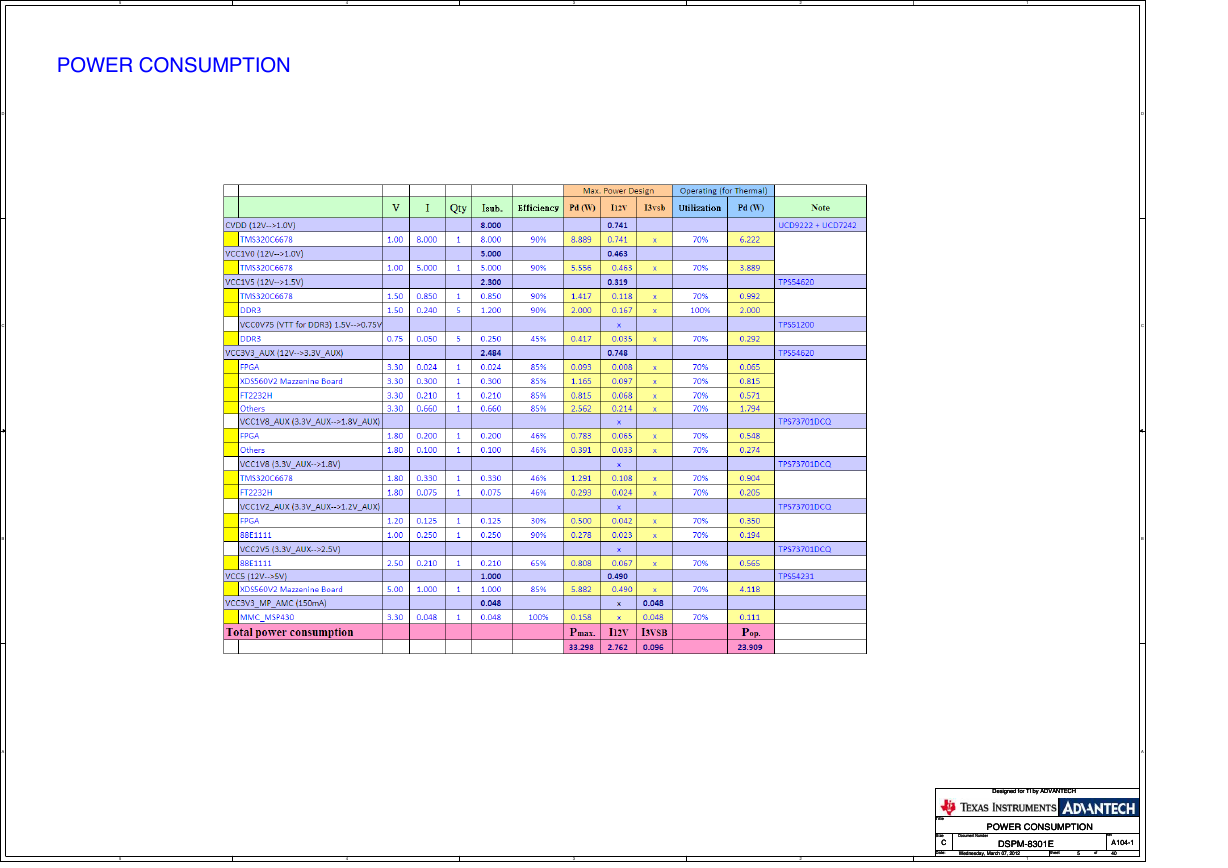

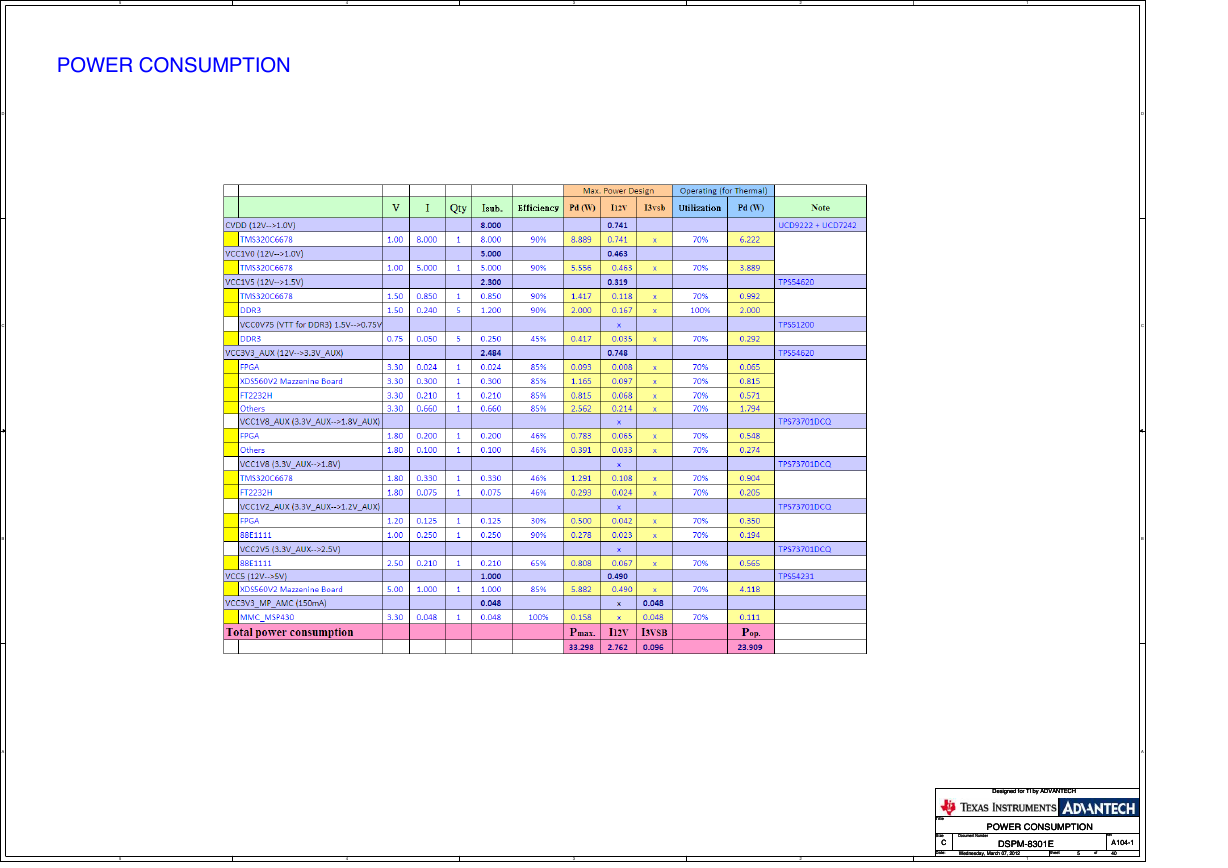

POWER CONSUMPTION

D

C

B

A

D

C

B

A

5

4

3

2

Designed for TI by ADVANTECH

Designed for TI by ADVANTECH

Designed for TI by ADVANTECH

Title

Title

Title

Size

Size

Size

C

C

C

Date:

Date:

Date:

POWER CONSUMPTION

POWER CONSUMPTION

POWER CONSUMPTION

Document Number

Document Number

Document Number

DSPM-8301E

DSPM-8301E

DSPM-8301E

Wednesday, March 07, 2012

Wednesday, March 07, 2012

Wednesday, March 07, 2012

1

Sheet

Sheet

Sheet

5

5

5

of

of

of

Rev

Rev

Rev

A104-1

A104-1

A104-1

40

40

40

�

5

4

3

2

1

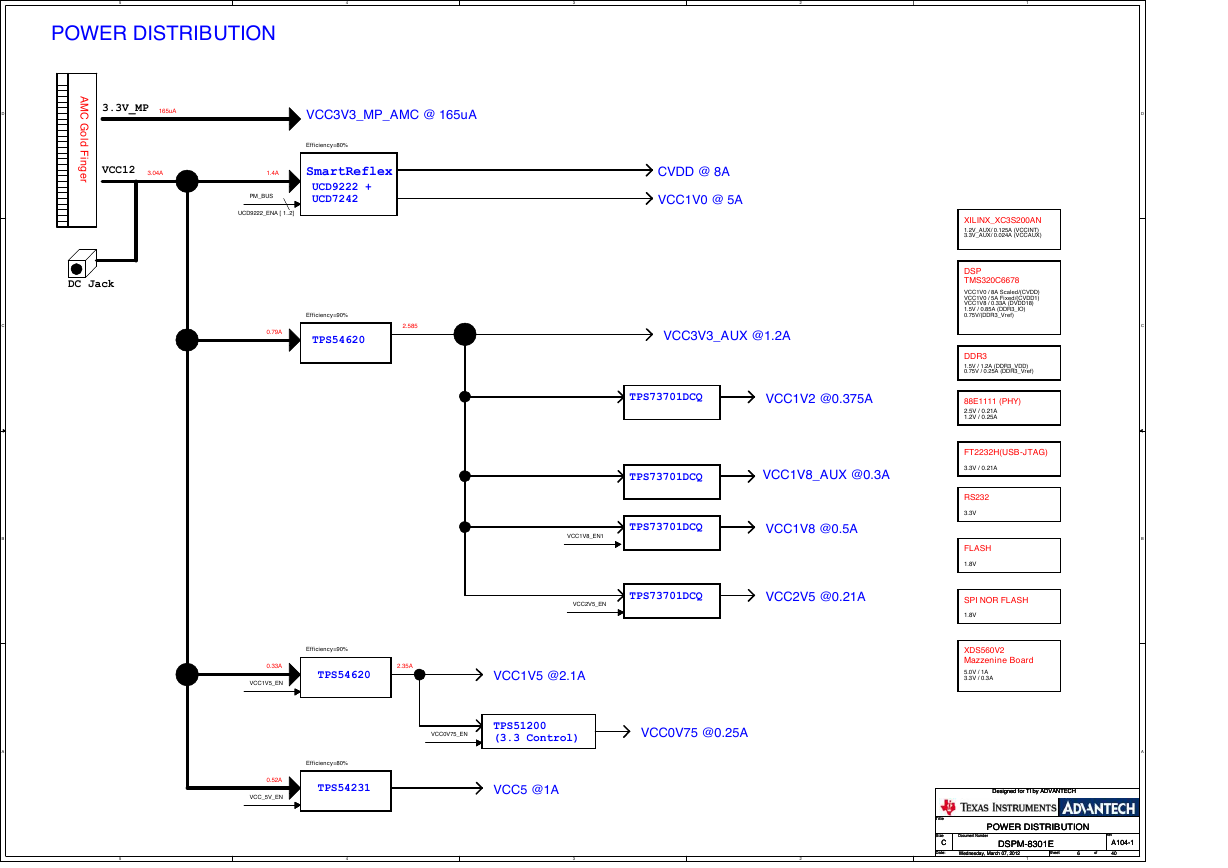

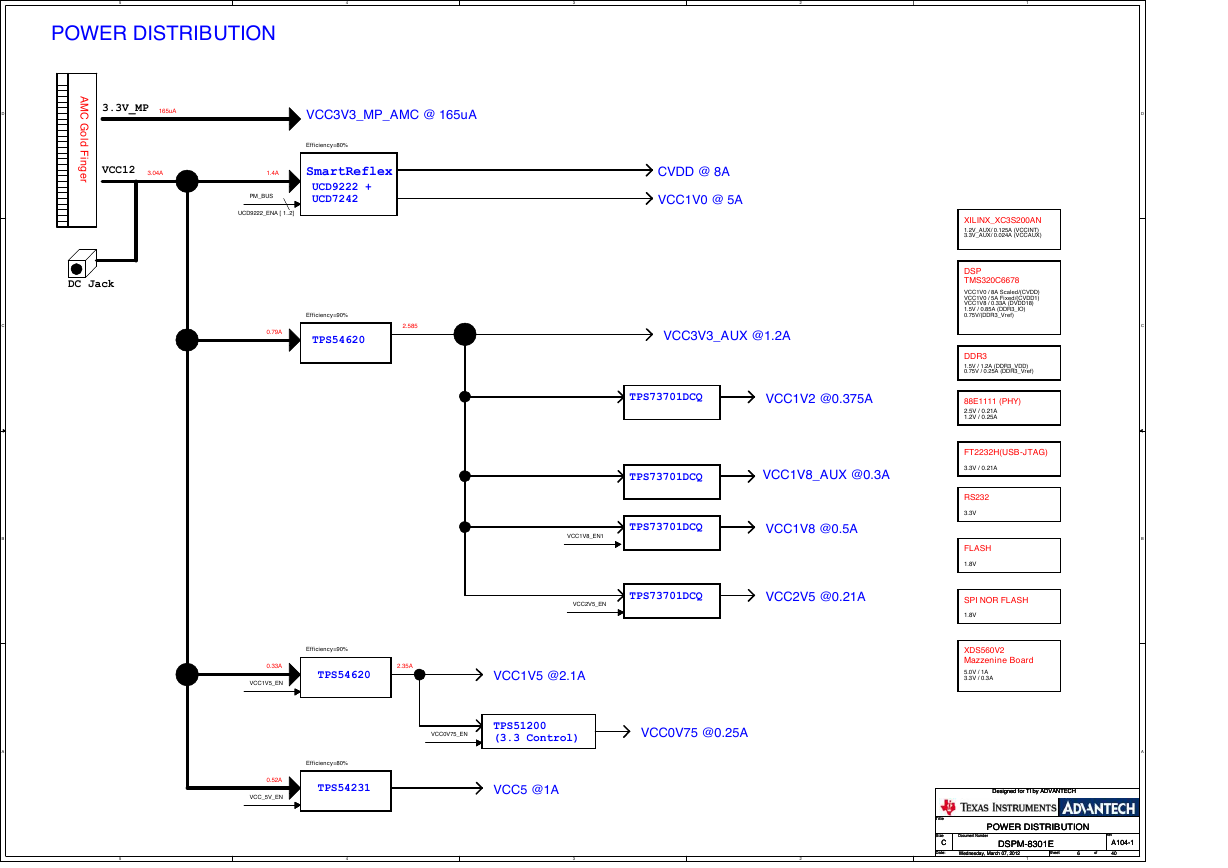

POWER DISTRIBUTION

D

C

B

A

A

M

C

G

o

d

F

n

g

e

r

i

l

3.3V_MP

165uA

VCC12

3.04A

VCC3V3_MP_AMC @ 165uA

Efficiency=80%

SmartReflex

UCD9222 +

UCD7242

1.4A

PM_BUS

UCD9222_ENA [ 1..2]

CVDD @ 8A

VCC1V0 @ 5A

DC Jack

Efficiency=90%

0.79A

TPS54620

2.585

VCC3V3_AUX @1.2A

TPS73701DCQ

VCC1V2 @0.375A

TPS73701DCQ

VCC1V8_AUX @0.3A

VCC1V8_EN1

TPS73701DCQ

VCC1V8 @0.5A

VCC2V5_EN

TPS73701DCQ

VCC2V5 @0.21A

Efficiency=90%

0.33A

VCC1V5_EN

TPS54620

2.35A

VCC1V5 @2.1A

VCC0V75_EN

TPS51200

(3.3 Control)

VCC0V75 @0.25A

Efficiency=80%

TPS54231

0.52A

VCC_5V_EN

VCC5 @1A

5

4

3

2

D

C

B

A

XILINX_XC3S200AN

1.2V_AUX/ 0.125A (VCCINT)

3.3V_AUX/ 0.024A (VCCAUX)

DSP

TMS320C6678

VCC1V0 / 8A Scaled/(CVDD)

VCC1V0 / 5A Fixed/(CVDD1)

VCC1V8 / 0.33A (DVDD18)

1.5V / 0.85A (DDR3_IO)

0.75V/(DDR3_Vref)

DDR3

1.5V / 1.2A (DDR3_VDD)

0.75V / 0.25A (DDR3_Vref)

88E1111 (PHY)

2.5V / 0.21A

1.2V / 0.25A

FT2232H(USB-JTAG)

3.3V / 0.21A

RS232

3.3V

FLASH

1.8V

SPI NOR FLASH

1.8V

XDS560V2

Mazzenine Board

5.0V / 1A

3.3V / 0.3A

Designed for TI by ADVANTECH

Designed for TI by ADVANTECH

Designed for TI by ADVANTECH

Title

Title

Title

Size

Size

Size

C

C

C

Date:

Date:

Date:

POWER DISTRIBUTION

POWER DISTRIBUTION

POWER DISTRIBUTION

Document Number

Document Number

Document Number

DSPM-8301E

DSPM-8301E

DSPM-8301E

Wednesday, March 07, 2012

Wednesday, March 07, 2012

Wednesday, March 07, 2012

1

Sheet

Sheet

Sheet

6

6

6

of

of

of

Rev

Rev

Rev

A104-1

A104-1

A104-1

40

40

40

�

5

4

3

2

1

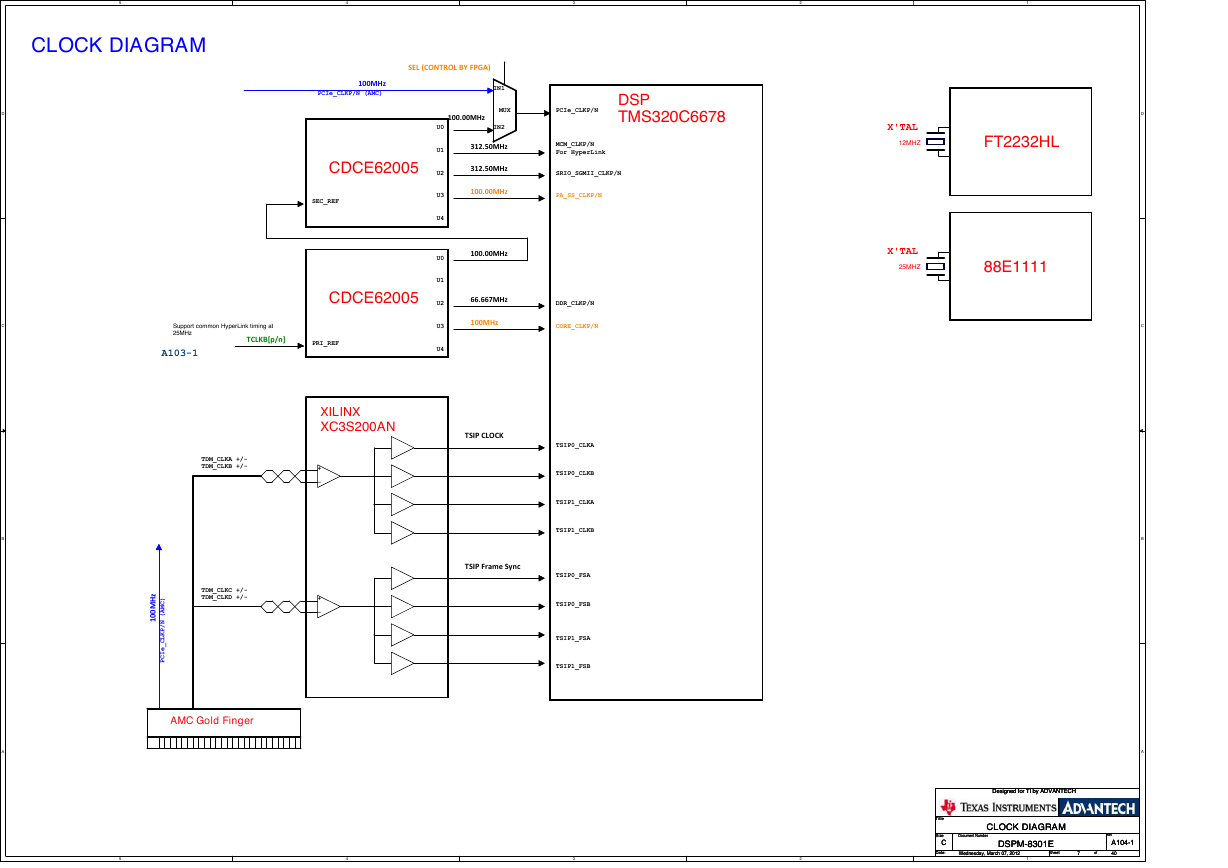

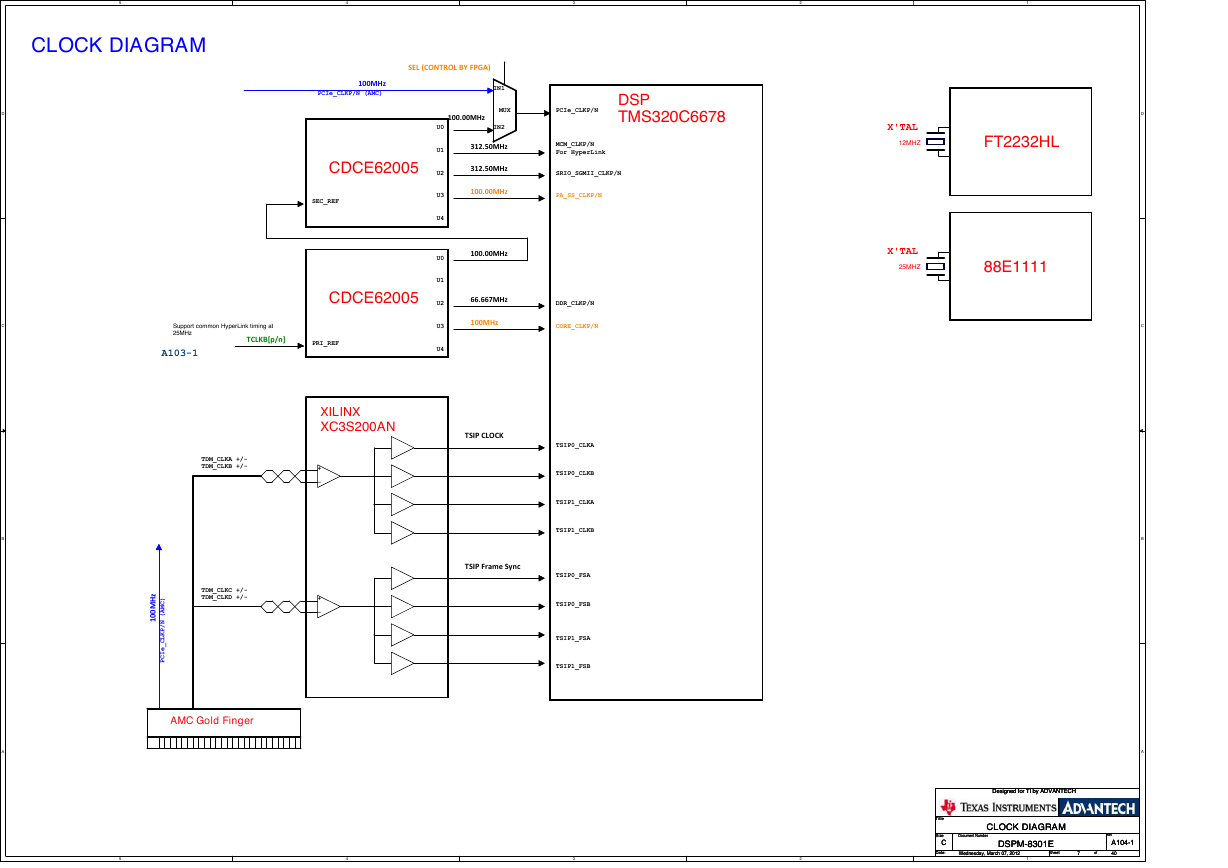

CLOCK DIAGRAM

SEL (CONTROL BY FPGA)

IN1

MUX

IN2

100.00MHz

PCIe_CLKP/N

DSP

TMS320C6678

100MHz

PCIe_CLKP/N (AMC)

CDCE62005

SEC_REF

CDCE62005

Support common HyperLink timing at

25MHz

TCLKB[p/n]

PRI_REF

A103-1

U0

U1

U2

U3

U4

U0

U1

U2

U3

U4

312.50MHz

312.50MHz

100.00MHz

100.00MHz

66.667MHz

100MHz

XILINX

XC3S200AN

TSIP CLOCK

TDM_CLKA +/-

TDM_CLKB +/-

TDM_CLKC +/-

TDM_CLKD +/-

+

-

+

-

z

H

M

0

0

1

)

C

M

A

(

N

/

P

K

L

C

_

e

I

C

P

AMC Gold Finger

TSIP Frame Sync

D

C

B

A

MCM_CLKP/N

For HyperLink

SRIO_SGMII_CLKP/N

PA_SS_CLKP/N

DDR_CLKP/N

CORE_CLKP/N

TSIP0_CLKA

TSIP0_CLKB

TSIP1_CLKA

TSIP1_CLKB

TSIP0_FSA

TSIP0_FSB

TSIP1_FSA

TSIP1_FSB

X'TAL

12MHZ

FT2232HL

X'TAL

25MHZ

88E1111

D

C

B

A

5

4

3

2

Designed for TI by ADVANTECH

Designed for TI by ADVANTECH

Designed for TI by ADVANTECH

Title

Title

Title

Size

Size

Size

C

C

C

Date:

Date:

Date:

CLOCK DIAGRAM

CLOCK DIAGRAM

CLOCK DIAGRAM

Document Number

Document Number

Document Number

DSPM-8301E

DSPM-8301E

DSPM-8301E

Wednesday, March 07, 2012

Wednesday, March 07, 2012

Wednesday, March 07, 2012

1

Sheet

Sheet

Sheet

7

7

7

of

of

of

Rev

Rev

Rev

A104-1

A104-1

A104-1

40

40

40

�

D

C

B

A

5

4

3

2

1

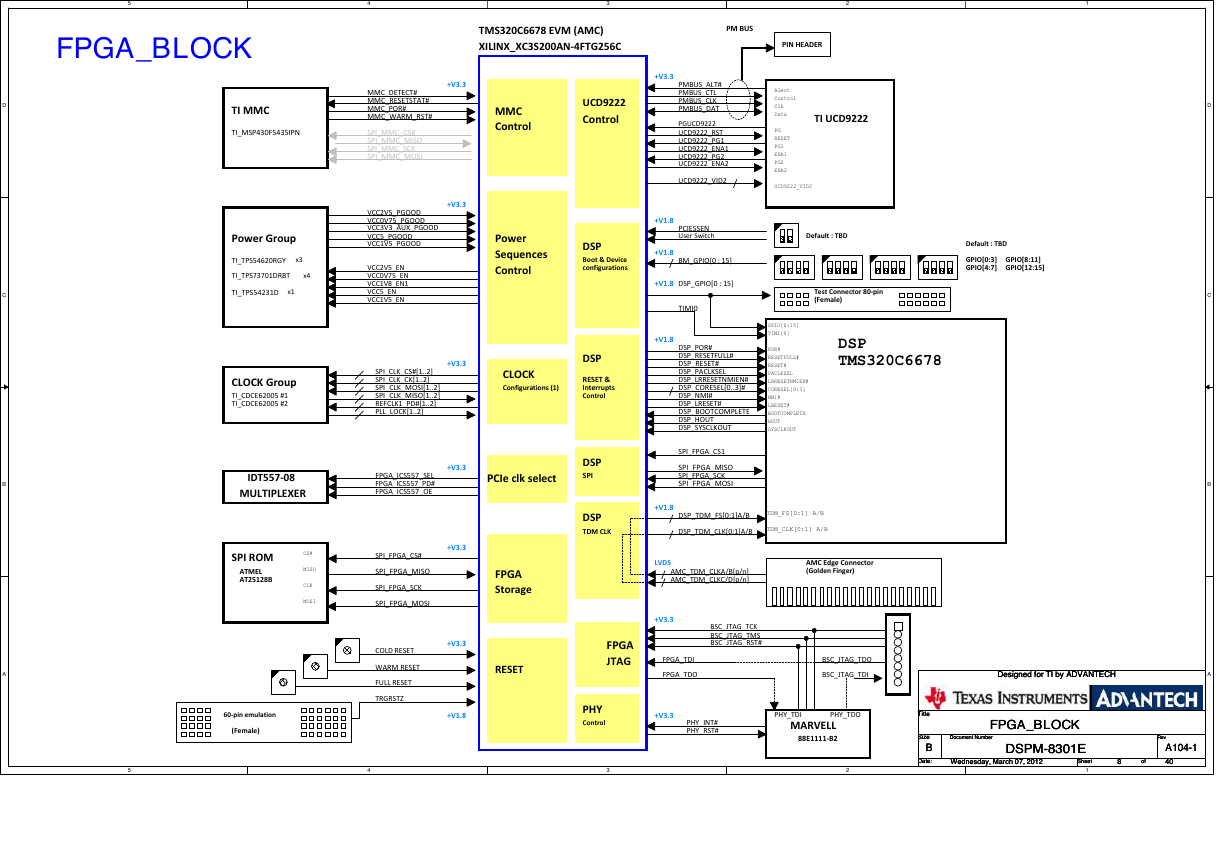

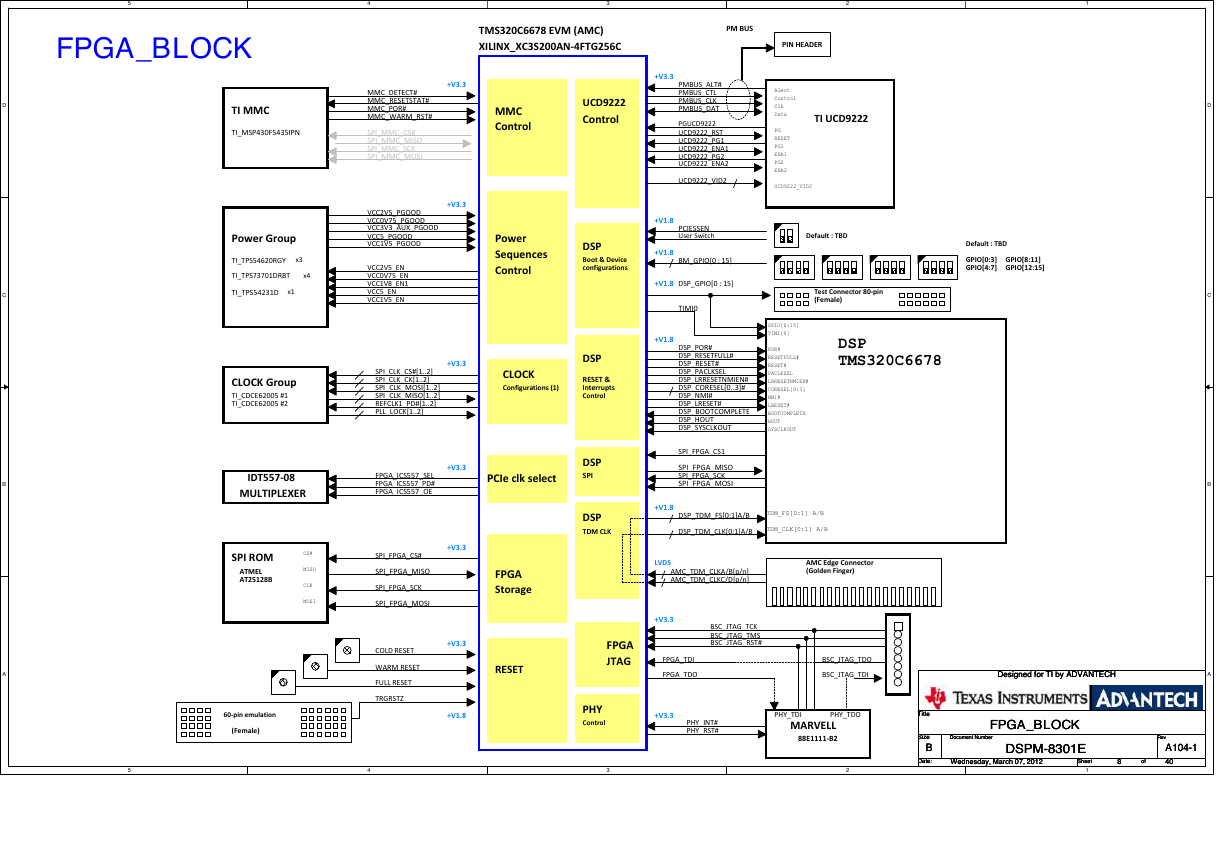

FPGA_BLOCK

TMS320C6678 EVM (AMC)

XILINX_XC3S200AN-4FTG256C

PM BUS

PIN HEADER

TI MMC

TI_MSP430F5435IPN

Power Group

TI_TPS54620RGY

x3

TI_TPS73701DRBT

x4

TI_TPS54231D

x1

+V3.3

MMC_DETECT#

MMC_RESETSTAT#

MMC_POR#

MMC_WARM_RST#

SPI_MMC_CS#

SPI_MMC_MISO

SPI_MMC_SCK

SPI_MMC_MOSI

+V3.3

VCC2V5_PGOOD

VCC0V75_PGOOD

VCC3V3_AUX_PGOOD

VCC5_PGOOD

VCC1V5_PGOOD

VCC2V5_EN

VCC0V75_EN

VCC1V8_EN1

VCC5_EN

VCC1V5_EN

MMC

Control

UCD9222

Control

Power

Sequences

Control

DSP

Boot & Device

configurations

CLOCK Group

TI_CDCE62005 #1

TI_CDCE62005 #2

+V3.3

SPI_CLK_CS#[1..2]

SPI_CLK_CK[1..2]

SPI_CLK_MOSI[1..2]

SPI_CLK_MISO[1..2]

REFCLK1_PD#[1..2]

PLL_LOCK[1..2]

CLOCK

Configurations (1)

IDT557-08

MULTIPLEXER

FPGA_ICS557_SEL

FPGA_ICS557_PD#

FPGA_ICS557_OE

+V3.3

PCIe clk select

DSP

RESET &

Interrupts

Control

DSP

SPI

DSP

TDM CLK

Default : TBD

GPIO[0:3]

GPIO[4:7] GPIO[12:15]

GPIO[8:11]

TI UCD9222

Alert

Control

Clk

Data

PG

RESET

PG1

ENA1

PG2

ENA2

UCD9222_VID2

Default : TBD

Test Connector 80-pin

(Female)

DSP

TMS320C6678

GPIO[0:15]

TIMI[0]

POR#

RESETFULL#

RESET#

PACLKSEL

LRRESETNMIEN#

CORESEL[0:3]

NMI#

LRESET#

BOOTCOMPLETE

HOUT

SYSCLKOUT

+V3.3

PMBUS_ALT#

PMBUS_CTL

PMBUS_CLK

PMBUS_DAT

PGUCD9222

UCD9222_RST

UCD9222_PG1

UCD9222_ENA1

UCD9222_PG2

UCD9222_ENA2

UCD9222_VID2

PCIESSEN

User Switch

+V1.8

+V1.8

BM_GPIO[0 : 15]

+V1.8

DSP_GPIO[0 : 15]

TIMI0

+V1.8

DSP_POR#

DSP_RESETFULL#

DSP_RESET#

DSP_PACLKSEL

DSP_LRRESETNMIEN#

DSP_CORESEL[0..3]#

DSP_NMI#

DSP_LRESET#

DSP_BOOTCOMPLETE

DSP_HOUT

DSP_SYSCLKOUT

SPI_FPGA_CS1

SPI_FPGA_MISO

SPI_FPGA_SCK

SPI_FPGA_MOSI

+V1.8

DSP_TDM_FS[0:1]A/B

TDM_FS[0:1] A/B

DSP_TDM_CLK[0:1]A/B

TDM_CLK[0:1] A/B

LVDS

AMC_TDM_CLKA/B[p/n]

AMC_TDM_CLKC/D[p/n]

AMC Edge Connector

(Golden Finger)

SPI ROM

ATMEL

AT25128B

CS#

MISO

CLK

MOSI

60-pin emulation

(Female)

SPI_FPGA_CS#

SPI_FPGA_MISO

SPI_FPGA_SCK

SPI_FPGA_MOSI

COLD RESET

WARM RESET

FULL RESET

TRGRSTZ

+V3.3

+V3.3

+V1.8

FPGA

Storage

RESET

5

4

FPGA

JTAG

+V3.3

FPGA_TDI

FPGA_TDO

BSC_JTAG_TCK

BSC_JTAG_TMS

BSC_JTAG_RST#

BSC_JTAG_TDO

BSC_JTAG_TDI

Designed for TI by ADVANTECH

Designed for TI by ADVANTECH

Designed for TI by ADVANTECH

PHY

Control

3

+V3.3

PHY_TDI

PHY_TDO

PHY_INT#

PHY_RST#

MARVELL

88E1111-B2

2

Title

Title

Title

Size

Size

Size

B

B

B

Date:

Date:

Date:

FPGA_BLOCK

FPGA_BLOCK

FPGA_BLOCK

Document Number

Document Number

Document Number

DSPM-8301E

DSPM-8301E

DSPM-8301E

Wednesday, March 07, 2012

Wednesday, March 07, 2012

Wednesday, March 07, 2012

Sheet

Sheet

Sheet

1

8

8

8

of

of

of

Rev

Rev

Rev

A104-1

A104-1

A104-1

40

40

40

D

C

B

A

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc