华侨大学电子工程系

集成电路设计与分析实验 B

(模拟集成电路分析与设计课程实验)

实验(八)

寄生参数提取及后仿真

华侨大学厦门专用集成电路系统重点实验室

-2011-

�

集成电路设计与分析实验 B(八)

一、实验目的

1.熟练掌握使用 Cadence Virtuoso ADE5.1.41 软件进行原理图的编辑

2.使用 Calibre 进行 Layout 寄生参数提取

3.使用 Spectre 对提取的寄生参数进行后仿验证

二、实验软件:

Cadence IC Virtuoso ADE 5.1.41 及 Calibre2008

三、实验要求:

实验前请做好预习工作,实验后请做好练习,较熟练地使用 Virtuoso 软件对原理图进行编

辑并熟练掌握常用的几种低频模拟电路的分析方法。

集成电路分析与设计实验 B(八)

教学任务 寄生参数提取及后仿验证

学时

3

专业能力:

1.熟练掌握原理图编辑软件的使用

2.使用 Calibre 对 Layout 进行寄生参数进行提取

3.使用 Spectre 对提取的寄生参数进行后仿验证

4.前仿结果和后仿结果对比

1. Calibre 进行寄生参数提取

2. Cadence ADE5.1.41 对提取电路后仿验证

教学目标

教学内容

重点 寄生参数提取及后仿验证

难点 寄生参数提取及后仿验证

华侨大学电子工程系(The Department of Electronic Engineering Huaqiao University)1

华侨大学厦门专用集成电路系统重点实验室

�

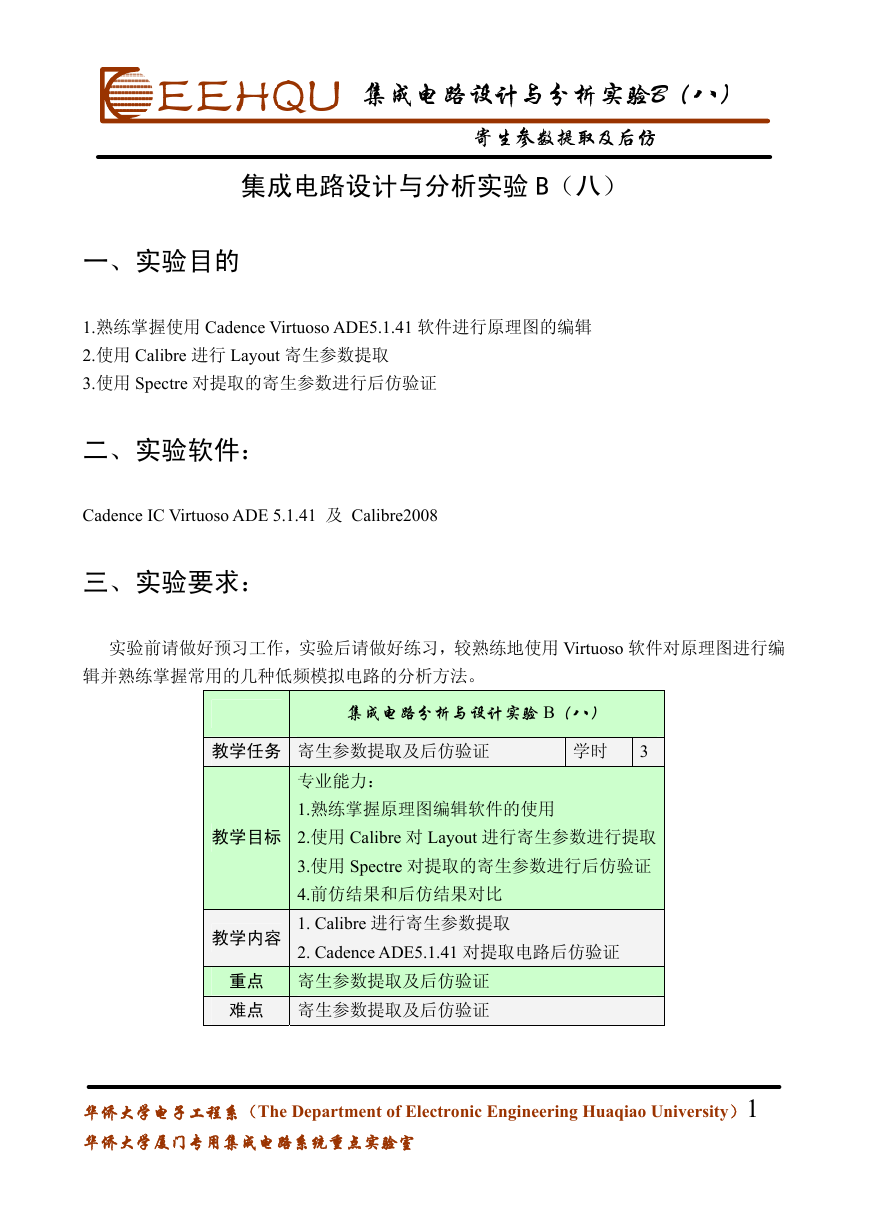

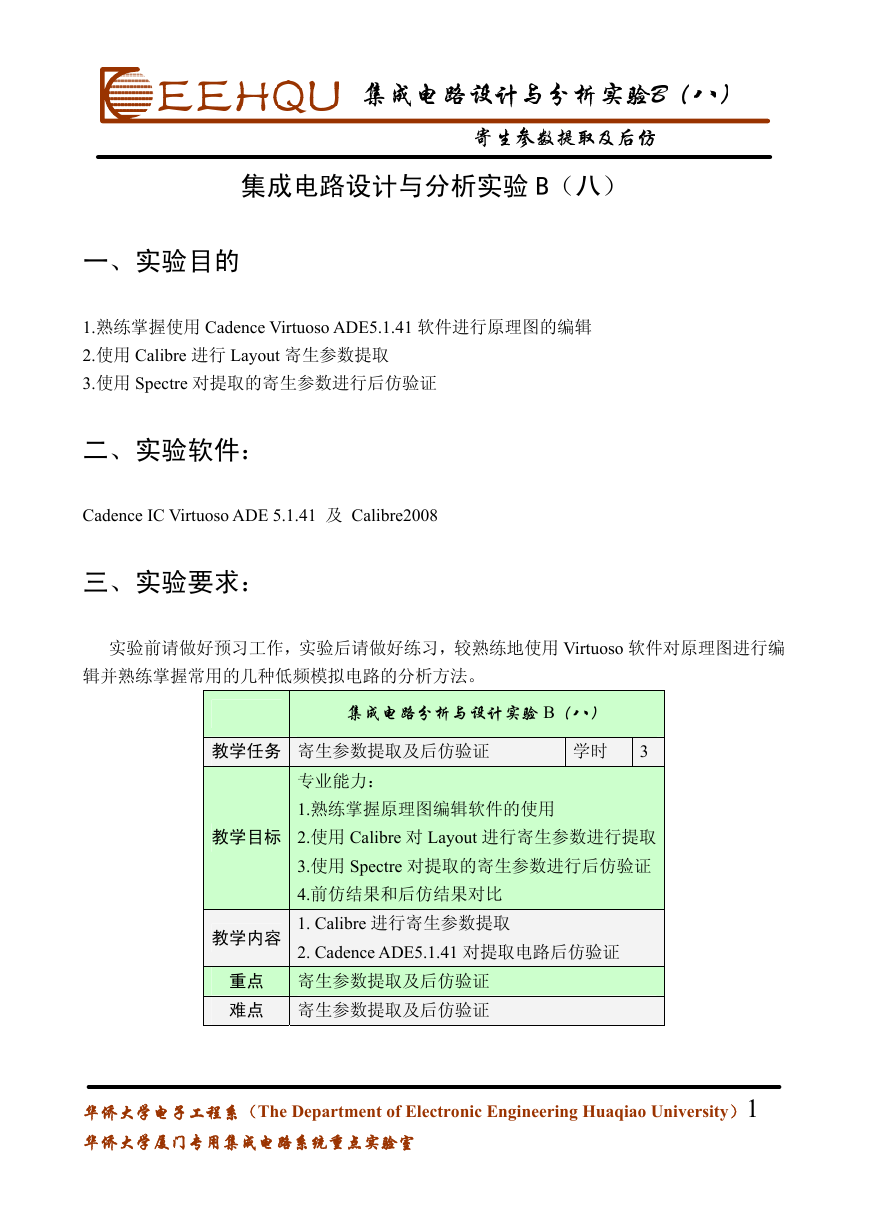

第一部分 分层次模块调用

实验内容:

分层次设计方法:

复杂的电路需要使用分模块设计的方法来使设计的电路看起来更加简单明了。

如下例:整体系统图

系统里面模块电路

华侨大学电子工程系(The Department of Electronic Engineering Huaqiao University)2

华侨大学厦门专用集成电路系统重点实验室

�

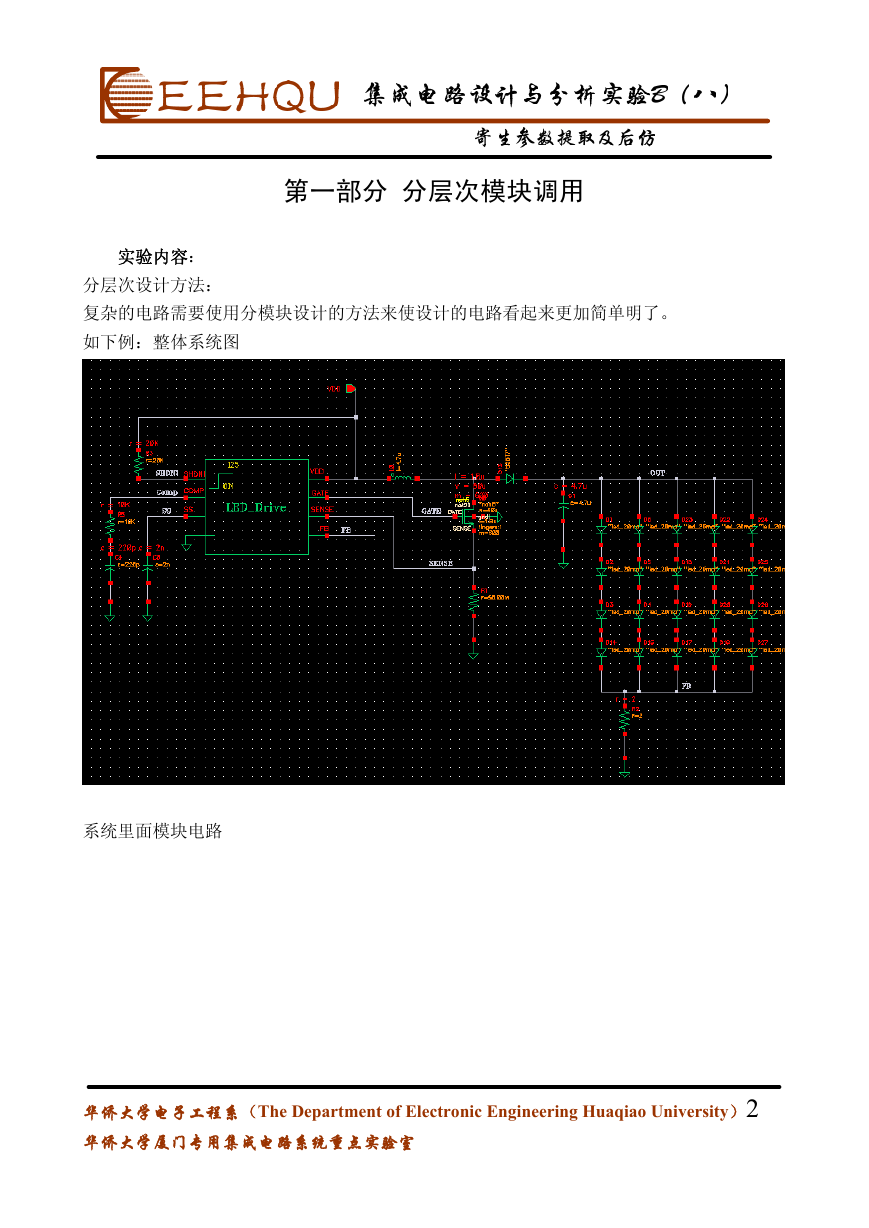

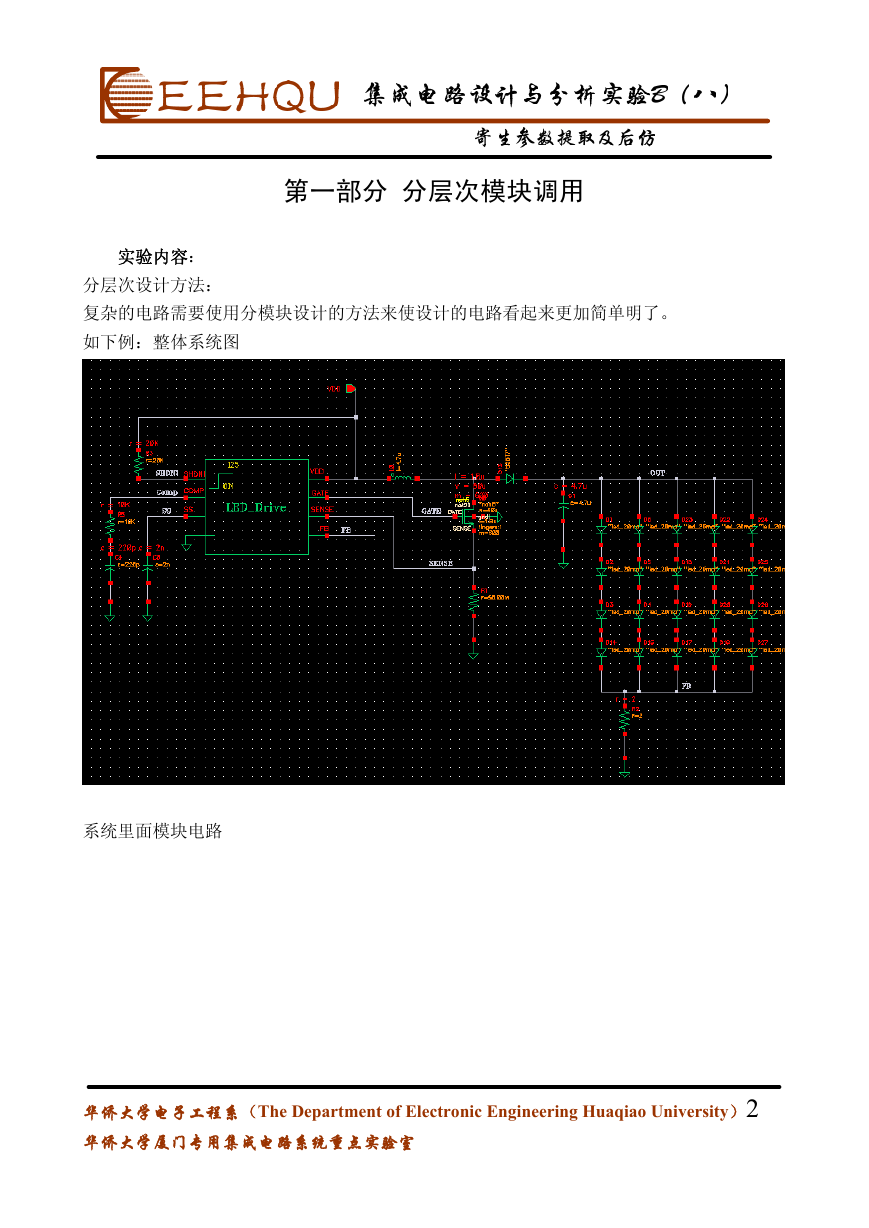

模块电路的下一级子模块

模块电路的电路

华侨大学电子工程系(The Department of Electronic Engineering Huaqiao University)3

华侨大学厦门专用集成电路系统重点实验室

�

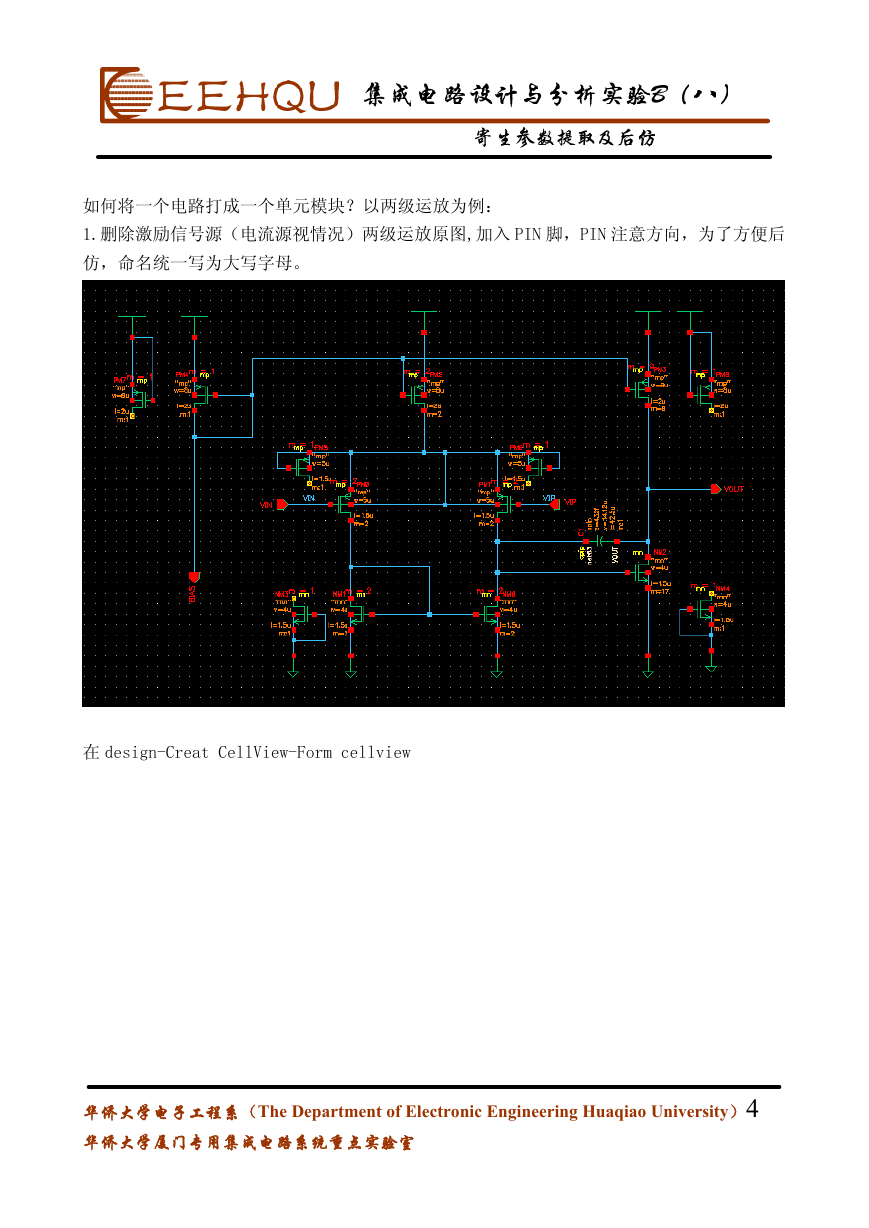

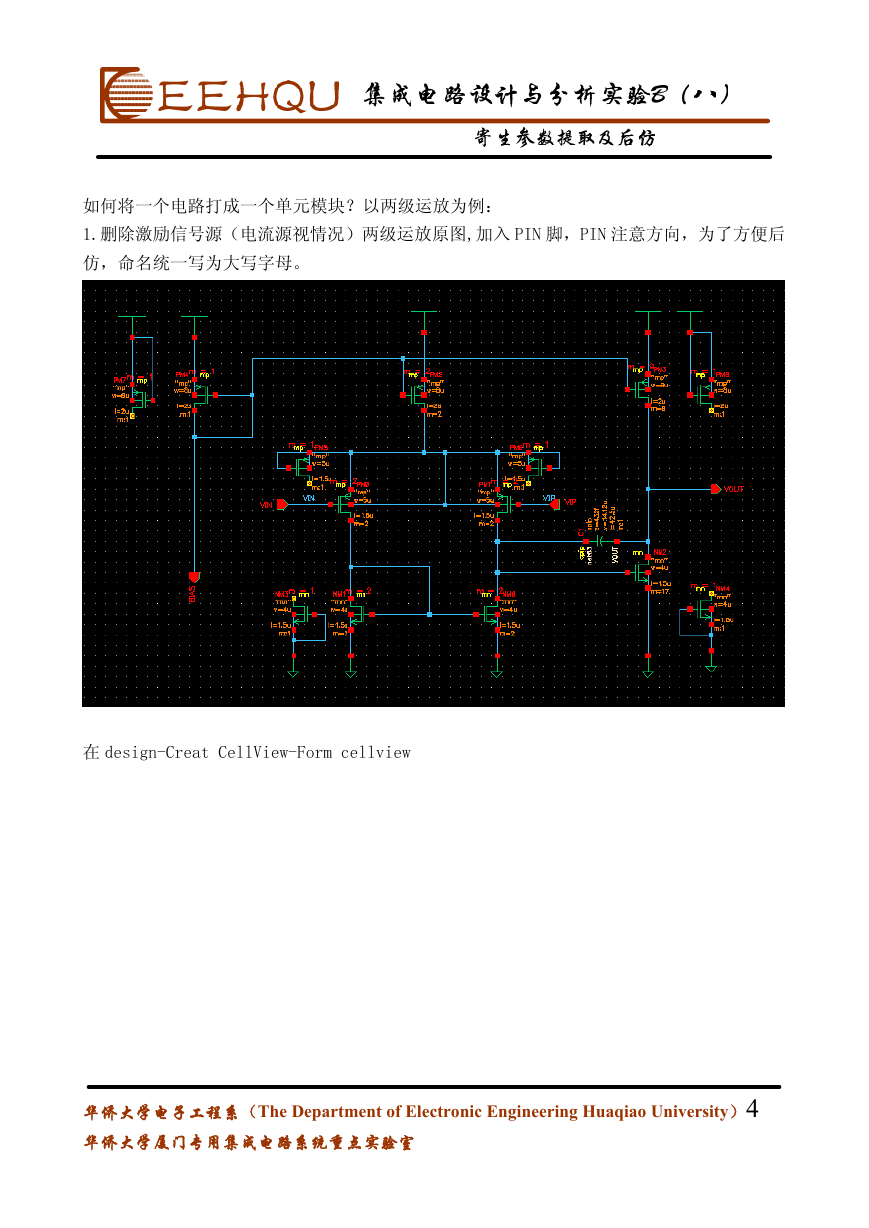

如何将一个电路打成一个单元模块?以两级运放为例:

1.删除激励信号源(电流源视情况)两级运放原图,加入 PIN 脚,PIN 注意方向,为了方便后

仿,命名统一写为大写字母。

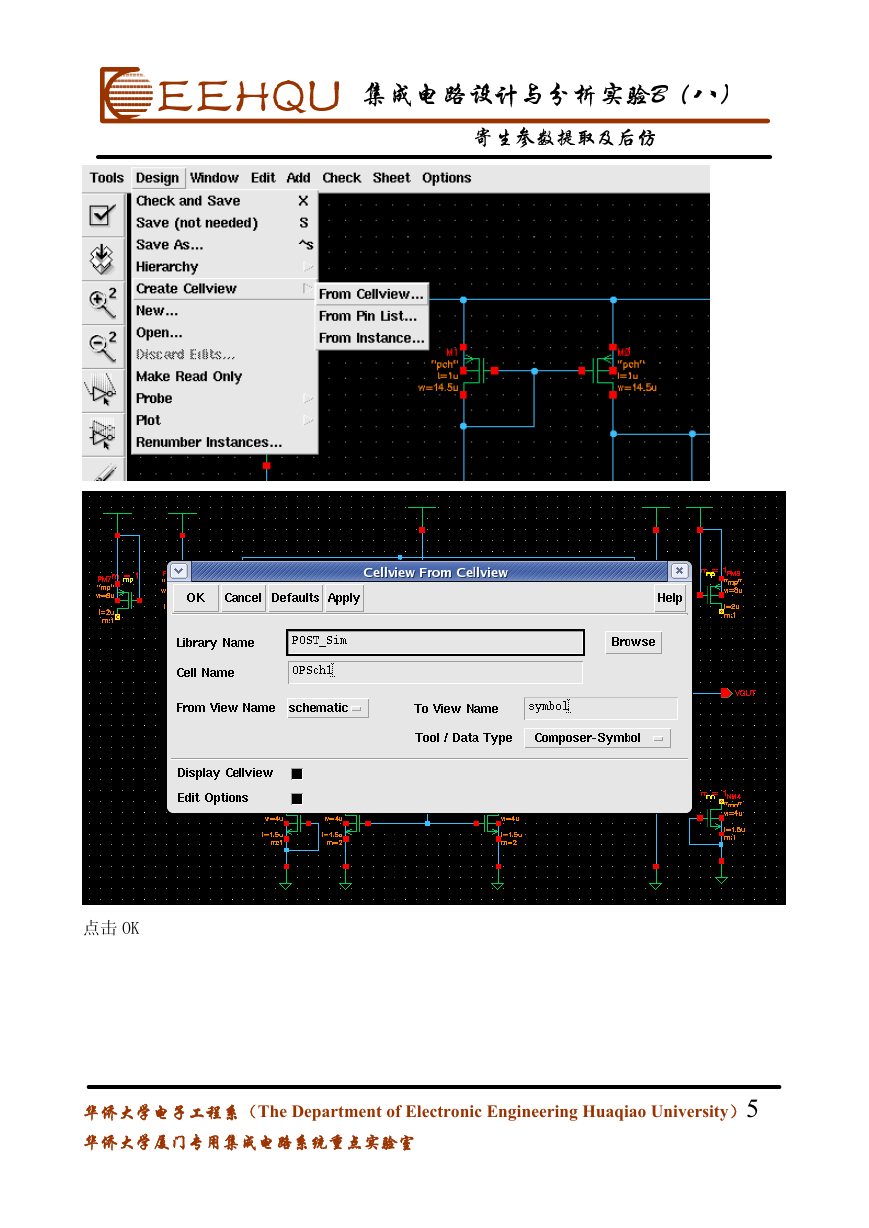

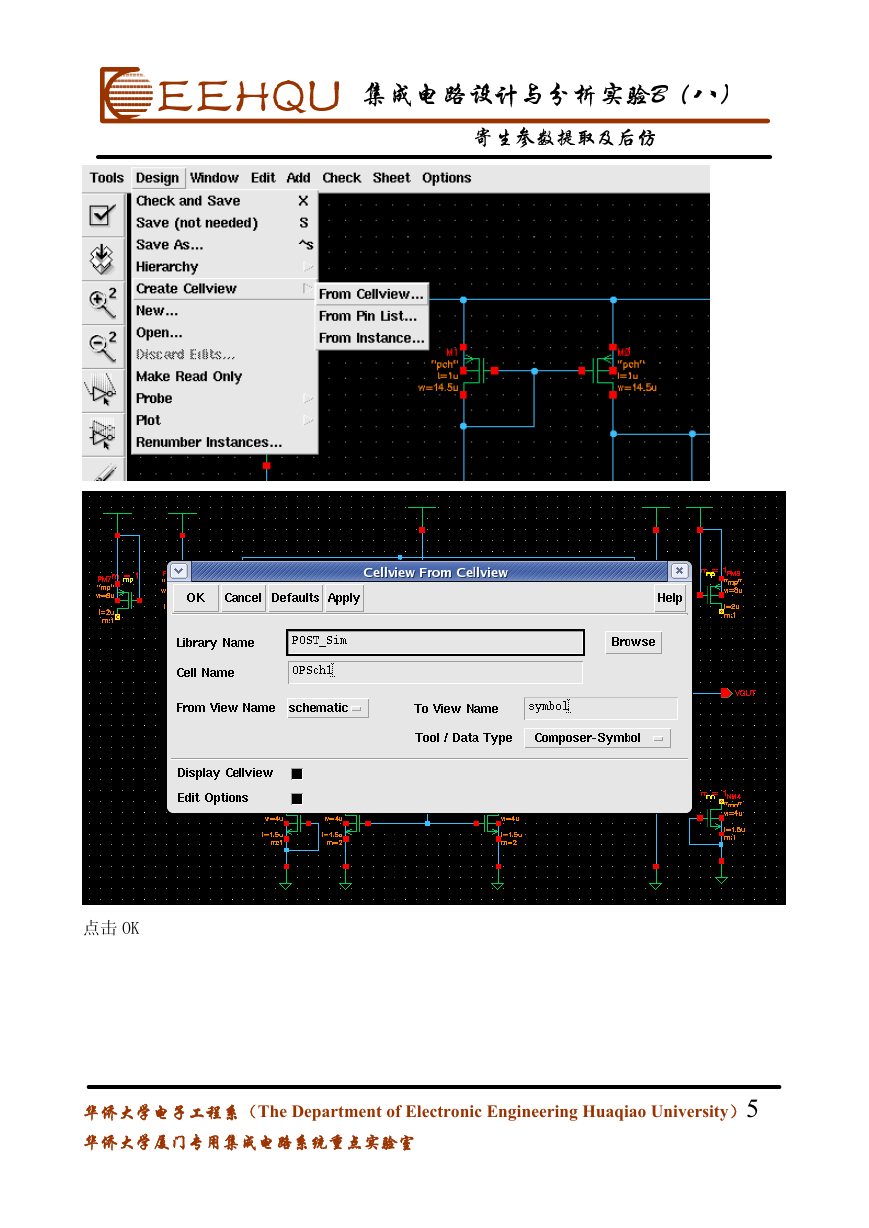

在 design-Creat CellView-Form cellview

华侨大学电子工程系(The Department of Electronic Engineering Huaqiao University)4

华侨大学厦门专用集成电路系统重点实验室

�

点击 OK

华侨大学电子工程系(The Department of Electronic Engineering Huaqiao University)5

华侨大学厦门专用集成电路系统重点实验室

�

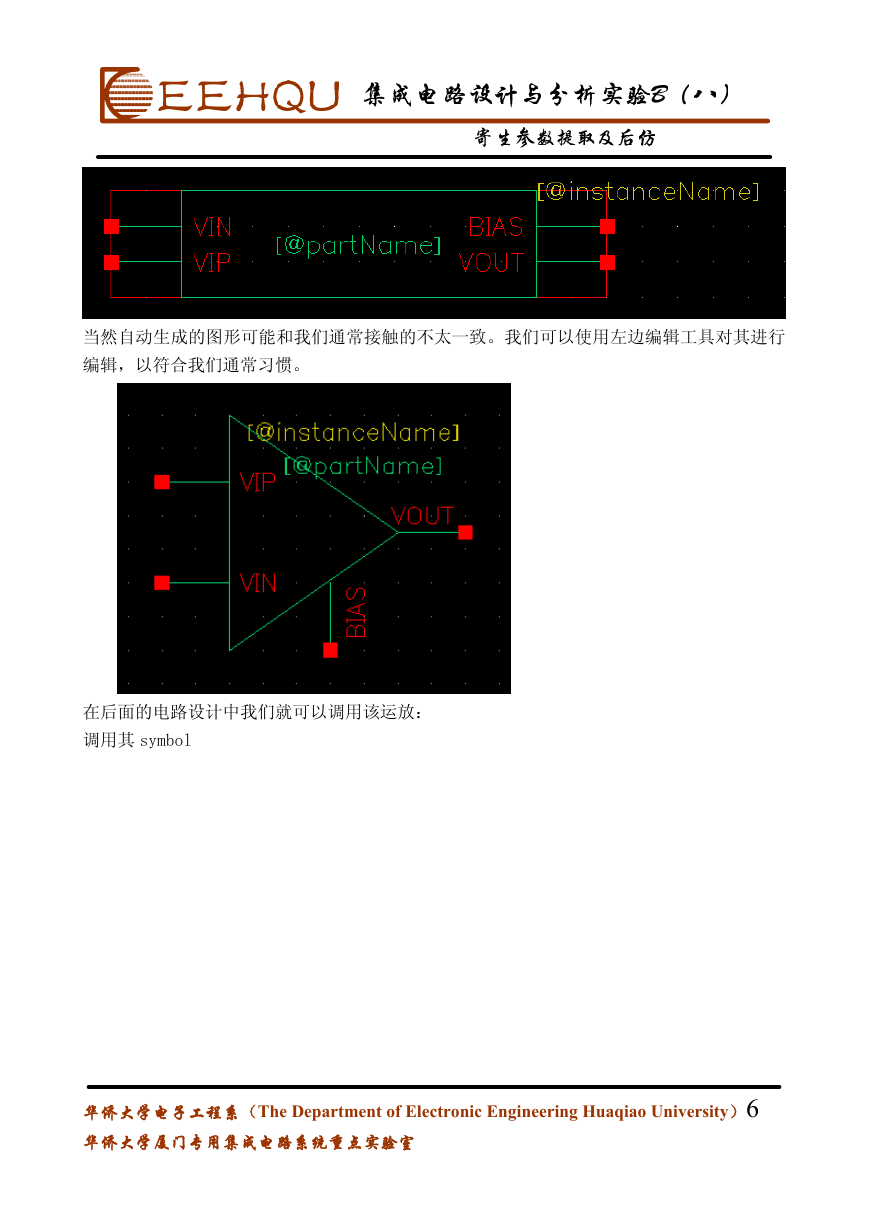

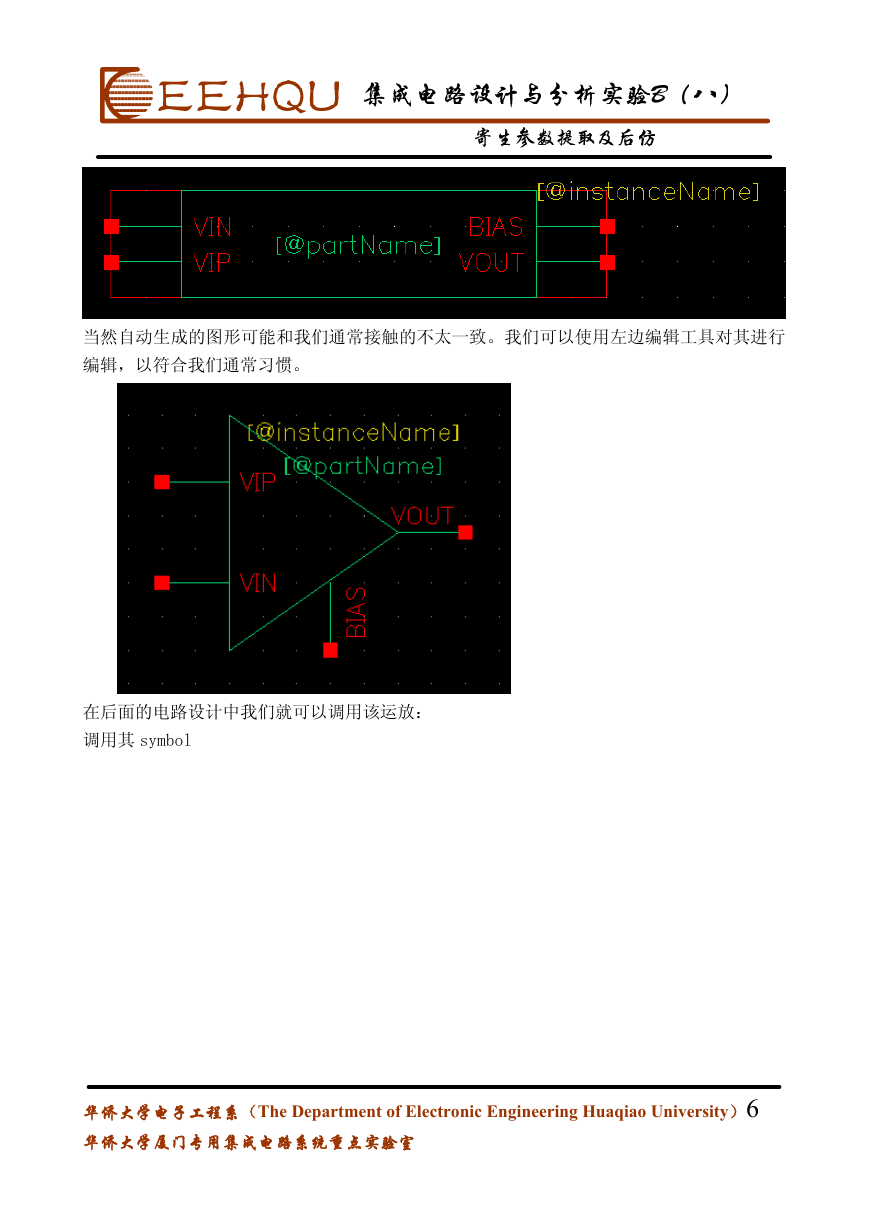

当然自动生成的图形可能和我们通常接触的不太一致。我们可以使用左边编辑工具对其进行

编辑,以符合我们通常习惯。

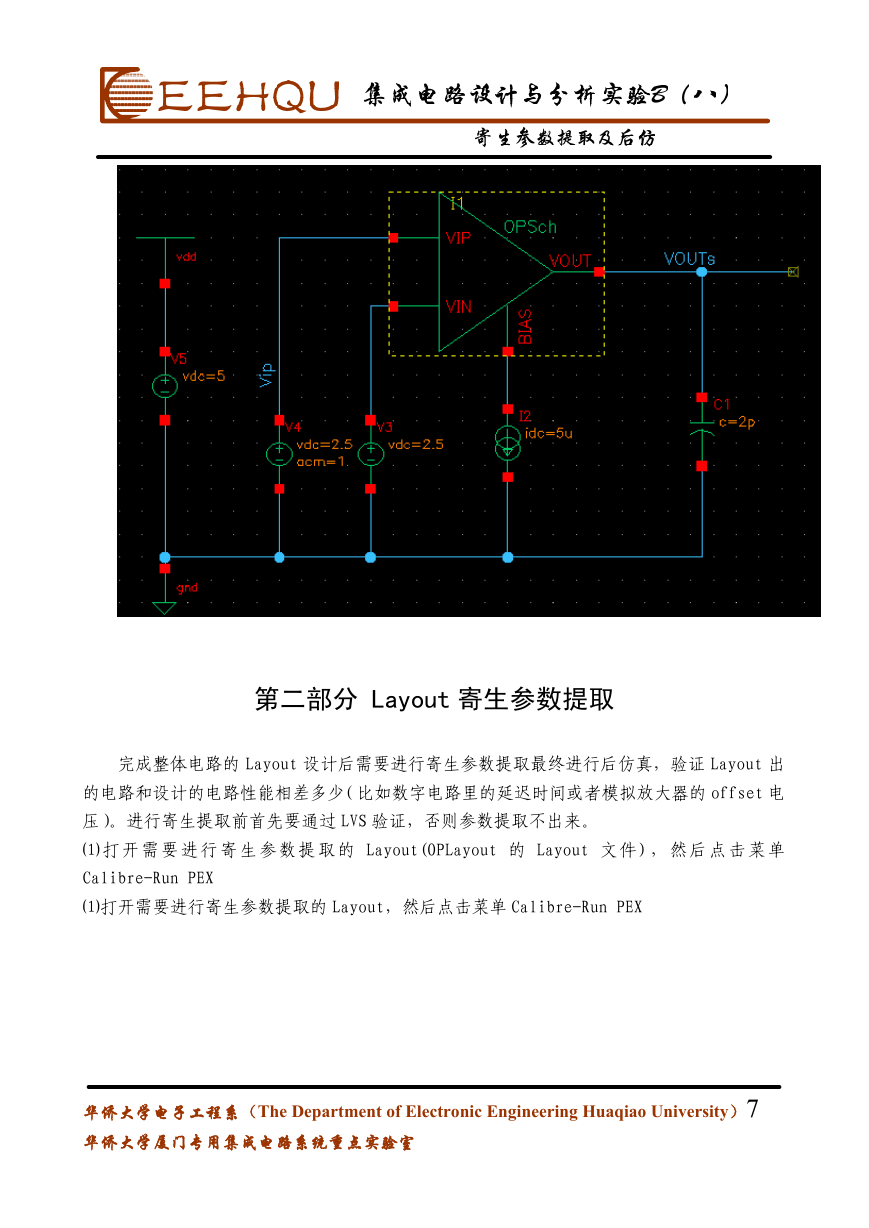

在后面的电路设计中我们就可以调用该运放:

调用其 symbol

华侨大学电子工程系(The Department of Electronic Engineering Huaqiao University)6

华侨大学厦门专用集成电路系统重点实验室

�

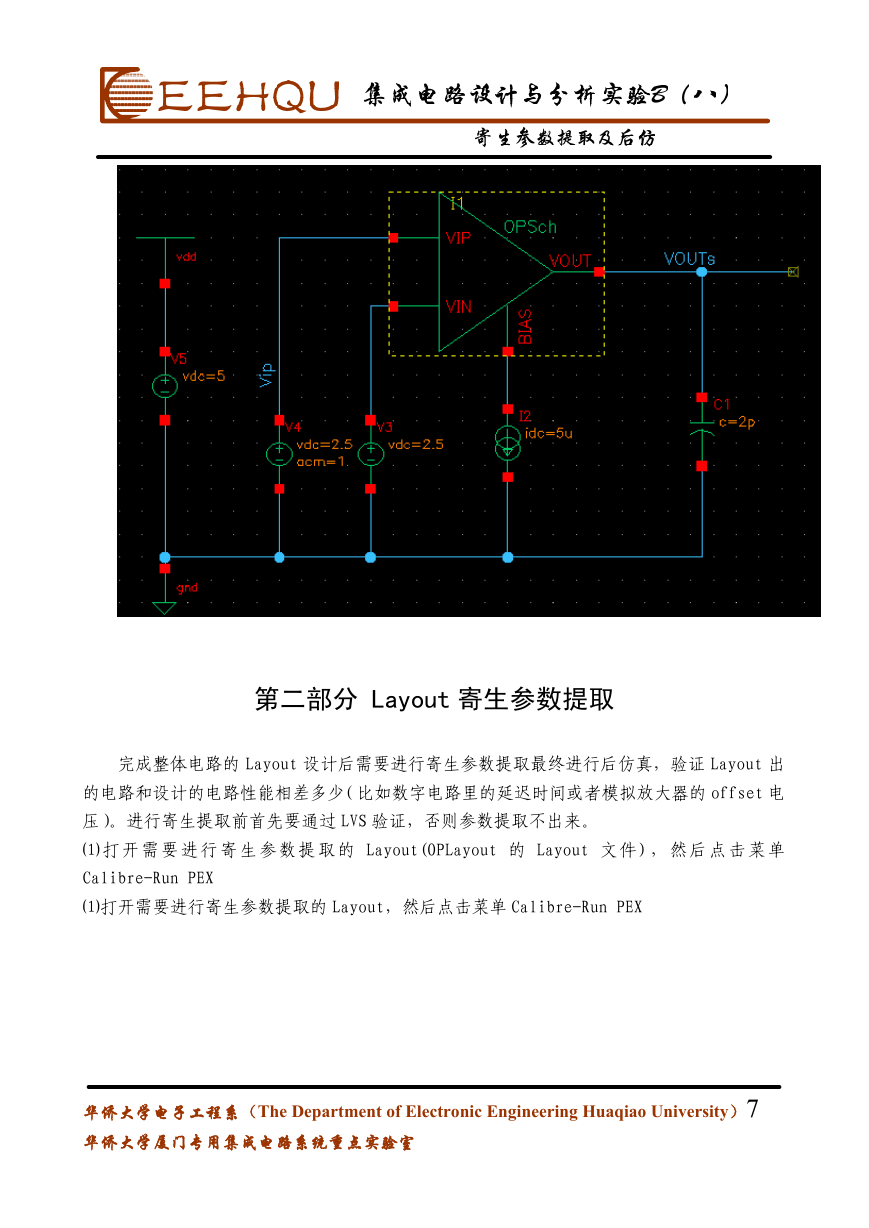

第二部分 Layout 寄生参数提取

完成整体电路的 Layout 设计后需要进行寄生参数提取最终进行后仿真,验证 Layout 出

的电路和设计的电路性能相差多少(比如数字电路里的延迟时间或者模拟放大器的 offset 电

压)。进行寄生提取前首先要通过 LVS 验证,否则参数提取不出来。

⑴ 打 开 需 要 进 行 寄 生 参 数 提 取 的 Layout(OPLayout 的 Layout 文 件 ) , 然 后 点 击 菜 单

Calibre-Run PEX

⑴打开需要进行寄生参数提取的 Layout,然后点击菜单 Calibre-Run PEX

华侨大学电子工程系(The Department of Electronic Engineering Huaqiao University)7

华侨大学厦门专用集成电路系统重点实验室

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc