基于 FPGA 的洗衣机控制电路设计

1、背景:

FPGA 是英文 Field Programmable Gate Array 的缩写,即现场可编程门阵列,它是在 PAL、

GAL、EPLD 等可编程器件的基础上进一步发展的产物。作为专用集成电路(ASIC)领域中的

一种半定制电路,该产品既解决了定制电路的不足,又克服了原有类型的可编程器件门电路

数有限的缺点。由于 FPGA 产品具有上市时间短、设计成本低、便于升级与重复使用的特

点,目前被广泛应用在通信、航天、航空、导航、遥感、遥测、程控交换机等军、民用领域。

FPGA 通常包含三类可编程资源:可编程逻辑功能块、可编程 I/O 块和可编程互连。可

编程逻辑功能块是实现用户功能的基本单元,它们通常排列成一个阵列,散布于整个芯片;

可编程 I/O 单元实现芯片上逻辑与外部封装脚的接口,围绕着阵列于芯片四周;可编程内部

互连包括各种长度的线段和编程连接开关,它们将各个可编程逻辑块或 I/O 块连接起来,构

成特定功能的电路。不同厂家生产的 FPGA 在可编程逻辑块的规模,内部互连线的结构和采

用的可编程元件上存在较大的差异。目前,在市场上比较常用的是 Xilinx 和 Altera 公司的

FPGA 器件。由于 FPGA 能够减少电子系统的开发风险和开发成本(NRE),同时有效的缩短

上市时间(time to market),并且通过在系统编程、远程在线重构等技术降低了维护和升级成

本,因此在通信、控制、数据计算等领域得到了广泛的应用。

FPGA 的发展推动了先进制造工艺和封装工艺的出现,通过全定制的电路和版图设计方

法所进行的设计优化,使 FPGA 在逻辑密度、性能、功能和功耗方面得到大幅改善,成本显

著下降。

随着 FPGA 在功能、密度、速度上的不断提升与成本的降低,用户需求与协议标准的变

化,FPGA 芯片由于其便利的可升级性,不但被用来制作原型机,而且还被大量地应用到网

络、消费电子、科研、航天及国防的许多最终产品中,成为一系列电子系统的核心。

2、目的

通过本次课程设计初步掌握 FPGA 的基本用法和数字电路设计基本方法。学会使用

Altera 公司的 MAX Plus II 软件进行数字电路设计,为以后深入学习 FPGA 数字电路设计打

下基础。

3、功能描述

设计一个电子定时器,控制洗衣机作如下运转:定时启动 正转 20 秒 暂停 10 秒 反

转 20 秒 暂停 10 秒 定时未到回到“正转 20 秒 暂停 10 秒

若定时到,则停机发出音响信号;

用两个数码管显示洗涤的预置时间(分钟数),按倒计时方式对洗涤过程作计时显示,直到

时间到停机;洗涤过程由“开始”信号开始;

三只 LED 灯表示“正转”、“反转”、“暂停”三个状态。

,定时到则停止;

4、设计总体介绍

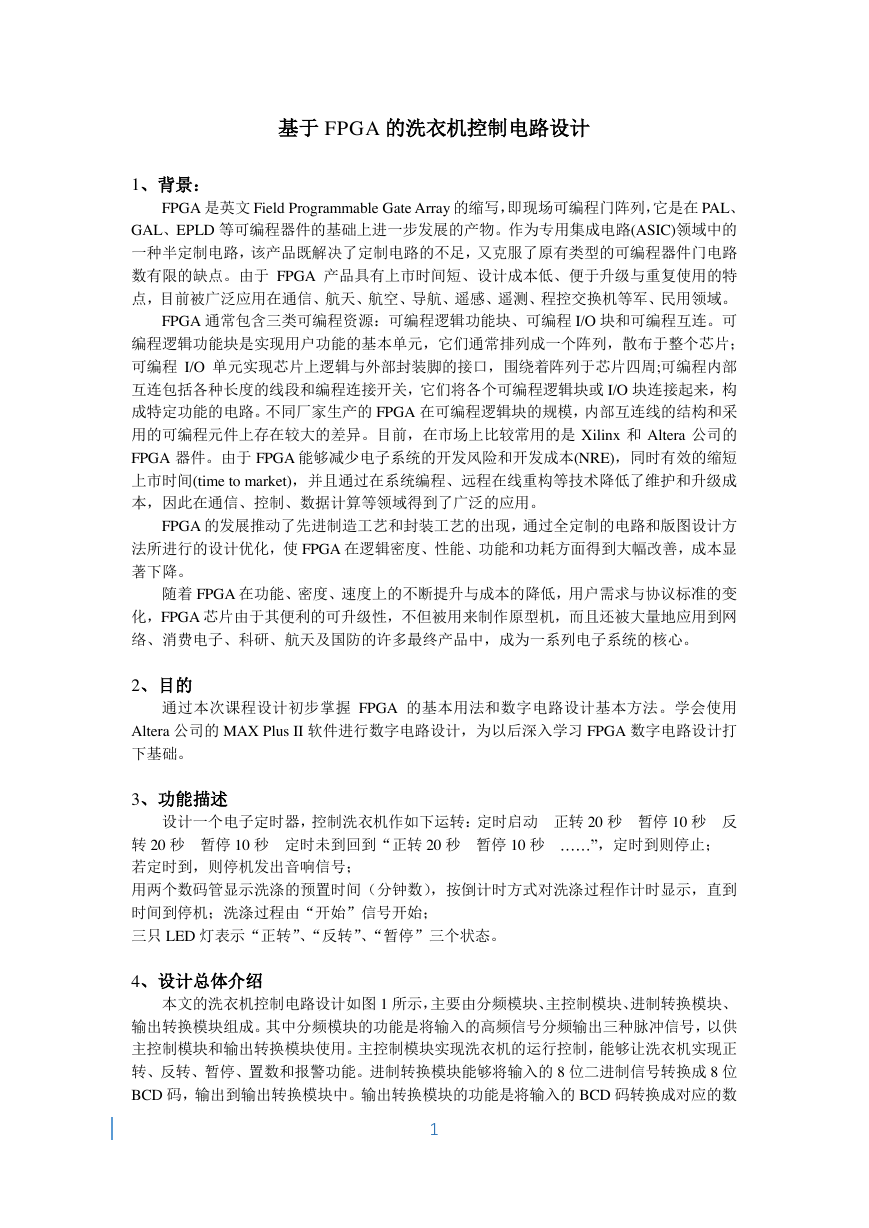

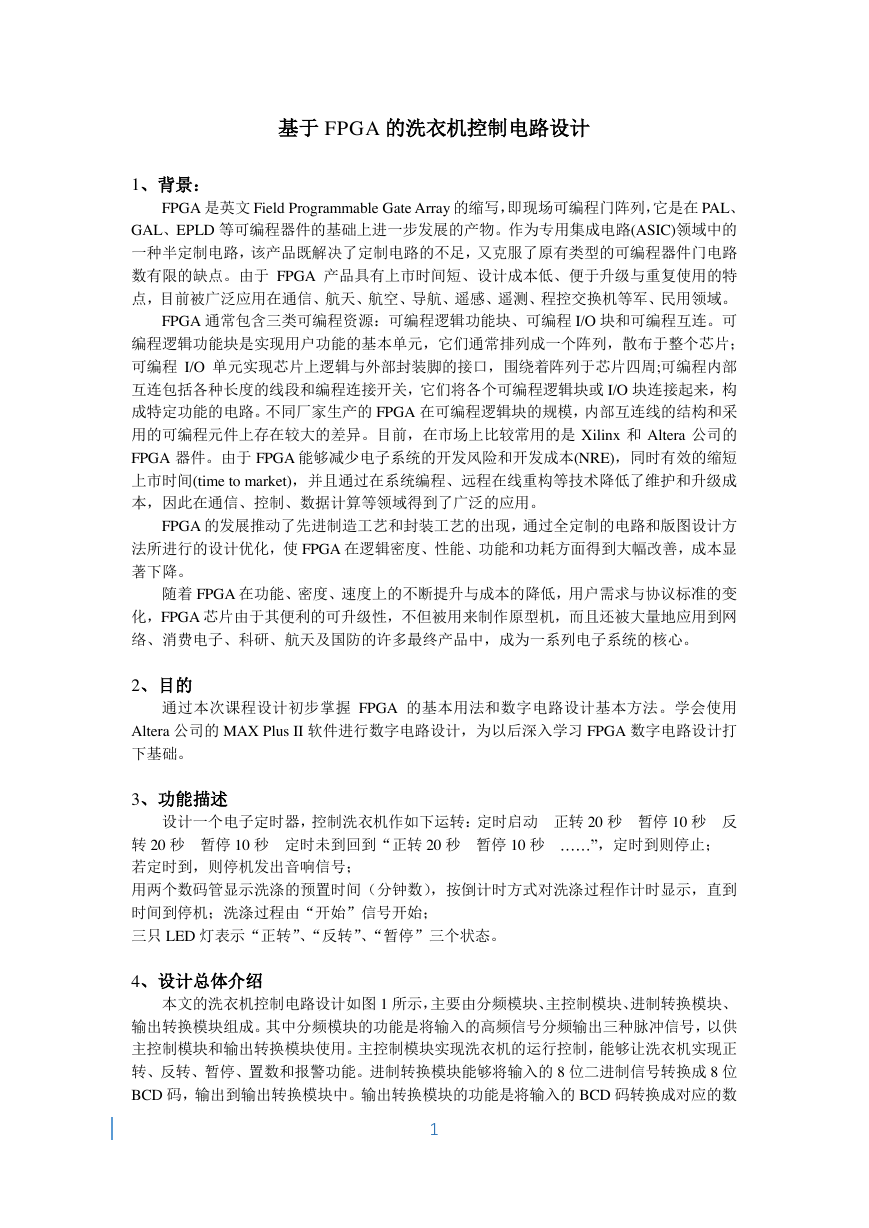

本文的洗衣机控制电路设计如图 1 所示,主要由分频模块、主控制模块、进制转换模块、

输出转换模块组成。其中分频模块的功能是将输入的高频信号分频输出三种脉冲信号,以供

主控制模块和输出转换模块使用。主控制模块实现洗衣机的运行控制,能够让洗衣机实现正

转、反转、暂停、置数和报警功能。进制转换模块能够将输入的 8 位二进制信号转换成 8 位

BCD 码,输出到输出转换模块中。输出转换模块的功能是将输入的 BCD 码转换成对应的数

1

�

码管段选码和位选码,送出到数码管以显示当前运行状态。

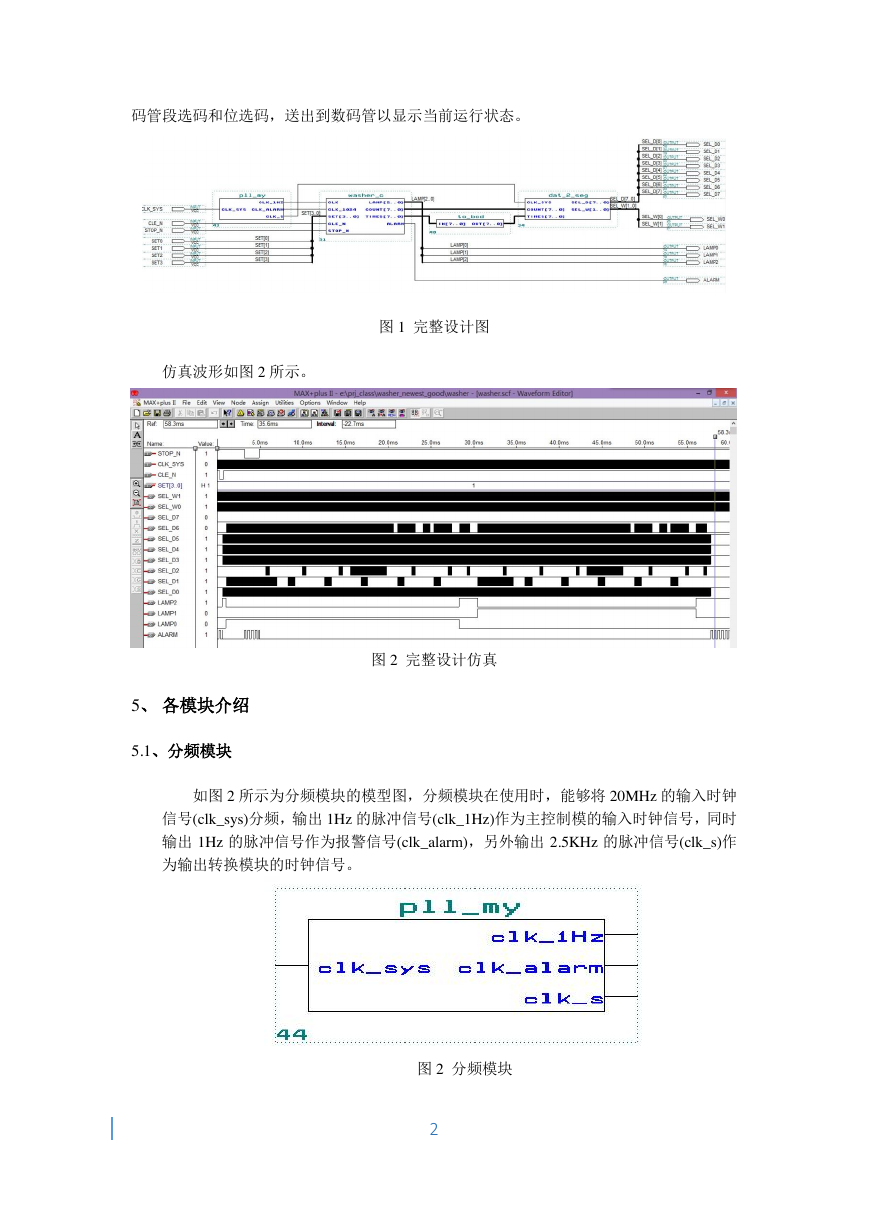

仿真波形如图 2 所示。

图 1 完整设计图

图 2 完整设计仿真

5、 各模块介绍

5.1、分频模块

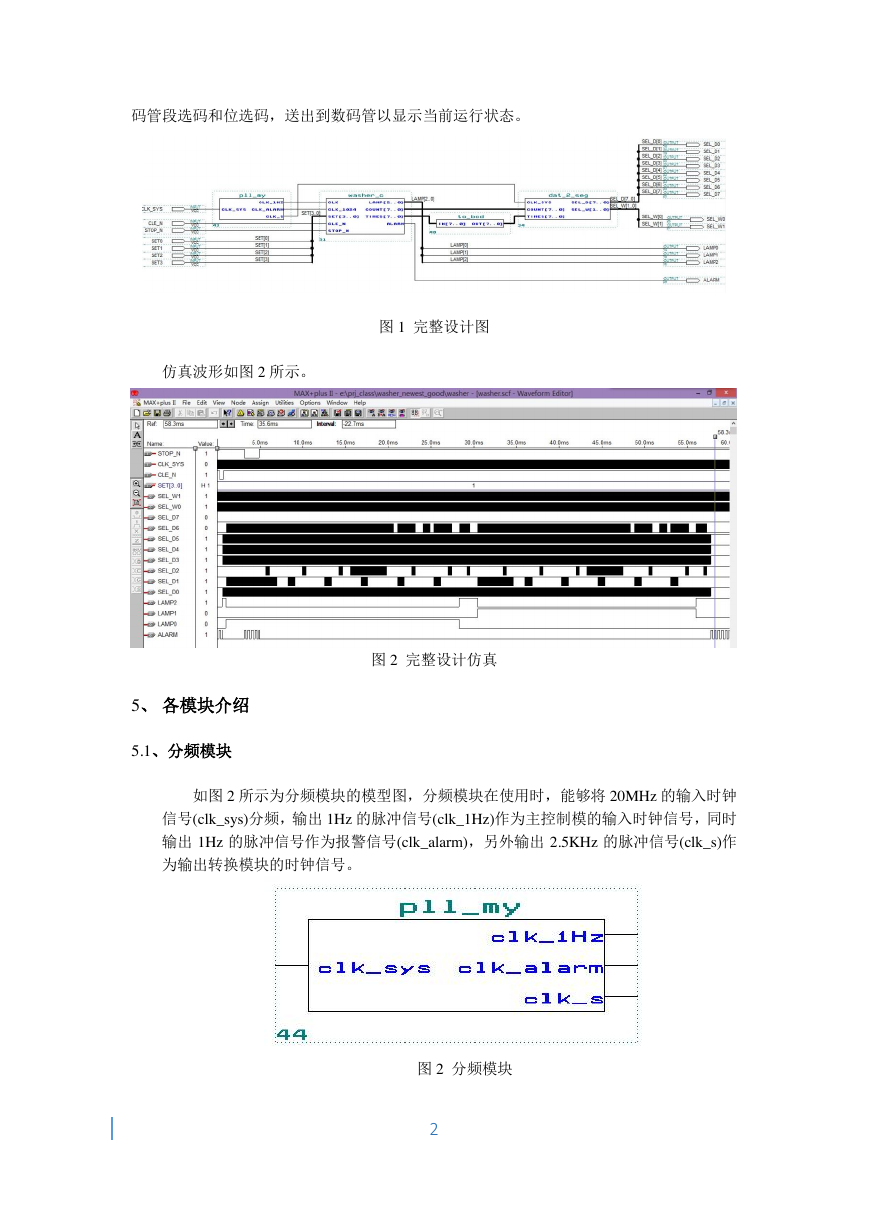

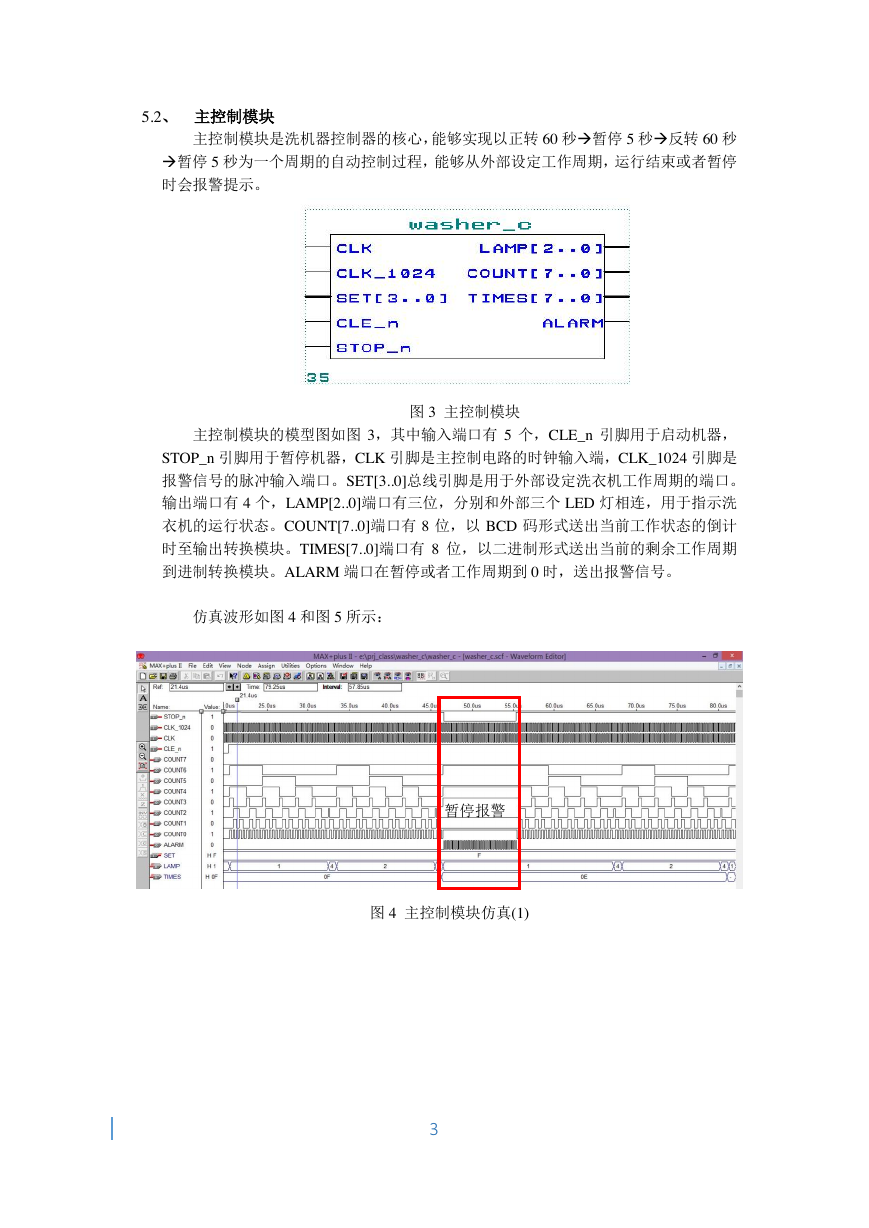

如图 2 所示为分频模块的模型图,分频模块在使用时,能够将 20MHz 的输入时钟

信号(clk_sys)分频,输出 1Hz 的脉冲信号(clk_1Hz)作为主控制模的输入时钟信号,同时

输出 1Hz 的脉冲信号作为报警信号(clk_alarm),另外输出 2.5KHz 的脉冲信号(clk_s)作

为输出转换模块的时钟信号。

图 2 分频模块

2

�

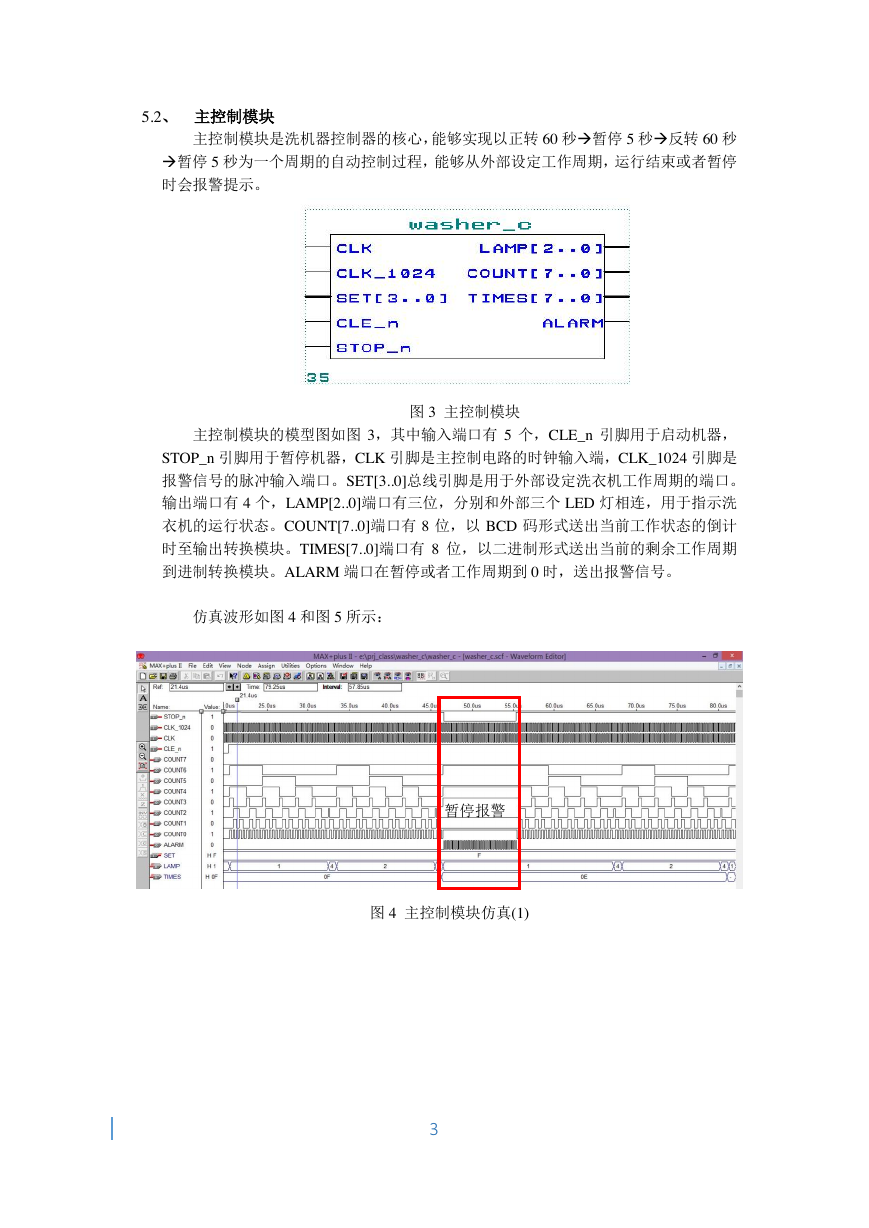

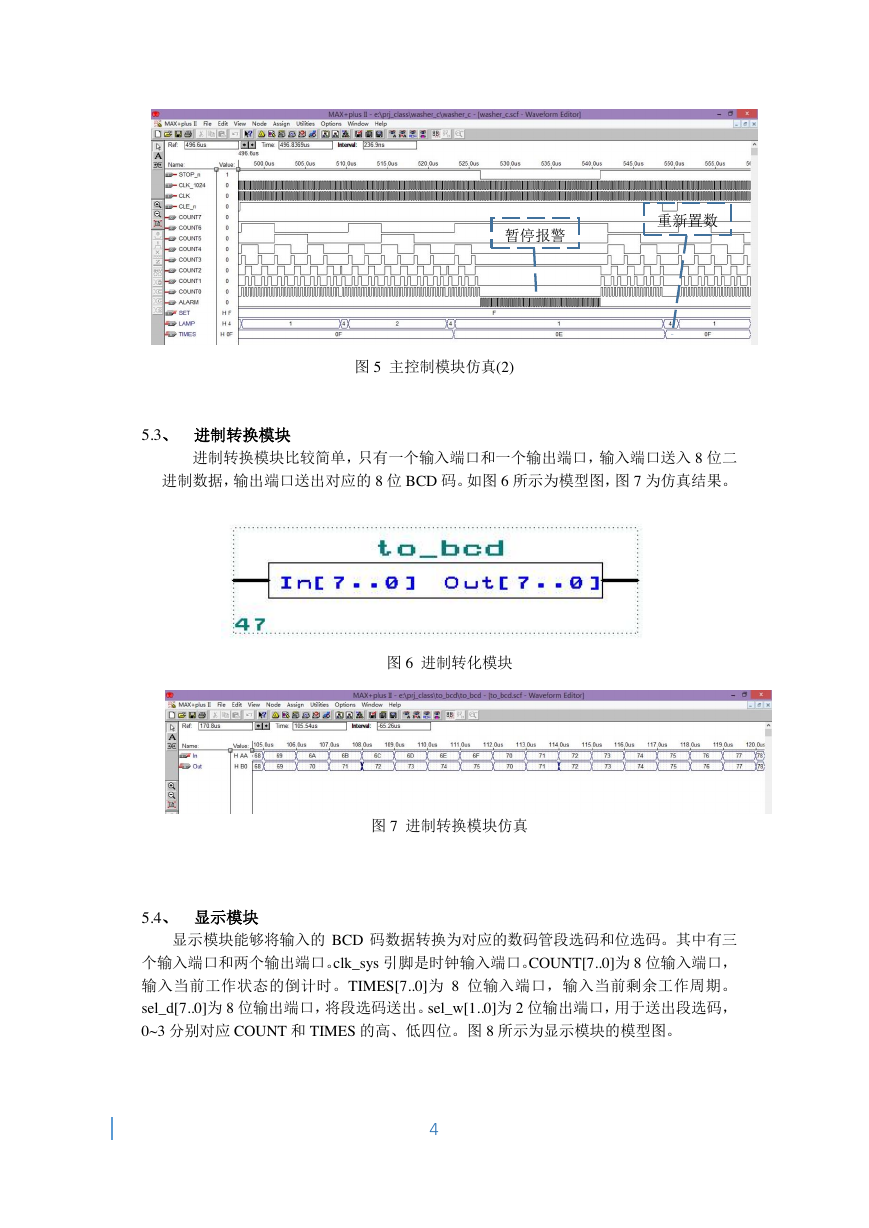

5.2、 主控制模块

主控制模块是洗机器控制器的核心,能够实现以正转 60 秒暂停 5 秒反转 60 秒

暂停 5 秒为一个周期的自动控制过程,能够从外部设定工作周期,运行结束或者暂停

时会报警提示。

图 3 主控制模块

主控制模块的模型图如图 3,其中输入端口有 5 个,CLE_n 引脚用于启动机器,

STOP_n 引脚用于暂停机器,CLK 引脚是主控制电路的时钟输入端,CLK_1024 引脚是

报警信号的脉冲输入端口。SET[3..0]总线引脚是用于外部设定洗衣机工作周期的端口。

输出端口有 4 个,LAMP[2..0]端口有三位,分别和外部三个 LED 灯相连,用于指示洗

衣机的运行状态。COUNT[7..0]端口有 8 位,以 BCD 码形式送出当前工作状态的倒计

时至输出转换模块。TIMES[7..0]端口有 8 位,以二进制形式送出当前的剩余工作周期

到进制转换模块。ALARM 端口在暂停或者工作周期到 0 时,送出报警信号。

仿真波形如图 4 和图 5 所示:

暂停报警

图 4 主控制模块仿真(1)

3

�

暂停报警

重新置数

图 5 主控制模块仿真(2)

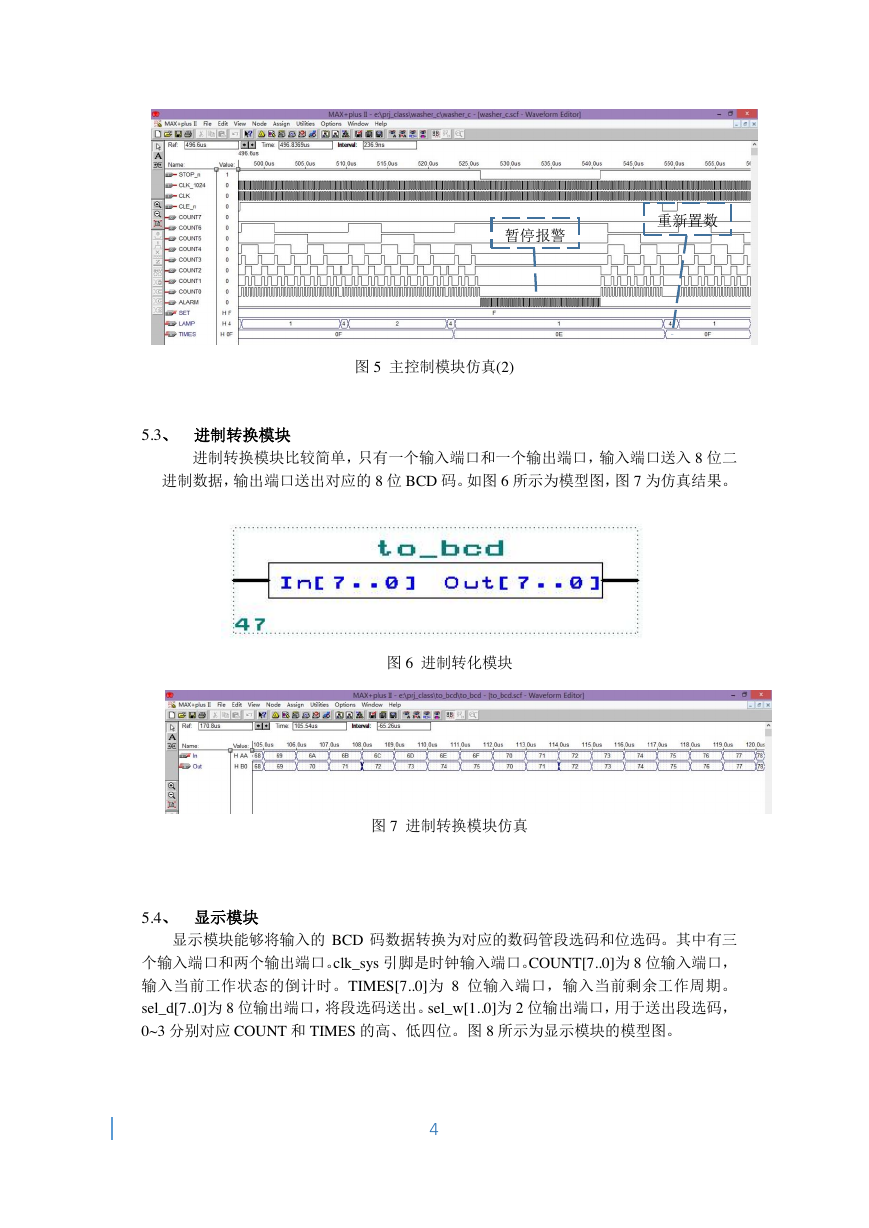

5.3、 进制转换模块

进制转换模块比较简单,只有一个输入端口和一个输出端口,输入端口送入 8 位二

进制数据,输出端口送出对应的 8 位 BCD 码。如图 6 所示为模型图,图 7 为仿真结果。

图 6 进制转化模块

图 7 进制转换模块仿真

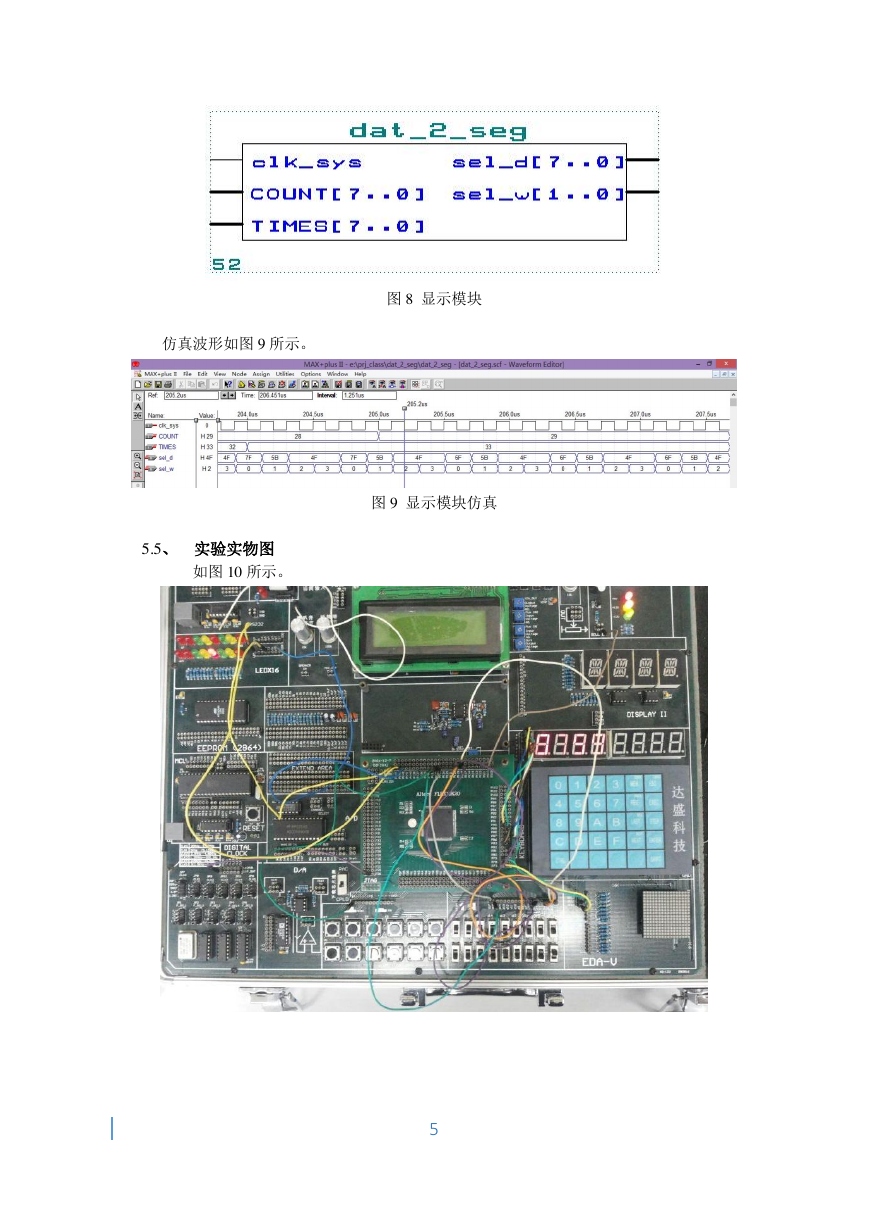

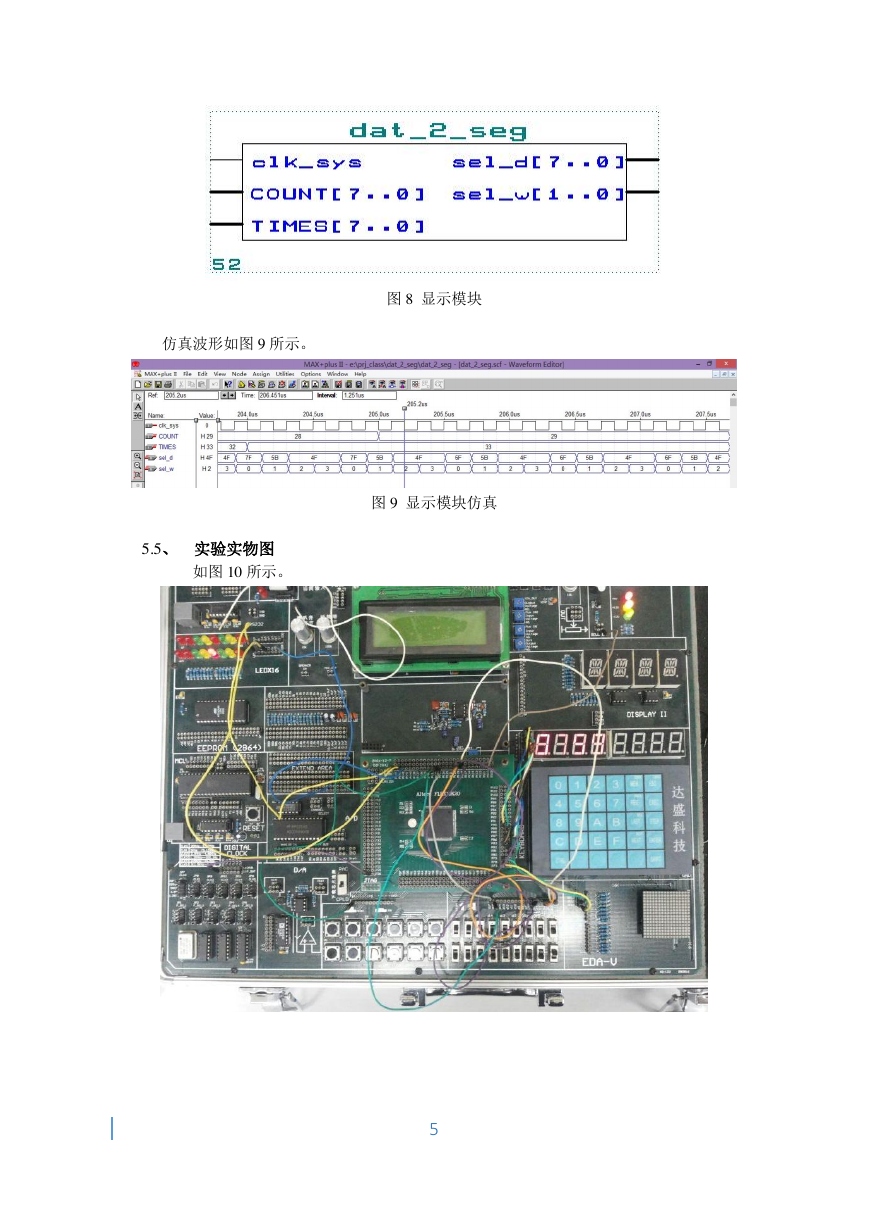

5.4、 显示模块

显示模块能够将输入的 BCD 码数据转换为对应的数码管段选码和位选码。其中有三

个输入端口和两个输出端口。clk_sys 引脚是时钟输入端口。COUNT[7..0]为 8 位输入端口,

输入当前工作状态的倒计时。TIMES[7..0]为 8 位输入端口,输入当前剩余工作周期。

sel_d[7..0]为 8 位输出端口,将段选码送出。sel_w[1..0]为 2 位输出端口,用于送出段选码,

0~3 分别对应 COUNT 和 TIMES 的高、低四位。图 8 所示为显示模块的模型图。

4

�

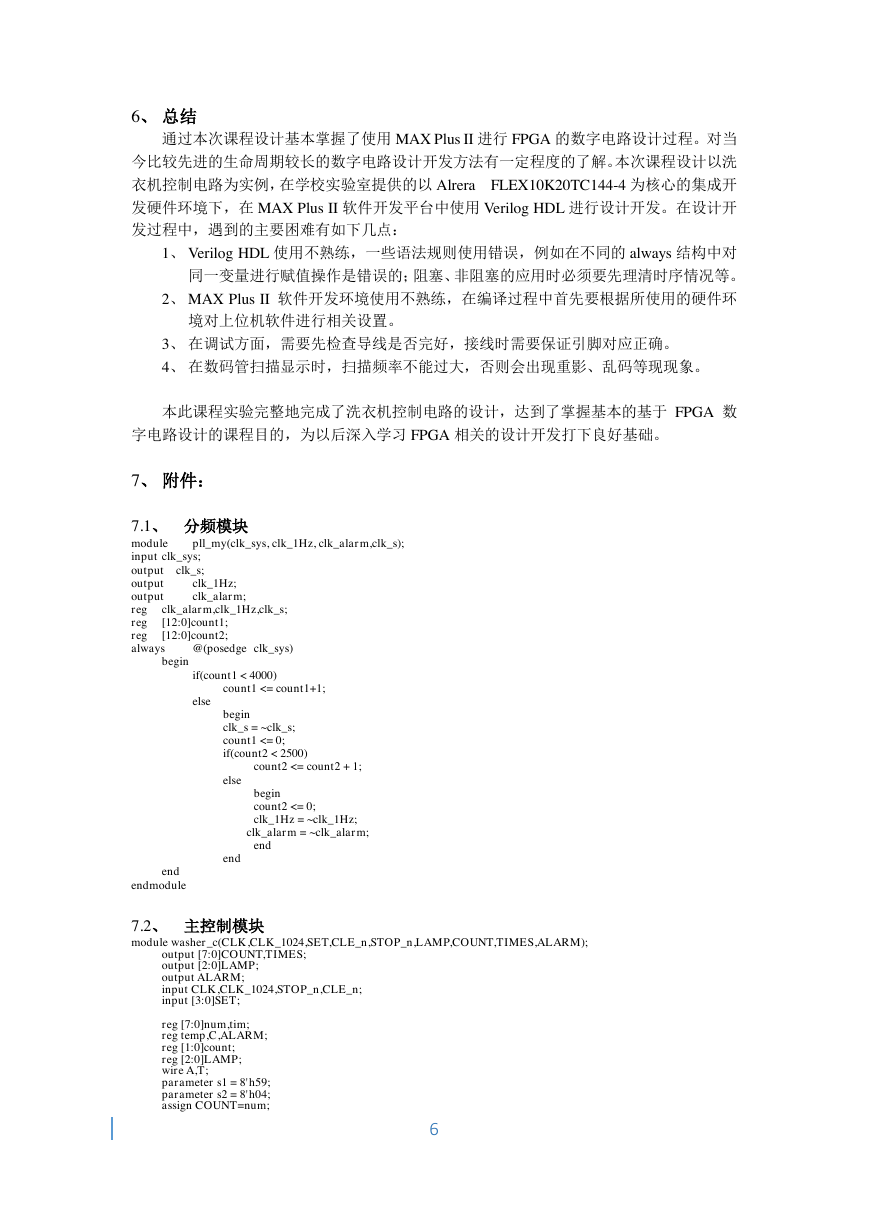

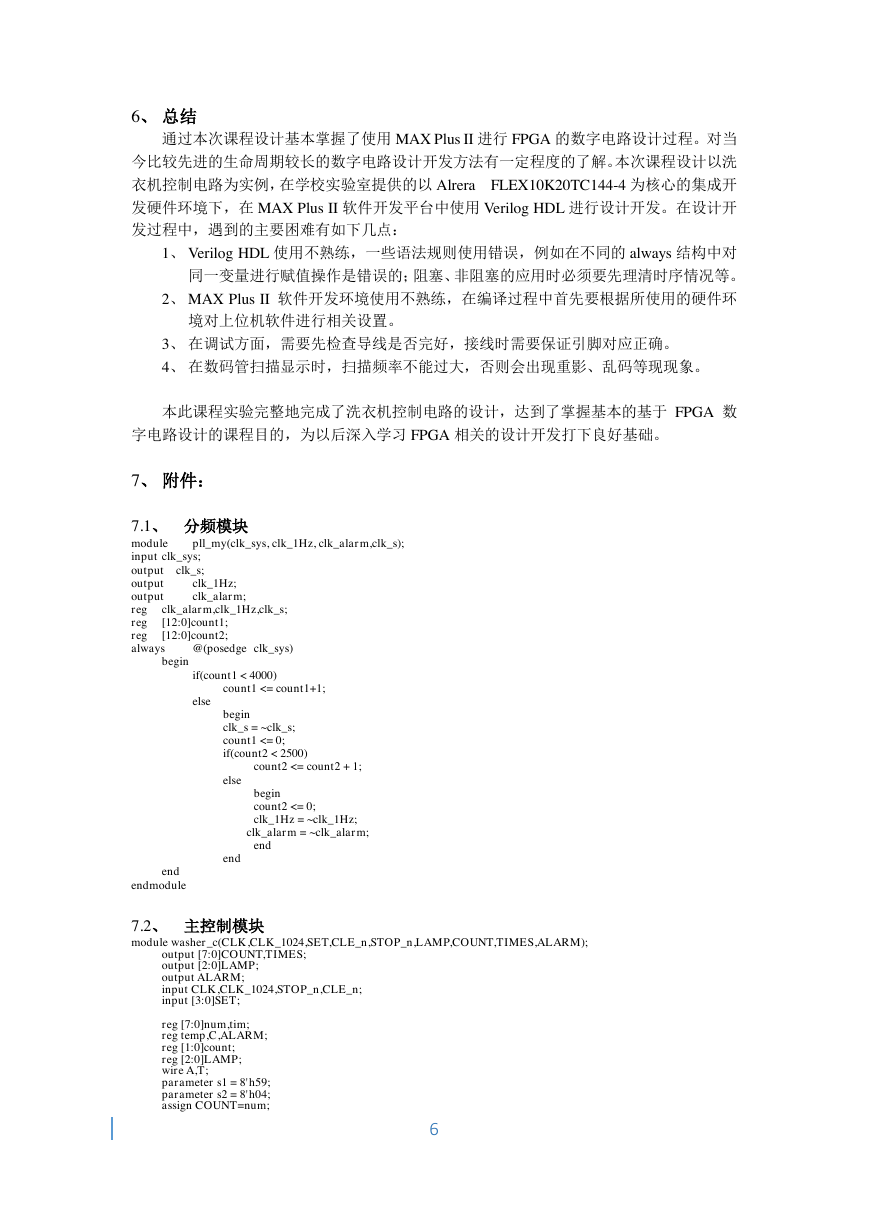

仿真波形如图 9 所示。

图 8 显示模块

图 9 显示模块仿真

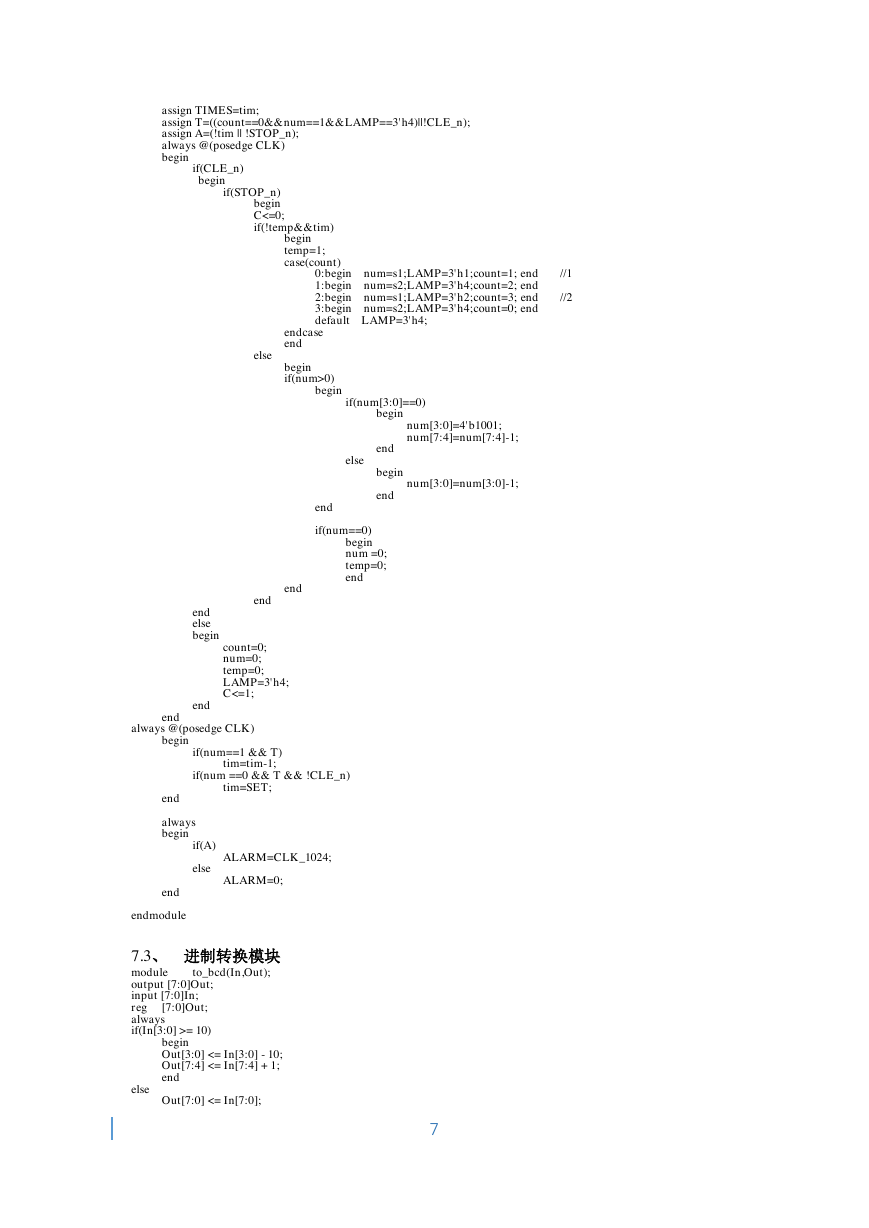

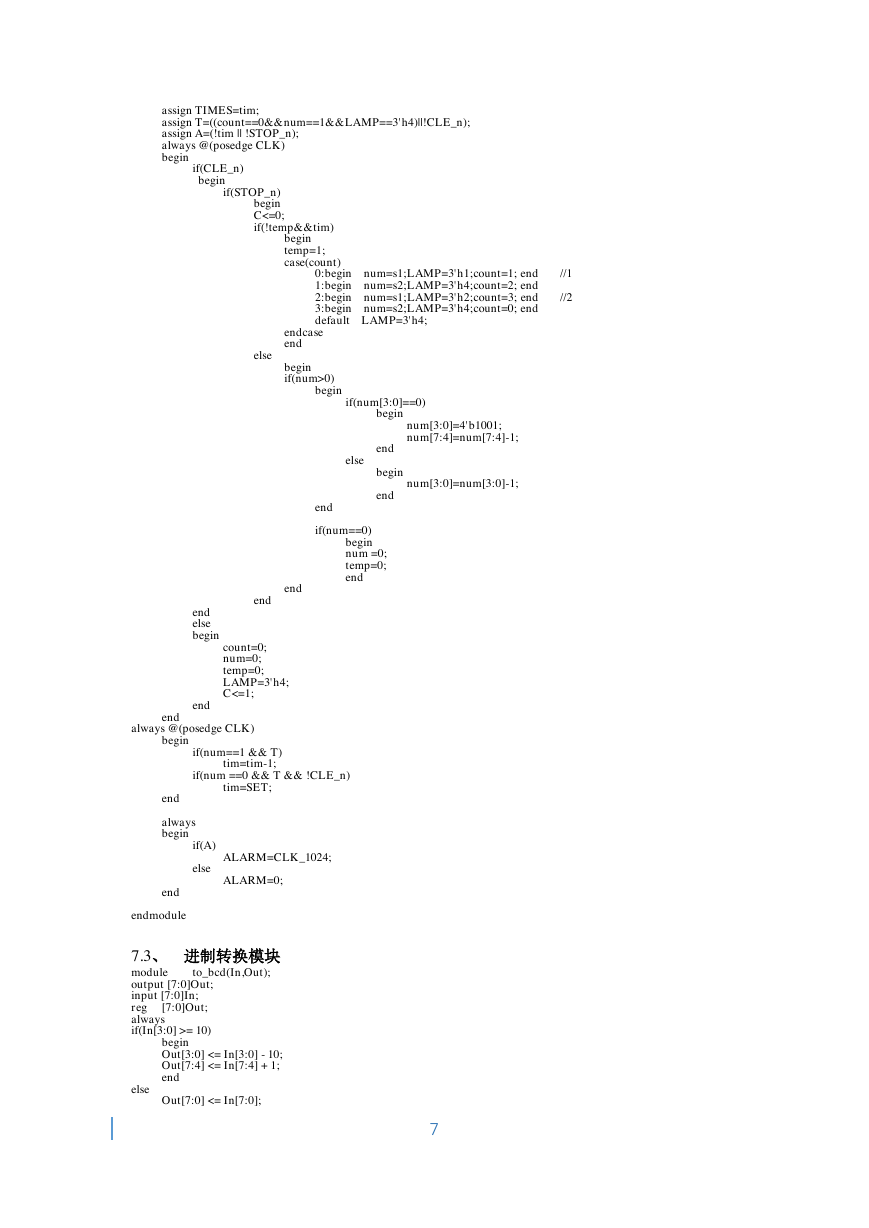

5.5、 实验实物图

如图 10 所示。

5

�

6、 总结

通过本次课程设计基本掌握了使用 MAX Plus II 进行 FPGA 的数字电路设计过程。对当

今比较先进的生命周期较长的数字电路设计开发方法有一定程度的了解。本次课程设计以洗

衣机控制电路为实例,在学校实验室提供的以 Alrera FLEX10K20TC144-4 为核心的集成开

发硬件环境下,在 MAX Plus II 软件开发平台中使用 Verilog HDL 进行设计开发。在设计开

发过程中,遇到的主要困难有如下几点:

1、 Verilog HDL 使用不熟练,一些语法规则使用错误,例如在不同的 always 结构中对

同一变量进行赋值操作是错误的;阻塞、非阻塞的应用时必须要先理清时序情况等。

2、 MAX Plus II 软件开发环境使用不熟练,在编译过程中首先要根据所使用的硬件环

境对上位机软件进行相关设置。

3、 在调试方面,需要先检查导线是否完好,接线时需要保证引脚对应正确。

4、 在数码管扫描显示时,扫描频率不能过大,否则会出现重影、乱码等现现象。

本此课程实验完整地完成了洗衣机控制电路的设计,达到了掌握基本的基于 FPGA 数

字电路设计的课程目的,为以后深入学习 FPGA 相关的设计开发打下良好基础。

7、 附件:

@(posedge clk_sys)

count1 <= count1+1;

count2 <= count2 + 1;

clk_1Hz;

clk_alarm;

pll_my(clk_sys, clk_1Hz, clk_alarm,clk_s);

clk_alarm,clk_1Hz,clk_s;

[12:0]count1;

[12:0]count2;

begin

end

if(count1 < 4000)

else

end

begin

clk_s = ~clk_s;

count1 <= 0;

if(count2 < 2500)

else

clk_alarm = ~clk_alarm;

end

7.1、 分频模块

module

input clk_sys;

output clk_s;

output

output

reg

reg

reg

always

endmodule

7.2、 主控制模块

module washer_c(CLK,CLK_1024,SET,CLE_n,STOP_n,LAMP,COUNT,TIMES,ALARM);

output [7:0]COUNT,TIMES;

output [2:0]LAMP;

output ALARM;

input CLK,CLK_1024,STOP_n,CLE_n;

input [3:0]SET;

reg [7:0]num,tim;

reg temp,C,ALARM;

reg [1:0]count;

reg [2:0]LAMP;

wire A,T;

parameter s1 = 8'h59;

parameter s2 = 8'h04;

assign COUNT=num;

begin

count2 <= 0;

clk_1Hz = ~clk_1Hz;

6

�

num[3:0]=4'b1001;

num[7:4]=num[7:4]-1;

num[3:0]=num[3:0]-1;

0:begin num=s1;LAMP=3'h1;count=1; end

1:begin num=s2;LAMP=3'h4;count=2; end

2:begin num=s1;LAMP=3'h2;count=3; end

3:begin num=s2;LAMP=3'h4;count=0; end

default LAMP=3'h4;

//1

//2

begin

temp=1;

case(count)

endcase

end

if(STOP_n)

begin

C<=0;

if(!temp&&tim)

else

end

assign TIMES=tim;

assign T=((count==0&&num==1&&LAMP==3'h4)||!CLE_n);

assign A=(!tim || !STOP_n);

always @(posedge CLK)

begin

end

begin

end

if(num==0)

begin

num =0;

temp=0;

end

begin

if(num>0)

end

if(num[3:0]==0)

else

count=0;

num=0;

temp=0;

LAMP=3'h4;

C<=1;

begin

end

begin

end

if(CLE_n)

begin

end

else

begin

end

always @(posedge CLK)

endmodule

7.3、 进制转换模块

module

output [7:0]Out;

input [7:0]In;

reg

always

if(In[3:0] >= 10)

else

begin

Out[3:0] <= In[3:0] - 10;

Out[7:4] <= In[7:4] + 1;

end

always

begin

end

begin

end

if(A)

else

Out[7:0] <= In[7:0];

to_bcd(In,Out);

if(num==1 && T)

tim=tim-1;

if(num ==0 && T && !CLE_n)

tim=SET;

ALARM=CLK_1024;

ALARM=0;

[7:0]Out;

7

�

dat_2_seg(clk_sys,COUNT,TIMES,sel_d,sel_w);

sel_d = 8'h3f;

[7:0]sel_d;

[1:0]sel_w;

[7:0]sel_d;

[1:0]sel_w;

endmodule

7.4、 显示模块

module

input clk_sys;

input [7:0]COUNT,TIMES;

output

output

reg

reg

reg [1:0]cnt;

always @(posedge clk_sys)

endmodule

cnt = cnt + 1;

if(cnt == 0)

begin

sel_w = 0;

case(COUNT[3:0])

4'h0: begin sel_d = 8'h3f; end

4'h1: begin sel_d = 8'h06; end

4'h2: begin sel_d = 8'h5b; end

4'h3: begin sel_d = 8'h4f; end

4'h4: begin sel_d = 8'h66; end

4'h5: begin sel_d = 8'h6d; end

4'h6: begin sel_d = 8'h7d; end

4'h7: begin sel_d = 8'h07; end

4'h8: begin sel_d = 8'h7f; end

4'h9: begin sel_d = 8'h6f; end

default

endcase

end

if(cnt == 1)

begin

sel_w = 1;

case(COUNT[7:4])

4'h0: begin sel_d = 8'h3f; end

4'h1: begin sel_d = 8'h06; end

4'h2: begin sel_d = 8'h5b; end

4'h3: begin sel_d = 8'h4f; end

4'h4: begin sel_d = 8'h66; end

4'h5: begin sel_d = 8'h6d; end

4'h6: begin sel_d = 8'h7d; end

4'h7: begin sel_d = 8'h07; end

4'h8: begin sel_d = 8'h7f; end

4'h9: begin sel_d = 8'h6f; end

default

endcase

end

if(cnt == 2)

begin

sel_w = 2;

case(TIMES[3:0])

4'h0: begin sel_d = 8'h3f; end

4'h1: begin sel_d = 8'h06; end

4'h2: begin sel_d = 8'h5b; end

4'h3: begin sel_d = 8'h4f; end

4'h4: begin sel_d = 8'h66; end

4'h5: begin sel_d = 8'h6d; end

4'h6: begin sel_d = 8'h7d; end

4'h7: begin sel_d = 8'h07; end

4'h8: begin sel_d = 8'h7f; end

4'h9: begin sel_d = 8'h6f; end

default

endcase

end

if(cnt == 3)

begin

sel_w = 3;

case(TIMES[7:4])

4'h0: begin sel_d = 8'h3f; end

4'h1: begin sel_d = 8'h06; end

4'h2: begin sel_d = 8'h5b; end

4'h3: begin sel_d = 8'h4f; end

4'h4: begin sel_d = 8'h66; end

4'h5: begin sel_d = 8'h6d; end

4'h6: begin sel_d = 8'h7d; end

4'h7: begin sel_d = 8'h07; end

4'h8: begin sel_d = 8'h7f; end

4'h9: begin sel_d = 8'h6f; end

default

endcase

end

begin

end

sel_d = 8'h3f;

sel_d = 8'h3f;

sel_d = 8'h3f;

8

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc