接口技术开放性实验

题 目:

抢答器的设计

姓 名:

班 级:

学 号:

�

一. 实验基本要求

利用并行接口和开关设计一个抢答器。逻辑开关代表抢答按钮,抢

答开始前,LED 小灯泡流水,当某个逻辑开关闭合时,相当于抢答按钮

按下,此时对应的 LED 灯泡常亮,同时蜂鸣器响起。

二. 实验扩展(选做)

无

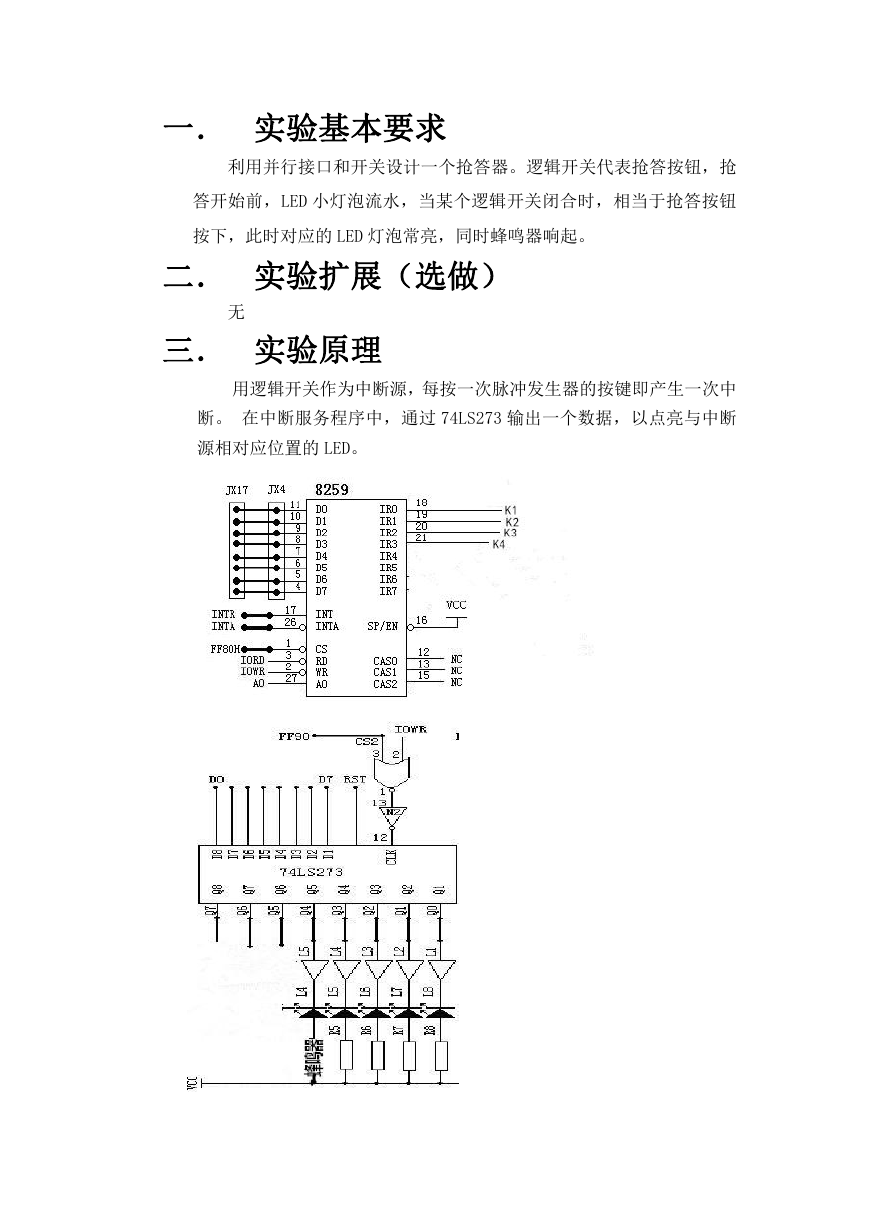

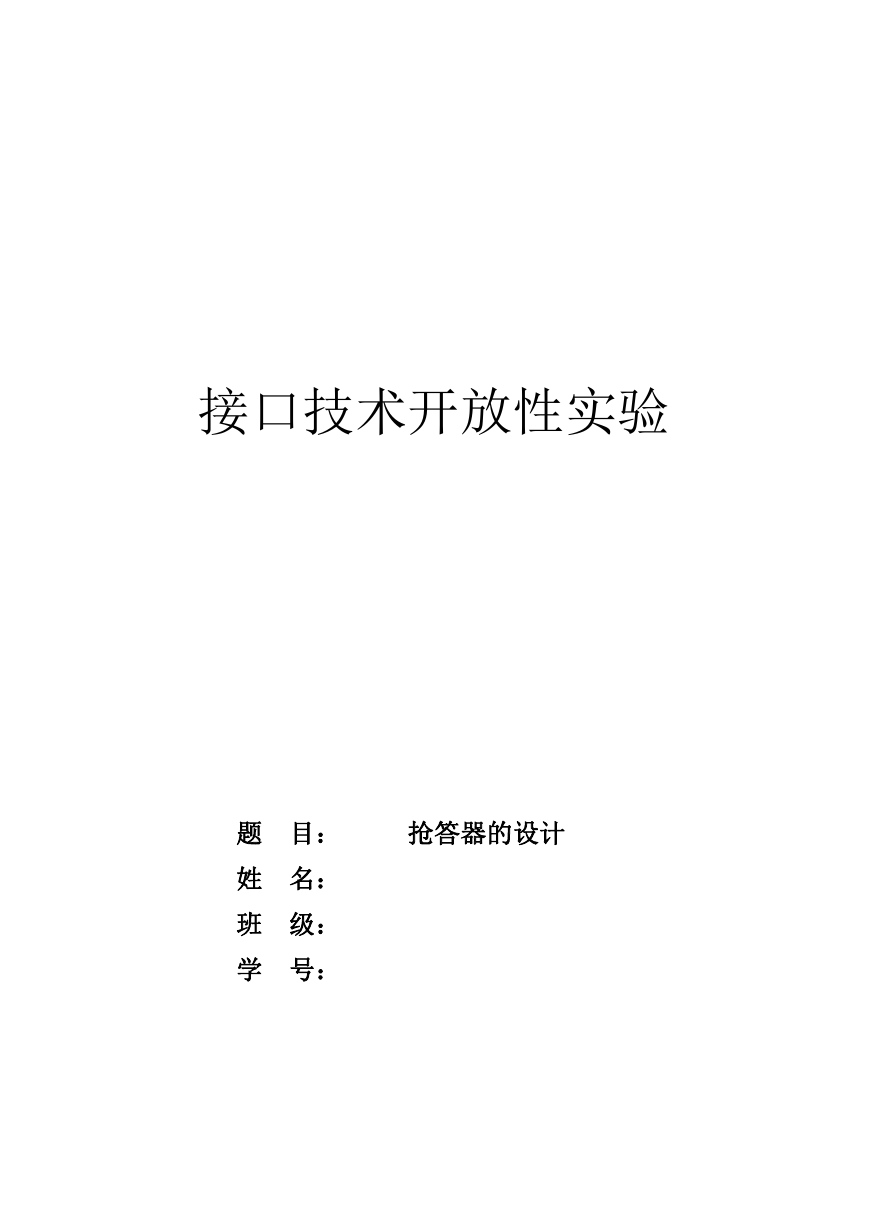

三. 实验原理

用逻辑开关作为中断源,每按一次脉冲发生器的按键即产生一次中

断。 在中断服务程序中,通过 74LS273 输出一个数据,以点亮与中断

源相对应位置的 LED。

�

四. 硬件设计

Ⅰ.包含芯片

8259A 中断控制器一片、上升沿锁存器 74LS273 一片

Ⅱ.芯片原理

(1)8259A 中断控制器

①内部结构:

8259A 有 28 根引脚,所有输入、输出端与 TTL 电平兼容,单一电源

(Vcc=+5V)供电。8259 的内部主要组成部分,包括处理部件(中断请 求

寄存器 IRR、优先级鉴别器 PR 及现行服务寄存器 ISR)、控制部件(控

制 逻辑及中断屏蔽寄存器 IMR)、数据总路线缓冲器、读/写逻辑 以

及级联缓冲器/比较器等 5 个部分。

②主要外部引脚:

D0~D7:双向数据线,CPU 与 8259 间利用这个数据总路线传送数据

及命令。

WR :写控制输入信号,同控制总路线上的 IOW 信号相连。

RD :读控制输入信号,同控制总路线上的 IOR 信号相连。

A0:地址选择信号,用来对 8259A 内部的两个可编程寄存器进行

选择。

CS :片选输入信号,低电平有效。有效时可通过数据总路线设置命

令并对内部寄存器进行读出。当进入中断响应时序时,该引脚

状态与进行的处理无关。

INT: 由 8259A 向 CPU 发出的中断请求信号。

INTA :输入信号,接收 CPU 送来的中断响应信号 INTA。

IR0~IR7:8 个中断请求输入信号,高电平或上升沿有效。用于接收外

设接口来的中断请求。

③工作方式:

a. 优先级设置方式:全嵌套方式(固定优先级方式)、特殊全嵌套方

式(可响应同级中断方式)、轮转优先级方式、特殊轮转优先级方式。

b.中断源屏蔽方式:普通屏蔽方式、特殊屏蔽方式。

c.中断结束方式:中断自动结束方式、中断非自动结束方式(包括一

般中断结束方式、特殊中断结束方式)。

d.系统总路线连接方式:缓冲方式、非缓冲方式。

e.中断请求信号触发方式:边沿触发方式、电平触发方式。

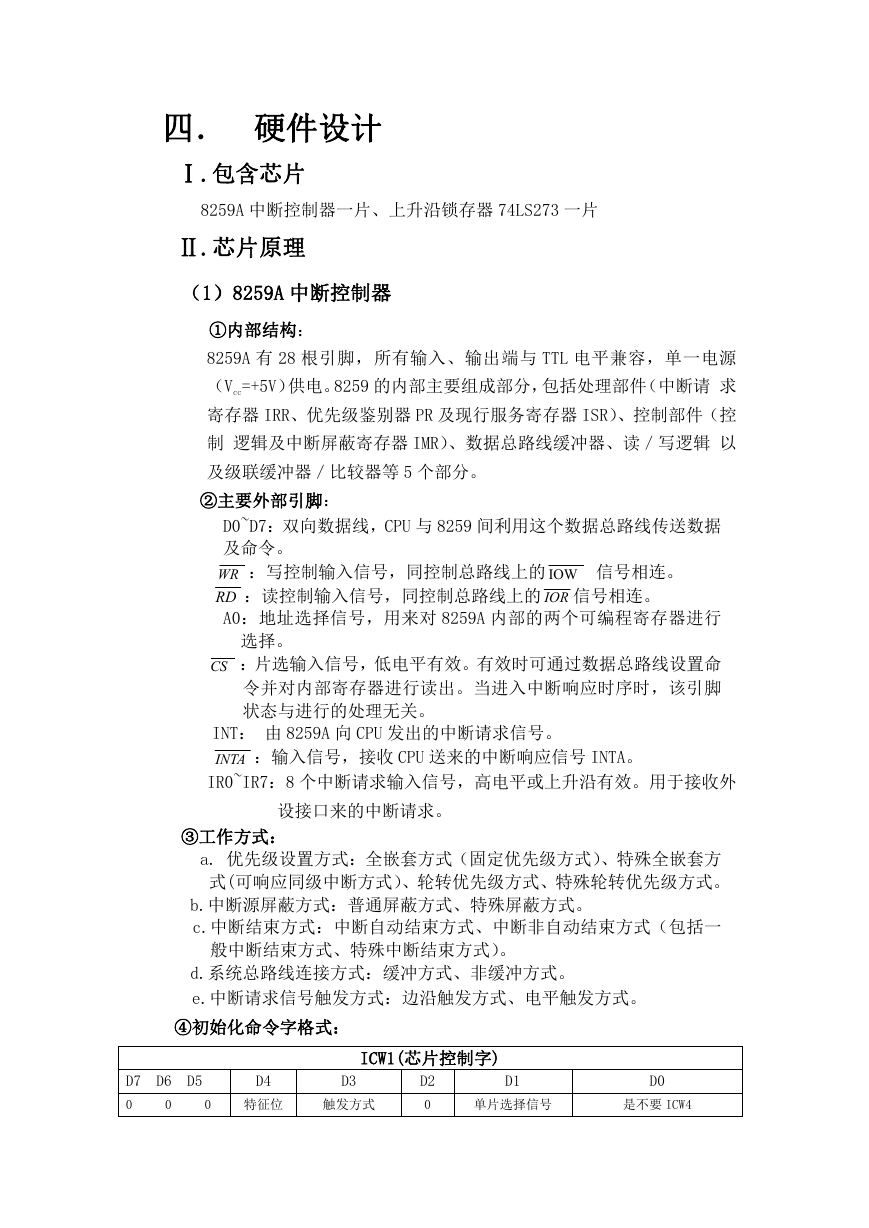

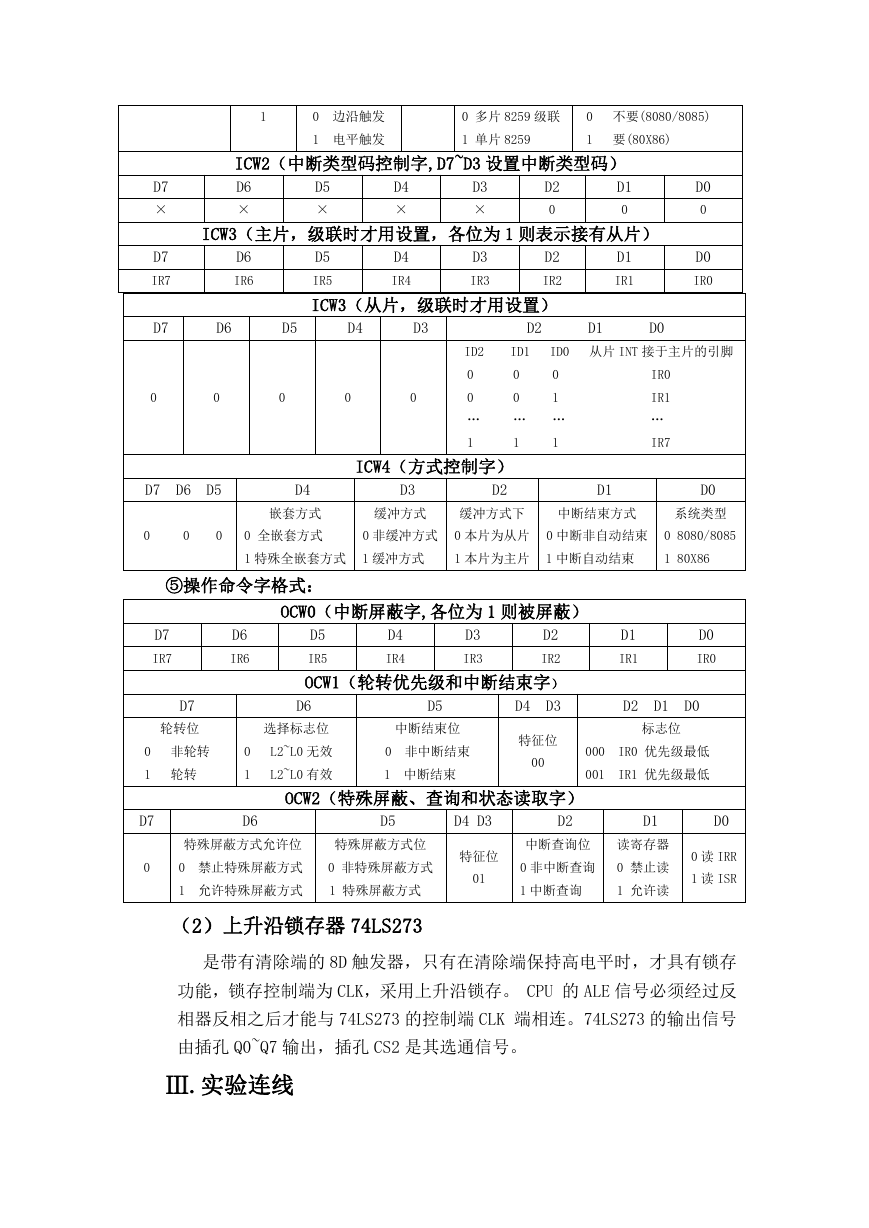

④初始化命令字格式:

ICW1(芯片控制字)

D7

D6

D5

D4

D3

0

0

0

特征位

触发方式

D2

0

D1

D0

单片选择信号

是不要 ICW4

�

1

0 边沿触发

0 多片 8259 级联

0 不要(8080/8085)

1 电平触发

1 单片 8259

1 要(80X86)

ICW2(中断类型码控制字,D7~D3 设置中断类型码)

D6

D1

D4

D3

D5

D2

×

×

×

×

0

0

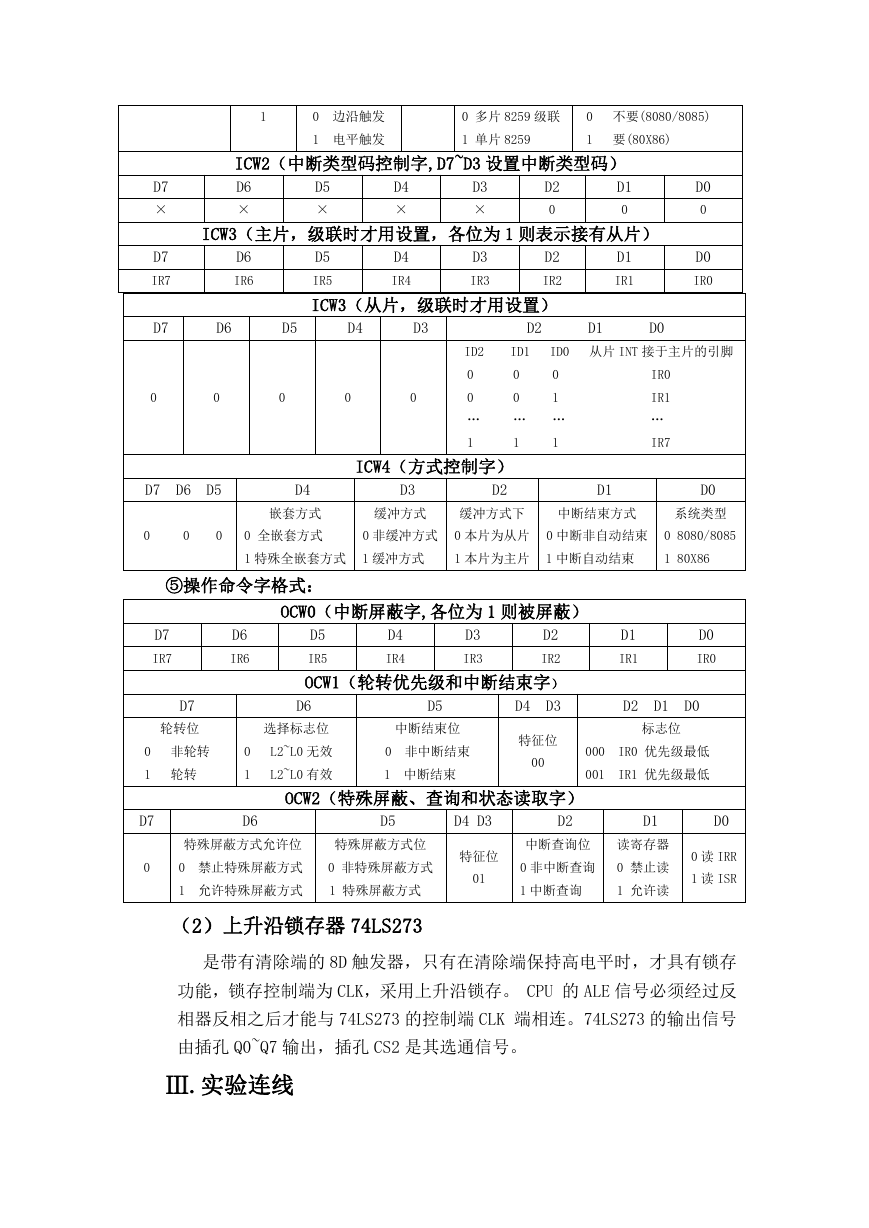

ICW3(主片,级联时才用设置,各位为 1 则表示接有从片)

D6

IR6

D5

IR5

D4

IR4

D3

IR3

D2

IR2

D1

IR1

ICW3(从片,级联时才用设置)

D6

D5

D4

D3

D2

D1

D0

D7

×

D7

IR7

D7

D0

0

D0

IR0

ID2

ID1

ID0 从片 INT 接于主片的引脚

0

0

0

0

0

0

0

…

0

0

…

D7

D6

D5

D4

1

1

ICW4(方式控制字)

D2

D3

0

1

…

1

IR0

IR1

…

IR7

D1

D0

嵌套方式

缓冲方式

缓冲方式下

中断结束方式

系统类型

0

0

0

0 全嵌套方式

0 非缓冲方式

0 本片为从片

0 中断非自动结束

0 8080/8085

1 特殊全嵌套方式

1 缓冲方式

1 本片为主片

1 中断自动结束

1 80X86

⑤操作命令字格式:

OCW0(中断屏蔽字,各位为 1 则被屏蔽)

D5

D4

D3

D2

IR4

IR5

IR2

OCW1(轮转优先级和中断结束字)

D6

D3

IR3

D5

D4

D7

IR7

D6

IR6

D7

轮转位

D1

IR1

D0

IR0

D2

D1

D0

标志位

000 IR0 优先级最低

001 IR1 优先级最低

特征位

00

选择标志位

中断结束位

0 非轮转

1 轮转

0

1

L2~L0 无效

L2~L0 有效

0 非中断结束

1 中断结束

OCW2(特殊屏蔽、查询和状态读取字)

D7

D6

D5

D4 D3

D2

D1

D0

特殊屏蔽方式允许位

特殊屏蔽方式位

0

0 禁止特殊屏蔽方式

0 非特殊屏蔽方式

1 允许特殊屏蔽方式

1 特殊屏蔽方式

特征位

01

中断查询位

读寄存器

0 非中断查询

0 禁止读

1 中断查询

1 允许读

0 读 IRR

1 读 ISR

(2)上升沿锁存器 74LS273

是带有清除端的 8D 触发器,只有在清除端保持高电平时,才具有锁存

功能,锁存控制端为 CLK,采用上升沿锁存。 CPU 的 ALE 信号必须经过反

相器反相之后才能与 74LS273 的控制端 CLK 端相连。74LS273 的输出信号

由插孔 Q0~Q7 输出,插孔 CS2 是其选通信号。

Ⅲ.实验连线

�

电平开关的输出端 K1~K4 分别与 8259A 的 IR0~IR3 对应连接。简单 I/O

单元的输出端(即 74LS273 的输出端)Q0~Q3 分别与发光二极管的输入端

L1~L4 对应连接。Q4 与蜂鸣器的插孔相连。8259A 的 CS 端接 FF80H 孔,

74LS273 的 CS 端接 FF90H 孔。8259A 的 INT 连 8088 的 INTR,8259A 的 INTA

连 8088 的 INTA。

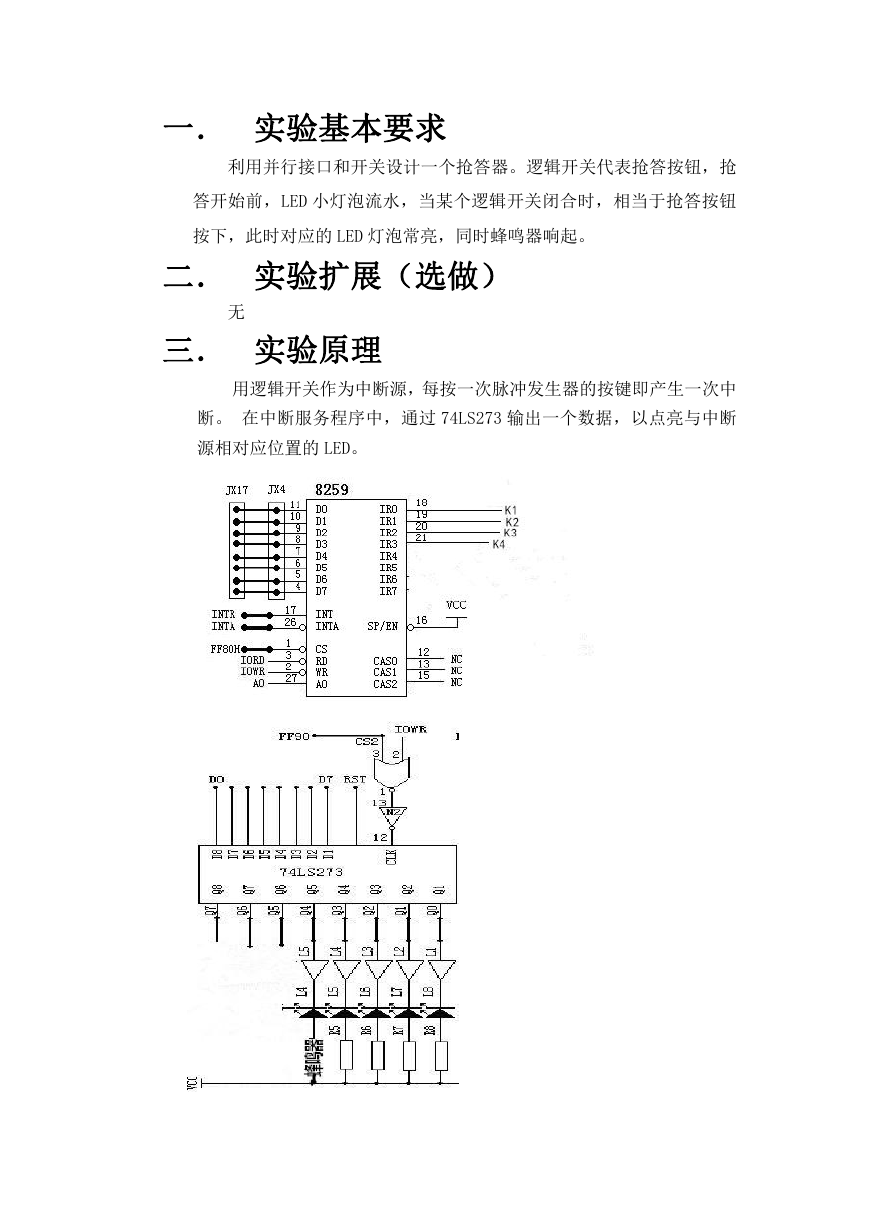

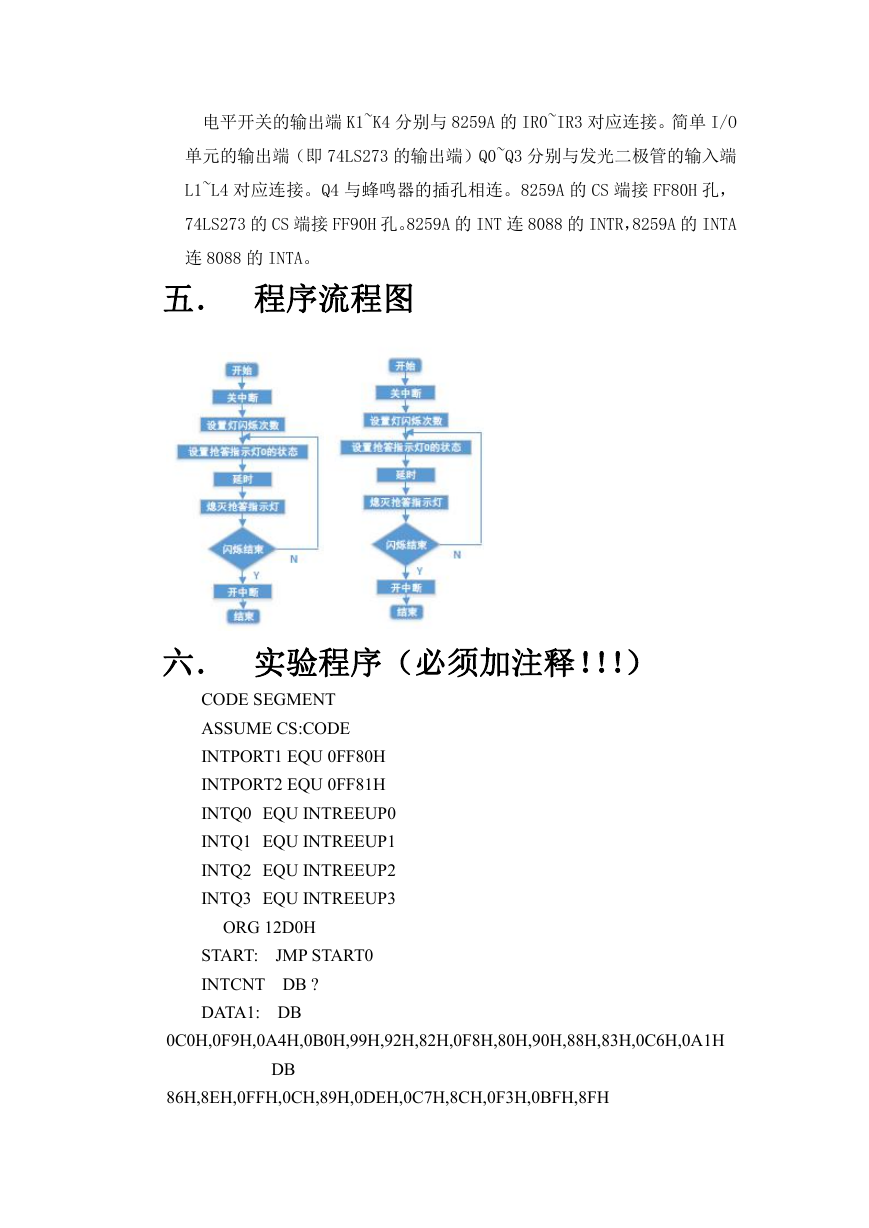

五. 程序流程图

六. 实验程序(必须加注释!!!)

CODE SEGMENT

ASSUME CS:CODE

INTPORT1 EQU 0FF80H

INTPORT2 EQU 0FF81H

INTQ0 EQU INTREEUP0

INTQ1 EQU INTREEUP1

INTQ2 EQU INTREEUP2

INTQ3 EQU INTREEUP3

ORG 12D0H

JMP START0

START:

INTCNT DB ?

DATA1: DB

0C0H,0F9H,0A4H,0B0H,99H,92H,82H,0F8H,80H,90H,88H,83H,0C6H,0A1H

DB

86H,8EH,0FFH,0CH,89H,0DEH,0C7H,8CH,0F3H,0BFH,8FH

�

START:

CLD

;四路抢答器对应四个

;中断子程序

CALL WRINTVER0

CALL WRINTVER1

CALL WRINTVER2

CALL WRINTVER3

MOV

AL,1BH

;ICW4

;OCW1

;TIME=1

;四个中断向量表

DX,INTPORT1

DX,AL

AL,08H

DX,INTPORT2

DX,AL

AL,09H

DX,AL

AL,0F0H

DX,AL

intcnt,01H

MOV

OUT

MOV

MOV

OUT

MOV

OUT

MOV

OUT

MOV

STI

MOV

MOV

ROR

MOV

OUT

MOV

LOOP

JMP WAITING

MOV

AX,0H

ES,AX

MOV

DI,0020H

MOV

LEA

AX,INTQ0

STOSW

MOV

STOSW

RET

MOV

MOV

AX,0H

ES,AX

AX,0000h

;流水灯

BL,0FEH

AL,BL

BL,1

DX,0FF90H ;273 口地址

DX,AL

CX,0

$

WAITING:

WRINTVER0:

WRINTVER1:

�

WRINTVER2:

WRINTVER3:

INTREEUP0:

L1:

DI,0024H

AX,INTQ1

AX,0000h

AX,0H

ES,AX

DI,0028H

AX,INTQ2

AX,0000h

MOV

LEA

STOSW

MOV

STOSW

RET

MOV

MOV

MOV

LEA

STOSW

MOV

STOSW

RET

MOV

MOV

MOV

LEA

STOSW

MOV

STOSW

RET

PUSH AX

PUSH

BX

DX

PUSH

AX,0H

ES,AX

DI,002CH

AX,INTQ3

AX,0000h

;一号小灯和蜂鸣器,Oi 控制字

;一号小灯延时闪烁

CLI

MOV

MOV

MOV

OUT

MOV

LOOP

OUT

MOV

LOOP

BH,0AH

AL,0EEH

DX,0FF90H

DX,AL

CX,0

$

DX,AL

CX,0

$

�

INTREEUP1:

L2:

BH

L1

AL,20H

DX,0FF80H

DX,AL

DX

BX

AX

DEC

JNZ

MOV

MOV

OUT

STI

POP

POP

POP

IRET

PUSH AX

BX

PUSH

PUSH

DX

CLI

MOV

MOV

MOV

OUT

MOV

LOOP

OUT

MOV

LOOP

DEC

JNZ

MOV

MOV

OUT

STI

POP

POP

POP

IRET

BH,0AH

AL,0EDH

DX,0FF90H

DX,AL

CX,0

$

DX,AL

CX,0

$

BH

L2

AL,20H

DX,0FF80H

DX,AL

DX

BX

AX

INTREEUP2: PUSH AX

BX

PUSH

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc