第1章 系统复位、中断、工作模式和系统控制模块(SYS)

1.1 系统控制模块介绍

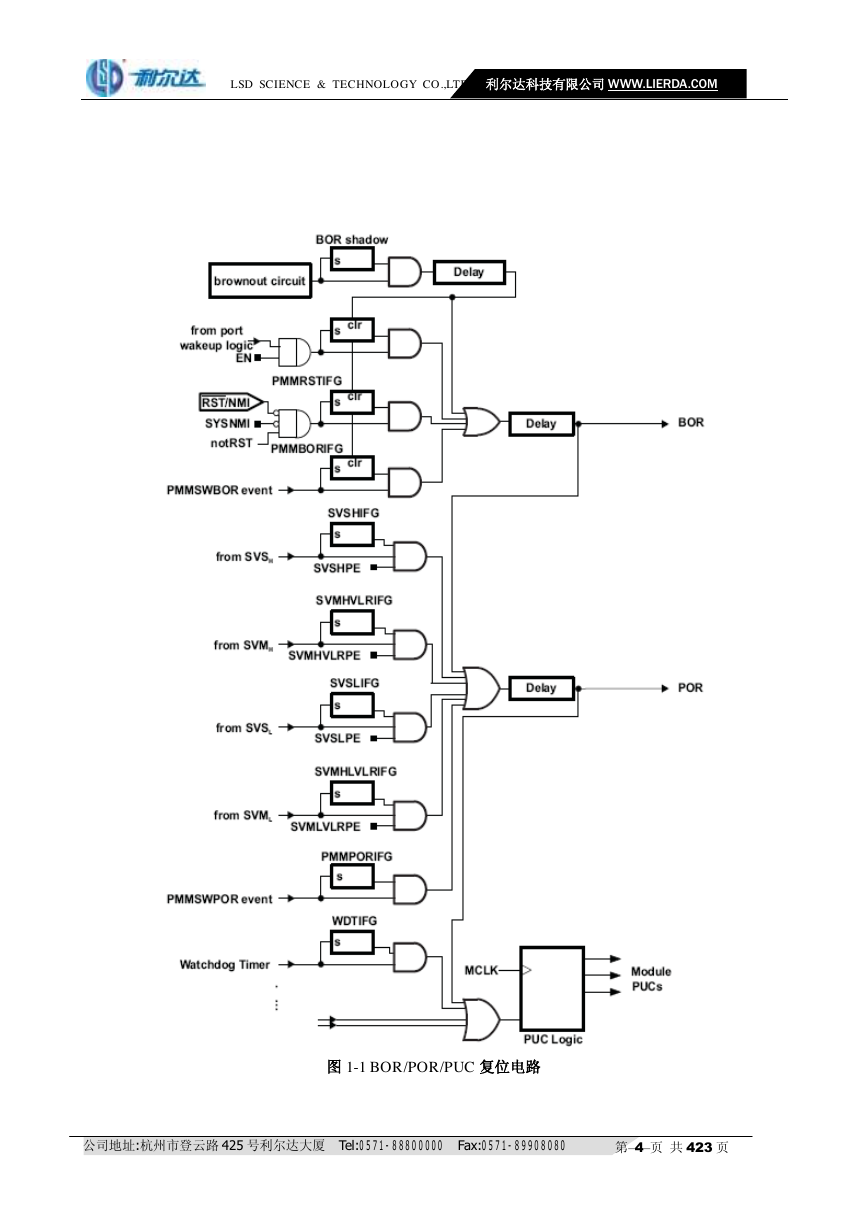

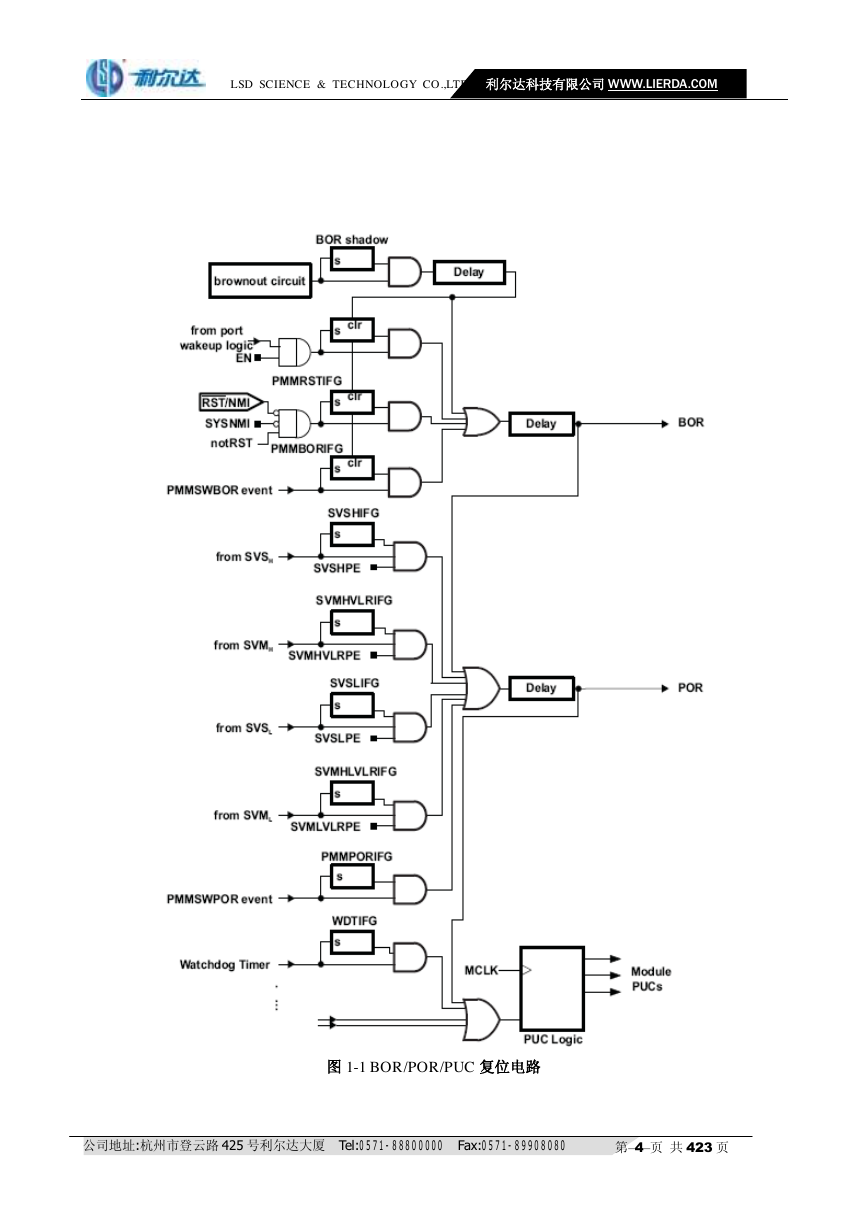

1.2 系统复位和初始化

1.2.1 系统复位后的初始状态

1.3 中断

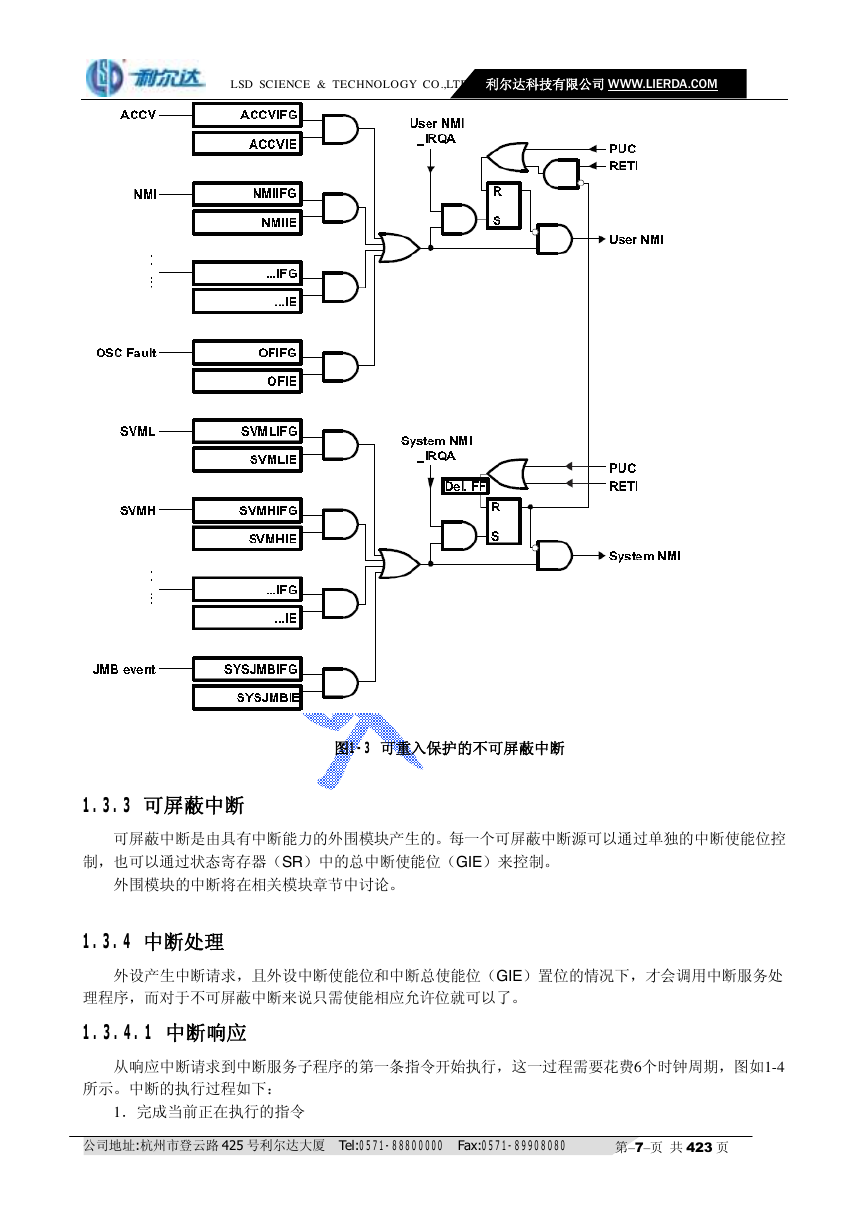

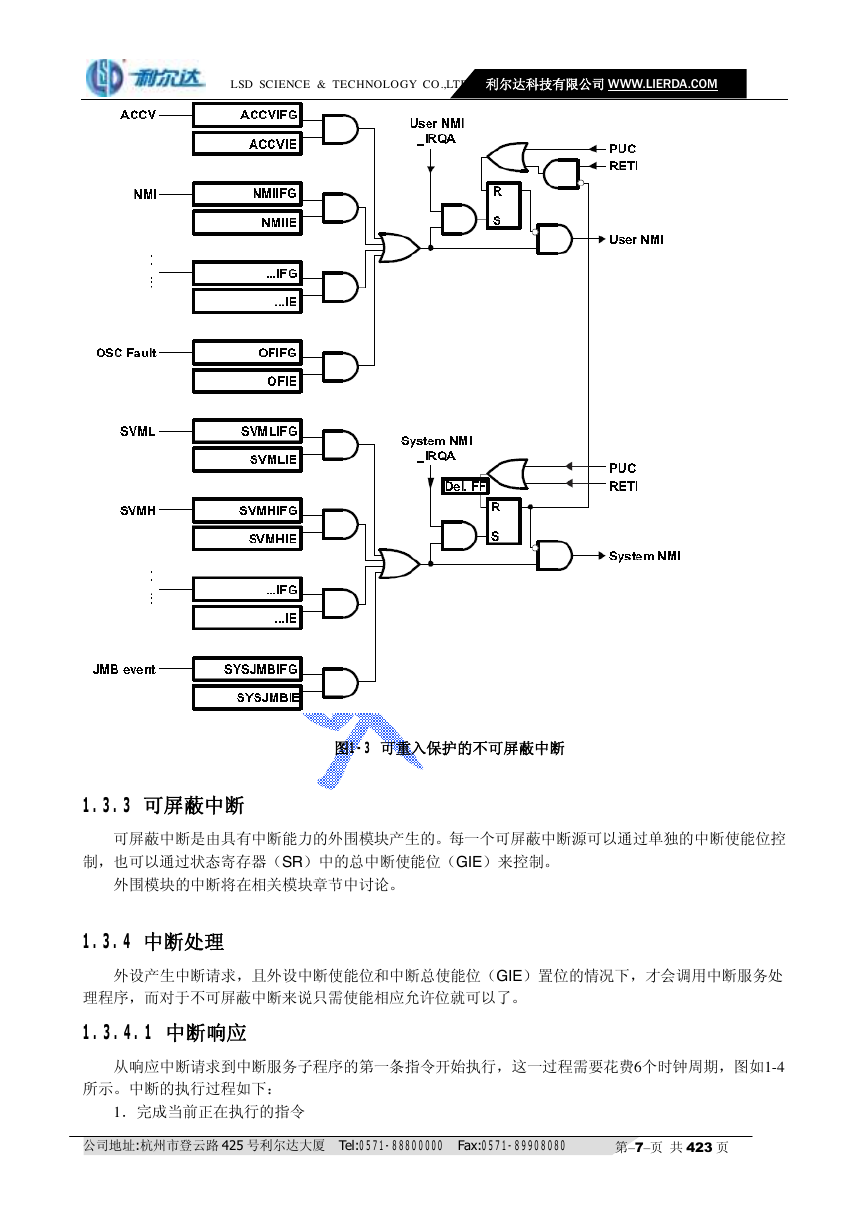

1.3.1 不可屏蔽中断(NMI)

1.3.2 SNMI时序

1.3.3 可屏蔽中断

1.3.4 中断处理

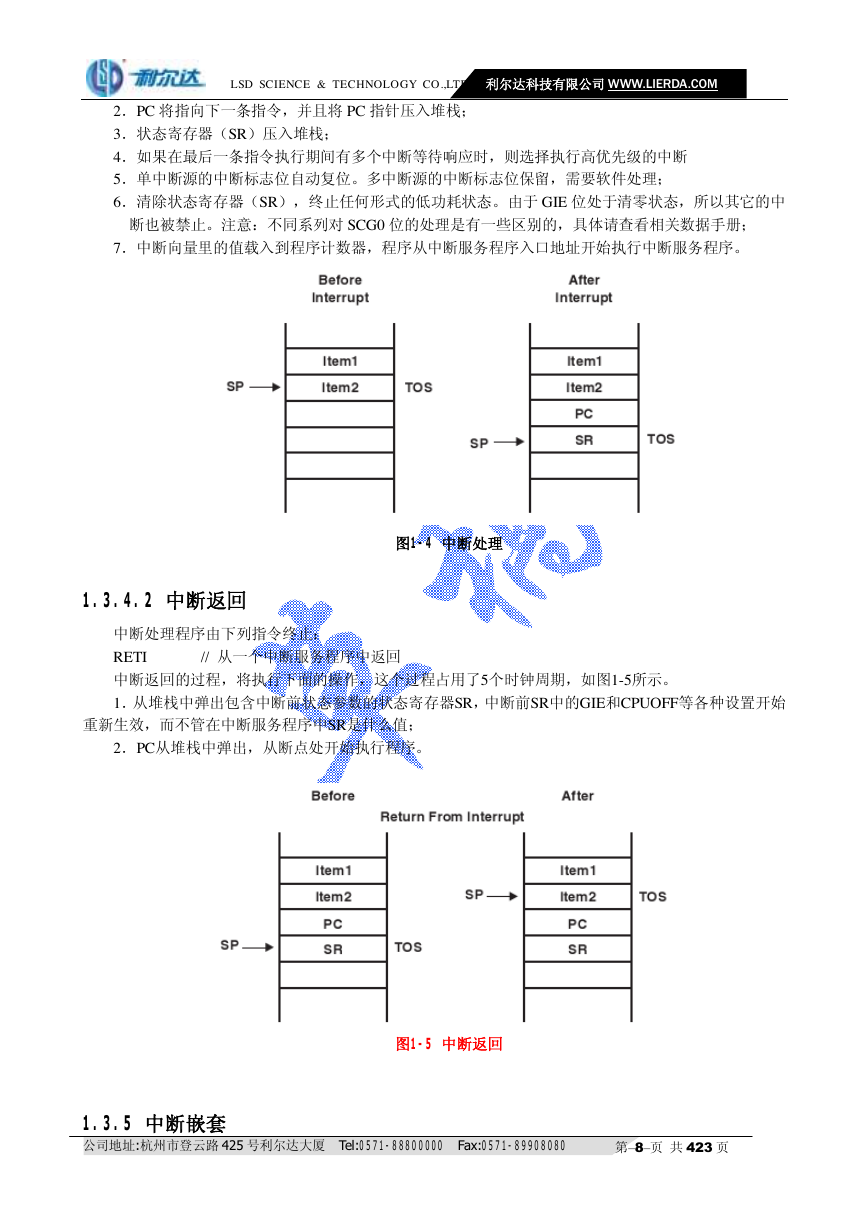

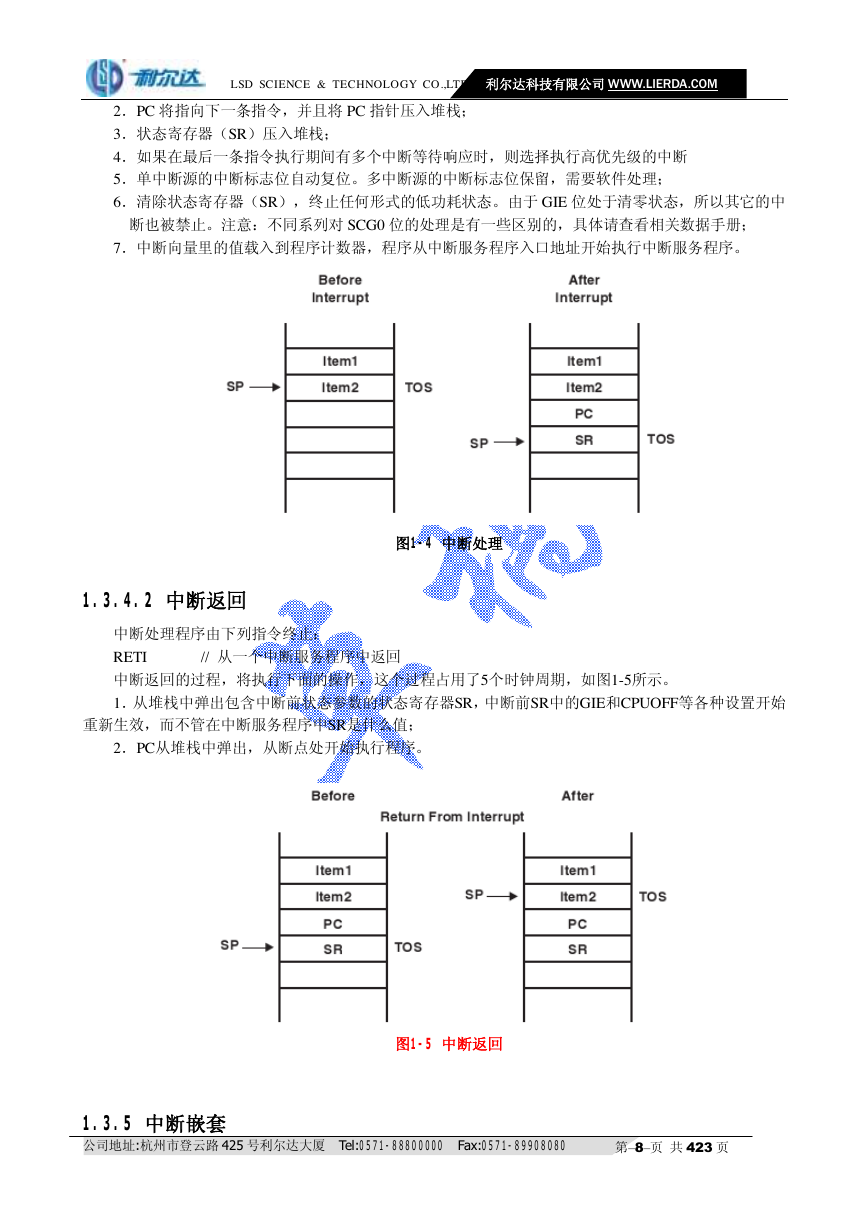

1.3.4.1 中断响应

1.3.4.2 中断返回

1.3.5 中断嵌套

1.3.6 中断向量

1.3.6.1 备用中断向量

1.3.7 SYS中断向量发生

1.3.7.2 SYSBERRIV 总线错误中断向量发生器

1.3.7.1 SYSSNIV软件示例

1.4 工作模式

1.4.1 进入和退出低功耗模式(LPM0~LPM4)

1.4.2 进入和退出低功耗模式(LPMX.5)

1.4.3 低功耗模式下的延长时间

1.5 低功耗应用的原则

1.6 未使用引脚的连接

1.7 /RST/NMI引脚配置

1.8 配置JTAG引脚

1.9 启动代码

1.10 Bootstrap装载区(BSL)

1.11 存储器映射-用法和功能

1.11.1 空存储器空间

1.11.2 具有保密熔丝的JTAG锁定机制

1.12 JTAG邮箱系统(JMB)

1.12.1 JMB配置

1.12.2 JMBOUT0及JMBOUT1输出邮箱

1.12.3 JMBIN0及JMBIN1输入邮箱

1.12.4 JMB的NMI使用

1.13 设备描述符表

1.13.1 识别芯片类型

1.13.2 TLV描述符

1.13.3 外围模块描述符

1.13.4 校准值

1.13.4.1 REF校准

1.13.4.2 ADC偏置及增益校正

1.13.4.3 温度传感器校正

1.14 特殊功能寄存器

1.15 SYS设置寄存器

第2章 电源管理模块和供电电压监视器

2.1 PMM介绍

2.2 电源管理模块操作

2.2.1 Vcore和稳压器

2.2.2 电压管理和监视

2.2.2.1 SVS/SVM电压门限值

2.2.2.2 初级电源电压管理与监控(SVSh/SVMh)

2.2.2.3 次级的电源电压管理与监控

2.2.3 电源电压管理与监控-上电

2.2.4 提高Vcore满足更高MCLK频率

2.2.5 降低Vcore电压以减少系统功耗

2.2.6 LPM3.5,LPM4.5

2.2.7 BOR,软件BOR及软件POR

2.2.8 SVS/SVM性能模式(正常和高性能模式)

2.2.8.1 在DEBUG模式下的唤醒时间

2.2.9 PMM中断

2.2.10 IO口控制

2.2.11 SVM输出

2.3 PMM寄存器介绍

第3章 标准时钟系统

3.1 时钟系统介绍

3.2 UCS操作

3.2.1 UCS模块在超低功耗方面的特性

3.2.2 内部低功耗低频率振荡器(VL0)

3.2.3 内部低频参考时钟(REF0)

3.2.4 XT1振荡器

3.2.5 晶振XT2

3.2.6 数值控制振荡器(DCO)

3.2.6.1 DCO频率调整

3.2.7 锁频环(FLL)

3.2.8 DCO调制器

3.2.9 禁止FLL硬件和调制器

3.2.10 低功耗模式下FLL

3.2.11 在低功耗模式下,外部模块的请求操作

3.2.12 UCS模块自动失效安全操作

3.2.13 时钟信号的同步

3.3 模块振荡器(MODOSC)

3.3.1 MODOSC操作

3.4 UCS模块寄存器

第4章 CPUX

4.1 CPU介绍

4.2 中断

4.3 CPU寄存器

4.3.1 程序计数器(PC)

4.3.2 堆栈指针(SP)

4.3.3 状态寄存器(SR)

4.3.4 常数发生器(CG1及CG2)

4.3.4.1 常数发生器-扩展指令集

4.3.5 通用寄存器(R4-R15)

4.4 寻址模式

4.4.1寄存器寻址模式

4.4.2 变址寻址模式

4.4.2.1 低64KB存储范围的变址寻址

4.4.2.2 高字节变址寻址MSP430指令

4.4.2.3 变址寻址模式的MSP430X指令

4.4.3 符号寻址

4.4.3.1 低64KB的符号寻址

4.4.3.2 对超出低64KB地址范围的符号寻址方式的MSP430指令

4.4.3.3 符号寻址的MSP430X指令

4.4.4 绝对寻址

4.4.4.1 低64KB存储范围的绝对寻址

4.4.4.2 MSP430X指令绝对寻址

4.4.5 寄存器间接寻址

4.4.6 间接增量寻址

4.4.7 立即数寻址

4.4.7.1 MSP430指令的立即数寻址

4.4.7.2 MSP430X的立即数模式

4.5 MSP430与MSP430X指令

4.5.1 MSP430指令

4.5.1.1 MSP430的双操作数指令(格式1)

4.5.1.2 MSP430单操作数指令(格式2)

4.5.1.3 跳转指令

4.5.1.4 仿真指令

4.5.1.5 MSP430指令执行

4.5.2 扩展指令

4.5.2.1寄存器模式扩展字

4.5.2.2 非寄存器模式下的扩展字

4.5.2.3 双操作数(格式1)的扩展指令

4.5.2.4 扩展单操作数(格式2)指令

4.5.2.5 扩展的仿真指令

4.5.2.6 地址指令

4.5.2.7 指令的执行

4.6 指令集描述

4.6.1 扩展指令的二进制描述

4.6.2 MSP430指令

4.6.3 扩展指令

第5章 Flash存储控制器

5.1 Flash存储器介绍

5.2 Flash存储器的分段结构

5.2.1 段A

5.3 Flash存储器操作

5.3.1擦除Flash存储器

5.3.1.1擦除周期

5.3.1.2擦除主存储器

5.3.1.3擦除信息存储器或Flash段

5.3.1.4从Flash存储器中启动擦除

5.3.1.5从RAM存储器中启动擦除

5.3.2Flash存储器写操作

5.3.2.1写入字节/字

5.3.2.2从Flash存储器中启动字/字节写入

5.3.2.3从RAM区中启动字/字节写入

5.3.2.4写入长字

5.3.2.5从Flash存储器中启动长字写入

5.3.2.6从RAM区中启动长字写入

5.3.2.7块写

5.3.2.8块写入的流程和范例

5.3.3写入或者擦除期间访问Flash存储器

5.3.4校验Flash存储器

5.3.5配置和访问Flash存储控制器

5.3.6flash存储控制器中断

5.3.7Flash存储器编程

5.3.7.1通过JTAG的Flash存储器编程

5.3.7.2通过引导加载程序(BSL)对Flash存储器编程

5.4Flash存储器寄存器

未标题

第6章 RAM控制器

6.1 RAM控制器介绍

6.2RAMCTL操作

6.3RAMCTL模块寄存器

第7章 DMA控制器

7.1DMA介绍

7.2 DMA操作

7.2.1DMA寻址模式

7.2.2 DMA传输模式

7.2.2.1 单次传输

7.2.2.2 块传输

7.2.2.3 突发块传输

7.2.3 启动DMA传输

7.2.3.1边沿触发

7.2.3.2电平触发

7.2.4DMA传输的终止执行指令

7.2.5停止DMA传输

7.2.6DMA通道优先级

7.2.7DMA传输周期

7.2.8系统中断下使用DMA

7.2.9DMA控制器中断

7.2.9.1DMAIV程序示例

7.2.10DMA控制器及使用USCI_B I2C模块

7.2.11DMA控制器及使用ADC12

7.2.12在DMA控制器及使用DAC12

7.3DMA寄存器

第8章 数字I/O口

8.1数字I/O口介绍

8.2操作数字I/O口

8.2.1输入寄存器PxIN

8.2.2输出寄存器 PxOUT

8.2.3输入/输出方向寄存器PxdIR

8.2.4上拉/下拉电阻能寄存器 PxREN

8.2.5输出驱动能力增强寄存器PxDS

8.2.6功能选择寄存器PxSEL

8.2.7 P1和P2口中断,端口中断

8.2.7.1 P1IV,P2IV软件例程

8.2.7.2中断沿选择寄存器P1IES,P2IES

8.2.7.3中断使能寄存器P1IE,P2IE

8.2.8配置未使用的端口管脚

8.3 IO配置及LPMx.5低功耗模式

8.3.1通过IO口唤醒LPMx.5

8.4数字I/O端口寄存器

第9章 端口映射控制器

9.1端口映射控制器介绍

9.2端口映射控制器的操作

9.2.1存取操作

9.2.2映射

9.2.3软件例程

9.3端口映射控制寄存器

第10章 CRC模块

10.1 CRC模块介绍

10.2生成CRC校验和

10.2.1 CRC实现

10.2.2汇编例程

10.2.2.1通用汇编例程

10.2.2.2参考数据序列

10.3 CRC模块寄存器

第11章 看门狗定时器

11.1 WDT_A简介

11.2 操作WDT_A

11.2.1看门狗定时器计数器(WDTCNT)

11.2.2看门狗模式

11.2.3间隔定时器模式

11.2.4 看门狗定时器中断

11.2.5时钟失效保护特性

11.2.6低功耗模式下的操作

11.2.7 软件举例

11.3 WDT_A寄存器

第12章 定时器Timer_A

12.1 Timer_A介绍

12.2 Timer_A操作

12.2.1 16位定时计数器

时钟源的选择和分频

12.2.2启动计数器

12.2.3定时器模式控制

12.2.3.1增计数模式

12.2.3.2连续计数模式

12.2.3.3连续计数模式的应用

12.2.3.4增/减计数模式

12.2.3.5增减技术模式的应用

12.2.4捕获/比较模块

12.2.4.1捕获模式

12.2.4.2比较模式

12.2.5 输出单元

12.2.5.1输出模式

12.2.6 Timer_A中断

12.2.6.1 TAxCCR0中断

12.2.6.2 TAIV,中断向量发生器

12.3 Timer_A寄存器

第14章 RTC控制器

14.1 RTC_A介绍

14.2 RTC_A操作

14.2.1计数器模式

14.2.2

14.2.2.1实时时钟和预分频器

14.2.2.2实时时钟闹钟功能

14.2.2.3在日历模式下读写实时时钟寄存器

14.2.3实时时钟中断

14.2.3.1日历模式下的实时时钟中断

14.2.3.2计数器模式下实时时钟中断

14.2.4实时时钟校准

14.3实时时钟寄存器

第15章 32位硬件乘法器

15.1 MPY32介绍

15.2 硬件乘法器操作

15.2.1 操作数寄存器

15.2.2结果寄存器

15.2.2.1 MACS的下溢和上溢

15.2.3 软件例程

15.2.4 小数部分

15.2.4.1小数模式

15.2.4.2饱和模式

15.2.5综合小结

15.2.6结果寄存器间接寻址

15.2.7 使用中断

15.2.7.1 保存和恢复

15.2.8使用DMA

15.3 32位硬件乘法器寄存器

第16章 REF

16.1 REF简介

16.2工作原理

16.2.1低功耗操作

16.2.3请求参考系统

16.2.3.1 REFBGACT,REFGENACT,REFGENBUSY

16.2.3.2 ADC12_A

16.2.3.3 DAC12_A

16.2.3.4 LCD_B

16.3 REF寄存器

第17章 ADC12_A

17.1 ADC12_A介绍

17.2 ADC12_A操作

17.2.1 12位ADC内核

17.2.1.1选择转换时钟

17.2.2 ADC12_A输入和多路复用器

17.2.2.1选择模拟端口

17.2.3电压参考发生器

17.2.3.1内部参考电压的低功耗特性

17.2.4自动断电

17.2.5采样转换时序

17.2.5.1扩展采用模式

17.2.6转换存储器

17.2.7 ADC12_A转换模式

17.2.7.1单通道单次转换模式

17.2.7.2序列通道单次转换模式

17.2.7.3单通道多次转换

17.2.7.4序列通道多次转换

17.2.7.5使用多路采样转换(ADC12MSC)位

17.2.7.6停止转换

17.2.9 ADC12_A接地和噪声的考虑

17.2.10 ADC12_A中断

17.2.10.1 ADC12IV,中断向量发生器

17.2.10.2 ADC12_A中断处理软件示例

17.3 ADC12_A寄存器

第18章 COMP_B

18.1 概述

18.2使用

18.2.1比较器

18.2.2模拟输入开关

18.2.3端口逻辑

18.2.4输入短路开关

18.2.5输出滤波器

18.2.6参考电压发生器

18.2.7 COMP_B,端口禁止寄存器CBPD

18.2.8 COMP-B的中断

18.2.9使用COMP_B测量电阻元件

18.3 寄存器

第19章 USCI-UART

19.1 USCI概述

19.2 USCI介绍:UART模式

19.3 USCI操作:UART模式

19.3.1 USCI初始化和复位

19.3.2字符格式

19.3.3异步通信格式

19.3.3.1线路空闲多处理器模式

19.3.3.2地址位多处理器模式

19.3.4自动波特率检测

19.3.4.1发送一个打断/同步字段

19.3.5IrDA编码和解码

19.3.5.1 IrDA编码

19.3.5.2 IrDA解码

19.3.6自动错误检测

19.3.7使能USCI接收

19.3.7.1接收数据抑制尖峰

19.3.8使能USCI发送

19.3.9产生UART波特率

19.3.9.1产生低频波特率

19.3.9.2产生过采样波特率

19.3.10设置波特率

19.3.10.1设置低频波特率模式

19.3.10.2设置过采样波特率模式

19.3.11发送位时序

19.3.11.1低频波特率模式下位时序

19.3.11.2 过采样波特率模式位时序

19.3.12接收位时序

19.3.13典型的波特率和误差

19.3.14 低功耗UART模式下使用USCI模块

19.3.15 USCI中断

19.3.15.1 USCI发送中断操作

19.3.15.2 USCI接收中断操作

19.3.15.3 UCAxIV,中断向量发生器

19.4 USCI寄存器:UART模式

第20章 USCI-SPI

20.1 USCI概述

20.2 USCI介绍:SPI模式

20.3 USCI的操作:SPI模式

20.3.1初始化及复位USCI

20.3.2字符格式

20.3.3主模式

20.3.3.1 4线制SPI主模式

20.3.4从模式

20.3.4.1 4线制SPI从模式

20.3.5 使能SPI

20.3.5.1使能发送

20.3.5.2使能接收

20.3.6串行时钟控制

20.3.6.1串行时钟的极性与相位

20.3.7 低功耗模式下使用SPI模式

20.3.8 SPI中断

20.3.8.1 SPI发送中断操作

20.3.8.2 SPI接收中断的运行

20.3.8.3中断向量发生器:UCxIV

20.4 USCI寄存器-SPI模式

第21章 USCI-I2C

21.1通用串行通信接口(USCI)概述

21.2 USCI介绍:I2C模式

21.3 USCI操作:I2C模式

21.3.1 初始化及复位USCI

21.3.2 I2C串行数据

21.3.3 I2C寻址方式

21.3.3.1 7位寻址

21.3.3.2 10位寻址

21.3.3.3重复START条件

21.3.4 I2C模式下的操作方式

21.3.4.1从芯片模式

21.3.4.2主模式

21.3.4.3总线仲裁

21.3.5 I2C时钟的产生与同步

21.3.5.1 时钟伸展

21.3.6 低功耗模式下的USCI模块中I2C模式的使用

21.3.7 I2C模式下的USCI中断

21.3.7.1 I2C发送中断操作

21.3.7.2 I2C接收中断操作

21.3.7.3 I2C状态改变中断操作

21.3.7.4 UCBxIV,中断向量发生器

21.4 USCI寄存器:I2C模式

第22章 USB模块

22.1 USB介绍

22.2 USB模块操作

22.2.1 USB收发器(PHY)

22.2.1.1 PUR引脚D+上拉

22.2.1.2损坏线路短路

22.2.1.3 端口U控制

22.2.2电源系统

22.2.2.1使能/禁止

22.2.2.2通过VUSB,采用USB总线电源为MSP430的其他部分供电

22.2.2.3通过VBS为系统其他组件供电

22.2.2.4限流/过载保护

22.2.3 USB锁相环(PLL)

22.2.3.1更改分频值

22.2.3.2 PLL误差指示器

22.2.3.3 PLL启动顺序

22.2.4 USB控制器引擎

22.2.4.1 USB串行接口引擎(SIE)

22.2.4.2 USB缓冲管理器(UBM)

22.2.4.3 USB缓冲存储器

22.2.4.4 USB精准时间戳

22.2.4.5暂停/继续逻辑

22.2.4.6复位逻辑

22.2.5 USB向量中断

22.2.6功耗

22.2.7 暂停和继续

22.2.7.1进入暂停

22.2.7.2进入继续模式

22.3 USB传输

22.3.1控制传输

22.3.1.1控制写传输

22.3.1.2没有数据阶段传输的控制写传输

22.3.1.3控制读传输

22.3.2中断传输

22.3.2.1中断输出传输

22.3.2.2中断输入传输

22.3.3批量传输

22.3.3.1批量输出传输

22.3.3.2批量输入传输

22.4寄存器

22.4.1 USB配置寄存器

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc