Application Note 062

IEEE 1284 – Updating the PC Parallel Port

Heidi Frock

Most personal computers today are equipped with a parallel port, commonly used to connect the computer to a

parallel printer. Because it is available on most personal computers, the parallel port is a perfect choice for

connection to other peripheral devices. However, communication to peripherals across the parallel port is limited

because the interface is traditionally unidirectional and there is no standard specification for the interface.

Additionally, although the performance of the PC has dramatically increased, the parallel port has remained the

same. This situation has led to the development of a new parallel port standard – IEEE Standard 1284-1994. This

standard is based on the original Centronics Standard Parallel Port (SPP) specification, and includes the Enhanced

Parallel Port (EPP) and Extended Capabilities Port (ECP).

This document describes SPP, EPP, and ECP, as defined by IEEE 1284.

The Standard Parallel Port – the Centronics Parallel Port

The Standard Parallel Port (SPP) is also known as the Centronics parallel port. Centronics Data Computer

Corporation developed the interface in the mid-1960s to be an 8-bit unidirectional parallel host-to-printer

connection. The interface became widely used; however, no industry-standard specification was developed to

define the interface.

The Centronics "standard" defines a 36-pin champ connector and interface signals for the printer side of the

connection. The host side implementation varied widely until the introduction of the IBM PC in 1981. The host

parallel port implementation used on the IBM PC, also referred to as the PC parallel interface, became the de facto

industry PC parallel port interface. The PC parallel interface defines a 25-pin DSub connector with 8 unidirectional

data lines, four control lines, and five status lines. A description of these signals is in Table 1.

Because there is no written standard, the timing relationships between the handshaking signals vary widely among

printers from different manufacturers, even though they may all claim Centronics compatibility. This document will

focus on the IBM PC parallel interface timing, the most common in the industry.

________________________________

Product and company names are trademarks or trade names of their respective companies.

340897A-01

© Copyright 1995 National Instruments Corporation. All rights reserved.

October 1995

�

Table 1. The IEEE 1284 Signal Line Descriptions

SPP Signal Name

EPP Signal Name

ECP Signal Name

Source

Connector

Pinout

Data8-1

Unidirectional data lines. Data8

is the most significant.

STROBE*

Data is valid during an active

low pulse on this line.

AD8-1

Bi-directional address and data

lines. AD8 is the most

significant.

WRITE*

This signal is low during a write

operation and high during a read

operation.

AUTOFD*

Usage of this line varies. Most

printers will perform a line feed

after each carriage return when

this line is low, and carriage

returns only when this line is

high.

INIT*

This line is held low for a

minimum of 50 µs to reset the

printer and clear the print buffer.

SelectIn*

The host drives this line low to

select the peripheral.

ACK*

The peripheral pulses this line

low when it has received the

previous data and is ready to

receive more data. The rising

edge of ACK* can be enabled to

interrupt the host.

BUSY

The peripheral drives this signal

high to indicate that it is not

ready to receive data.

DSTROBE*

This signal denotes data cycles.

During a write operation, data is

valid when this signal is active.

During a read operation, this

signal is low when the host is

ready to receive data.

INIT*

This line is driven low to

terminate EPP mode and return

to SPP mode.

ASTROBE*

This line denotes address cycles.

When this signal is low, AD8-1

is an address.

INTR*

The peripheral can enable this

signal to interrupt the host on the

low to high transition.

WAIT*

The peripheral drives this signal

low to acknowledge that it has

successfully completed the data

or address transfer initiated by

the host.

PError

Usage of this line varies.

Printers typically drive this

signal high during a paper empty

condition.

Select

The peripheral drives this signal

high when it is selected and

ready for data transfer.

FAULT*

Usage of this line varies.

Peripherals usually drive this

line low when an error condition

exists.

User Defined

User Defined

User Defined

Data8-1

Bi-directional address and data

lines. Data8 is the most

significant.

HostClk

This forward direction

handshaking line is interlocked

with PeriphAck and driven low

when data is valid.

HostAck

In the forward direction, this line

is driven low for a command

transfer, and high for a data

transfer. In the reverse direction,

this signal is a handshaking line

interlocked with PeriphClk.

ReverseRequest*

This line is driven low to place the

parallel port interface in the

reverse direction.

1284 Active

The host drives this line high

while in ECP mode, and low to

terminate ECP mode.

PeriphClk

The peripheral drives this reverse

direction handshaking line low to

indicate that the data is valid.

PeriphClk is interlocked with

HostAck.

PeriphAck

This forward direction

handshaking line is interlocked

with HostClk and driven by the

peripheral to acknowledge data

received from the host. During

reverse direction transfers, the

peripheral drives this line high

during data transfers and low

during command transfers.

AckReverse*

The peripheral drives this line to

follow the level of the

ReverseRequest* line.

XFlag

The peripheral drives this line

high to indicate that it uses ECP

mode.

PeriphRequest*

The peripheral drives this signal

low to request a reverse transfer.

This line can be used to interrupt

the host.

Host/

Peripheral

1284-A: 9 - 2

1284-B: 9 - 2

1284-C: 13 - 6

Host

Host

Host

Host

1284-A: 1

1284-B: 1

1284-C: 15

1284-A: 14

1284-B: 14

1284-C: 17

1284-A: 16

1284-B: 31

1284-C: 14

1284-A: 17

1284-B: 36

1284-C: 16

Peripheral 1284-A: 10

1284-B: 10

1284-C: 3

Peripheral 1284-A: 11

1284-B: 11

1284-C: 1

Peripheral 1284-A: 12

1284-B: 12

1284-C: 5

Peripheral 1284-A: 13

1284-B: 13

1284-C: 2

Peripheral 1284-A: 15

1284-B: 32

1284-C: 4

2

�

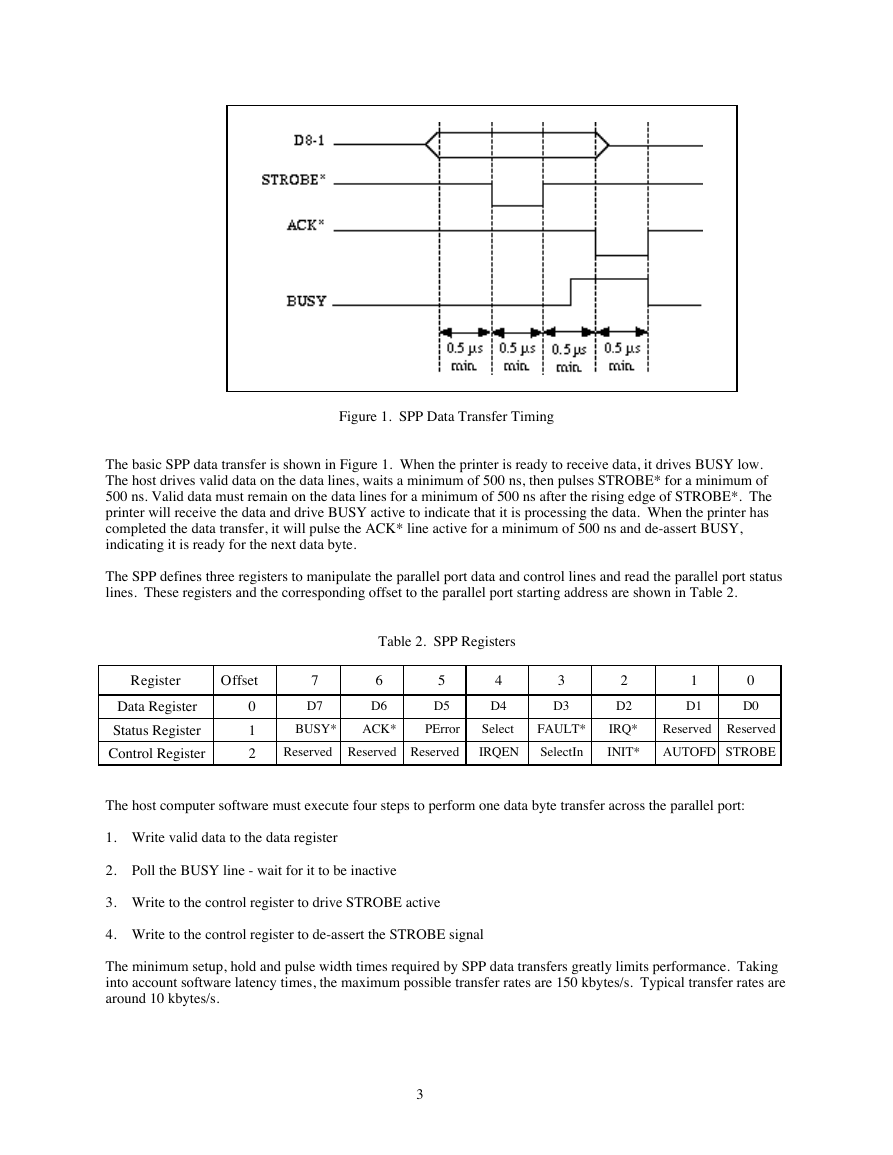

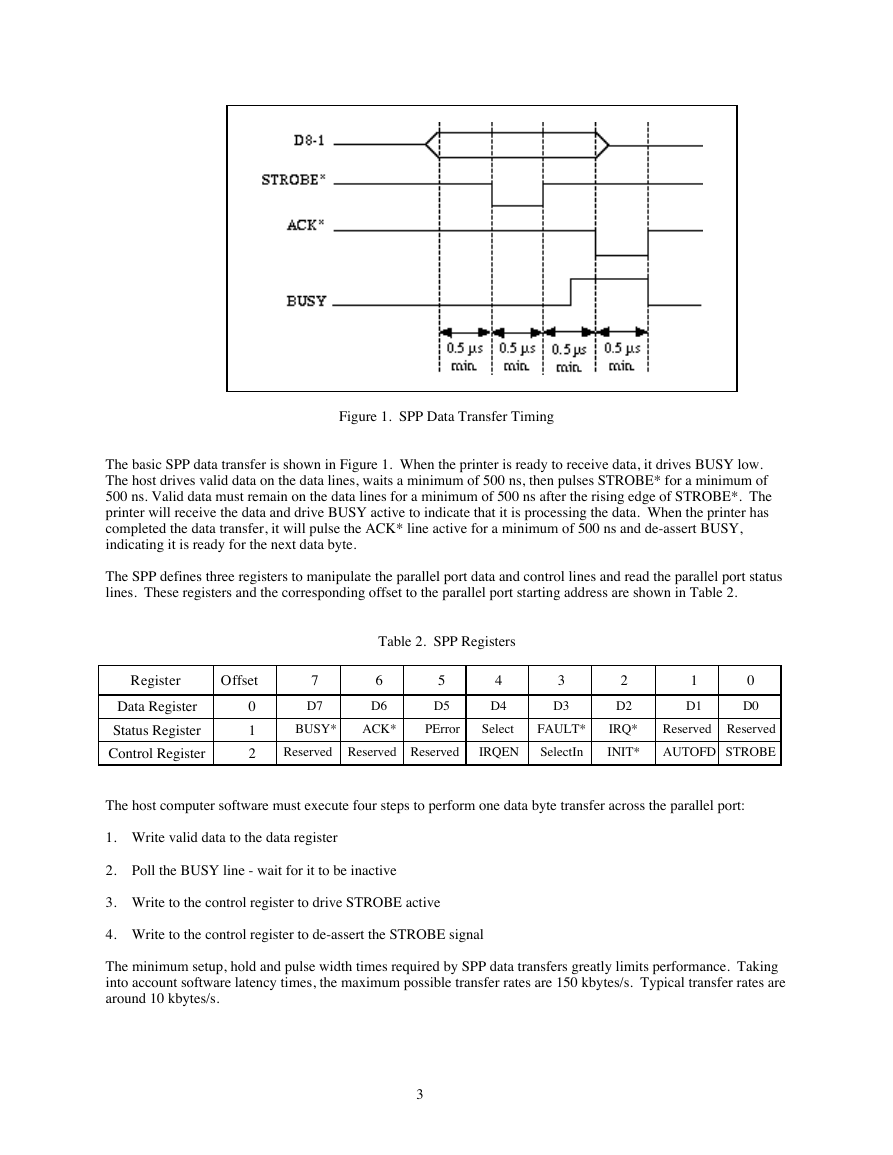

Figure 1. SPP Data Transfer Timing

The basic SPP data transfer is shown in Figure 1. When the printer is ready to receive data, it drives BUSY low.

The host drives valid data on the data lines, waits a minimum of 500 ns, then pulses STROBE* for a minimum of

500 ns. Valid data must remain on the data lines for a minimum of 500 ns after the rising edge of STROBE*. The

printer will receive the data and drive BUSY active to indicate that it is processing the data. When the printer has

completed the data transfer, it will pulse the ACK* line active for a minimum of 500 ns and de-assert BUSY,

indicating it is ready for the next data byte.

The SPP defines three registers to manipulate the parallel port data and control lines and read the parallel port status

lines. These registers and the corresponding offset to the parallel port starting address are shown in Table 2.

Table 2. SPP Registers

Register

Offset

Data Register

Status Register

Control Register

0

1

2

7

D7

6

D6

5

D5

4

D4

3

D3

2

D2

1

D1

0

D0

BUSY*

ACK*

PError

Select

FAULT*

IRQ*

Reserved Reserved

Reserved Reserved Reserved

IRQEN

SelectIn

INIT*

AUTOFD STROBE

The host computer software must execute four steps to perform one data byte transfer across the parallel port:

1. Write valid data to the data register

2. Poll the BUSY line - wait for it to be inactive

3. Write to the control register to drive STROBE active

4. Write to the control register to de-assert the STROBE signal

The minimum setup, hold and pulse width times required by SPP data transfers greatly limits performance. Taking

into account software latency times, the maximum possible transfer rates are 150 kbytes/s. Typical transfer rates are

around 10 kbytes/s.

3

�

Many file transfer programs overcome the unidirectional limitation of the PC parallel port by using four of the status

lines (SLCT, BUSY, PE, ERROR) to send data to the host four bits at a time. The ACK line can be used to interrupt

the host to indicate that data is ready to be read.

The Bidirectional Port

The IBM PS/2 computer enhanced the standard PC parallel interface by adding bidirectional drivers to the eight data

lines. The I/O connector and signal assignments remained the same. A parallel port with bidirectional drivers is

often referred to as an extended mode parallel port. IBM refers to a bidirectional port as a Type 1 parallel port.

IBM also defines Type 2 and Type 3 parallel ports which use a DMA channel to write/read blocks of data to/from

the parallel port. The parallel port on most computers is configured at the factory to operate as an unidirectional

parallel port. A setup utility specifically for the system must be used to select bidirectional operation.

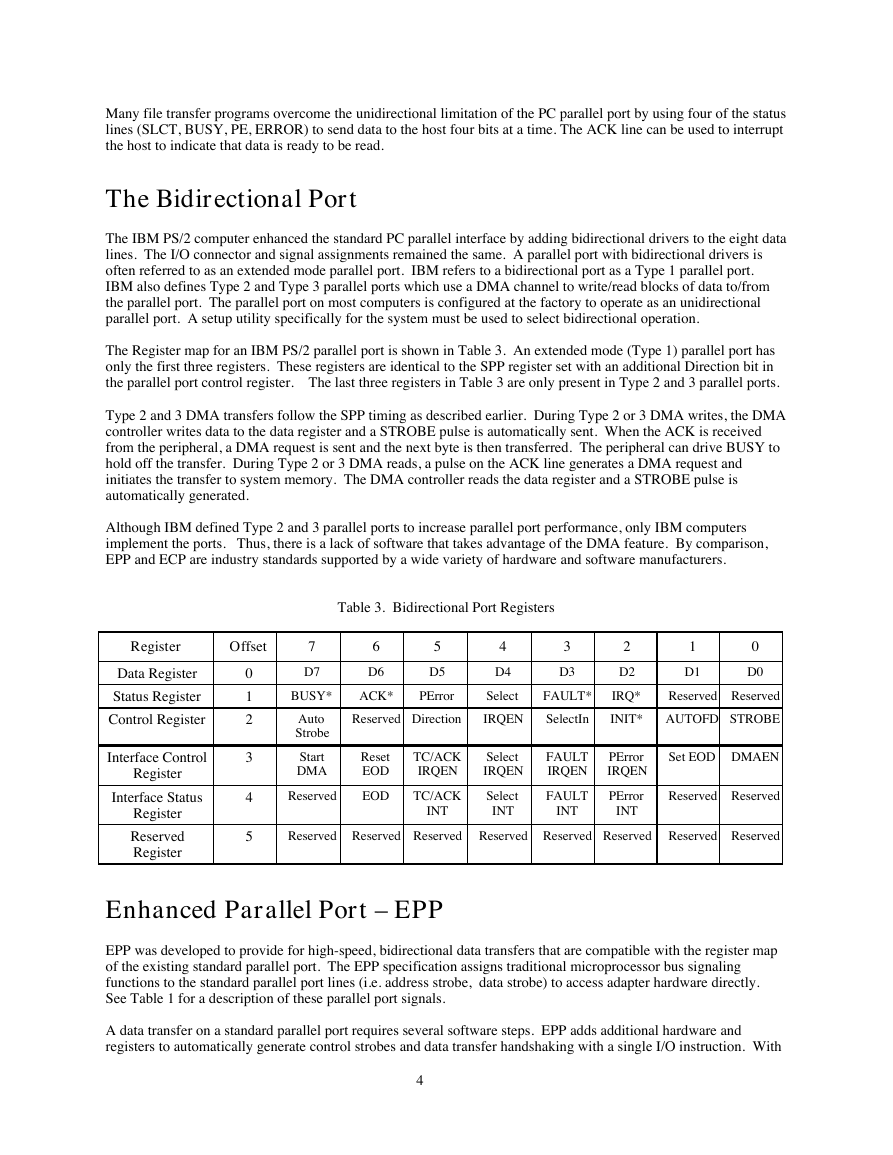

The Register map for an IBM PS/2 parallel port is shown in Table 3. An extended mode (Type 1) parallel port has

only the first three registers. These registers are identical to the SPP register set with an additional Direction bit in

the parallel port control register. The last three registers in Table 3 are only present in Type 2 and 3 parallel ports.

Type 2 and 3 DMA transfers follow the SPP timing as described earlier. During Type 2 or 3 DMA writes, the DMA

controller writes data to the data register and a STROBE pulse is automatically sent. When the ACK is received

from the peripheral, a DMA request is sent and the next byte is then transferred. The peripheral can drive BUSY to

hold off the transfer. During Type 2 or 3 DMA reads, a pulse on the ACK line generates a DMA request and

initiates the transfer to system memory. The DMA controller reads the data register and a STROBE pulse is

automatically generated.

Although IBM defined Type 2 and 3 parallel ports to increase parallel port performance, only IBM computers

implement the ports. Thus, there is a lack of software that takes advantage of the DMA feature. By comparison,

EPP and ECP are industry standards supported by a wide variety of hardware and software manufacturers.

Table 3. Bidirectional Port Registers

Register

Offset

Data Register

Status Register

Control Register

Interface Control

Register

Interface Status

Register

Reserved

Register

0

1

2

3

4

5

7

D7

6

D6

5

D5

4

D4

3

D3

2

D2

1

D1

0

D0

BUSY*

ACK*

PError

Select

FAULT*

IRQ*

Reserved Reserved

Auto

Strobe

Start

DMA

Reserved

Reserved Direction

IRQEN

SelectIn

INIT*

AUTOFD STROBE

Reset

EOD

EOD

TC/ACK

IRQEN

TC/ACK

INT

Select

IRQEN

Select

INT

FAULT

IRQEN

FAULT

INT

PError

IRQEN

PError

INT

Set EOD DMAEN

Reserved Reserved

Reserved Reserved Reserved Reserved Reserved Reserved Reserved Reserved

Enhanced Parallel Port – EPP

EPP was developed to provide for high-speed, bidirectional data transfers that are compatible with the register map

of the existing standard parallel port. The EPP specification assigns traditional microprocessor bus signaling

functions to the standard parallel port lines (i.e. address strobe, data strobe) to access adapter hardware directly.

See Table 1 for a description of these parallel port signals.

A data transfer on a standard parallel port requires several software steps. EPP adds additional hardware and

registers to automatically generate control strobes and data transfer handshaking with a single I/O instruction. With

4

�

an ISA machine, maximum possible transfer rates are 2 Mbytes/s. Transfer rates up to 10 Mbytes/s can be achieved

on other platforms.

EPP operations are typically two-phase bus cycles initiated by the host. The host first selects a register within the

peripheral and performs an address cycle. Then the host performs a series of read and/or writes to that selected

register. EPP defines a single interrupt request signal, INTR, enabling the peripheral with a means to signal the host.

EPP has four basic operations – address write, address read, data write, and data read.

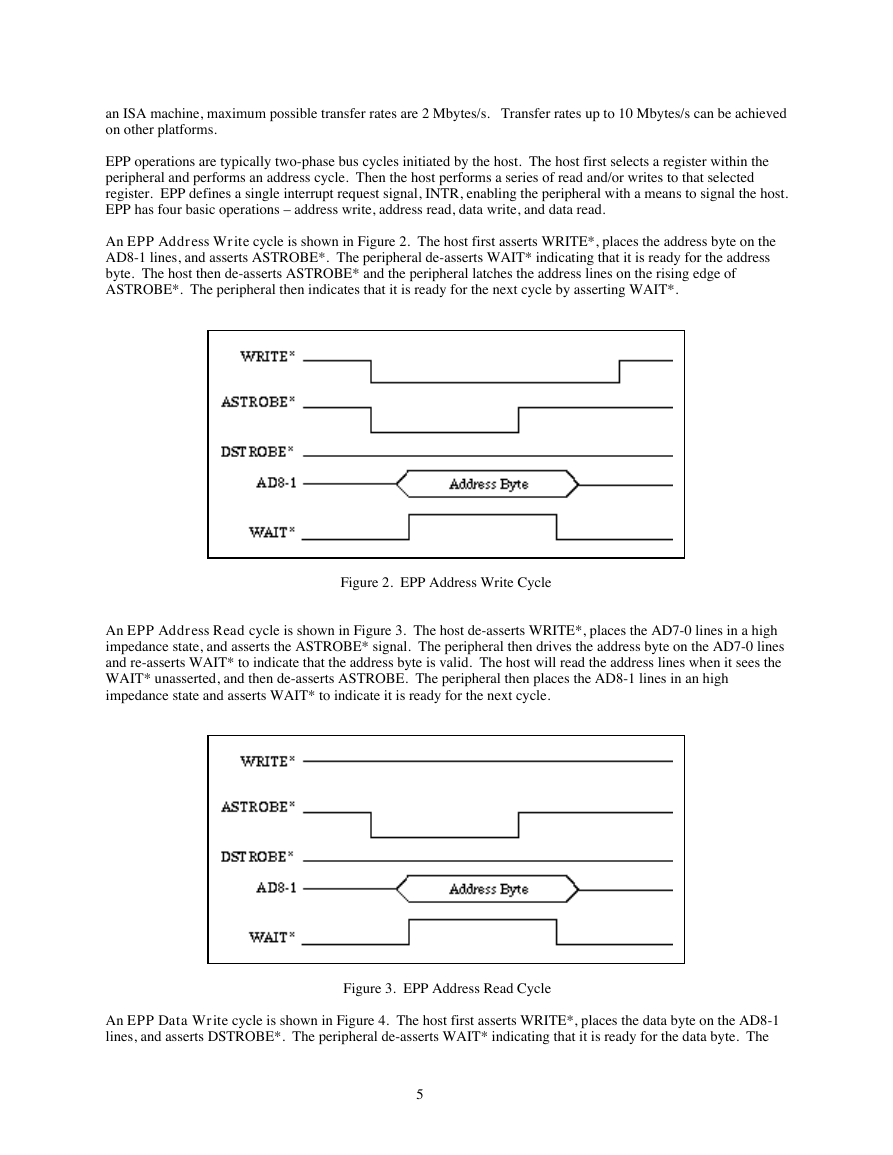

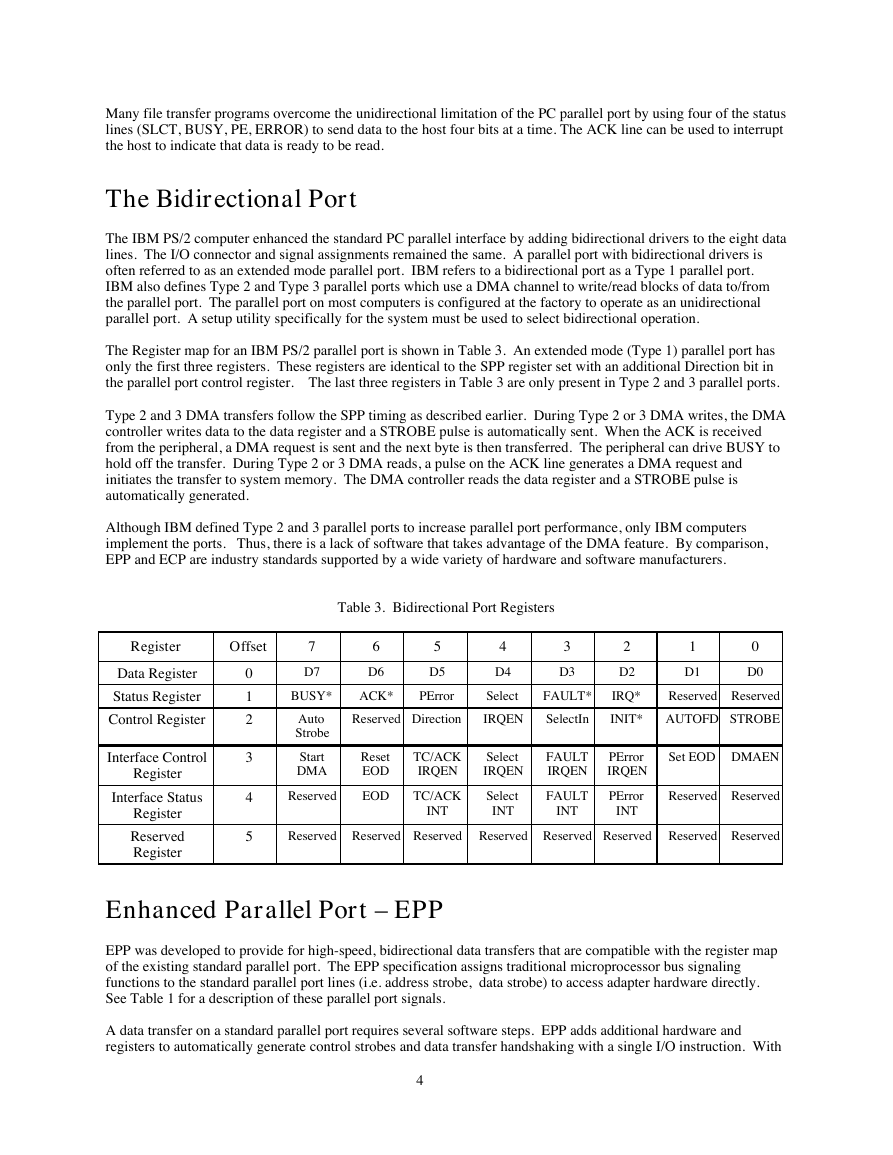

An EPP Address Write cycle is shown in Figure 2. The host first asserts WRITE*, places the address byte on the

AD8-1 lines, and asserts ASTROBE*. The peripheral de-asserts WAIT* indicating that it is ready for the address

byte. The host then de-asserts ASTROBE* and the peripheral latches the address lines on the rising edge of

ASTROBE*. The peripheral then indicates that it is ready for the next cycle by asserting WAIT*.

Figure 2. EPP Address Write Cycle

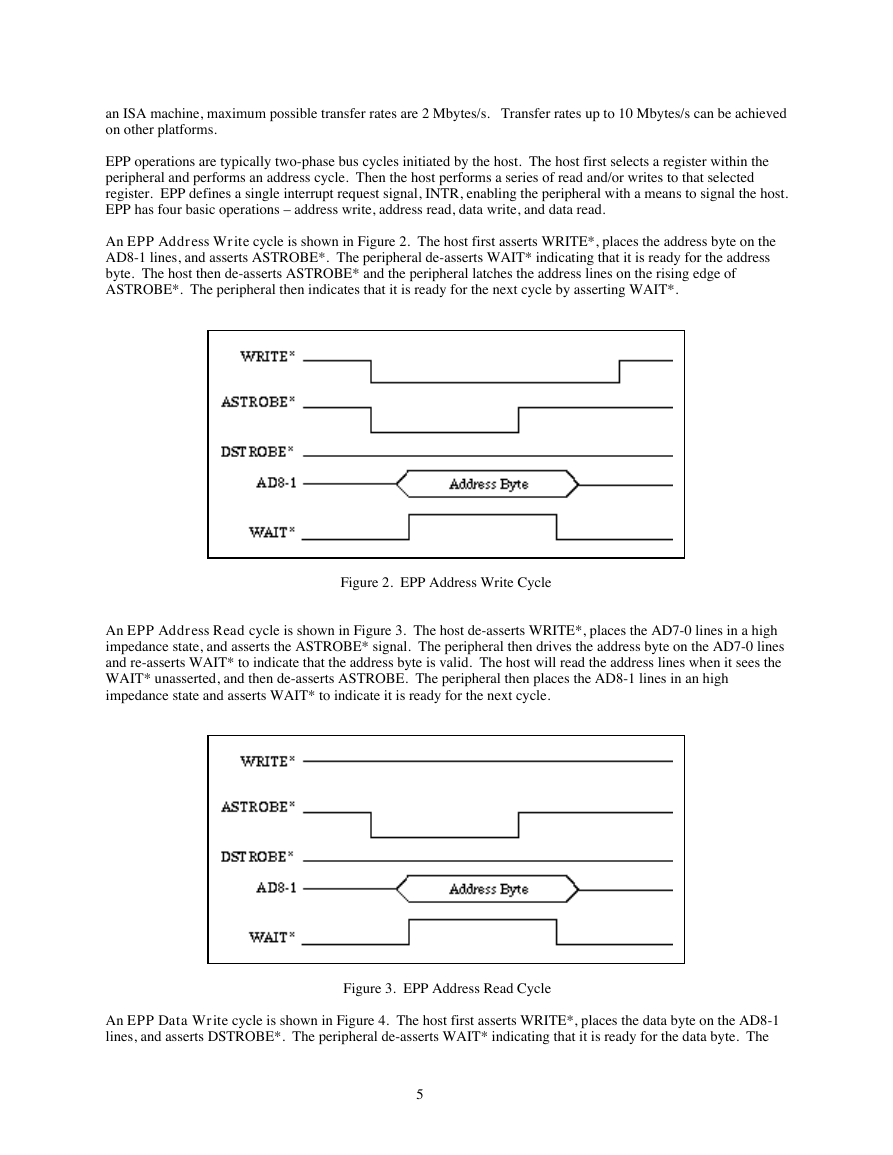

An EPP Address Read cycle is shown in Figure 3. The host de-asserts WRITE*, places the AD7-0 lines in a high

impedance state, and asserts the ASTROBE* signal. The peripheral then drives the address byte on the AD7-0 lines

and re-asserts WAIT* to indicate that the address byte is valid. The host will read the address lines when it sees the

WAIT* unasserted, and then de-asserts ASTROBE. The peripheral then places the AD8-1 lines in an high

impedance state and asserts WAIT* to indicate it is ready for the next cycle.

Figure 3. EPP Address Read Cycle

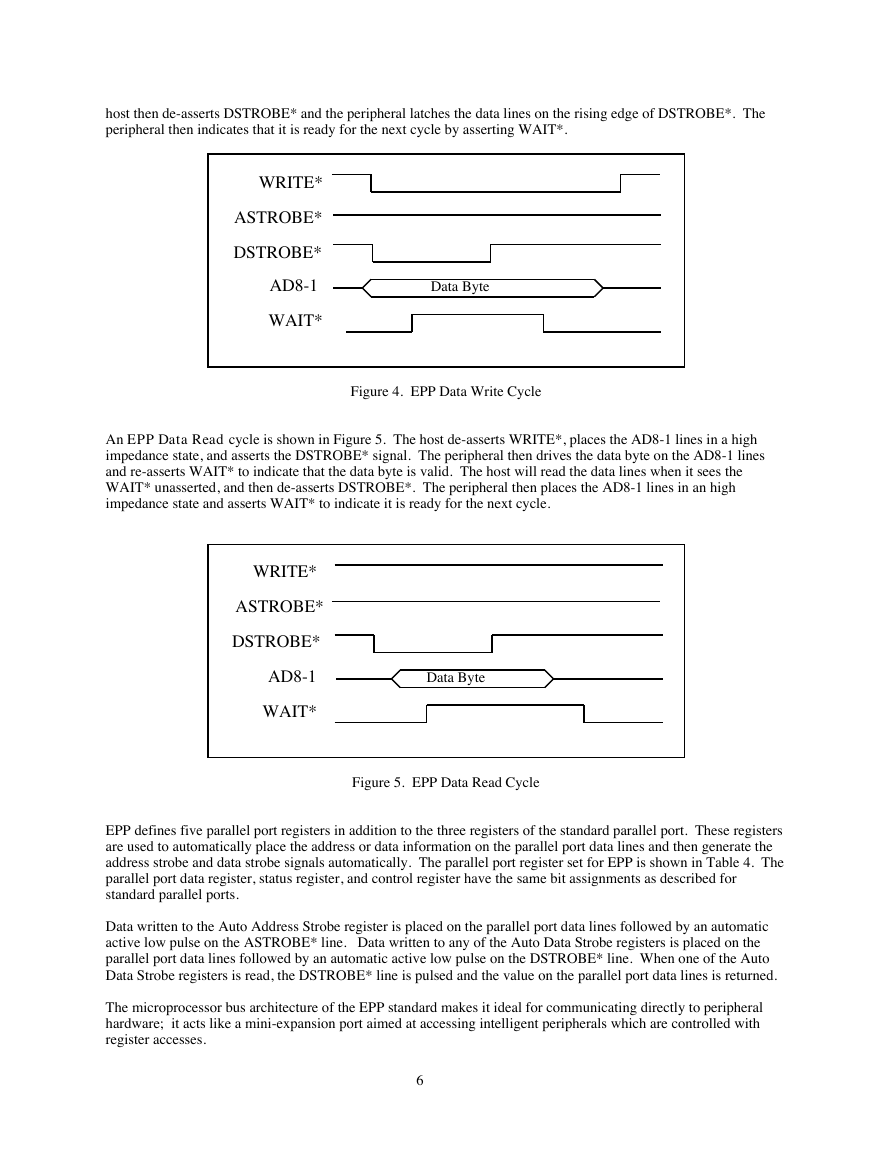

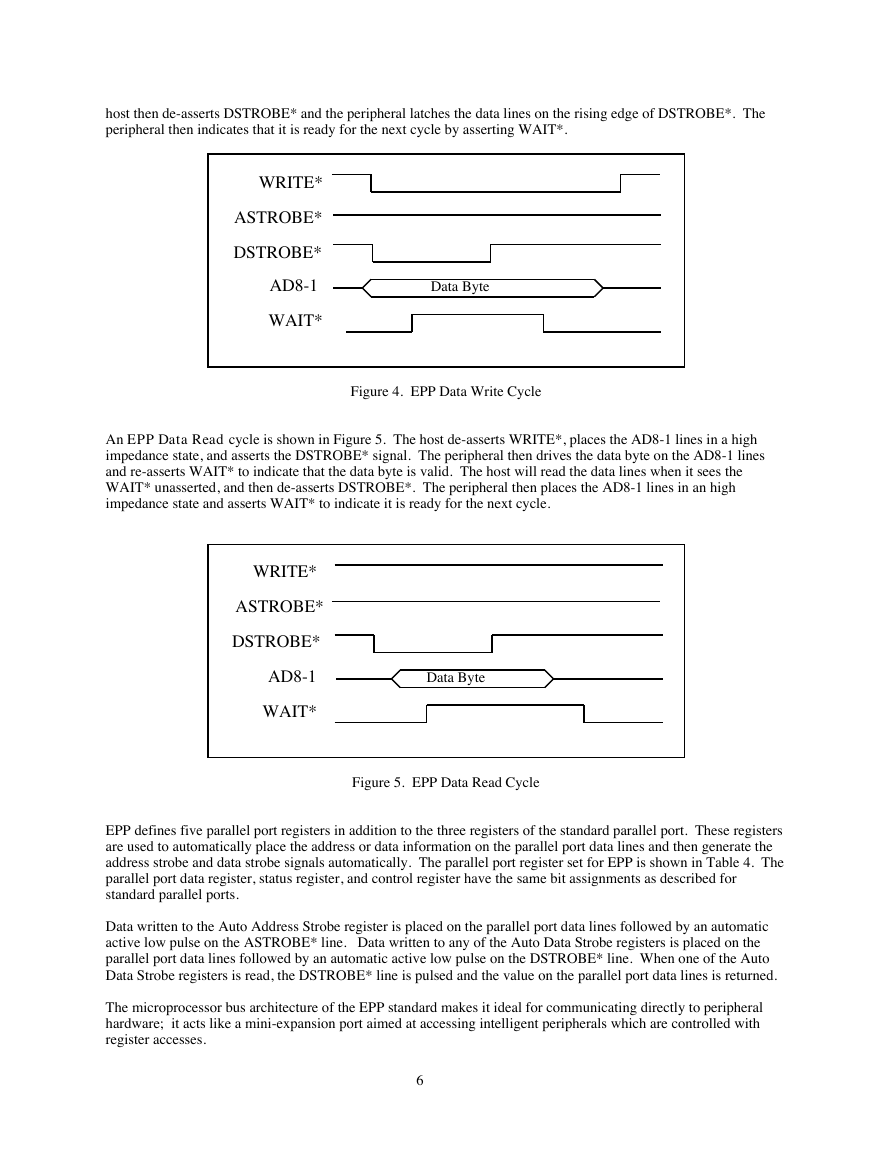

An EPP Data Write cycle is shown in Figure 4. The host first asserts WRITE*, places the data byte on the AD8-1

lines, and asserts DSTROBE*. The peripheral de-asserts WAIT* indicating that it is ready for the data byte. The

5

�

host then de-asserts DSTROBE* and the peripheral latches the data lines on the rising edge of DSTROBE*. The

peripheral then indicates that it is ready for the next cycle by asserting WAIT*.

WRITE*

ASTROBE*

DSTROBE*

AD8-1

WAIT*

Data Byte

Figure 4. EPP Data Write Cycle

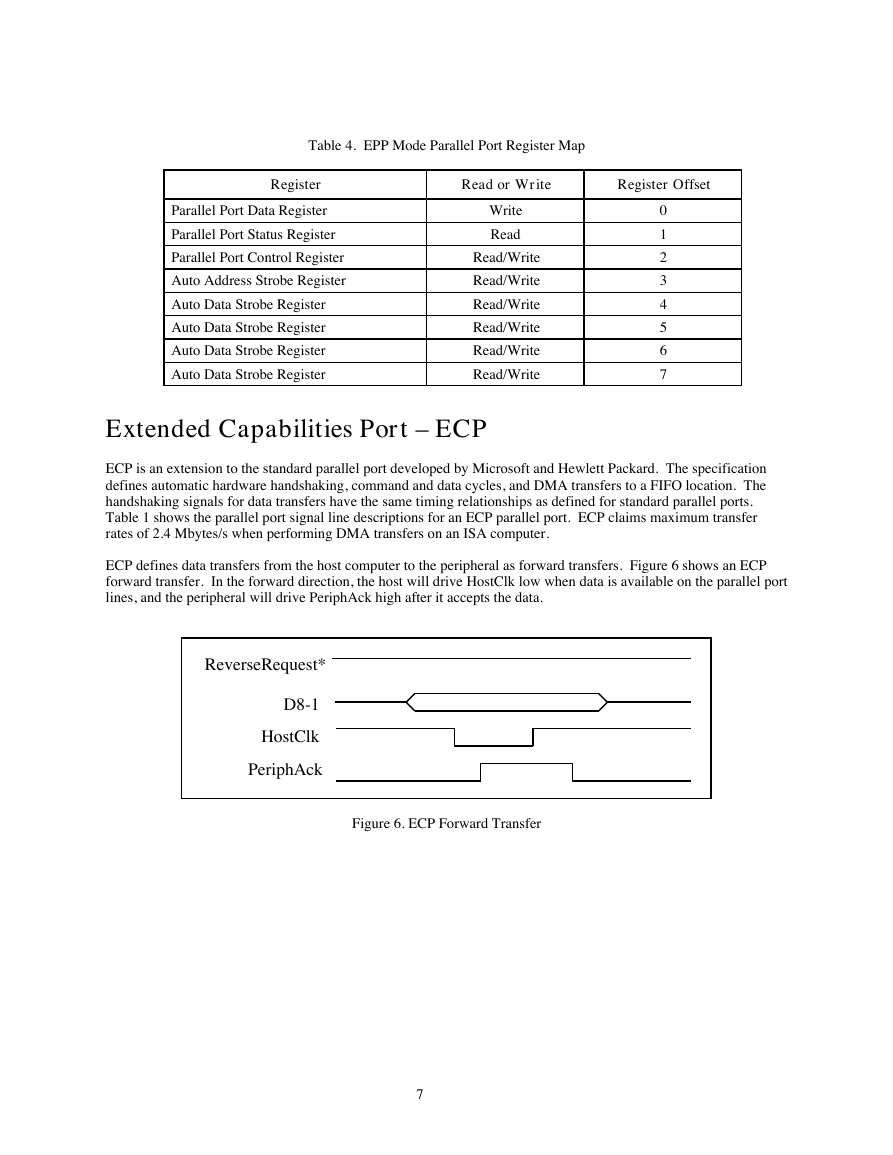

An EPP Data Read cycle is shown in Figure 5. The host de-asserts WRITE*, places the AD8-1 lines in a high

impedance state, and asserts the DSTROBE* signal. The peripheral then drives the data byte on the AD8-1 lines

and re-asserts WAIT* to indicate that the data byte is valid. The host will read the data lines when it sees the

WAIT* unasserted, and then de-asserts DSTROBE*. The peripheral then places the AD8-1 lines in an high

impedance state and asserts WAIT* to indicate it is ready for the next cycle.

WRITE*

ASTROBE*

DSTROBE*

AD8-1

WAIT*

Data Byte

Figure 5. EPP Data Read Cycle

EPP defines five parallel port registers in addition to the three registers of the standard parallel port. These registers

are used to automatically place the address or data information on the parallel port data lines and then generate the

address strobe and data strobe signals automatically. The parallel port register set for EPP is shown in Table 4. The

parallel port data register, status register, and control register have the same bit assignments as described for

standard parallel ports.

Data written to the Auto Address Strobe register is placed on the parallel port data lines followed by an automatic

active low pulse on the ASTROBE* line. Data written to any of the Auto Data Strobe registers is placed on the

parallel port data lines followed by an automatic active low pulse on the DSTROBE* line. When one of the Auto

Data Strobe registers is read, the DSTROBE* line is pulsed and the value on the parallel port data lines is returned.

The microprocessor bus architecture of the EPP standard makes it ideal for communicating directly to peripheral

hardware; it acts like a mini-expansion port aimed at accessing intelligent peripherals which are controlled with

register accesses.

6

�

Table 4. EPP Mode Parallel Port Register Map

Register

Read or Write

Register Offset

Parallel Port Data Register

Parallel Port Status Register

Parallel Port Control Register

Auto Address Strobe Register

Auto Data Strobe Register

Auto Data Strobe Register

Auto Data Strobe Register

Auto Data Strobe Register

Write

Read

Read/Write

Read/Write

Read/Write

Read/Write

Read/Write

Read/Write

0

1

2

3

4

5

6

7

Extended Capabilities Port – ECP

ECP is an extension to the standard parallel port developed by Microsoft and Hewlett Packard. The specification

defines automatic hardware handshaking, command and data cycles, and DMA transfers to a FIFO location. The

handshaking signals for data transfers have the same timing relationships as defined for standard parallel ports.

Table 1 shows the parallel port signal line descriptions for an ECP parallel port. ECP claims maximum transfer

rates of 2.4 Mbytes/s when performing DMA transfers on an ISA computer.

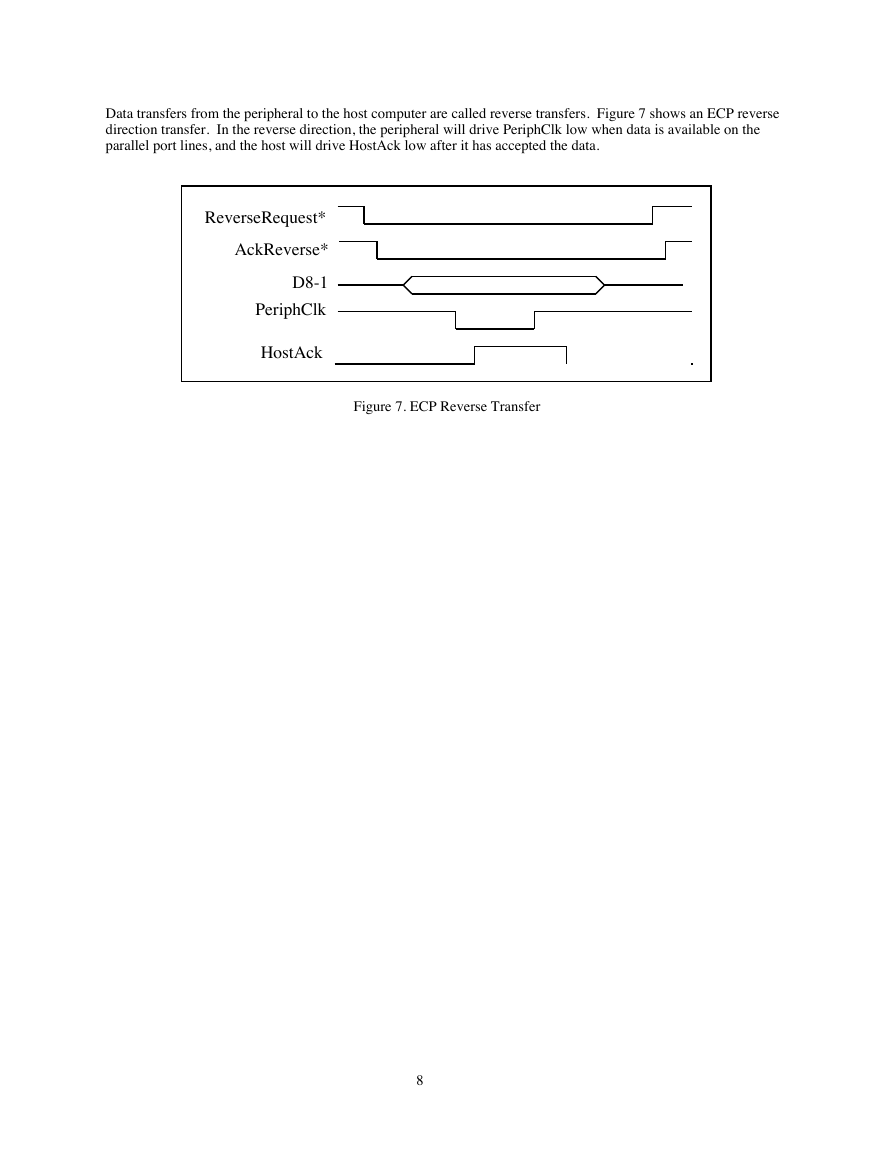

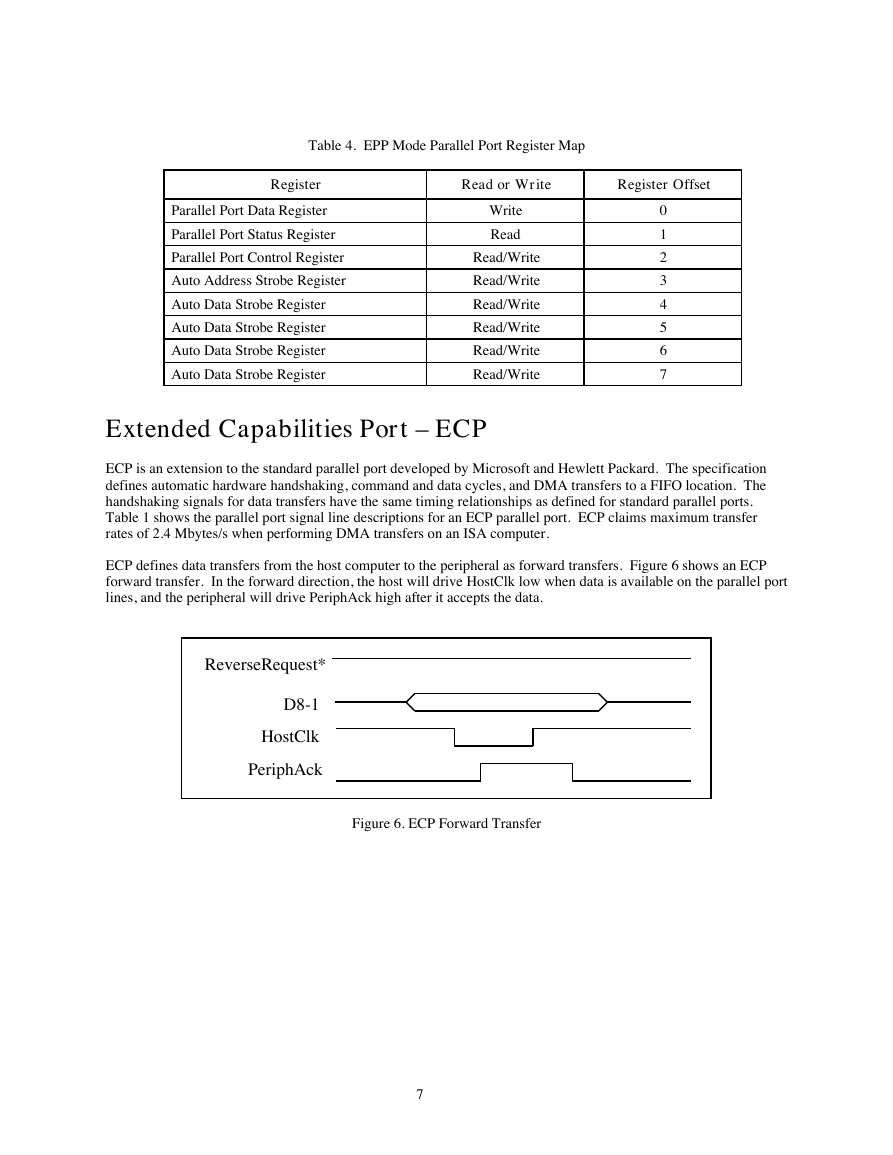

ECP defines data transfers from the host computer to the peripheral as forward transfers. Figure 6 shows an ECP

forward transfer. In the forward direction, the host will drive HostClk low when data is available on the parallel port

lines, and the peripheral will drive PeriphAck high after it accepts the data.

ReverseRequest*

D8-1

HostClk

PeriphAck

Figure 6. ECP Forward Transfer

7

�

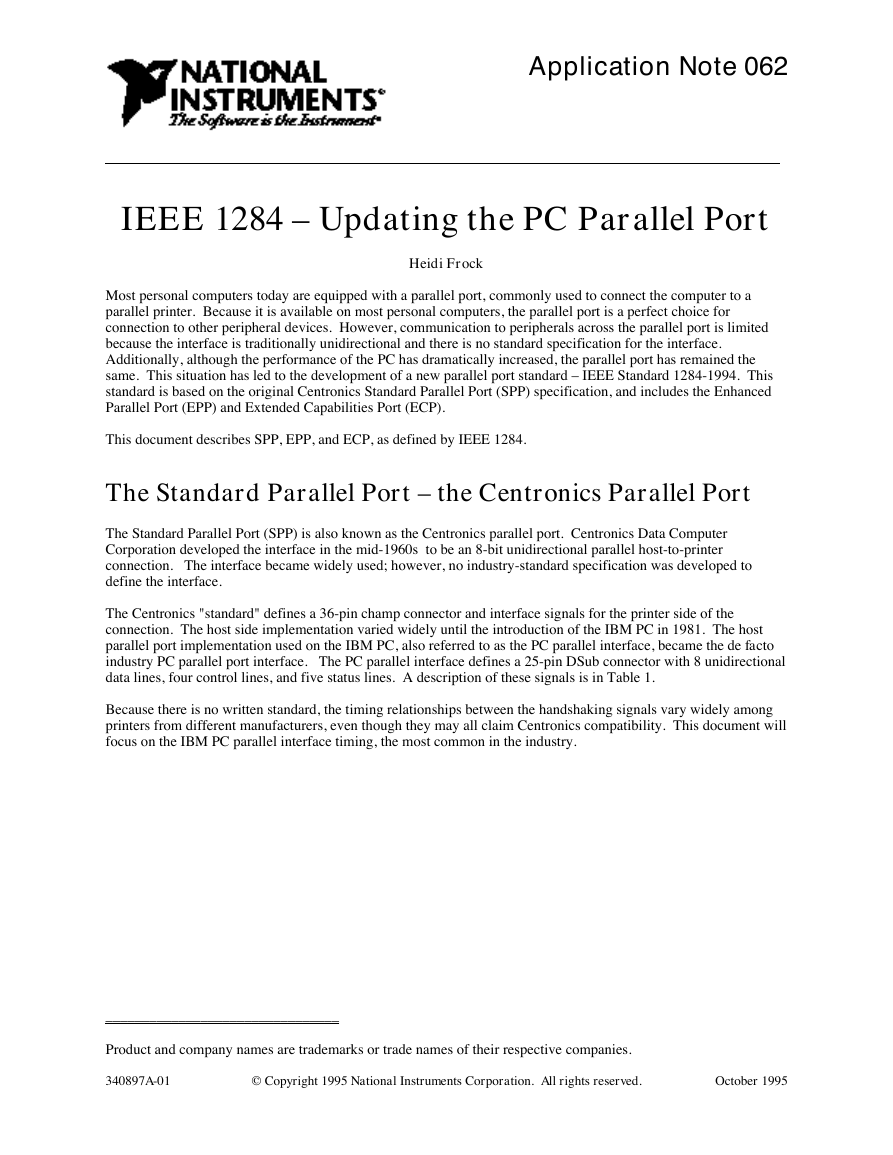

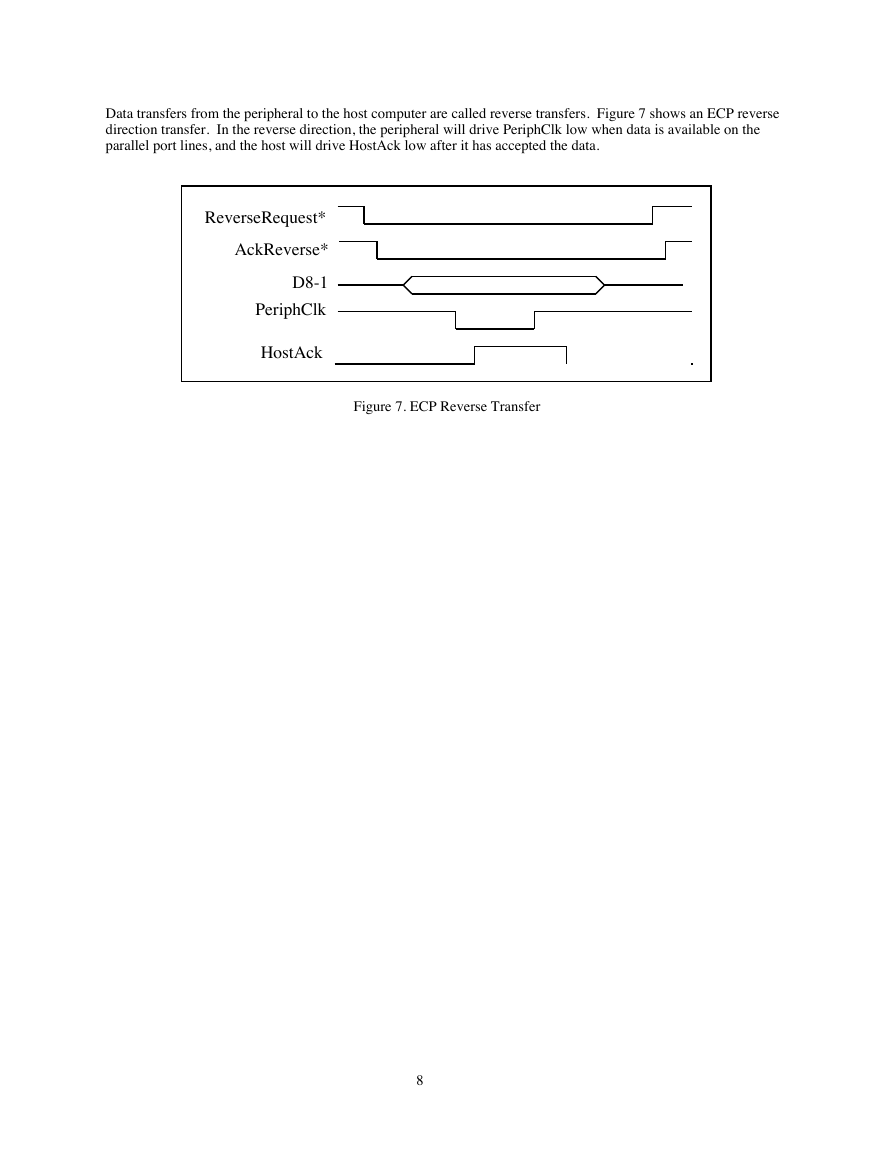

Data transfers from the peripheral to the host computer are called reverse transfers. Figure 7 shows an ECP reverse

direction transfer. In the reverse direction, the peripheral will drive PeriphClk low when data is available on the

parallel port lines, and the host will drive HostAck low after it has accepted the data.

ReverseRequest*

AckReverse*

D8-1

PeriphClk

HostAck

Figure 7. ECP Reverse Transfer

8

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc