视频缩放在FPGA中的应用和实现

视频缩放在

中的应用和实现

针对某显示系统中监控视频控制器的实际需求,设计了一种可实现四路视频信号实时缩放的电路架构。通过权

衡几种常用图像缩放算法的显示质量和硬件可行性,选择用双线性插值算法实现视频的缩放,并在FPGA平台上

以双口RAM资源构建的线缓存作为算法硬件实现,该算法主要由视频数据缓冲模块、插值系数产生模块以及整

体控制模块构成。本设计在满足视频缩放质量要求的基础上,避免了采用过于复杂算法而消耗过多的FPGA资

源,有效地解决了视频缩放时原始图像信息量丢失导致图像失真的问题。结果表明,该设计能够实现任意比例

的视频缩放,实时性高,应用灵活,缩放后显示效果良好,能够满足实际工程的要求。

0 引言引言

随着数字多媒体技术的不断发展,数字图像处理技术广泛应用于空间探测、生物医学、监控系统以及工业检测等许多领域

中。数字视频处理则是基于对视频中每帧图像的处理来实现的。数字视频图像的缩放是视频处理中的一个重要组成部分。

目前[1]。本设计是在

1 缩放算法的硬件可行性

缩放算法的硬件可行性

1.1 缩放算法的选取

缩放算法的选取

目前,图像缩放算法大致可以分为两大类[2],一类是基于边缘的图像缩放算法,它利用了图像的边缘信息,能够很好地还原

原始图像,但该算法计算复杂,运算速度慢,硬件上难以实现;另一类是基于插值的图像缩放算法,它的算法实现相对简单,

但缩放后可能会产生细节丢失、轮廓模糊等现象。其中,不同的插值算法有不同的精度,插值算法的好坏也直接影响着图像的

失真程度。最常用的插值算法有3种:最近邻插值、双线性插值、立方卷积插值,使用立方卷积插值达到的效果是最佳的。考

虑到最终算法需要在FPGA上完成,算法的复杂度直接影响FPGA内部的逻辑资源和存储块的消耗量,以及处理每个实时像素

值所消耗的时钟周期,本设计选用双线性插值来完成视频图像的缩放。

1.2 双线性插值算法的原理

双线性插值算法的原理

双线性插值,又称为双线性内插。在数学上,双线性插值是由两个变量插值函数的线性插值扩展,利用了需要处理的原始

图像像素点周围4个像素点的相关性,通过双线性算法计算而得出[3]。

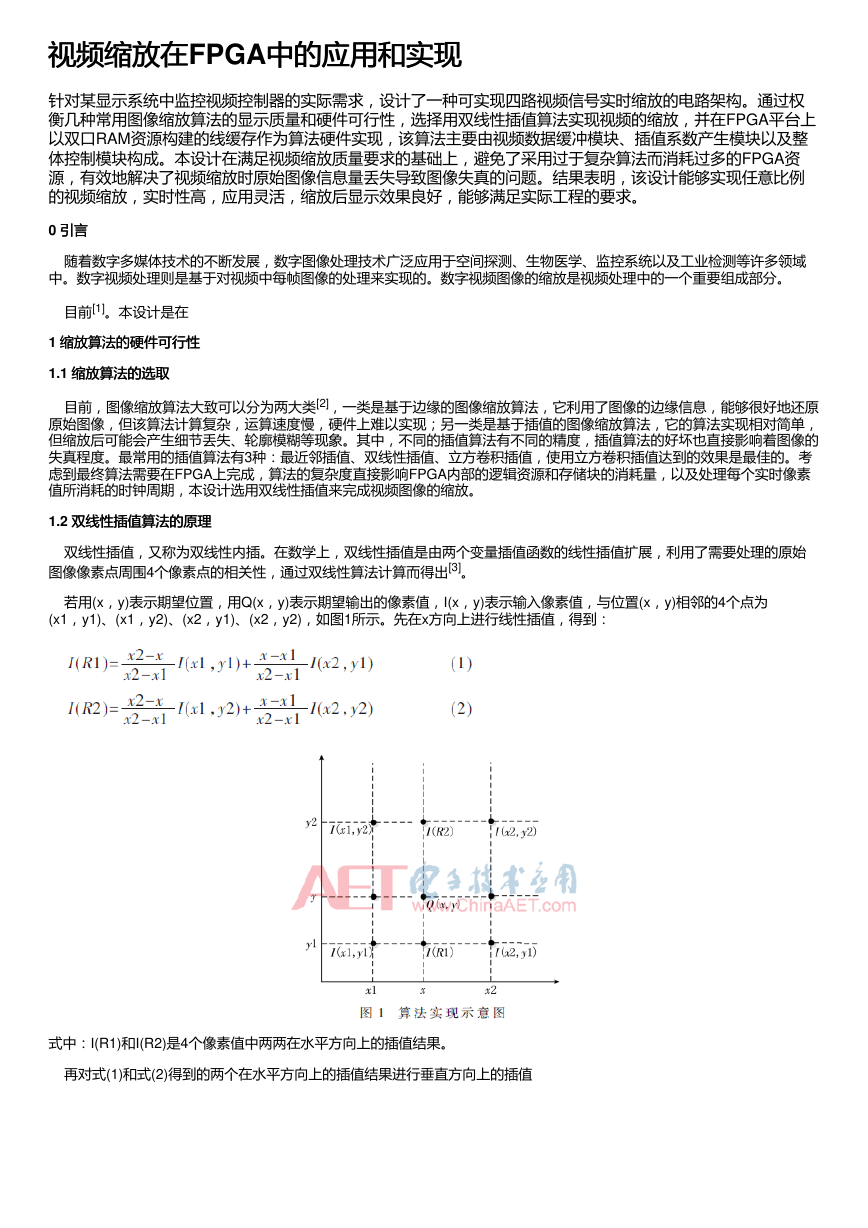

若用(x,y)表示期望位置,用Q(x,y)表示期望输出的像素值,I(x,y)表示输入像素值,与位置(x,y)相邻的4个点为

(x1,y1)、(x1,y2)、(x2,y1)、(x2,y2),如图1所示。先在x方向上进行线性插值,得到:

式中:I(R1)和I(R2)是4个像素值中两两在水平方向上的插值结果。

再对式(1)和式(2)得到的两个在水平方向上的插值结果进行垂直方向上的插值

�

这样Q(x,y)就是期望位置所要的像素值,双线性插值法计算量大,但缩放后的图像质量高,由于双线性插值具有低通滤波

器的性质,使高频信号受损,可能会使图像在轮廓上有一定的模糊。

考虑到FPGA内部丰富的存储块,设计将视频数据以行为单位交替写入两个由双口RAM构成的线缓存中,通过缩放比例合

理控制读写地址,先进行相邻4个像素的垂直线性插值,然后对得到的两个结果进行水平方向插值。

2 FPGA实现实现

2.1 功能模块的划分

功能模块的划分

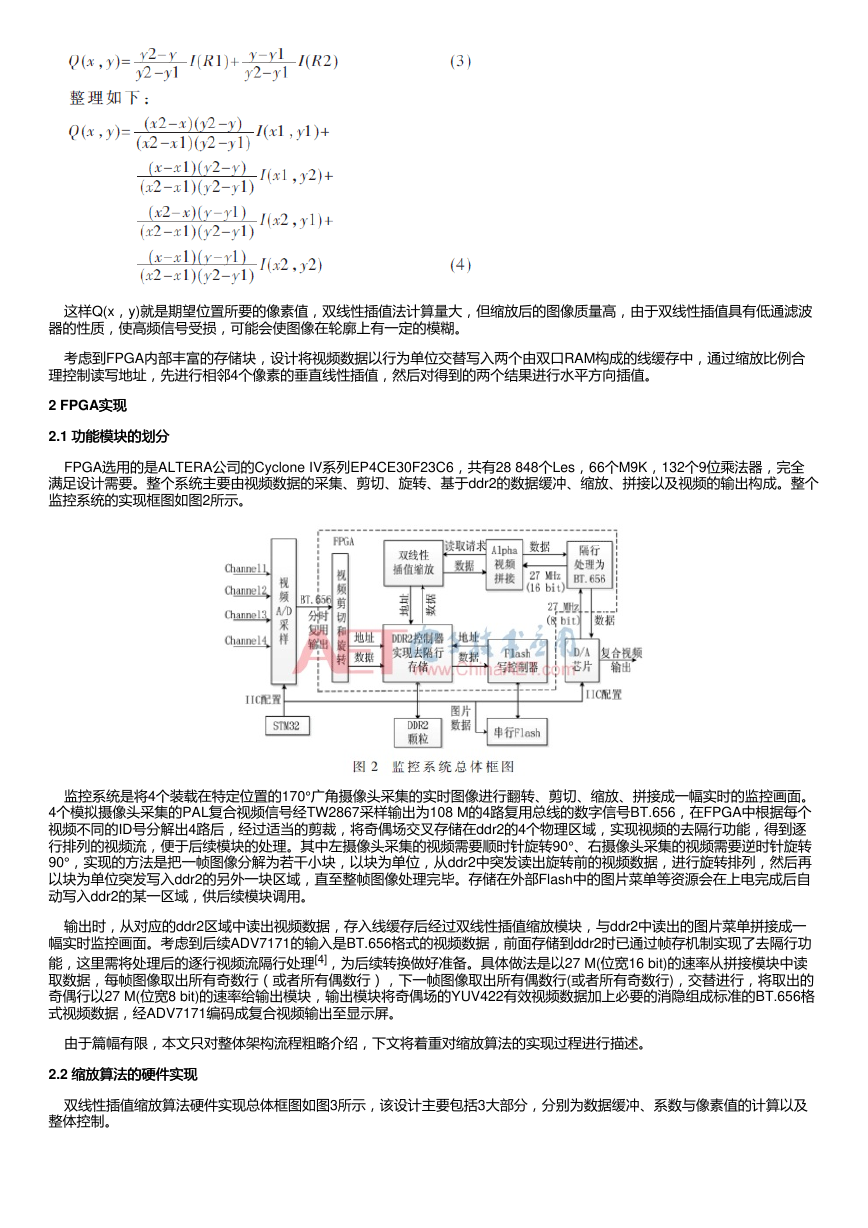

FPGA选用的是ALTERA公司的Cyclone IV系列EP4CE30F23C6,共有28 848个Les,66个M9K,132个9位乘法器,完全

满足设计需要。整个系统主要由视频数据的采集、剪切、旋转、基于ddr2的数据缓冲、缩放、拼接以及视频的输出构成。整个

监控系统的实现框图如图2所示。

监控系统是将4个装载在特定位置的170°广角摄像头采集的实时图像进行翻转、剪切、缩放、拼接成一幅实时的监控画面。

4个模拟摄像头采集的PAL复合视频信号经TW2867采样输出为108 M的4路复用总线的数字信号BT.656,在FPGA中根据每个

视频不同的ID号分解出4路后,经过适当的剪裁,将奇偶场交叉存储在ddr2的4个物理区域,实现视频的去隔行功能,得到逐

行排列的视频流,便于后续模块的处理。其中左摄像头采集的视频需要顺时针旋转90°、右摄像头采集的视频需要逆时针旋转

90°,实现的方法是把一帧图像分解为若干小块,以块为单位,从ddr2中突发读出旋转前的视频数据,进行旋转排列,然后再

以块为单位突发写入ddr2的另外一块区域,直至整帧图像处理完毕。存储在外部Flash中的图片菜单等资源会在上电完成后自

动写入ddr2的某一区域,供后续模块调用。

输出时,从对应的ddr2区域中读出视频数据,存入线缓存后经过双线性插值缩放模块,与ddr2中读出的图片菜单拼接成一

幅实时监控画面。考虑到后续ADV7171的输入是BT.656格式的视频数据,前面存储到ddr2时已通过帧存机制实现了去隔行功

能,这里需将处理后的逐行视频流隔行处理[4],为后续转换做好准备。具体做法是以27 M(位宽16 bit)的速率从拼接模块中读

取数据,每帧图像取出所有奇数行(或者所有偶数行),下一帧图像取出所有偶数行(或者所有奇数行),交替进行,将取出的

奇偶行以27 M(位宽8 bit)的速率给输出模块,输出模块将奇偶场的YUV422有效视频数据加上必要的消隐组成标准的BT.656格

式视频数据,经ADV7171编码成复合视频输出至显示屏。

由于篇幅有限,本文只对整体架构流程粗略介绍,下文将着重对缩放算法的实现过程进行描述。

2.2 缩放算法的硬件实现

缩放算法的硬件实现

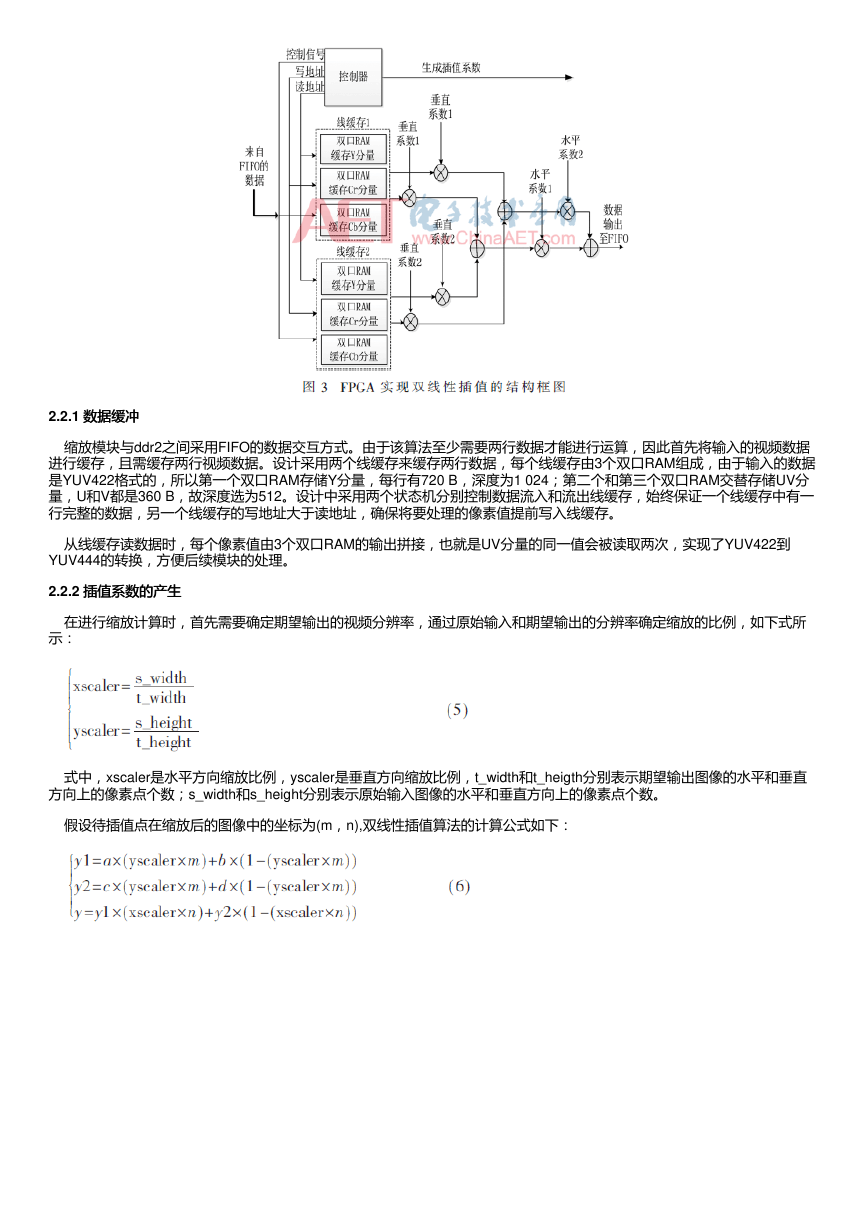

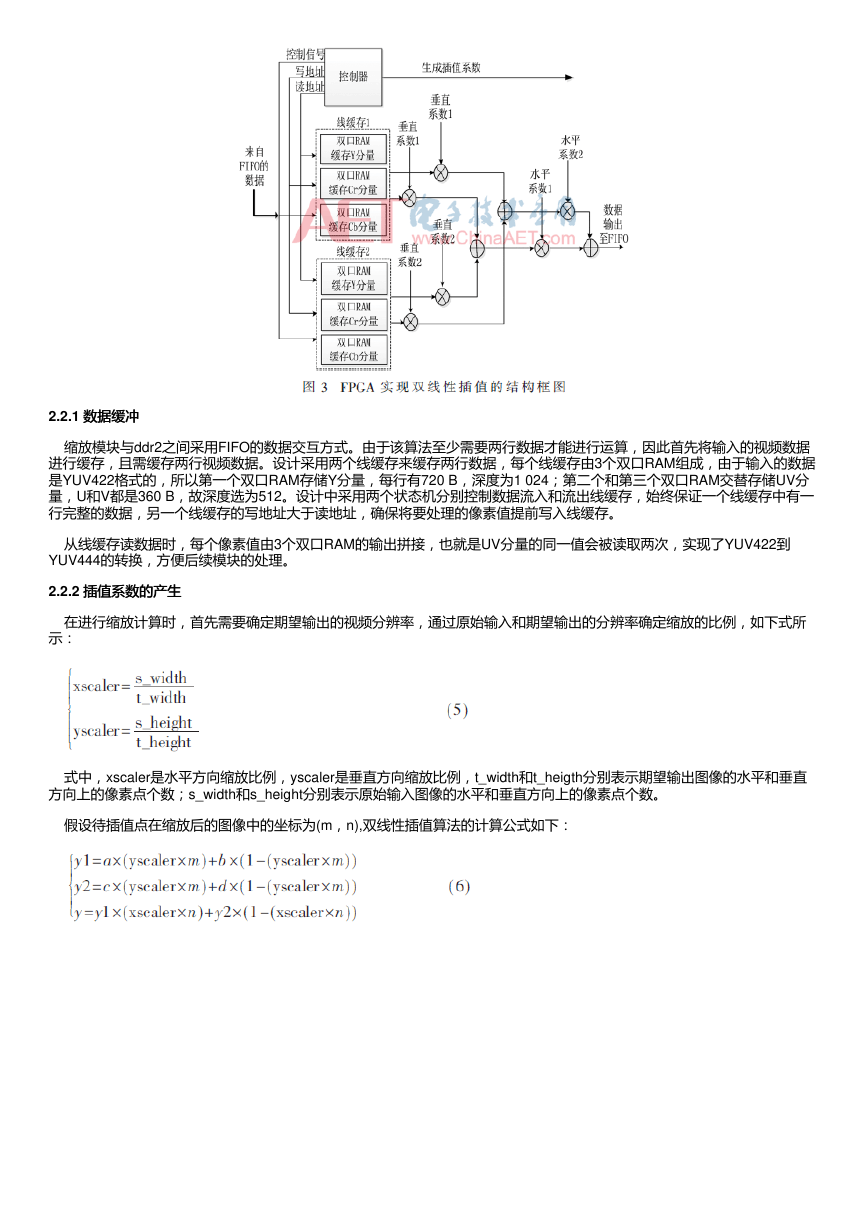

双线性插值缩放算法硬件实现总体框图如图3所示,该设计主要包括3大部分,分别为数据缓冲、系数与像素值的计算以及

整体控制。

�

2.2.1 数据缓冲

数据缓冲

缩放模块与ddr2之间采用FIFO的数据交互方式。由于该算法至少需要两行数据才能进行运算,因此首先将输入的视频数据

进行缓存,且需缓存两行视频数据。设计采用两个线缓存来缓存两行数据,每个线缓存由3个双口RAM组成,由于输入的数据

是YUV422格式的,所以第一个双口RAM存储Y分量,每行有720 B,深度为1 024;第二个和第三个双口RAM交替存储UV分

量,U和V都是360 B,故深度选为512。设计中采用两个状态机分别控制数据流入和流出线缓存,始终保证一个线缓存中有一

行完整的数据,另一个线缓存的写地址大于读地址,确保将要处理的像素值提前写入线缓存。

从线缓存读数据时,每个像素值由3个双口RAM的输出拼接,也就是UV分量的同一值会被读取两次,实现了YUV422到

YUV444的转换,方便后续模块的处理。

2.2.2 插值系数的产生

插值系数的产生

在进行缩放计算时,首先需要确定期望输出的视频分辨率,通过原始输入和期望输出的分辨率确定缩放的比例,如下式所

示:

式中,xscaler是水平方向缩放比例,yscaler是垂直方向缩放比例,t_width和t_heigth分别表示期望输出图像的水平和垂直

方向上的像素点个数;s_width和s_height分别表示原始输入图像的水平和垂直方向上的像素点个数。

假设待插值点在缩放后的图像中的坐标为(m,n),双线性插值算法的计算公式如下:

�

FPGA无法处理浮点数,故在代码中需将水平和垂直缩放比例乘以256倍,最终得到的y需要向右移位8位,即为插值的期望像

素值。

式中,a、b、c、d分别相邻4个像素点(左上、右上、左下、右下)的像素值。由于

2.2.3 整体控制

整体控制

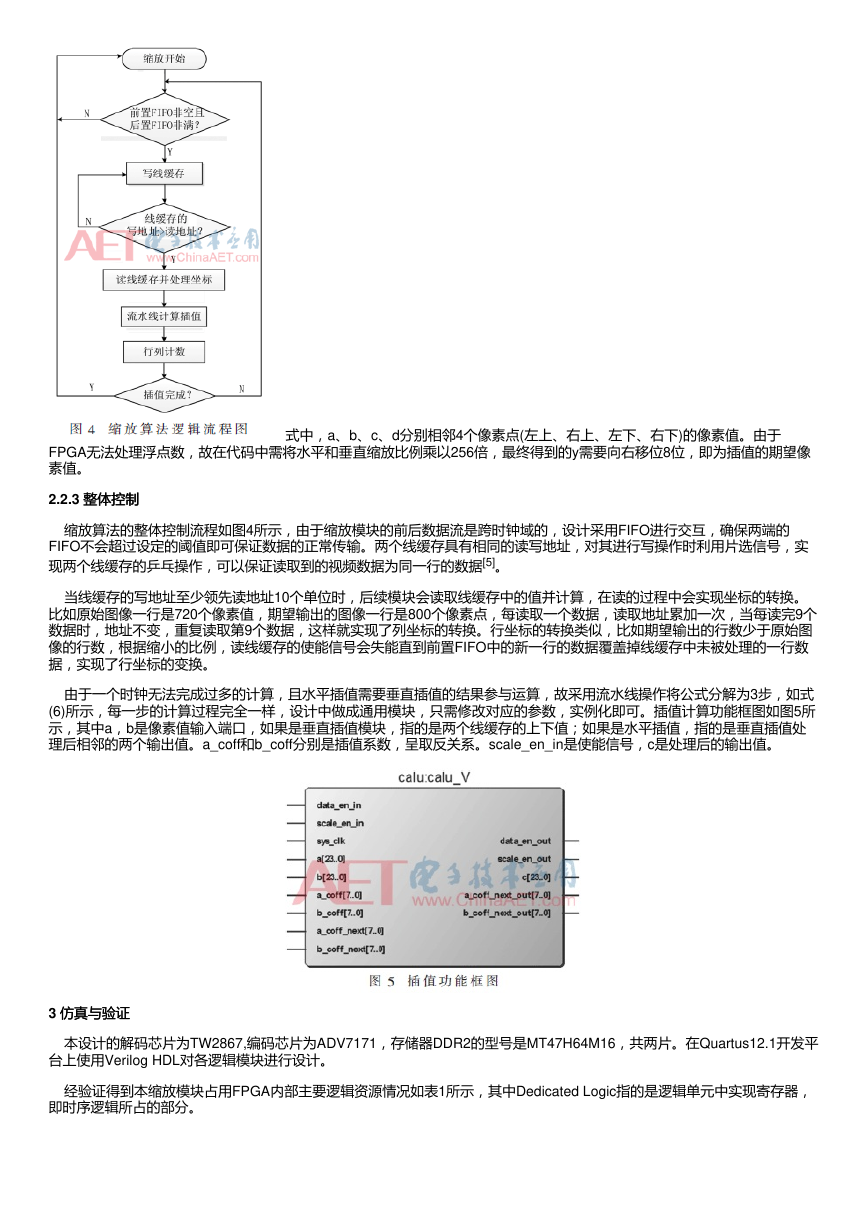

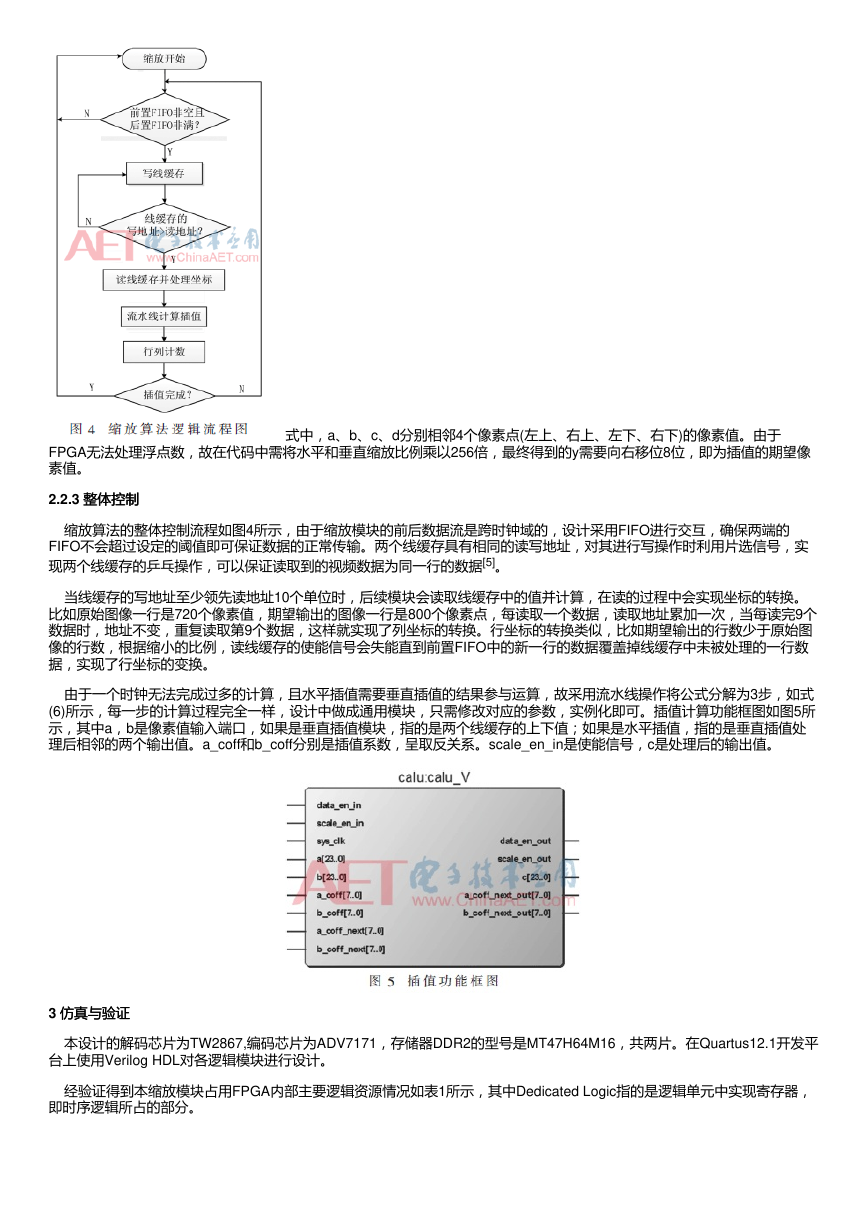

缩放算法的整体控制流程如图4所示,由于缩放模块的前后数据流是跨时钟域的,设计采用FIFO进行交互,确保两端的

FIFO不会超过设定的阈值即可保证数据的正常传输。两个线缓存具有相同的读写地址,对其进行写操作时利用片选信号,实

现两个线缓存的乒乓操作,可以保证读取到的视频数据为同一行的数据[5]。

当线缓存的写地址至少领先读地址10个单位时,后续模块会读取线缓存中的值并计算,在读的过程中会实现坐标的转换。

比如原始图像一行是720个像素值,期望输出的图像一行是800个像素点,每读取一个数据,读取地址累加一次,当每读完9个

数据时,地址不变,重复读取第9个数据,这样就实现了列坐标的转换。行坐标的转换类似,比如期望输出的行数少于原始图

像的行数,根据缩小的比例,读线缓存的使能信号会失能直到前置FIFO中的新一行的数据覆盖掉线缓存中未被处理的一行数

据,实现了行坐标的变换。

由于一个时钟无法完成过多的计算,且水平插值需要垂直插值的结果参与运算,故采用流水线操作将公式分解为3步,如式

(6)所示,每一步的计算过程完全一样,设计中做成通用模块,只需修改对应的参数,实例化即可。插值计算功能框图如图5所

示,其中a,b是像素值输入端口,如果是垂直插值模块,指的是两个线缓存的上下值;如果是水平插值,指的是垂直插值处

理后相邻的两个输出值。a_coff和b_coff分别是插值系数,呈取反关系。scale_en_in是使能信号,c是处理后的输出值。

3 仿真与验证

仿真与验证

本设计的解码芯片为TW2867,编码芯片为ADV7171,存储器DDR2的型号是MT47H64M16,共两片。在Quartus12.1开发平

台上使用Verilog HDL对各逻辑模块进行设计。

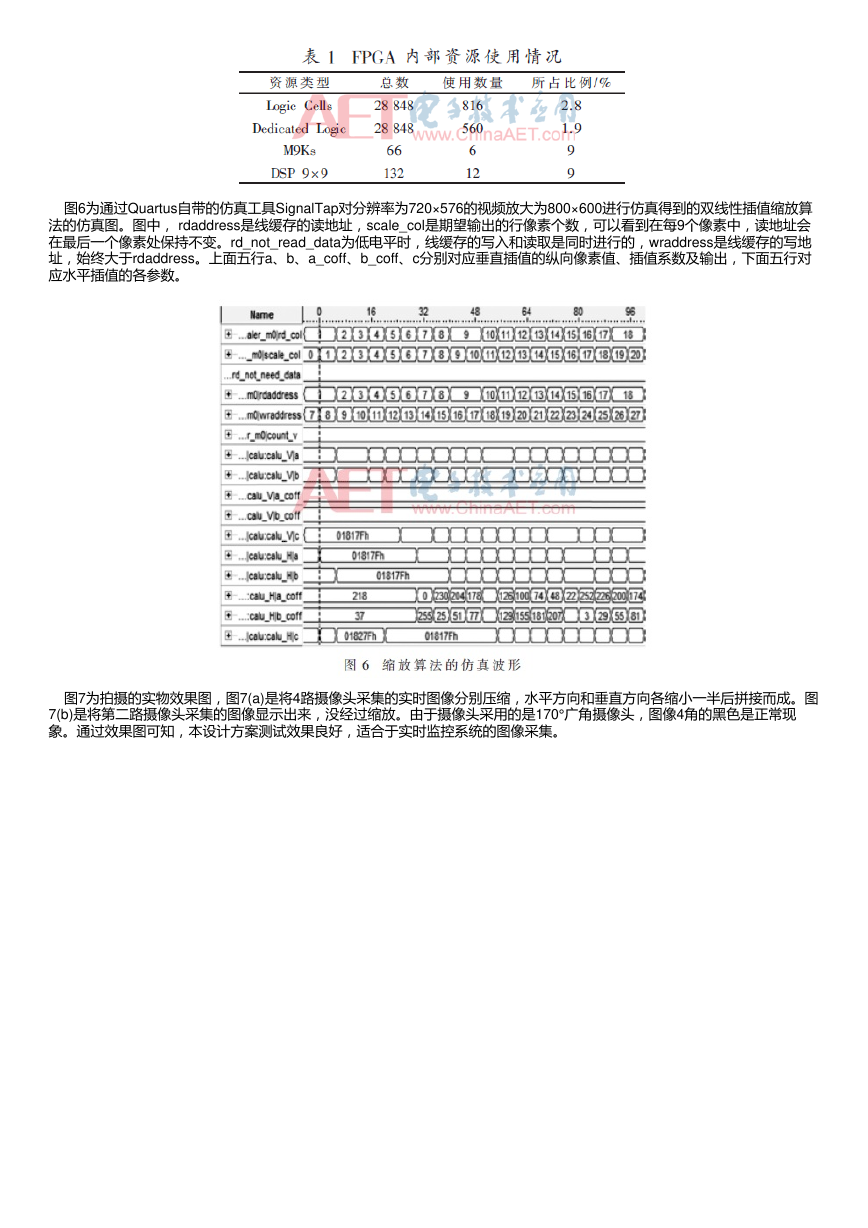

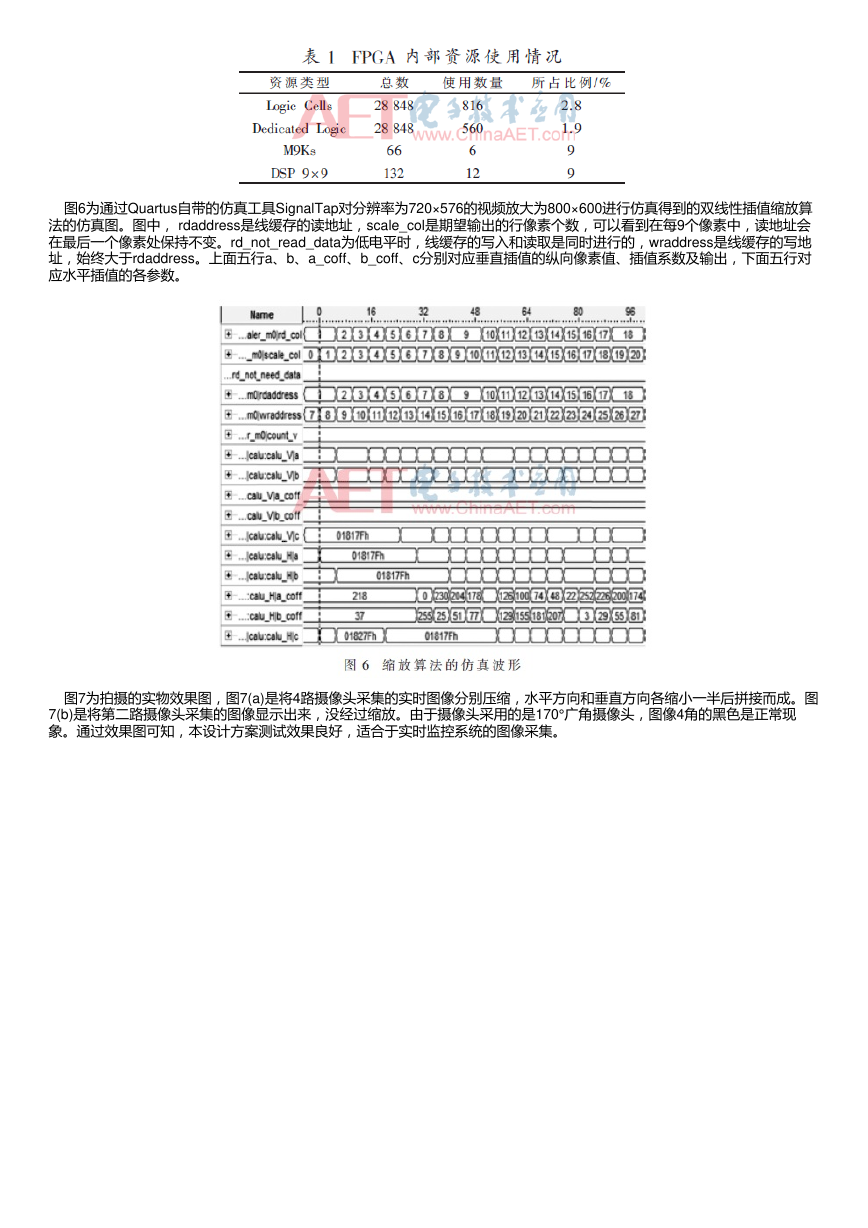

经验证得到本缩放模块占用FPGA内部主要逻辑资源情况如表1所示,其中Dedicated Logic指的是逻辑单元中实现寄存器,

即时序逻辑所占的部分。

�

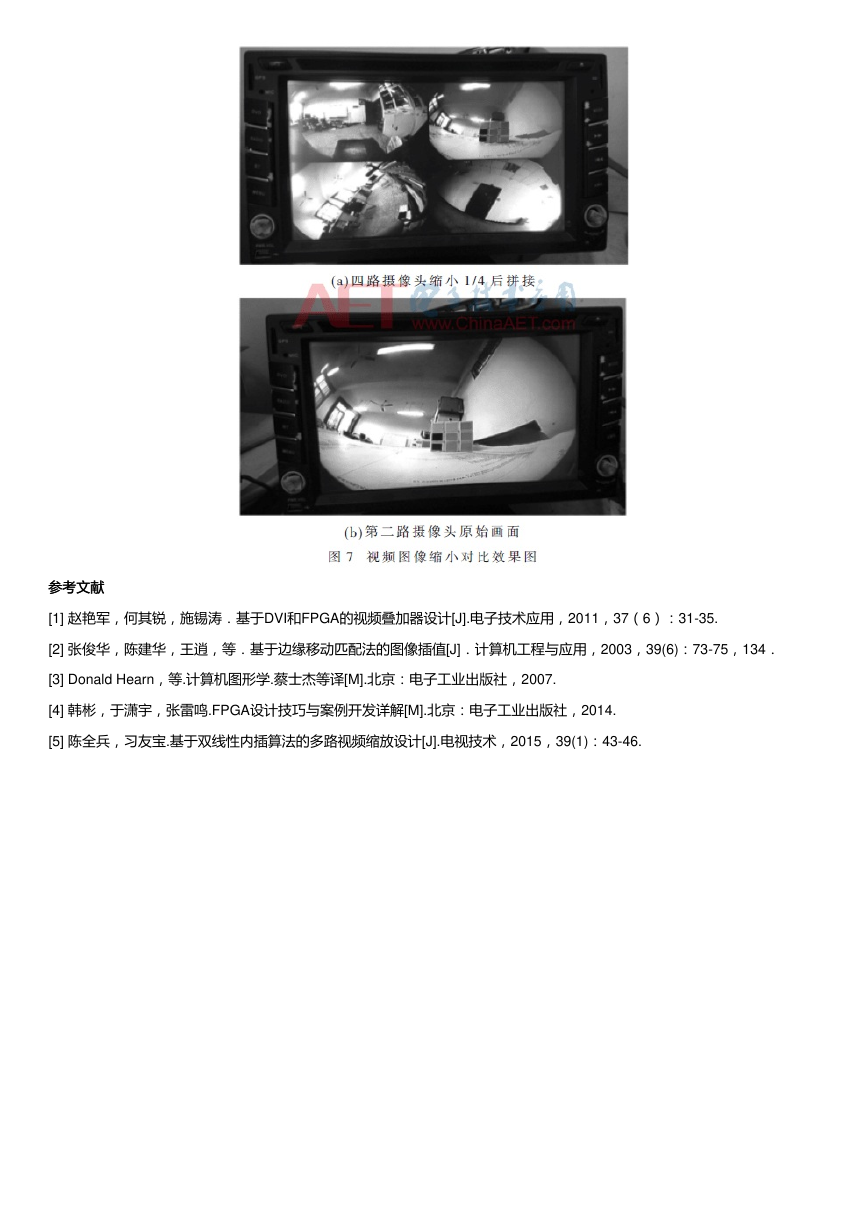

图6为通过Quartus自带的仿真工具SignalTap对分辨率为720×576的视频放大为800×600进行仿真得到的双线性插值缩放算

法的仿真图。图中, rdaddress是线缓存的读地址,scale_col是期望输出的行像素个数,可以看到在每9个像素中,读地址会

在最后一个像素处保持不变。rd_not_read_data为低电平时,线缓存的写入和读取是同时进行的,wraddress是线缓存的写地

址,始终大于rdaddress。上面五行a、b、a_coff、b_coff、c分别对应垂直插值的纵向像素值、插值系数及输出,下面五行对

应水平插值的各参数。

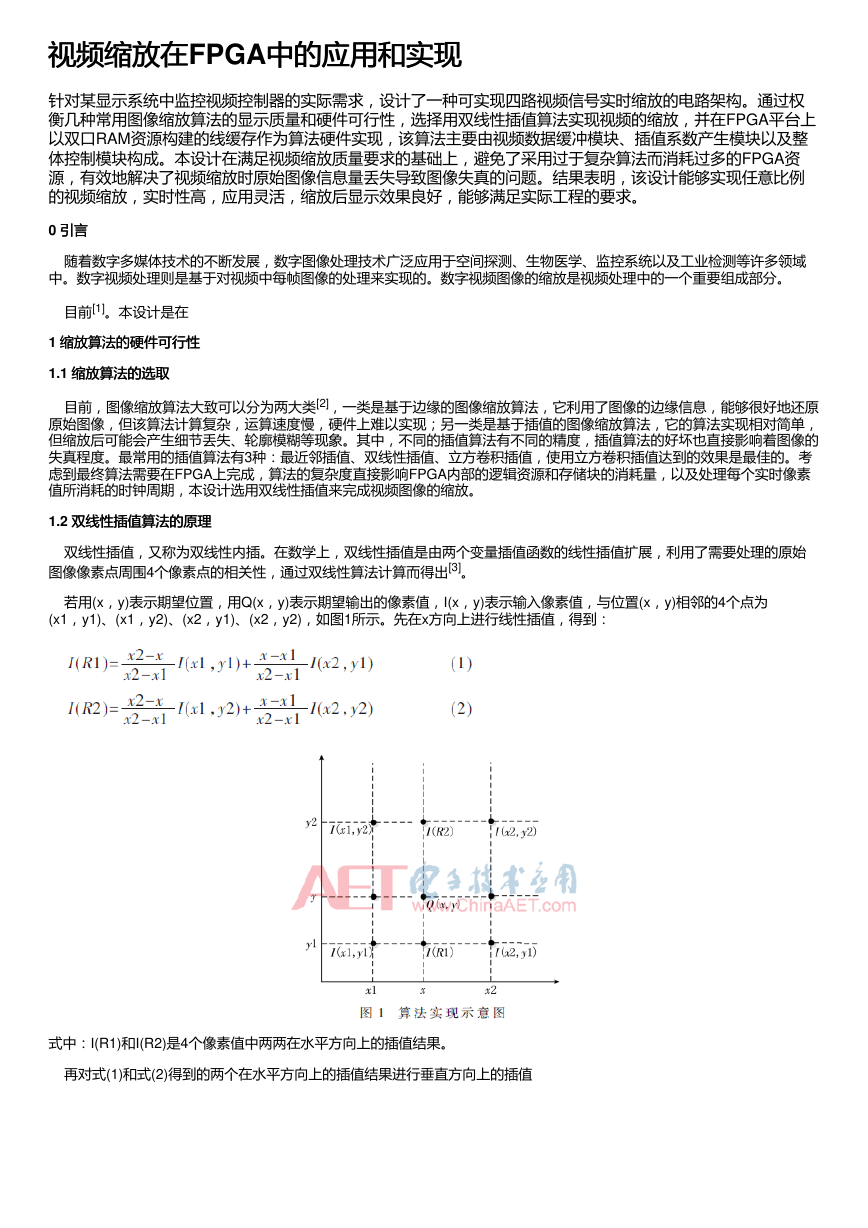

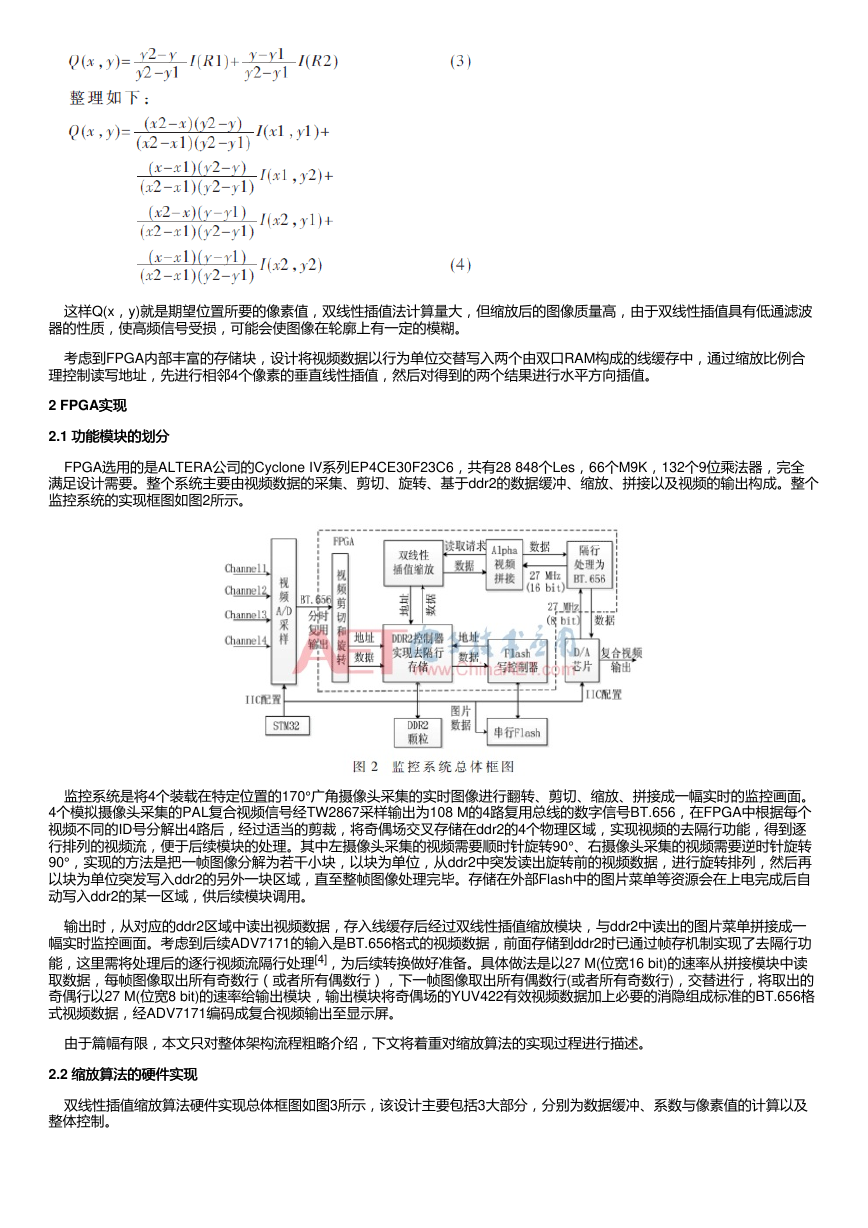

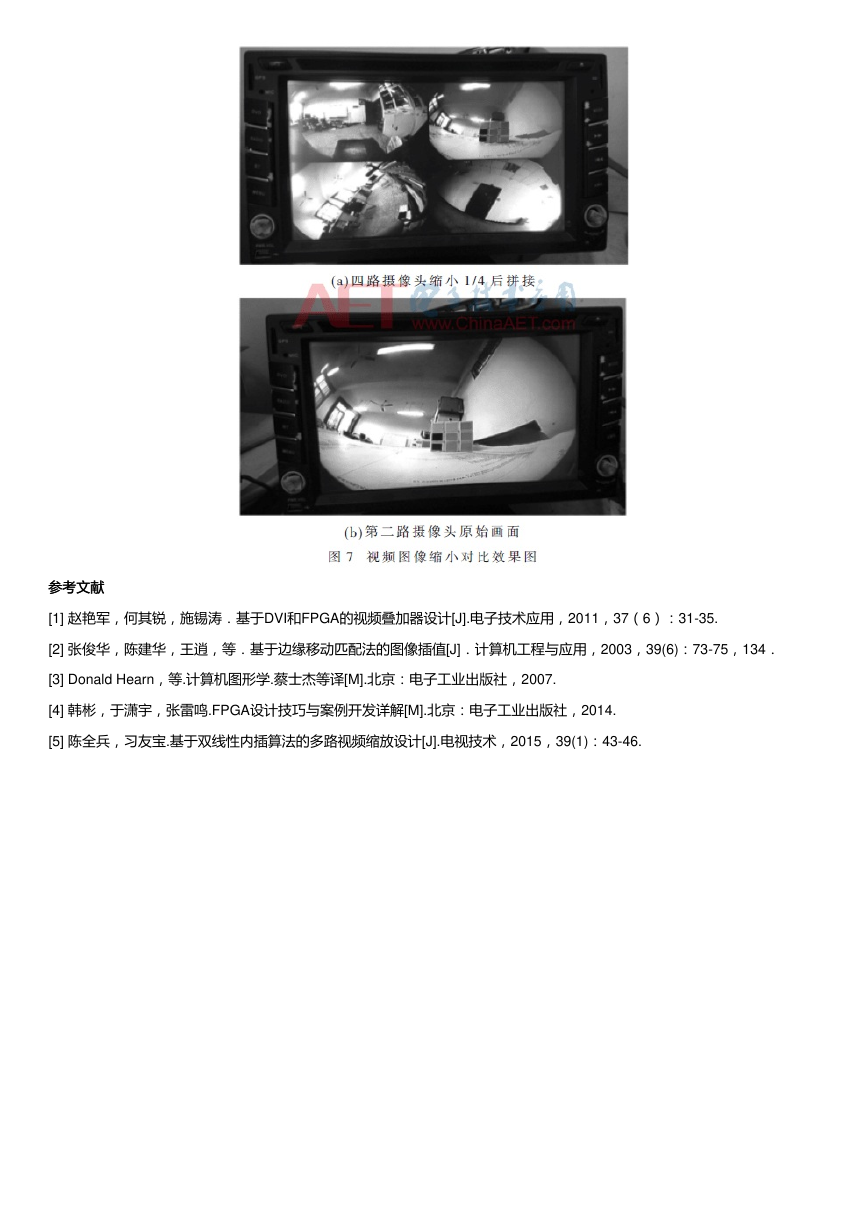

图7为拍摄的实物效果图,图7(a)是将4路摄像头采集的实时图像分别压缩,水平方向和垂直方向各缩小一半后拼接而成。图

7(b)是将第二路摄像头采集的图像显示出来,没经过缩放。由于摄像头采用的是170°广角摄像头,图像4角的黑色是正常现

象。通过效果图可知,本设计方案测试效果良好,适合于实时监控系统的图像采集。

�

参考文献

参考文献

[1] 赵艳军,何其锐,施锡涛.基于DVI和FPGA的视频叠加器设计[J].电子技术应用,2011,37(6):31-35.

[2] 张俊华,陈建华,王逍,等.基于边缘移动匹配法的图像插值[J].计算机工程与应用,2003,39(6):73-75,134.

[3] Donald Hearn,等.计算机图形学.蔡士杰等译[M].北京:电子工业出版社,2007.

[4] 韩彬,于潇宇,张雷鸣.FPGA设计技巧与案例开发详解[M].北京:电子工业出版社,2014.

[5] 陈全兵,习友宝.基于双线性内插算法的多路视频缩放设计[J].电视技术,2015,39(1):43-46.

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc