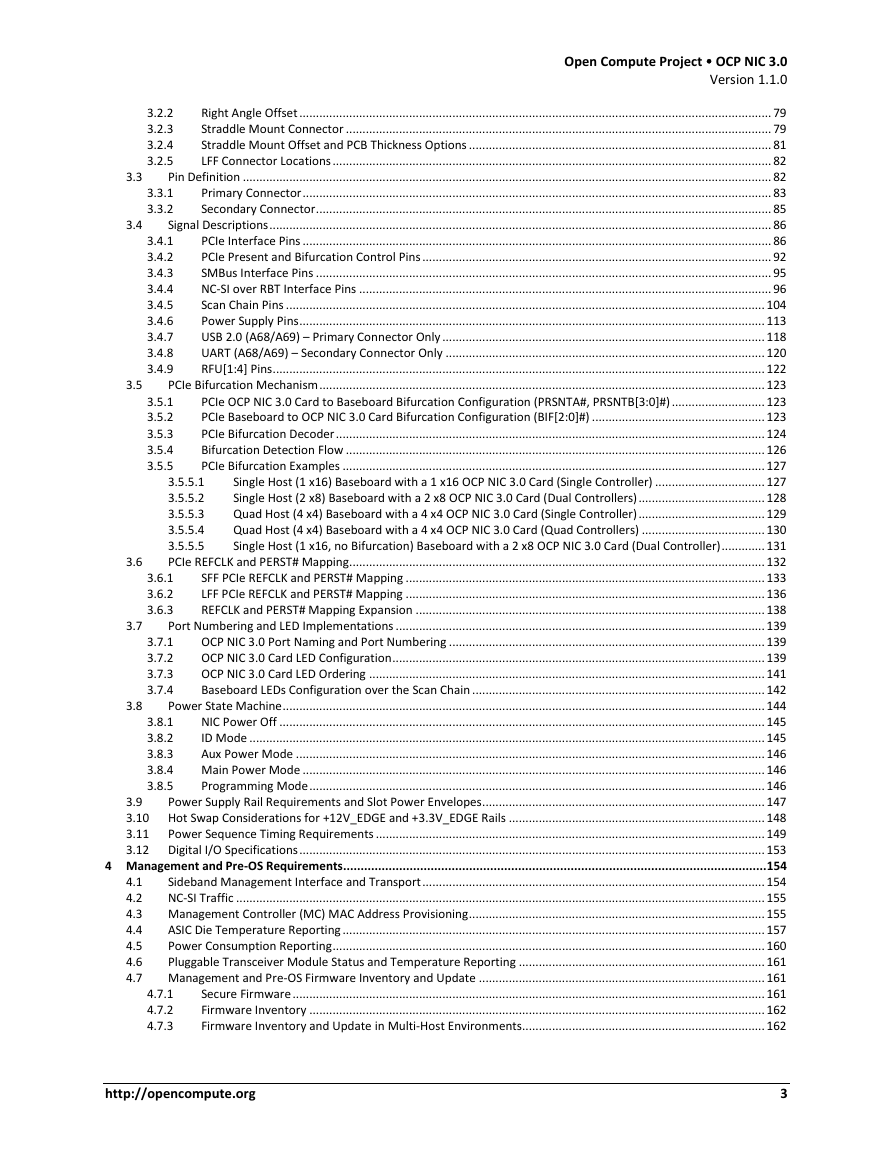

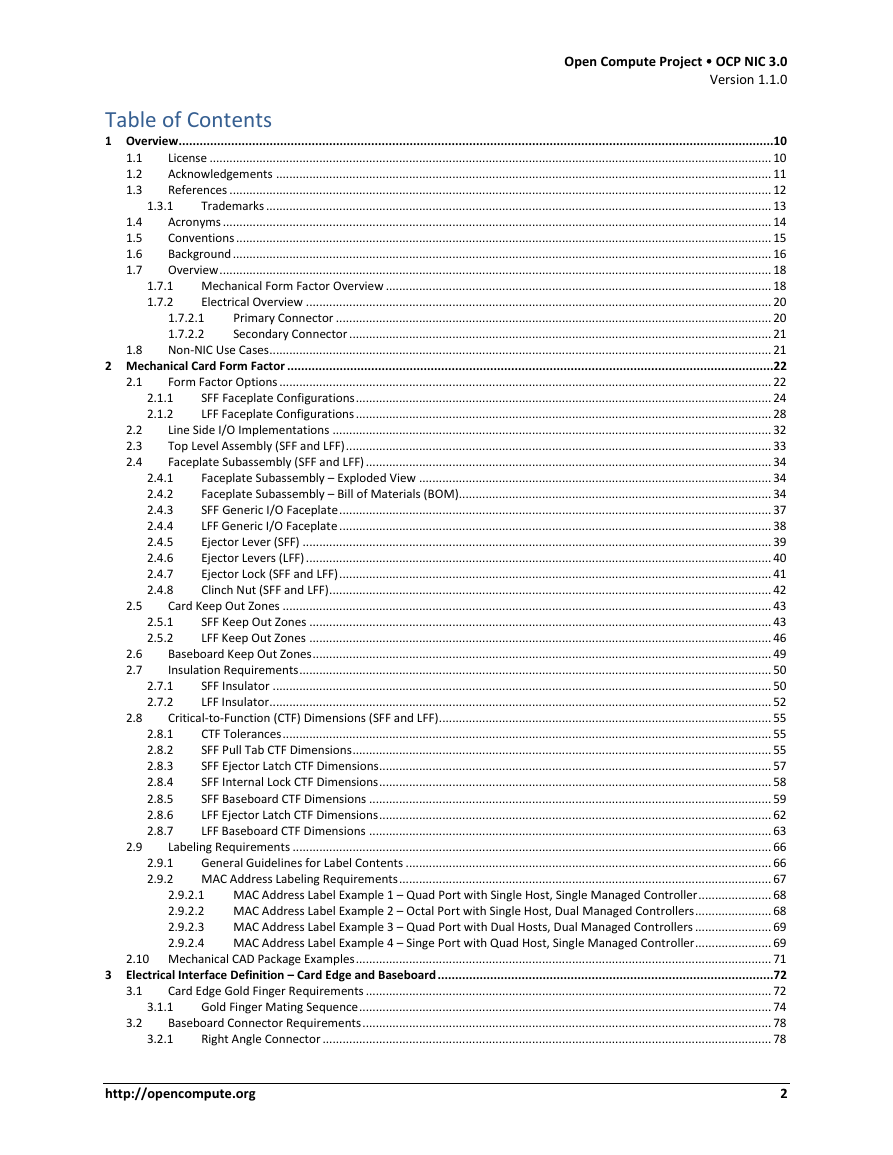

1 Overview

1.1 License

1.2 Acknowledgements

1.3 References

1.3.1 Trademarks

1.4 Acronyms

1.5 Conventions

1.6 Background

1.7 Overview

1.7.1 Mechanical Form Factor Overview

1.7.2 Electrical Overview

1.7.2.1 Primary Connector

1.7.2.2 Secondary Connector

1.8 Non-NIC Use Cases

2 Mechanical Card Form Factor

2.1 Form Factor Options

2.1.1 SFF Faceplate Configurations

2.1.2 LFF Faceplate Configurations

2.2 Line Side I/O Implementations

2.3 Top Level Assembly (SFF and LFF)

2.4 Faceplate Subassembly (SFF and LFF)

2.4.1 Faceplate Subassembly – Exploded View

2.4.2 Faceplate Subassembly – Bill of Materials (BOM)

2.4.3 SFF Generic I/O Faceplate

2.4.4 LFF Generic I/O Faceplate

2.4.5 Ejector Lever (SFF)

2.4.6 Ejector Levers (LFF)

2.4.7 Ejector Lock (SFF and LFF)

2.4.8 Clinch Nut (SFF and LFF)

2.5 Card Keep Out Zones

2.5.1 SFF Keep Out Zones

2.5.2 LFF Keep Out Zones

2.6 Baseboard Keep Out Zones

2.7 Insulation Requirements

2.7.1 SFF Insulator

2.7.2 LFF Insulator

2.8 Critical-to-Function (CTF) Dimensions (SFF and LFF)

2.8.1 CTF Tolerances

2.8.2 SFF Pull Tab CTF Dimensions

2.8.3 SFF Ejector Latch CTF Dimensions

2.8.4 SFF Internal Lock CTF Dimensions

2.8.5 SFF Baseboard CTF Dimensions

2.8.6 LFF Ejector Latch CTF Dimensions

2.8.7 LFF Baseboard CTF Dimensions

2.9 Labeling Requirements

2.9.1 General Guidelines for Label Contents

2.9.2 MAC Address Labeling Requirements

2.9.2.1 MAC Address Label Example 1 – Quad Port with Single Host, Single Managed Controller

2.9.2.2 MAC Address Label Example 2 – Octal Port with Single Host, Dual Managed Controllers

2.9.2.3 MAC Address Label Example 3 – Quad Port with Dual Hosts, Dual Managed Controllers

2.9.2.4 MAC Address Label Example 4 – Singe Port with Quad Host, Single Managed Controller

2.10 Mechanical CAD Package Examples

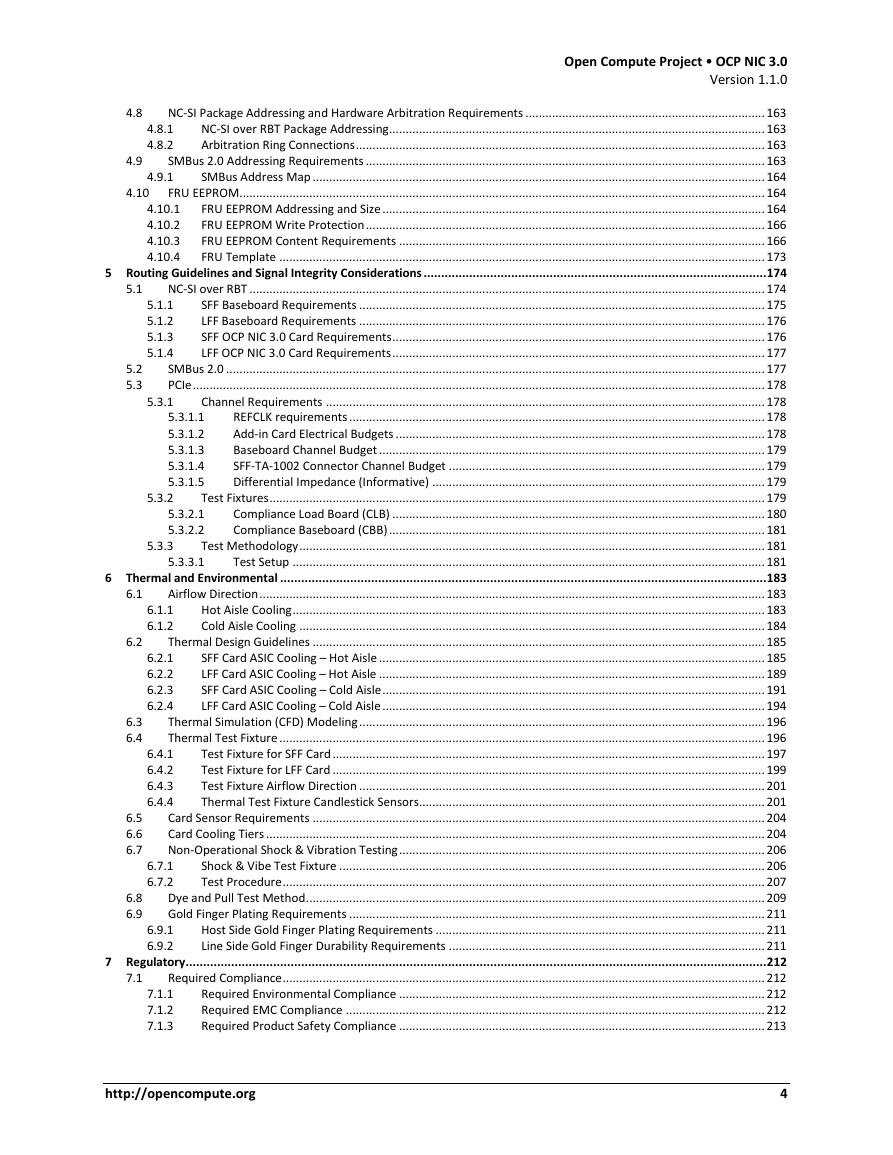

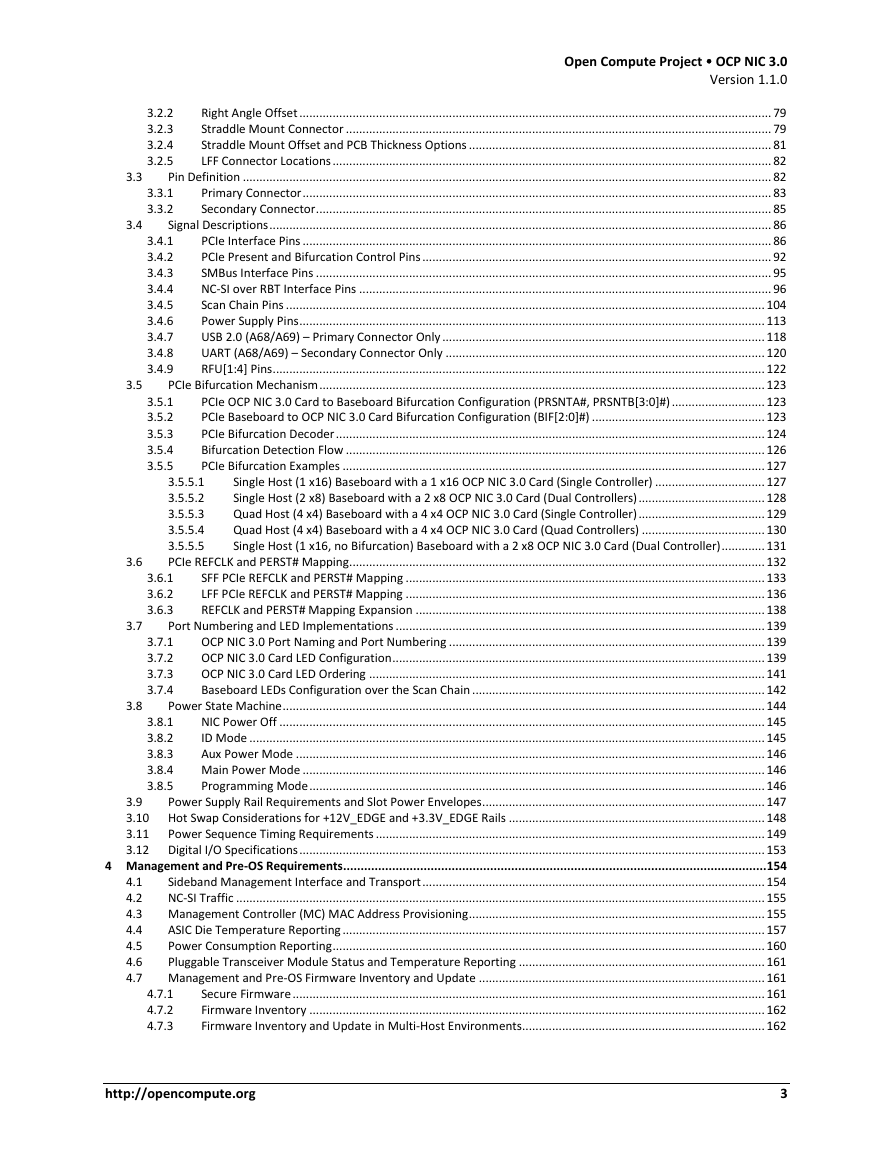

3 Electrical Interface Definition – Card Edge and Baseboard

3.1 Card Edge Gold Finger Requirements

3.1.1 Gold Finger Mating Sequence

3.2 Baseboard Connector Requirements

3.2.1 Right Angle Connector

3.2.2 Right Angle Offset

3.2.3 Straddle Mount Connector

3.2.4 Straddle Mount Offset and PCB Thickness Options

3.2.5 LFF Connector Locations

3.3 Pin Definition

3.3.1 Primary Connector

3.3.2 Secondary Connector

3.4 Signal Descriptions

3.4.1 PCIe Interface Pins

3.4.2 PCIe Present and Bifurcation Control Pins

3.4.3 SMBus Interface Pins

3.4.4 NC-SI over RBT Interface Pins

3.4.5 Scan Chain Pins

3.4.6 Power Supply Pins

3.4.7 USB 2.0 (A68/A69) – Primary Connector Only

3.4.8 UART (A68/A69) – Secondary Connector Only

3.4.9 RFU[1:4] Pins

3.5 PCIe Bifurcation Mechanism

3.5.1 PCIe OCP NIC 3.0 Card to Baseboard Bifurcation Configuration (PRSNTA#, PRSNTB[3:0]#)

3.5.2 PCIe Baseboard to OCP NIC 3.0 Card Bifurcation Configuration (BIF[2:0]#)

3.5.3 PCIe Bifurcation Decoder

3.5.4 Bifurcation Detection Flow

3.5.5 PCIe Bifurcation Examples

3.5.5.1 Single Host (1 x16) Baseboard with a 1 x16 OCP NIC 3.0 Card (Single Controller)

3.5.5.2 Single Host (2 x8) Baseboard with a 2 x8 OCP NIC 3.0 Card (Dual Controllers)

3.5.5.3 Quad Host (4 x4) Baseboard with a 4 x4 OCP NIC 3.0 Card (Single Controller)

3.5.5.4 Quad Host (4 x4) Baseboard with a 4 x4 OCP NIC 3.0 Card (Quad Controllers)

3.5.5.5 Single Host (1 x16, no Bifurcation) Baseboard with a 2 x8 OCP NIC 3.0 Card (Dual Controller)

3.6 PCIe REFCLK and PERST# Mapping

3.6.1 SFF PCIe REFCLK and PERST# Mapping

3.6.2 LFF PCIe REFCLK and PERST# Mapping

3.6.3 REFCLK and PERST# Mapping Expansion

3.7 Port Numbering and LED Implementations

3.7.1 OCP NIC 3.0 Port Naming and Port Numbering

3.7.2 OCP NIC 3.0 Card LED Configuration

3.7.3 OCP NIC 3.0 Card LED Ordering

3.7.4 Baseboard LEDs Configuration over the Scan Chain

3.8 Power State Machine

3.8.1 NIC Power Off

3.8.2 ID Mode

3.8.3 Aux Power Mode

3.8.4 Main Power Mode

3.8.5 Programming Mode

3.9 Power Supply Rail Requirements and Slot Power Envelopes

3.10 Hot Swap Considerations for +12V_EDGE and +3.3V_EDGE Rails

3.11 Power Sequence Timing Requirements

3.12 Digital I/O Specifications

4 Management and Pre-OS Requirements

4.1 Sideband Management Interface and Transport

4.2 NC-SI Traffic

4.3 Management Controller (MC) MAC Address Provisioning

4.4 ASIC Die Temperature Reporting

4.5 Power Consumption Reporting

4.6 Pluggable Transceiver Module Status and Temperature Reporting

4.7 Management and Pre-OS Firmware Inventory and Update

4.7.1 Secure Firmware

4.7.2 Firmware Inventory

4.7.3 Firmware Inventory and Update in Multi-Host Environments

4.8 NC-SI Package Addressing and Hardware Arbitration Requirements

4.8.1 NC-SI over RBT Package Addressing

4.8.2 Arbitration Ring Connections

4.9 SMBus 2.0 Addressing Requirements

4.9.1 SMBus Address Map

4.10 FRU EEPROM

4.10.1 FRU EEPROM Addressing and Size

4.10.2 FRU EEPROM Write Protection

4.10.3 FRU EEPROM Content Requirements

4.10.4 FRU Template

5 Routing Guidelines and Signal Integrity Considerations

5.1 NC-SI over RBT

5.1.1 SFF Baseboard Requirements

5.1.2 LFF Baseboard Requirements

5.1.3 SFF OCP NIC 3.0 Card Requirements

5.1.4 LFF OCP NIC 3.0 Card Requirements

5.2 SMBus 2.0

5.3 PCIe

5.3.1 Channel Requirements

5.3.1.1 REFCLK requirements

5.3.1.2 Add-in Card Electrical Budgets

5.3.1.3 Baseboard Channel Budget

5.3.1.4 SFF-TA-1002 Connector Channel Budget

5.3.1.5 Differential Impedance (Informative)

5.3.2 Test Fixtures

5.3.2.1 Compliance Load Board (CLB)

5.3.2.2 Compliance Baseboard (CBB)

5.3.3 Test Methodology

5.3.3.1 Test Setup

6 Thermal and Environmental

6.1 Airflow Direction

6.1.1 Hot Aisle Cooling

6.1.2 Cold Aisle Cooling

6.2 Thermal Design Guidelines

6.2.1 SFF Card ASIC Cooling – Hot Aisle

6.2.2 LFF Card ASIC Cooling – Hot Aisle

6.2.3 SFF Card ASIC Cooling – Cold Aisle

6.2.4 LFF Card ASIC Cooling – Cold Aisle

6.3 Thermal Simulation (CFD) Modeling

6.4 Thermal Test Fixture

6.4.1 Test Fixture for SFF Card

6.4.2 Test Fixture for LFF Card

6.4.3 Test Fixture Airflow Direction

6.4.4 Thermal Test Fixture Candlestick Sensors

6.5 Card Sensor Requirements

6.6 Card Cooling Tiers

6.7 Non-Operational Shock & Vibration Testing

6.7.1 Shock & Vibe Test Fixture

6.7.2 Test Procedure

6.8 Dye and Pull Test Method

6.9 Gold Finger Plating Requirements

6.9.1 Host Side Gold Finger Plating Requirements

6.9.2 Line Side Gold Finger Durability Requirements

7 Regulatory

7.1 Required Compliance

7.1.1 Required Environmental Compliance

7.1.2 Required EMC Compliance

7.1.3 Required Product Safety Compliance

7.1.4 Required Immunity (ESD) Compliance

7.2 Recommended Compliance

7.2.1 Recommended Environmental Compliance

7.2.2 Recommended EMC Compliance

8 Revision History

8.1 Document Revision History

8.2 FRU Content Revision History

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc