华为硬件机试题目(2019 版本)

一、是非题 [8x4]

1、( )DRAM 上电时存储单元的内容是全 0,而 Flash 上电时存储单元的

内容是全 1。

2、( )眼图可以用来分析高速信号的码间干扰、抖动、噪声和衰减。

3、( )以太网交换机将冲突域限制在每个端口,提高了网络性能。

4、( )放大电路的输出信号产生非线性失真是由于电路中晶体管的非线性引

起的。

5、( )1 的 8 位二进制补码是 0000_0001,-1 的 8 位二进制补码是

1111_1111 。

6、( )洗衣机,电冰箱等家用电器都使用三孔插座, 是因为如果不接地,

家用电器是不能工作的。

7、( )十进制数据 0x5a 与 0xa5 的同或运算结果为: 0x00。

8、( )硅二极管的正向导通压降比锗二极管的大。

.

二、单选题 [17x4]

1、一空气平行板电容器, 两级间距为 d,充电后板间电压为 u。然后将电源

断开,在平板间平行插入一厚度为 d/3 的金属板。 此时电容器原板间电压变

为

A.U/3 B.2U/3 C.3U/4 D.不变

2、8086CPU 内部包括哪些单元

A.ALU,EU B.ALU,BIU C.EU,BIU D.ALU,EU,BIU

�

6 M3 r. w; ?: m1 |' L; [

3、为了避免 50Hz 的电网电压干扰放大器,应该用那种滤波器:

A.带阻滤波器 B.带通滤波器 C.低通滤波器 D.高通滤波器

/ b/ |$ \. h2 k

4、关于 SRAM 和 DRAM,下面说话正确的是:

A.SRAM 需要定时刷新,否则数据会丢失;

B.DRAM 使用内部电容来保存信息;

C.SRAM 的集成度高于 DRAM;

D.只要不掉电, DRAM 内的数据不会丢失;

5、在 RS232 串口中, 采用哪一种校验方式:

A.CRC 校验 B.海明码校验 C.多种校验方式的组合 D.奇偶校验

6、对于 D 触发器来说, 为了保证可靠的采样, 数据必须在时钟信号的上升

沿到来之前继续稳定一段时间,这个时间称为

A.保持时间 B.恢复时间 C.稳定时间 D.建立时间

7、本征半导体中加入()元素可形成 N 型半导体

A.五价 B.四价 C.三价 D.二价

8、模拟信号数字化的过程是

A.采样 ->量化 ->编码 B.采样 ->编码 ->量化

C.编码 ->采样 ->量化 D.量化 ->编码 ->采样

9、在 Buck 电路中,不能起到减小纹波作用的措施是

A.采用多项并联的模式;

�

B.开关管内置,提高电源的开关频率;

C.输出滤波电容由陶瓷电容改为容量电解电容;

D.增大输出滤波电感量。

4 i7 |6 @: D% D, E

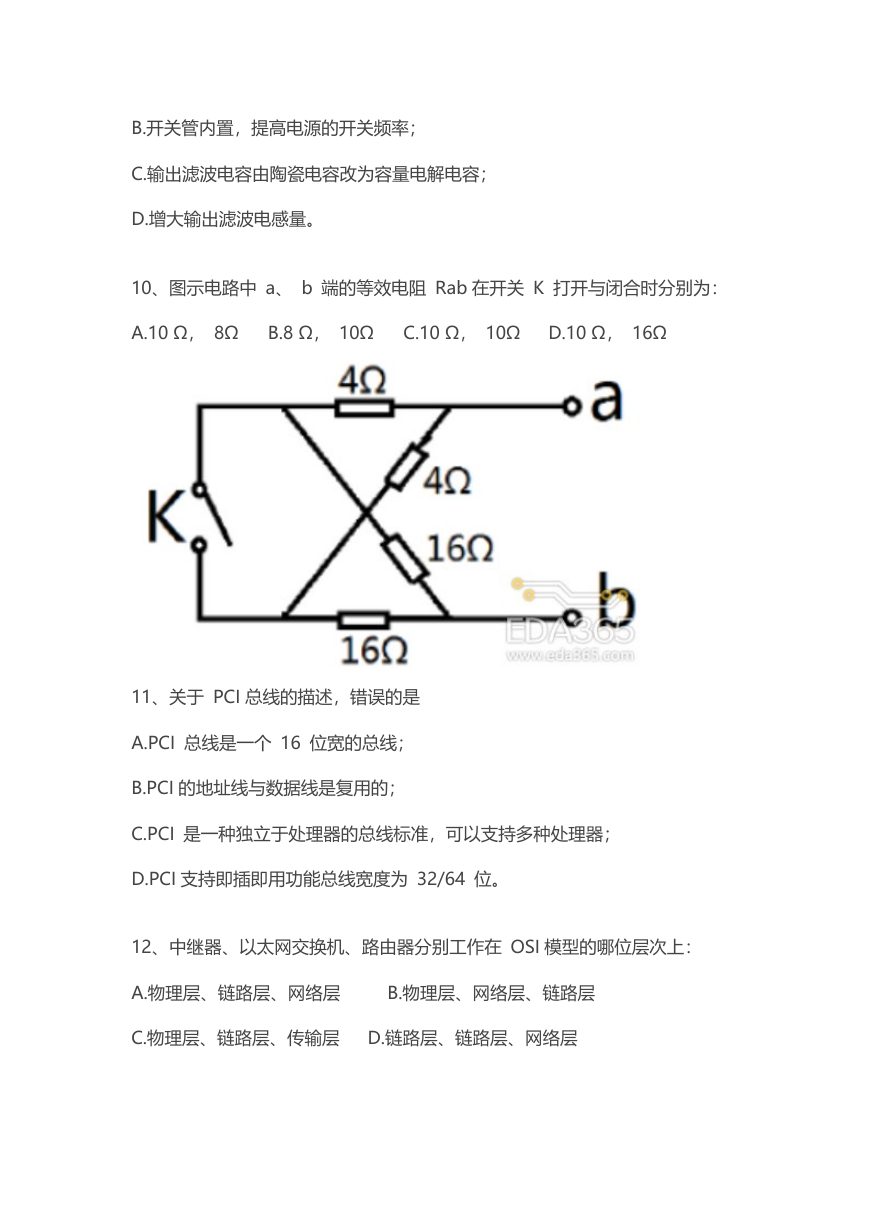

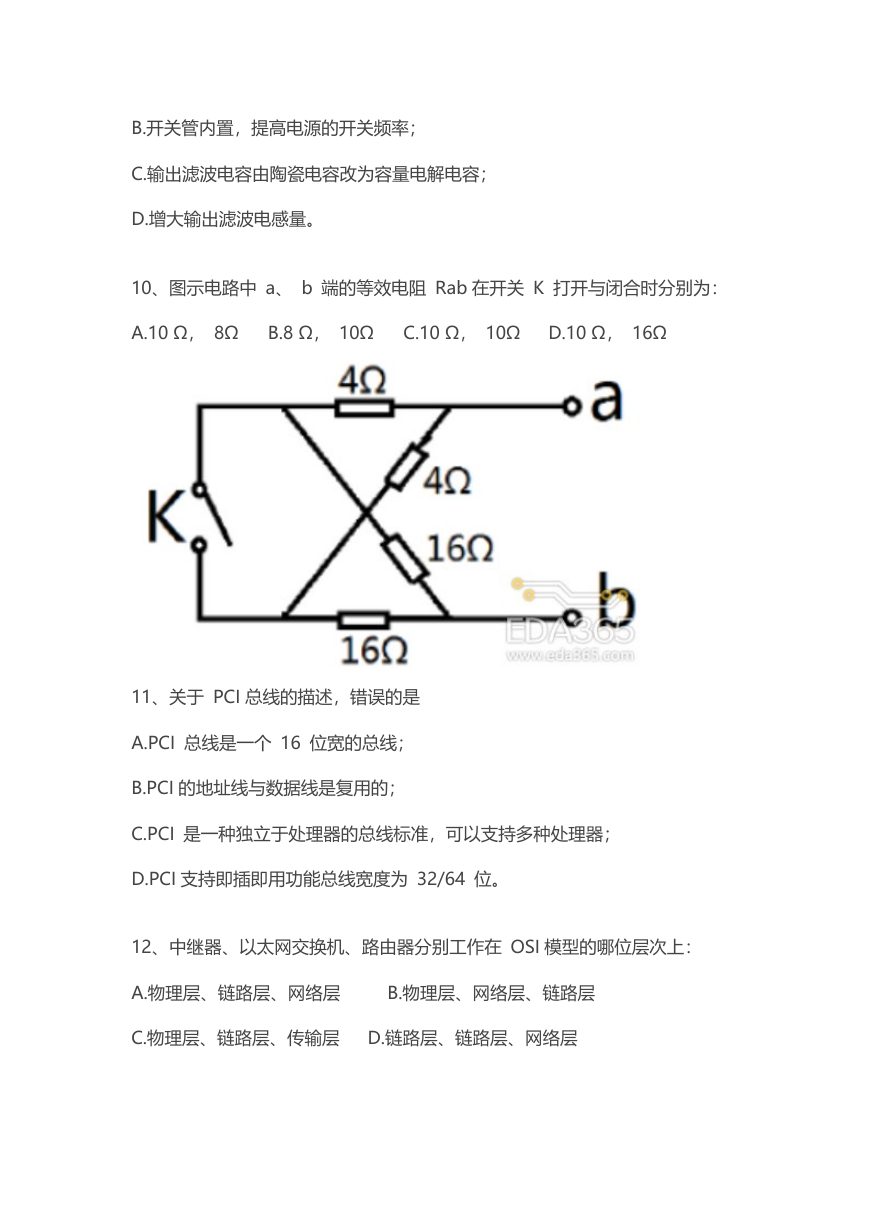

10、图示电路中 a、 b 端的等效电阻 Rab 在开关 K 打开与闭合时分别为:

A.10 Ω, 8Ω B.8 Ω, 10Ω C.10 Ω, 10Ω D.10 Ω, 16Ω

11、关于 PCI 总线的描述,错误的是

A.PCI 总线是一个 16 位宽的总线;

B.PCI 的地址线与数据线是复用的;

C.PCI 是一种独立于处理器的总线标准,可以支持多种处理器;

D.PCI 支持即插即用功能总线宽度为 32/64 位。

0 | p+ T, X, C2 j/ Z% y, h) Z5 [

12、中继器、以太网交换机、路由器分别工作在 OSI 模型的哪位层次上:

A.物理层、链路层、网络层 B.物理层、网络层、链路层

C.物理层、链路层、传输层 D.链路层、链路层、网络层

7 @( o- l1 F$ x" F

�

13、某电路,对 100KHz 以下低频信号干扰敏感,为减少干扰,应采用()滤

波器。

A.高通 B.低通 C.带阻 D.带通

0 c4 o7 c+ H3 p

14、捕捉毛刺用最佳触发方式()进行触发

A.Width B.Edge C.Glitch D.State

15、以下哪种信号异常能用逻辑分析仪测试:

A.信号占空比超标 B.信号上升缓慢

C.6 个信号的异常组合 D.信号抖动过大

' N1 I1 v+ x; T0 G0 B

16、8421 码 10010111 表示的十进制数是:

A.98 B.151 C.97 D.227

. n, h& b, P( K! e2 V# s

17、晶体管能够放大的外部条件是:

A.发射结反偏,集电结正偏 B.发射结正偏,集电结正偏

C.发射结反偏,集电结反偏 D.发射结正偏,集电结反偏

2 Y3 G: f. }& e* G; J$ |- g, m$ T

答案与解析

.

一、是非题 [8x4]

1、(N)【解析】FLASH 可保存

2、(N)

3、(Y)

�

4、(N)

5、(Y)

6、(N)

7、(Y)

8、(Y)

.

二、单选题 [17x4]

1、B.2U/3

【解析】

电容的大小不是由 Q(带电量)或 U(电压)决定的,即:

C=εS/4πkd。(ε 是一个常数, S 为电容极板的正对面积, d 为电容极板的

距离, k 则是静电力常量。)而常见的平行板电容器电容为 C=εS/d. (ε 为

极板间介质的介电常数,S 为极板面积, d 为极板间的距离。)电容器的电势

能计算公式:E=CU^2/2=QU/2。

2、C.EU,BIU

【解析】

80x86 从功能上分执行单元 EU(Execution Unit) 和总线接口单元

BIU(Bus InteRFace Unit) ,执行单元由 8 个 16 位通用寄存器, 1 个 16

位标志寄存器, 1 个 16 位暂存寄存器, 1 个 16 位算术逻辑单元 ALU 及

EU 控制电路组成。总线接口单元由 4 个 16 位段寄存器

( CS,DS,SS,ES) ,1 个 16 位的指令指针寄存器, 1 个与 EU 通信的内部

�

暂存器, 1 个指令队列, 1 个计算 20 位物理地址的加法器∑及总线控制电

路构成。

+ Y. R, j8 m, ~

3、A.带阻滤波器

0 P& _. J: a" c7 i

4、B.DRAM 使用内部电容来保存信息

【解析】

SRAM 和 DRAM 都是随机存储器,机器掉电后,两者的信息都将丢

失。它们的最大区别就是:DRAM 是用电容有无电荷来表示信息 0 和 1,为

防止电容漏电而导致读取信息出错,需要周期性地给电容充电,即刷新;而

SRAM 是利用触发器的两个稳态来表示信息 0 和 1, 所以不需要刷新。 另

外, SRAM 的存取速度比 DRAM 更高,常用作高速缓冲存储器 Cache。

5、D.奇偶校验

6、D.建立时间

【解析】

setup/hold time 是测试芯片对输入信号和时钟信号之间的时间要求 .

建立时间是指触发器的时钟信号上升沿到来以前数据稳定不变的时间输入信号

应提前时钟上升沿 ( 如上升沿有效 )T 时间到达芯片 这 个 T 就 是 建 立

时 间 -Setup time. 如不 满 足 setup time, 这个数据就不能被这一时钟打入

触发器只有在下一个时钟上升沿数据才能被打入触发器保持时间是指触发器的

时钟信号上升沿到来以后数据稳定不变的时间如果 hold time 不够数据同样不

能被打入触发器建立时间 (Setup Time) 和保持时间 (Hold time).建立时间是

�

指在时钟边沿前数据信号需要保持不变的时间保持时间是指时钟跳变边沿后数

据。

7、本征半导体中加入()元素可形成 N 型半导体

A.五价

8、A.采样 ->量化 ->编码

9、C.输出滤波电容由陶瓷电容改为容量电解电容

- p" @; I3 x0 y: n) m+ {: L3 k9 J( Q

10、C.10 Ω, 10Ω

11、A.PCI 总线是一个 16 位宽的总线

8 I5 i7 r# ?2 ?& A6 d$ F, E

12、C.物理层、链路层、传输层

【解析】

物理层 : 将数据转换为可通过物理介质传送的电子信号 相当于邮局中的搬运

工人

链路层 : 决定访问网络介质的方式在此层将数据分帧,并处理流控制。本层

指定拓扑结构并提供硬件寻 址。相当于邮局中的装拆箱工人

网络层 : 使用权数据路由经过大型网络 相当于邮局中的排序工人传输层 : 提

供终端到终端的可靠连接 相当于公司中跑邮局的送信职员

会话层 : 允许用户使用简单易记的名称建立连接相当于公司中收寄信、写信封

与拆信封的秘书

表示层 : 协商数据交换格式 相当公司中简报老板、替老板写信的助理

�

应用层 : 用户的应用程序和网络之间的接口老板

13、A.高通

14、C.Glitch

15、A.信号占空比超标

16、C.97

1 ~: P8 z! r- a o! B' Z

17、D.发射结正偏,集电结反偏

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc