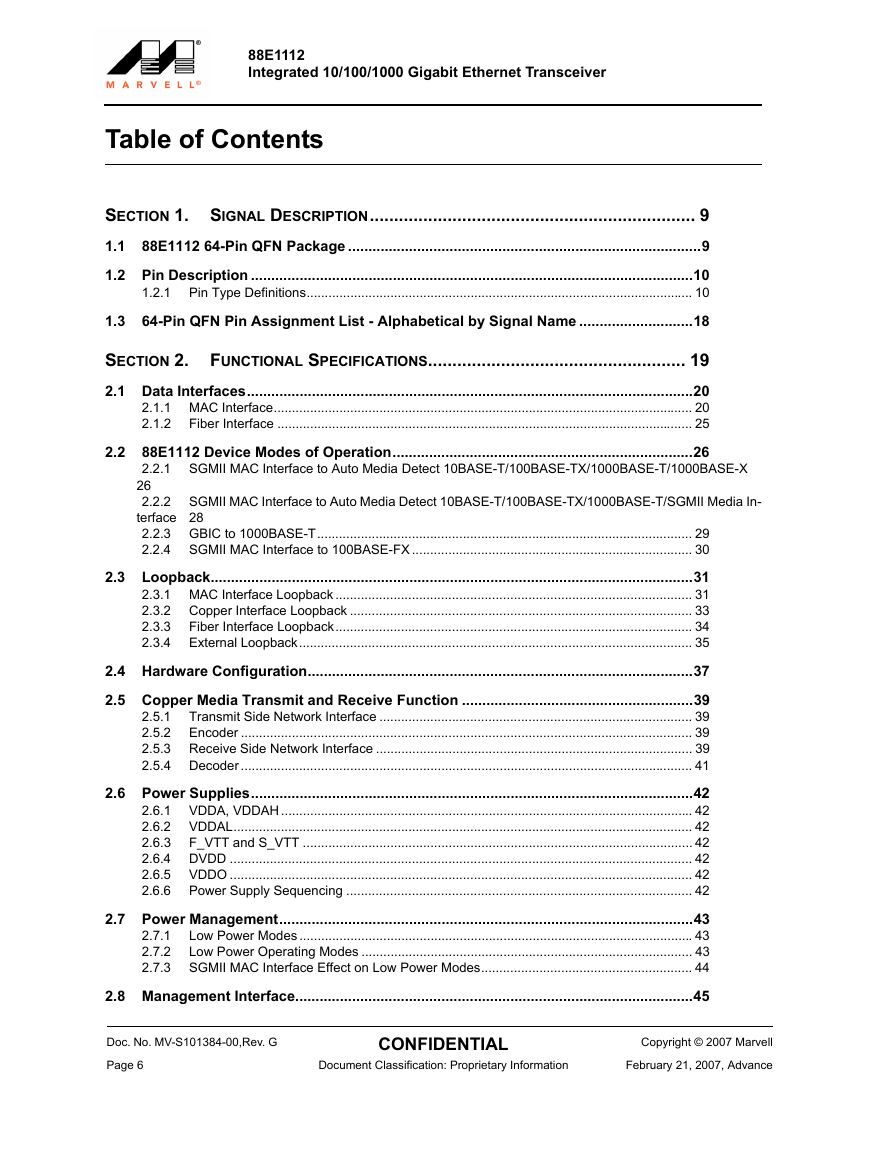

Section 1. Signal Description

1.1 88E1112 64-Pin QFN Package

1.2 Pin Description

1.2.1 Pin Type Definitions

1.3 64-Pin QFN Pin Assignment List - Alphabetical by Signal Name

Section 2. Functional Specifications

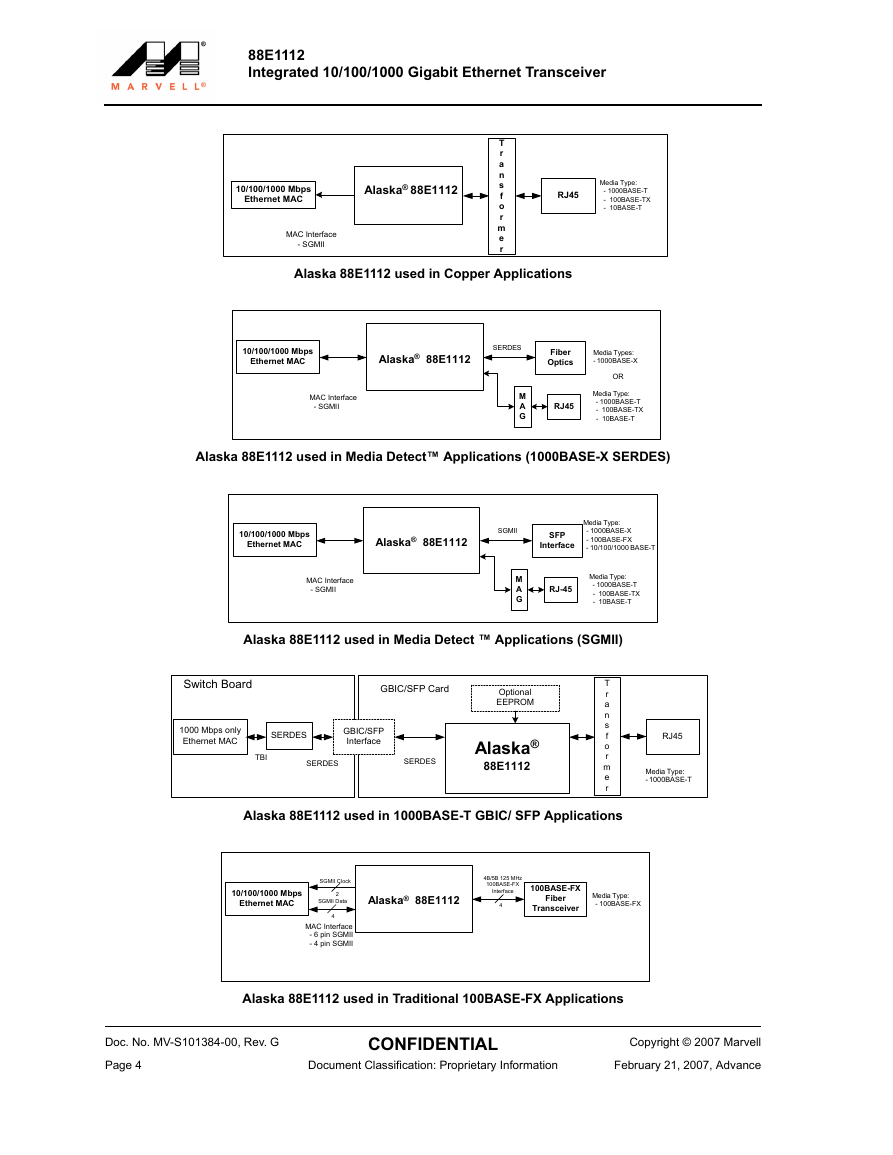

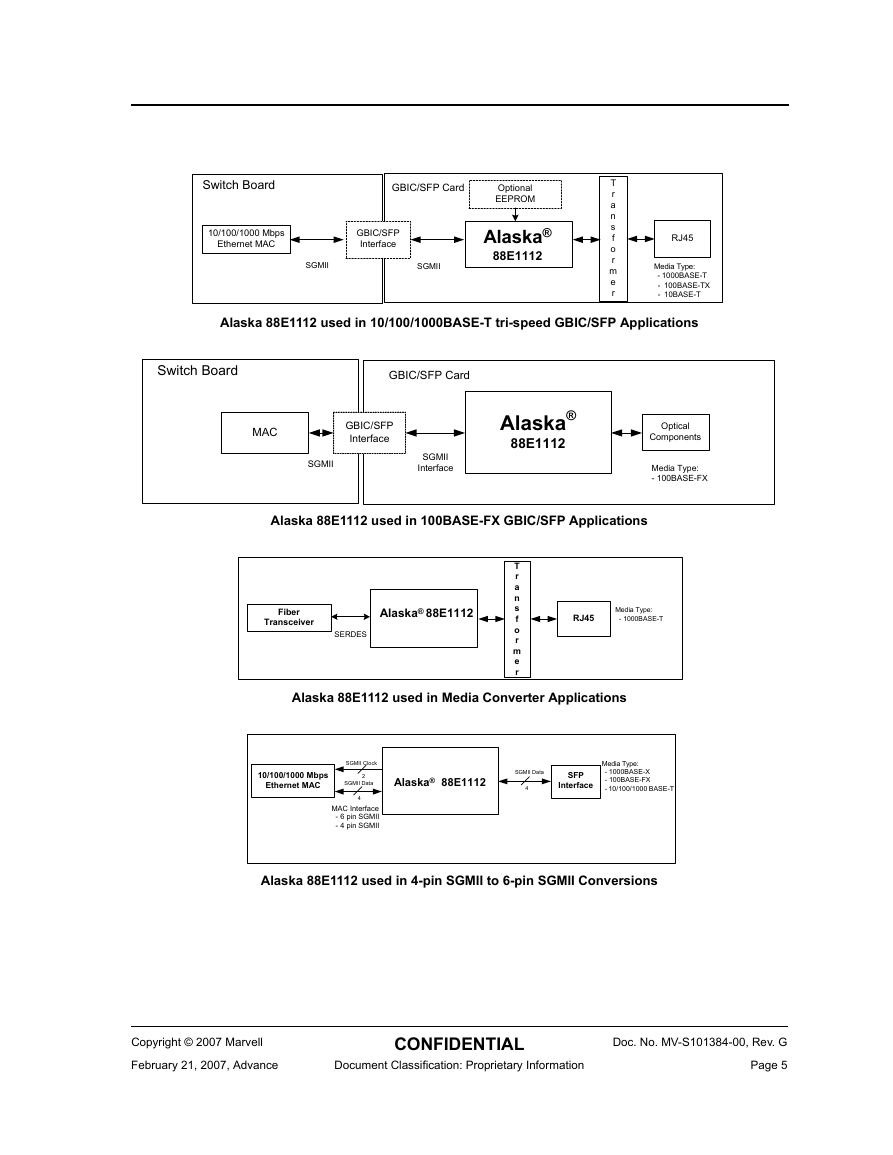

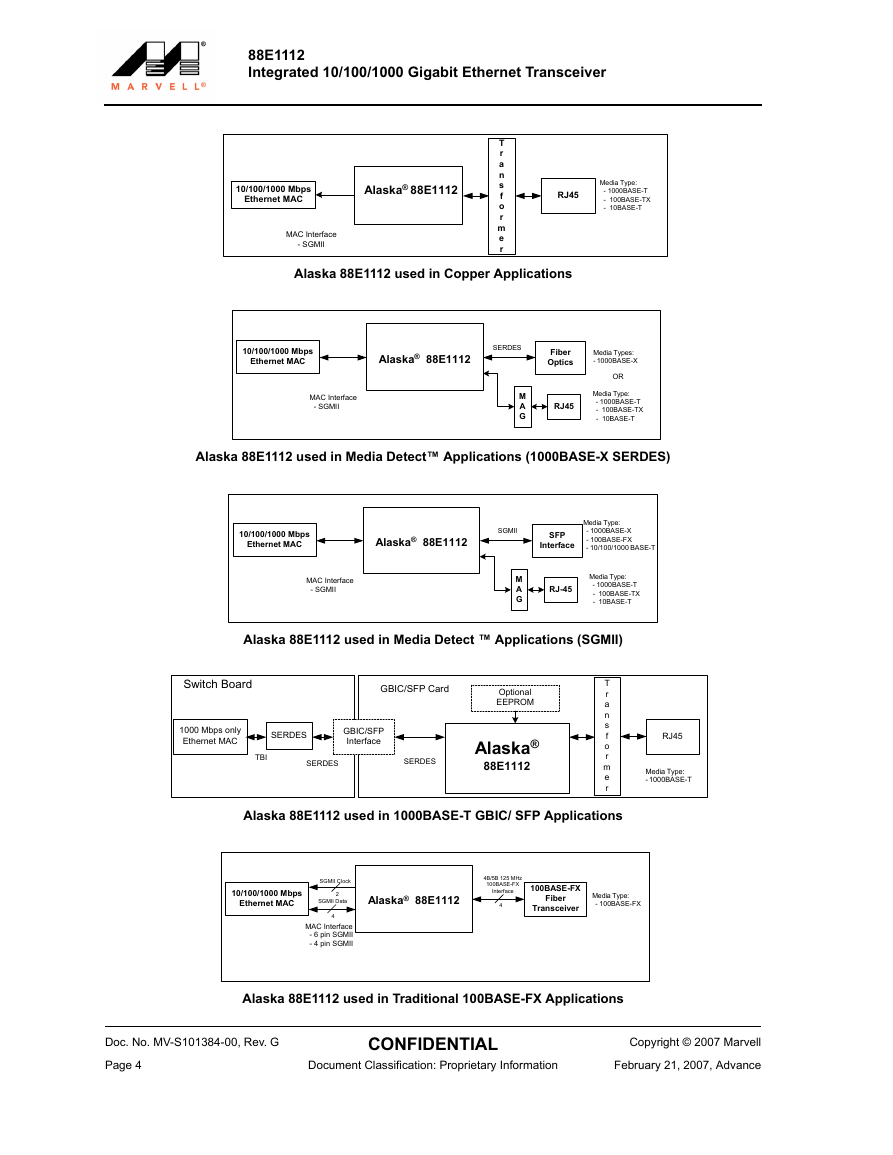

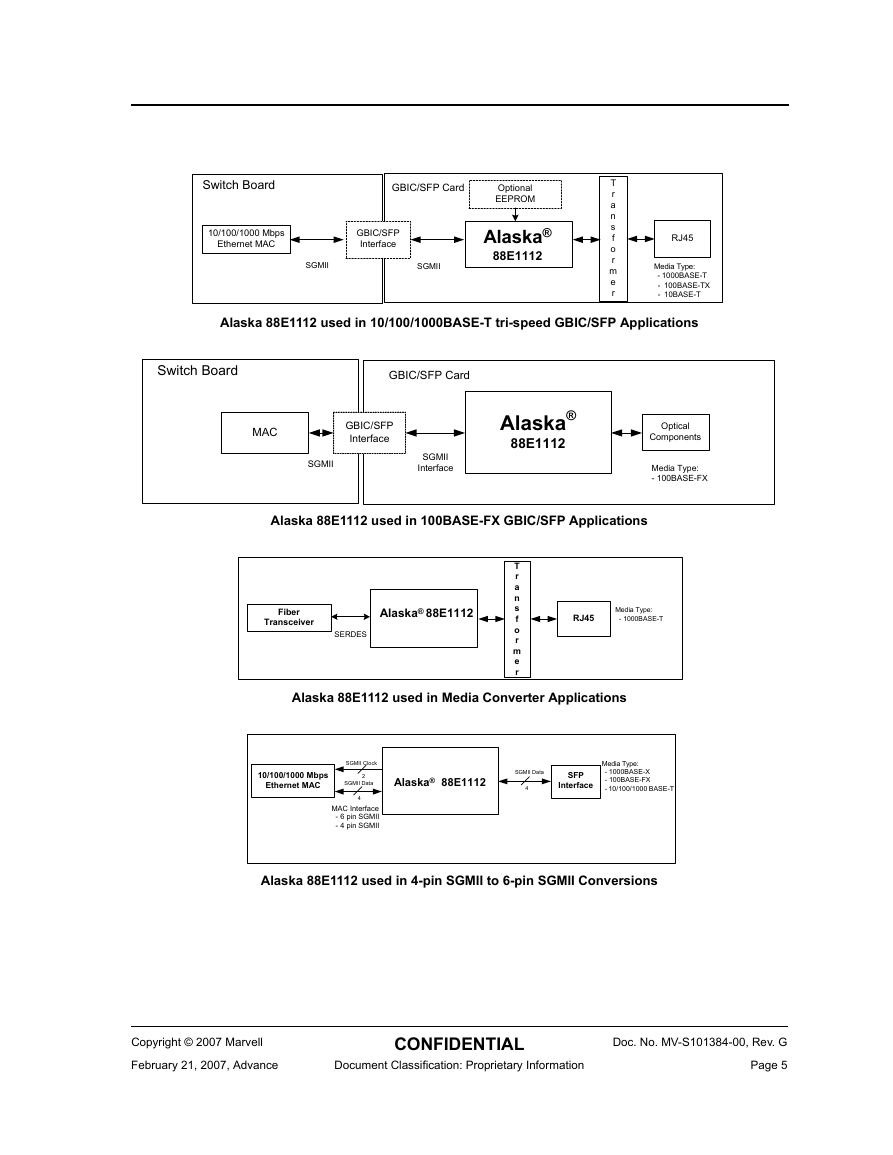

2.1 Data Interfaces

2.1.1 MAC Interface

2.1.1.1 SGMII MAC Interface

2.1.1.2 GBIC/SFP Interface

2.1.1.3 Media Converter MAC Interface

2.1.2 Fiber Interface

2.2 88E1112 Device Modes of Operation

2.2.1 SGMII MAC Interface to Auto Media Detect 10BASE-T/ 100BASE-TX/1000BASE-T/1000BASE-X

2.2.2 SGMII MAC Interface to Auto Media Detect 10BASE-T/ 100BASE-TX/1000BASE-T/SGMII Media Interface

2.2.3 GBIC to 1000BASE-T

2.2.4 SGMII MAC Interface to 100BASE-FX

2.3 Loopback

2.3.1 MAC Interface Loopback

2.3.2 Copper Interface Loopback

2.3.3 Fiber Interface Loopback

2.3.4 External Loopback

2.3.4.1 Copper Media

2.3.4.2 Fiber Media

2.4 Hardware Configuration

2.5 Copper Media Transmit and Receive Function

2.5.1 Transmit Side Network Interface

2.5.1.1 Multi-mode TX Digital to Analog Converter

2.5.1.2 Slew Rate Control and Waveshaping

2.5.2 Encoder

2.5.2.1 1000BASE-T

2.5.2.2 100BASE-TX

2.5.2.3 10BASE-T

2.5.3 Receive Side Network Interface

2.5.3.1 Analog to Digital Converter

2.5.3.2 Active Hybrid

2.5.3.3 Echo Canceller

2.5.3.4 NEXT Canceller

2.5.3.5 Baseline Wander Canceller

2.5.3.6 Digital Adaptive Equalizer

2.5.3.7 Digital Phase Lock Loop

2.5.3.8 Link Monitor

2.5.3.9 Signal Detection

2.5.4 Decoder

2.5.4.1 1000BASE-T

2.5.4.2 100BASE-TX

2.5.4.3 10BASE-T

2.6 Power Supplies

2.6.1 VDDA, VDDAH

2.6.2 VDDAL

2.6.3 F_VTT and S_VTT

2.6.4 DVDD

2.6.5 VDDO

2.6.6 Power Supply Sequencing

2.7 Power Management

2.7.1 Low Power Modes

2.7.2 Low Power Operating Modes

2.7.2.1 IEEE Power Down Mode

2.7.2.2 Energy Detect Power Down Modes

2.7.2.3 Normal 10/100/1000 Mbps Operation

2.7.3 SGMII MAC Interface Effect on Low Power Modes

2.8 Management Interface

2.8.1 Extended Register Access

2.8.2 Preamble Suppression

2.9 Two-Wire Serial Interface

2.9.1 Bus Operation

2.9.2 Read and Write Operations

2.9.2.1 Random Write

2.9.2.2 Sequential Write

2.9.2.3 Current Address Read

2.9.2.4 Random Read

2.9.2.5 Sequential Read

2.10 Auto-Negotiation

2.10.1 10/100/1000BASE-T Auto-Negotiation

2.10.2 1000BASE-X Auto-Negotiation

2.10.3 SGMII Auto-Negotiation

2.10.3.1 SGMII MAC Interface Auto-Negotiation

2.10.3.2 SGMII Media Interface Auto-Negotiation

2.10.4 GBIC Mode Auto-Negotiation

2.10.5 Auto-Media Detect Auto-Negotiation

2.10.6 Serial Interface Auto-Negotiation Bypass Mode

2.11 Fiber/Copper Auto-Selection

2.11.1 Preferred Media

2.11.2 Definition of link in SGMII Media Interface in the context of auto media selection

2.11.3 Notes on Determining which Media Linked Up

2.11.3.1 Polling Method 1

2.11.3.2 Polling Method 2

2.12 Downshift Feature

2.13 Virtual Cable Tester® (VCT™)

2.14 Data Terminal Equipment (DTE) Detect

2.15 CRC Error Counter and Packet Counter

2.15.1 Enabling The CRC Error Counter and Packet Counter

2.16 Packet Generator

2.17 MDI/MDIX Crossover

2.18 Polarity Correction

2.19 EEPROM Interface

2.19.1 Initializing the PHY with an EEPROM

2.19.2 Host Read and Write Commands to EEPROM and non- EEPROM Devices

2.19.3 Read and Write Commands

2.19.4 PHY Register Initialization

2.19.5 Bridging Function

2.19.5.1 Read from Two-Wire Serial Interface slave device to the MDIO

2.19.5.2 Write from MDIO into the Two-Wire Serial Interface slave device

2.19.6 INIT Functionality

2.20 Interrupt

2.21 LED

2.21.1 LED Polarity

2.21.2 Pulse Stretching and Blinking

2.21.3 Bi-Color LED Mixing

2.21.4 Modes of Operation

2.21.4.1 Compound Single LED Statuses

2.21.4.2 Speed Blink

2.21.4.3 Manual Override

2.21.4.4 MODE 1, MODE 2, MODE 3, MODE 4

Section 3. Register Description

Section 4. Electrical Specifications

4.1. Absolute Maximum Ratings

4.2. Recommended Operating Conditions

4.3. Package Thermal Information

4.4. Current Consumption

4.4.1 Current Consumption VDDO

4.4.2 Current Consumption VDDAH

4.4.3 Current Consumption VDDAL

4.4.4 Current Consumption VDDA

4.4.5 Current Consumption Center Tap

4.4.6 Current Consumption DVDD

4.4.7 Current Consumption F_VTT

4.4.8 Current Consumption S_VTT

4.5. DC Operating Conditions

4.5.0.1 Digital Pins

4.5.1 Internal Resistor Description

4.5.2 IEEE DC Transceiver Parameters

4.5.3 Fiber and MAC Interface

4.5.3.1 Transmitter DC Characteristics

4.5.3.2 Common Mode Voltage (Voffset) Calculations

4.5.3.3 Receiver DC Characteristics

4.6. AC Electrical Specifications

4.6.1 Reset Timing

4.6.2 XTAL1/XTAL2 Timing

4.6.3 STATUS[1:0] to CONFIG[5:0] Timing

4.7. SGMII MAC Interface Timing

4.7.1 Serial Interface and SGMII Output AC Characteristics

4.7.2 Serial Interface and SGMII Input AC Characteristics

4.8. 1000BASE-X,SGMII Media Interface and 100BASE-FX Interface Timing

4.9. MDC/MDIO Timing

4.10. Two-Wire Serial Interface (Slave) Timing

4.11. Two-Wire Serial Interface (Master) Timing

4.12. IEEE AC Transceiver Parameters

4.13. Latency Timing

4.13.1 SGMII MAC Interface/GBIC to 10/100/1000BASE-T Transmit Latency Timing

4.13.2 10/100/1000BASE-T to SGMII MAC Interface/GBIC Receive Latency Timing

4.13.3 SGMII MAC Interface to SGMII Media Interface/1000BASE-X Transmit Latency Timing

4.13.4 SGMII Media Interface/1000BASE-X to SGMII MAC Interface Receive Latency Timing

4.13.5 SGMII MAC Interface to 100BASE-FX Transmit Latency Timing

4.13.6 100BASE-FX to SGMII MAC Interface Receive Latency Timing

Section 5. Mechanical Drawings

5.1 64 - Pin 9x9 mm QFN Package

Section 6. Order Information

6.1 Ordering Part Numbers and Package Markings

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc