Micron Confidential and Proprietary

1Gb: x8 NAND Flash Memory

Features

NAND Flash Memory

MT29F1G08ABAFAWP-ITE:F, MT29F1G08ABAFAH4-ITE:F,

MT29F1G08ABBFAH4-ITE:F

Features

• Open NAND Flash Interface (ONFI) 1.0-compliant1

• Single-level cell (SLC) technology

• Organization

– Page size x8: 2176 bytes (2048 + 128 bytes)

– Block size: 64 pages (128K + 8K bytes)

– Plane size: 1 planes x 1024 blocks per plane

– Device size: 1Gb: 1024 blocks

• Asynchronous I/O performance

– tRC/tWC: 20ns/20ns (3.3V), 30ns/30ns (1.8V)

• Array performance

– Read page: 80µs

– Program page: 220µs (TYP 3.3V/1.8V)

– Erase block: 2ms (TYP)

• Command set: ONFI NAND Flash Protocol

• Advanced command set

– Program page cache mode

– Read page cache mode

– Permanent block locking (blocks 47:0)

– One-time programmable (OTP) mode

– Block lock (1.8V only)

– Programmable drive strength

– Read unique ID

– Internal data move

• Operation status byte provides software method for

detecting

– Operation completion

– Pass/Fail condition

– Write-protect status

• Ready/Busy# (R/B#) signal provides a hardware

method of detecting operation completion

• WP# signal: Write protect entire device

• ECC: 8-bit internal ECC is enabled by default.2 It

can not be disabled

• Blocks 7-0 are valid when shipped from factory with

ECC

• RESET (FFh) required as first command after pow-

er-on

• Alternate method of device initialization after pow-

er-up (contact factory)

• Internal data move operations supported within the

plane from which data is read

• Quality and reliability

– Endurance: 100,000 PROGRAM/ERASE cycles

– Data retention: JESD47G-compliant; see qualifi-

cation report

– Additional: Uncycled data retention: 10 years

24/7 @ 85°C

• Operating voltage range

– VCC: 2.7–3.6V

– VCC: 1.7–1.95V

• Operating temperature:

– Industrial (IT): –40°C to +85°C

• Package

– 48-pin TSOP type 1, CPL3

– 63-ball VFBGA

Notes:

1. The ONFI 1.0 specification is available at

www.onfi.org.

2. Refer to the Part Numbering Information to

check the default status of the ECC. If ECC is

enabled by default, it can not be disabled.

3. CPL = Center parting line.

CCMTD-1725822587-10323

m78a_1gb_ecc_on_embedded_nand.pdf – Rev. E 6/19 EN

Products and specifications discussed herein are subject to change by Micron without notice.

1

Micron Technology, Inc. reserves the right to change products or specifications without notice.

© 2016 Micron Technology, Inc. All rights reserved.

�

Micron Confidential and Proprietary

1Gb: x8 NAND Flash Memory

Features

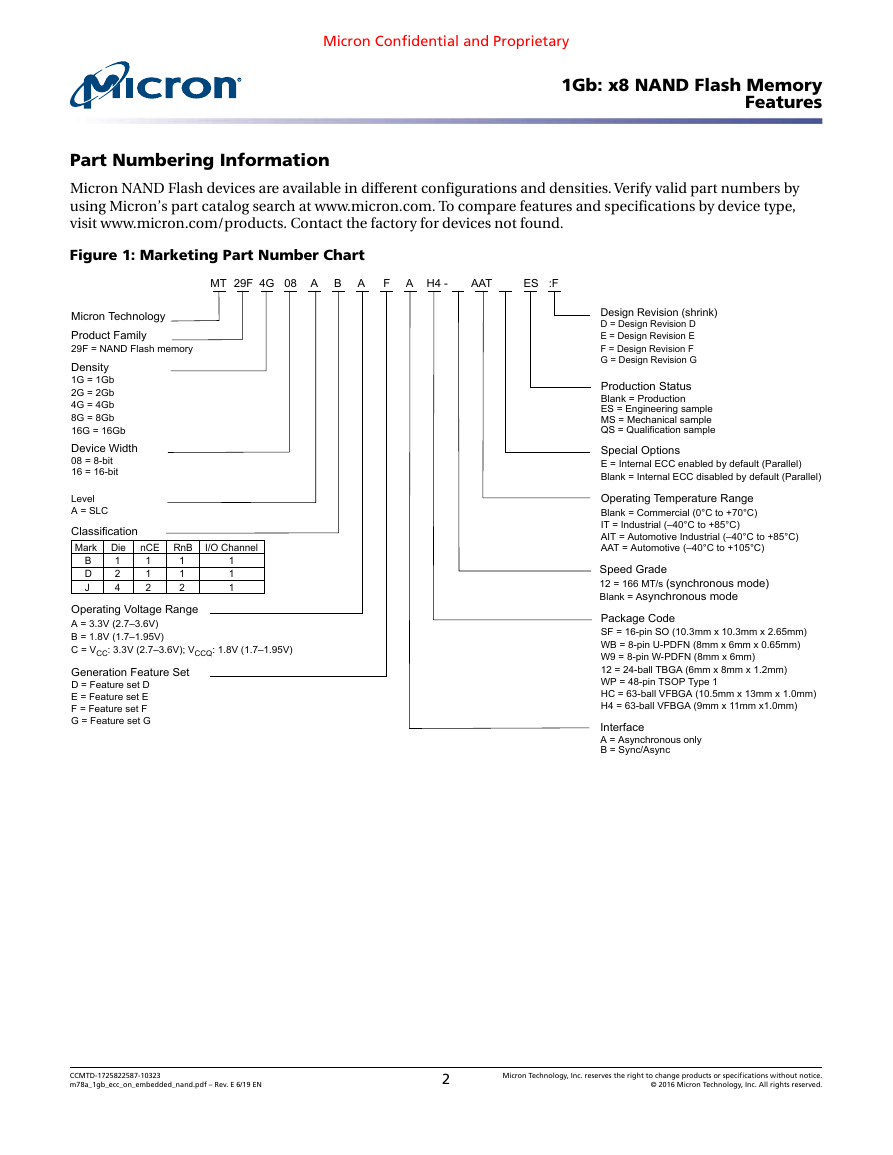

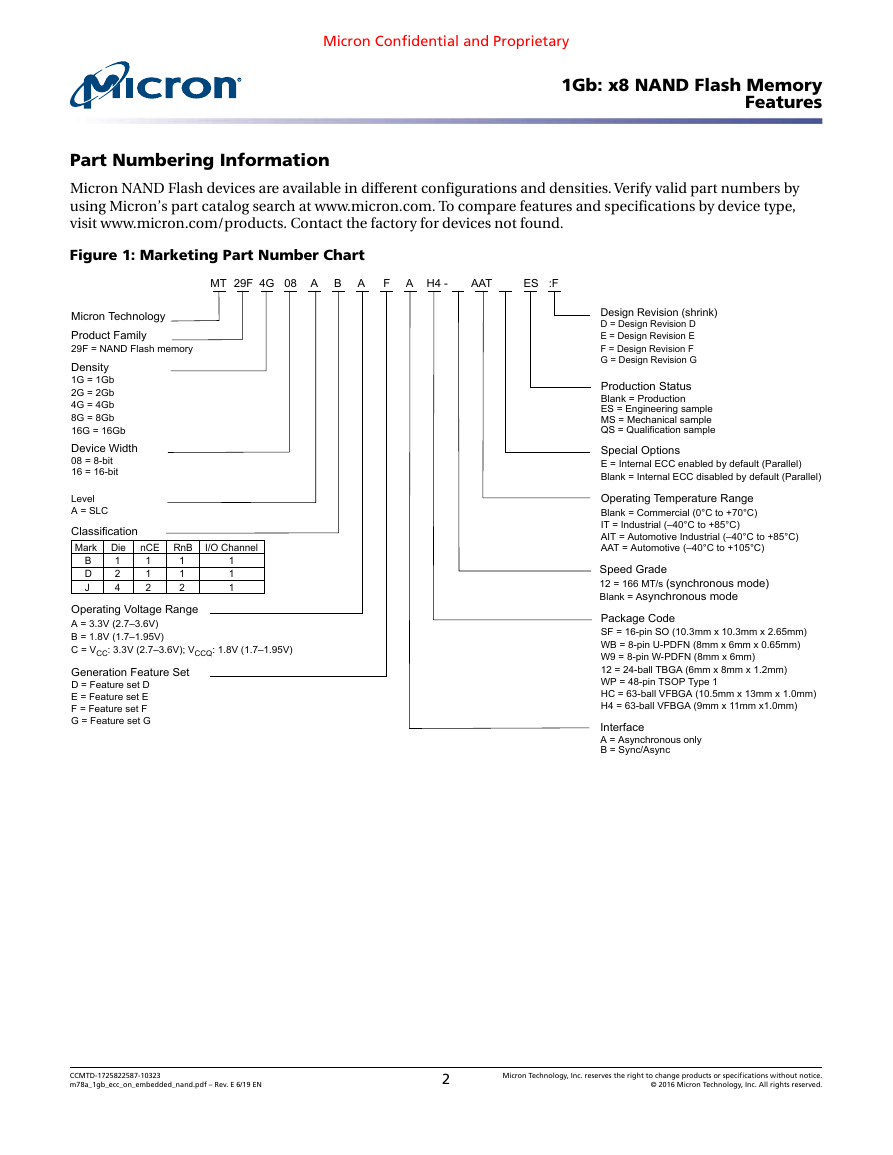

Part Numbering Information

Micron NAND Flash devices are available in different configurations and densities. Verify valid part numbers by

using Micron’s part catalog search at www.micron.com. To compare features and specifications by device type,

visit www.micron.com/products. Contact the factory for devices not found.

Figure 1: Marketing Part Number Chart

MT 29F 4G 08 A B A

F A H4 AAT

-

ES

:F

Micron Technology

Product Family

29F = NAND Flash memory

Density

1G = 1Gb

2G = 2Gb

4G = 4Gb

8G = 8Gb

16G = 16Gb

Device Width

08 = 8-bit

16 = 16-bit

Level

A = SLC

Classification

Mark

B

D

J

Die

1

2

4

nCE RnB I/O Channel

1

1

2

1

1

1

1

1

2

Operating Voltage Range

A = 3.3V (2.7–3.6V)

B = 1.8V (1.7–1.95V)

C = VCC: 3.3V (2.7–3.6V); VCCQ: 1.8V (1.7–1.95V)

Generation Feature Set

D = Feature set D

E = Feature set E

F = Feature set F

G = Feature set G

Design Revision (shrink)

D = Design Revision D

E = Design Revision E

F = Design Revision F

G = Design Revision G

Production Status

Blank = Production

ES = Engineering sample

MS = Mechanical sample

QS = Qualification sample

Special Options

E = Internal ECC enabled by default (Parallel)

Blank = Internal ECC disabled by default (Parallel)

Operating Temperature Range

Blank = Commercial (0°C to +70°C)

IT = Industrial (–40°C to +85°C)

AIT = Automotive Industrial (–40°C to +85°C)

AAT = Automotive (–40°C to +105°C)

Speed Grade

12 = 166 MT/s (synchronous mode)

Blank = Asynchronous mode

Package Code

SF = 16-pin SO (10.3mm x 10.3mm x 2.65mm)

WB = 8-pin U-PDFN (8mm x 6mm x 0.65mm)

W9 = 8-pin W-PDFN (8mm x 6mm)

12 = 24-ball TBGA (6mm x 8mm x 1.2mm)

WP = 48-pin TSOP Type 1

HC = 63-ball VFBGA (10.5mm x 13mm x 1.0mm)

H4 = 63-ball VFBGA (9mm x 11mm x1.0mm)

Interface

A = Asynchronous only

B = Sync/Async

CCMTD-1725822587-10323

m78a_1gb_ecc_on_embedded_nand.pdf – Rev. E 6/19 EN

2

Micron Technology, Inc. reserves the right to change products or specifications without notice.

© 2016 Micron Technology, Inc. All rights reserved.

�

Micron Confidential and Proprietary

1Gb: x8 NAND Flash Memory

Features

Contents

Important Notes and Warnings ......................................................................................................................... 8

General Description ......................................................................................................................................... 9

Signal Descriptions ......................................................................................................................................... 10

Signal Assignments ......................................................................................................................................... 11

Package Dimensions ....................................................................................................................................... 13

Architecture ................................................................................................................................................... 15

Device and Array Organization ........................................................................................................................ 16

Asynchronous Interface Bus Operation ........................................................................................................... 17

Asynchronous Enable/Standby ................................................................................................................... 17

Asynchronous Commands .......................................................................................................................... 17

Asynchronous Addresses ............................................................................................................................ 19

Asynchronous Data Input ........................................................................................................................... 20

Asynchronous Data Output ......................................................................................................................... 21

Write Protect# ............................................................................................................................................ 22

Ready/Busy# .............................................................................................................................................. 22

Device Initialization ....................................................................................................................................... 26

Power Cycle Requirements .............................................................................................................................. 27

Command Definitions .................................................................................................................................... 28

Reset Operations ............................................................................................................................................ 30

RESET (FFh) ............................................................................................................................................... 30

Identification Operations ................................................................................................................................ 31

READ ID (90h) ............................................................................................................................................ 31

READ ID Parameter Tables .............................................................................................................................. 32

READ PARAMETER PAGE (ECh) ...................................................................................................................... 34

Parameter Page Data Structure Tables ............................................................................................................. 35

READ UNIQUE ID (EDh) ................................................................................................................................ 37

Feature Operations ......................................................................................................................................... 38

SET FEATURES (EFh) .................................................................................................................................. 38

GET FEATURES (EEh) ................................................................................................................................. 39

Status Operations ........................................................................................................................................... 42

READ STATUS (70h) ................................................................................................................................... 43

READ STATUS ENHANCED (78h) ................................................................................................................ 43

Column Address Operations ........................................................................................................................... 45

RANDOM DATA READ (05h-E0h) ................................................................................................................ 45

RANDOM DATA INPUT (85h) ...................................................................................................................... 46

PROGRAM FOR INTERNAL DATA INPUT (85h) ........................................................................................... 47

Read Operations ............................................................................................................................................. 48

READ MODE (00h) ..................................................................................................................................... 49

READ PAGE (00h-30h) ................................................................................................................................ 49

READ PAGE CACHE SEQUENTIAL (31h) ...................................................................................................... 50

READ PAGE CACHE RANDOM (00h-31h) .................................................................................................... 50

READ PAGE CACHE LAST (3Fh) .................................................................................................................. 51

Program Operations ....................................................................................................................................... 53

PROGRAM PAGE (80h-10h) ......................................................................................................................... 53

PROGRAM PAGE CACHE (80h-15h) ............................................................................................................. 54

Erase Operations ............................................................................................................................................ 56

ERASE BLOCK (60h-D0h) ............................................................................................................................ 56

Internal Data Move Operations ....................................................................................................................... 57

READ FOR INTERNAL DATA MOVE (00h-35h) ............................................................................................. 57

PROGRAM FOR INTERNAL DATA MOVE (85h–10h) ..................................................................................... 58

CCMTD-1725822587-10323

m78a_1gb_ecc_on_embedded_nand.pdf – Rev. E 6/19 EN

3

Micron Technology, Inc. reserves the right to change products or specifications without notice.

© 2016 Micron Technology, Inc. All rights reserved.

�

Micron Confidential and Proprietary

1Gb: x8 NAND Flash Memory

Features

Block Lock Feature ......................................................................................................................................... 60

WP# and Block Lock ................................................................................................................................... 60

UNLOCK (23h-24h) .................................................................................................................................... 60

LOCK (2Ah) ................................................................................................................................................ 62

LOCK TIGHT (2Ch) ..................................................................................................................................... 63

BLOCK LOCK READ STATUS (7Ah) .............................................................................................................. 64

PROTECT Command .................................................................................................................................. 65

PROTECTION Command Details ................................................................................................................ 66

One-Time Programmable (OTP) Operations .................................................................................................... 67

Legacy OTP Commands .............................................................................................................................. 67

OTP DATA PROGRAM (80h-10h) ................................................................................................................. 67

RANDOM DATA INPUT (85h) ...................................................................................................................... 68

OTP DATA PROTECT (80h-10) ..................................................................................................................... 69

OTP DATA READ (00h-30h) ......................................................................................................................... 70

ECC Protection ............................................................................................................................................... 72

Error Management ......................................................................................................................................... 74

Electrical Specifications .................................................................................................................................. 75

Electrical Specifications – DC Characteristics and Operating Conditions ........................................................... 77

Electrical Specifications – AC Characteristics and Operating Conditions ........................................................... 79

Electrical Specifications – Program/Erase Characteristics ................................................................................. 82

Asynchronous Interface Timing Diagrams ....................................................................................................... 83

Revision History ............................................................................................................................................. 93

Rev. E – 6/19 ............................................................................................................................................... 93

Rev. D – 3/19 .............................................................................................................................................. 93

Rev. C – 1/19 ............................................................................................................................................... 93

Rev. B – 5/18 ............................................................................................................................................... 93

Rev. A – 2/16 ............................................................................................................................................... 93

CCMTD-1725822587-10323

m78a_1gb_ecc_on_embedded_nand.pdf – Rev. E 6/19 EN

4

Micron Technology, Inc. reserves the right to change products or specifications without notice.

© 2016 Micron Technology, Inc. All rights reserved.

�

Micron Confidential and Proprietary

1Gb: x8 NAND Flash Memory

Features

List of Figures

Figure 1: Marketing Part Number Chart ............................................................................................................ 2

Figure 2: 48-Pin TSOP – Type 1, CPL (Top View) .............................................................................................. 11

Figure 3: 63-Ball VFBGA, x8 (Balls Down, Top View) ........................................................................................ 12

Figure 4: 48-Pin TSOP – Type 1, CPL (WP) ...................................................................................................... 13

Figure 5: 63-Ball VFBGA (H4) 9mm x 11mm ................................................................................................... 14

Figure 6: NAND Flash Die (LUN) Functional Block Diagram ............................................................................ 15

Figure 7: Array Organization .......................................................................................................................... 16

Figure 8: Asynchronous Command Latch Cycle .............................................................................................. 18

Figure 9: Asynchronous Address Latch Cycle .................................................................................................. 19

Figure 10: Asynchronous Data Input Cycles .................................................................................................... 20

Figure 11: Asynchronous Data Output Cycles ................................................................................................. 21

Figure 12: Asynchronous Data Output Cycles (EDO Mode) ............................................................................. 22

Figure 13: READ/BUSY# Open Drain .............................................................................................................. 23

Figure 14: tFall and tRise (3.3V VCC) ................................................................................................................ 24

Figure 15: IOL vs. Rp (VCC = 3.3V VCC) .............................................................................................................. 24

Figure 16: TC vs. Rp ....................................................................................................................................... 25

Figure 17: R/B# Power-On Behavior ............................................................................................................... 26

Figure 18: RESET (FFh) Operation .................................................................................................................. 30

Figure 19: READ ID (90h) with 00h Address Operation .................................................................................... 31

Figure 20: READ ID (90h) with 20h Address Operation .................................................................................... 31

Figure 21: READ PARAMETER (ECh) Operation .............................................................................................. 34

Figure 22: READ UNIQUE ID (EDh) Operation ............................................................................................... 37

Figure 23: SET FEATURES (EFh) Operation .................................................................................................... 39

Figure 24: GET FEATURES (EEh) Operation .................................................................................................... 39

Figure 25: READ STATUS (70h) Operation ...................................................................................................... 43

Figure 26: READ STATUS ENHANCED (78h) Operation ................................................................................... 44

Figure 27: RANDOM DATA READ (05h-E0h) Operation ................................................................................... 45

Figure 28: RANDOM DATA INPUT (85h) Operation ........................................................................................ 46

Figure 29: PROGRAM FOR INTERNAL DATA INPUT (85h) Operation .............................................................. 47

Figure 30: READ PAGE (00h-30h) Operation ................................................................................................... 49

Figure 31: READ PAGE (00h-30h) Operation with Internal ECC Enabled .......................................................... 50

Figure 32: READ PAGE CACHE SEQUENTIAL (31h) Operation ......................................................................... 50

Figure 33: READ PAGE CACHE RANDOM (00h-31h) Operation ....................................................................... 51

Figure 34: READ PAGE CACHE LAST (3Fh) Operation ..................................................................................... 52

Figure 35: PROGRAM PAGE (80h-10h) Operation ............................................................................................ 54

Figure 36: PROGRAM PAGE CACHE (80h–15h) Operation (Start) ..................................................................... 55

Figure 37: PROGRAM PAGE CACHE (80h–15h) Operation (End) ...................................................................... 55

Figure 38: ERASE BLOCK (60h-D0h) Operation .............................................................................................. 56

Figure 39: READ FOR INTERNAL DATA MOVE (00h-35h) Operation ................................................................ 57

Figure 40: READ FOR INTERNAL DATA MOVE (00h–35h) with RANDOM DATA READ (05h–E0h) ..................... 58

Figure 41: INTERNAL DATA MOVE (85h-10h) with Internal ECC Enabled ........................................................ 58

Figure 42: INTERNAL DATA MOVE (85h-10h) with RANDOM DATA INPUT with Internal ECC Enabled ............ 58

Figure 43: PROGRAM FOR INTERNAL DATA MOVE (85h–10h) Operation ........................................................ 59

Figure 44: PROGRAM FOR INTERNAL DATA MOVE (85h-10h) with RANDOM DATA INPUT (85h) .................... 59

Figure 45: Flash Array Protected: Invert Area Bit = 0 ........................................................................................ 61

Figure 46: Flash Array Protected: Invert Area Bit = 1 ........................................................................................ 61

Figure 47: UNLOCK Operation ....................................................................................................................... 62

Figure 48: LOCK Operation ............................................................................................................................ 62

Figure 49: LOCK TIGHT Operation ................................................................................................................. 63

Figure 50: PROGRAM/ERASE Issued to Locked Block ...................................................................................... 63

CCMTD-1725822587-10323

m78a_1gb_ecc_on_embedded_nand.pdf – Rev. E 6/19 EN

5

Micron Technology, Inc. reserves the right to change products or specifications without notice.

© 2016 Micron Technology, Inc. All rights reserved.

�

Micron Confidential and Proprietary

1Gb: x8 NAND Flash Memory

Features

Figure 51: BLOCK LOCK READ STATUS .......................................................................................................... 64

Figure 52: BLOCK LOCK Flowchart ................................................................................................................ 65

Figure 53: Address and Command Cycles ....................................................................................................... 66

Figure 54: OTP DATA PROGRAM (After Entering OTP Operation Mode) ........................................................... 68

Figure 55: OTP DATA PROGRAM Operation with RANDOM DATA INPUT (After Entering OTP Operation Mode) ... 69

Figure 56: OTP DATA PROTECT Operation (After Entering OTP Protect Mode) ................................................. 70

Figure 57: OTP DATA READ ........................................................................................................................... 71

Figure 58: OTP DATA READ with RANDOM DATA READ Operation ................................................................. 71

Figure 59: RESET Operation ........................................................................................................................... 83

Figure 60: READ STATUS Cycle ...................................................................................................................... 83

Figure 61: READ STATUS ENHANCED Cycle ................................................................................................... 84

Figure 62: READ PARAMETER PAGE .............................................................................................................. 84

Figure 63: READ PAGE ................................................................................................................................... 85

Figure 64: READ PAGE Operation with CE# “Don’t Care” ................................................................................ 86

Figure 65: RANDOM DATA READ ................................................................................................................... 86

Figure 66: READ PAGE CACHE SEQUENTIAL ................................................................................................. 87

Figure 67: READ PAGE CACHE RANDOM ....................................................................................................... 88

Figure 68: READ ID Operation ....................................................................................................................... 89

Figure 69: PROGRAM PAGE Operation ........................................................................................................... 89

Figure 70: PROGRAM PAGE Operation with CE# “Don’t Care” ......................................................................... 90

Figure 71: PROGRAM PAGE Operation with RANDOM DATA INPUT ............................................................... 90

Figure 72: PROGRAM PAGE CACHE ............................................................................................................... 91

Figure 73: PROGRAM PAGE CACHE Ending on 15h ......................................................................................... 91

Figure 74: INTERNAL DATA MOVE ................................................................................................................ 92

Figure 75: ERASE BLOCK Operation ............................................................................................................... 92

CCMTD-1725822587-10323

m78a_1gb_ecc_on_embedded_nand.pdf – Rev. E 6/19 EN

6

Micron Technology, Inc. reserves the right to change products or specifications without notice.

© 2016 Micron Technology, Inc. All rights reserved.

�

Micron Confidential and Proprietary

1Gb: x8 NAND Flash Memory

Features

List of Tables

Table 1: Signal Definitions ............................................................................................................................. 10

Table 2: Array Addressing .............................................................................................................................. 16

Table 3: Asynchronous Interface Mode Selection ............................................................................................ 17

Table 4: Power Cycle Requirements ................................................................................................................ 27

Table 5: Command Set .................................................................................................................................. 28

Table 6: READ ID Parameters for Address 00h ................................................................................................. 32

Table 7: READ ID Parameters for Address 20h ................................................................................................. 32

Table 8: Parameter Page Data Structure .......................................................................................................... 35

Table 9: Feature Address Definitions .............................................................................................................. 38

Table 10: Feature Address 90h – Array Operation Mode ................................................................................... 38

Table 11: Feature Addresses 01h: Timing Mode ............................................................................................... 39

Table 12: Feature Addresses 80h: Programmable I/O Drive Strength ................................................................ 41

Table 13: Feature Addresses 81h: Programmable R/B# Pull-Down Strength ...................................................... 41

Table 14: Status Register Definition ................................................................................................................ 42

Table 15: Block Lock Address Cycle Assignments ............................................................................................ 61

Table 16: Block Lock Status Register Bit Definitions ........................................................................................ 64

Table 17: Spare Area Mapping (x8) ................................................................................................................. 72

Table 18: ECC Status ...................................................................................................................................... 73

Table 19: Error Management Details .............................................................................................................. 74

Table 20: Absolute Maximum Ratings ............................................................................................................. 75

Table 21: Recommended Operating Conditions .............................................................................................. 75

Table 22: Valid Blocks .................................................................................................................................... 75

Table 23: Capacitance .................................................................................................................................... 76

Table 24: Test Conditions ............................................................................................................................... 76

Table 25: DC Characteristics and Operating Conditions (3.3V) ........................................................................ 77

Table 26: DC Characteristics and Operating Conditions (1.8V) ........................................................................ 78

Table 27: AC Characteristics: Command, Data, and Address Input (3.3V) ......................................................... 79

Table 28: AC Characteristics: Command, Data, and Address Input (1.8V) ......................................................... 79

Table 29: AC Characteristics: Normal Operation (3.3V) ................................................................................... 80

Table 30: AC Characteristics: Normal Operation (1.8V) ................................................................................... 80

Table 31: Program/Erase Characteristics ........................................................................................................ 82

CCMTD-1725822587-10323

m78a_1gb_ecc_on_embedded_nand.pdf – Rev. E 6/19 EN

7

Micron Technology, Inc. reserves the right to change products or specifications without notice.

© 2016 Micron Technology, Inc. All rights reserved.

�

Micron Confidential and Proprietary

1Gb: x8 NAND Flash Memory

Important Notes and Warnings

Important Notes and Warnings

Micron Technology, Inc. ("Micron") reserves the right to make changes to information published in this document,

including without limitation specifications and product descriptions. This document supersedes and replaces all

information supplied prior to the publication hereof. You may not rely on any information set forth in this docu-

ment if you obtain the product described herein from any unauthorized distributor or other source not authorized

by Micron.

Automotive Applications. Products are not designed or intended for use in automotive applications unless specifi-

cally designated by Micron as automotive-grade by their respective data sheets. Distributor and customer/distrib-

utor shall assume the sole risk and liability for and shall indemnify and hold Micron harmless against all claims,

costs, damages, and expenses and reasonable attorneys' fees arising out of, directly or indirectly, any claim of

product liability, personal injury, death, or property damage resulting directly or indirectly from any use of non-

automotive-grade products in automotive applications. Customer/distributor shall ensure that the terms and con-

ditions of sale between customer/distributor and any customer of distributor/customer (1) state that Micron

products are not designed or intended for use in automotive applications unless specifically designated by Micron

as automotive-grade by their respective data sheets and (2) require such customer of distributor/customer to in-

demnify and hold Micron harmless against all claims, costs, damages, and expenses and reasonable attorneys'

fees arising out of, directly or indirectly, any claim of product liability, personal injury, death, or property damage

resulting from any use of non-automotive-grade products in automotive applications.

Critical Applications. Products are not authorized for use in applications in which failure of the Micron compo-

nent could result, directly or indirectly in death, personal injury, or severe property or environmental damage

("Critical Applications"). Customer must protect against death, personal injury, and severe property and environ-

mental damage by incorporating safety design measures into customer's applications to ensure that failure of the

Micron component will not result in such harms. Should customer or distributor purchase, use, or sell any Micron

component for any critical application, customer and distributor shall indemnify and hold harmless Micron and

its subsidiaries, subcontractors, and affiliates and the directors, officers, and employees of each against all claims,

costs, damages, and expenses and reasonable attorneys' fees arising out of, directly or indirectly, any claim of

product liability, personal injury, or death arising in any way out of such critical application, whether or not Mi-

cron or its subsidiaries, subcontractors, or affiliates were negligent in the design, manufacture, or warning of the

Micron product.

Customer Responsibility. Customers are responsible for the design, manufacture, and operation of their systems,

applications, and products using Micron products. ALL SEMICONDUCTOR PRODUCTS HAVE INHERENT FAIL-

URE RATES AND LIMITED USEFUL LIVES. IT IS THE CUSTOMER'S SOLE RESPONSIBILITY TO DETERMINE

WHETHER THE MICRON PRODUCT IS SUITABLE AND FIT FOR THE CUSTOMER'S SYSTEM, APPLICATION, OR

PRODUCT. Customers must ensure that adequate design, manufacturing, and operating safeguards are included

in customer's applications and products to eliminate the risk that personal injury, death, or severe property or en-

vironmental damages will result from failure of any semiconductor component.

Limited Warranty. In no event shall Micron be liable for any indirect, incidental, punitive, special or consequential

damages (including without limitation lost profits, lost savings, business interruption, costs related to the removal

or replacement of any products or rework charges) whether or not such damages are based on tort, warranty,

breach of contract or other legal theory, unless explicitly stated in a written agreement executed by Micron's duly

authorized representative.

CCMTD-1725822587-10323

m78a_1gb_ecc_on_embedded_nand.pdf – Rev. E 6/19 EN

8

Micron Technology, Inc. reserves the right to change products or specifications without notice.

© 2016 Micron Technology, Inc. All rights reserved.

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc