FPGA 系统设计实验报告

《使用 Quartus II 配置 Nios 软核》

班

姓

学

级

名

号

指导老师

日

期

13 电 科

张 书 安

1328401006

2017 年 11 月 30 日

1

�

一 实验目的

1.熟悉用 Quartus II 开发 SOPC 的基本流程。

2.熟悉用 SOPC Builder 进行 Nios II CPU 开发的基本流程。

3.熟悉用 Nios II IDE 进行 C 语言编译、下载的基本过程。

4.掌握整个 Nios II 集成开发环境。

二 硬件需求

1.FPGA 开发板。

2.并口/USB 下载电缆一条。

三 实验原理

设计本实验的目的主要是为了让学生对 SOPC 有一个感性的认识,了解整个开发过程,

并熟练掌握整个 Nios II 集成开发环境的应用。

SOPC 是 system on a programmable chip 的缩写,顾名思义就是把一个系统集成在单

片可编程芯片中。一个最小系统应该包括中央处理单元(CPU)、随机存储器(RAM)和 Flash

ROM(存储代码、数据等),稍微复杂点的系统至少应该包括 UART、DMA、Timer、中断管理

模块以及 GPIO 等。

早在 2002 年的时候,Altera 公司就基于 SOC 的设计思想,推出了其第一款 32 位 RISC CPU

软核——Nios,那时的 Nios CPU 功能简单,执行效率低下且不支持在线调试,所以并未得

到很大的推广。在 Nios CPU 基础上,Altera 公司又于 2005 年推出了其第二代 32 位 RISC CPU

——Nios II。与 Nios CPU 相比,Nios II CPU 在性能方面得到了质的提升,指令执行速度

快,执行效率高,且支持 JTAG 在线调试。

Nios II CPU 的开发流程与 Nios CPU 基本一致,唯一不同的就是 Nios CPU 的软件开发

是在 Nios SDK Shell 下进行,而 Nios II CPU 则是在 Nios II IDE 集成环境下开发。其基

本开发流程依旧为:

(1) 在 Quartus II 中新建一个工程(硬件)。

(2) 在 SOPC Builder 中根据自己的需要加入各种 IP 核。

(3) 利用 SOPC Builder 产生 Quartus II 能够识别的文件。

(4) 在(1)中新建的工程中加入(3)中生成的文件。

(5) 加入输入、输出以及双向端口,并根据需要对其命名。

(6) 对(5)中命名的输入、输出核双向端口根据选定的 FPGA 进行引脚分配。

(7) 编译工程。

(8) 下载编辑代码到 FPGA。

2

�

(9) 利用 Nios II IDE 新建另一个工程(软件)。

(10) 根据(2)中的资源,编写项目需要的代码。

(11) 编译、下载并调试,查看运行结果,直到正确。

(12) 如果需要,将(11)中生成的代码下载到代码 Flash 中。

说简单一点,实际上 SOPC 的开发流程是一个软硬件协同开发的过程,首先根据硬件需

要,决定使用何种性能的 CPU,加入系统需要的外设(SRAM、Flash、Timer、UART、Timer

和 GPIO 等),此时一个基本的硬件系统便搭建起来了。利用专用工具,对这些象积木一样搭

起来的系统进行编译,产生 FPGA 软件可以识别的文件,然后再用 FPGA 专用软件对这些文件

进行编译,产生满足加载 FPGA 的代码,这样一个硬件平台就全部完成了。接下来工作就是

软件开发,在软件集成开发环境中编写代码,编译后,下载到 CPU 中进行调试。整个过程中

软件工作量相对较大。下面对 Altera 的软件开发环境作一些简要说明。

Nios II CPU 使用的软件开发环境叫 Nios II IDE,它是 Nios II 系列嵌入式处理器的

基本软件开发工具。所有软件开发任务都可以 Nios II IDE 下完成,包括编辑、编译和调试

程序。Nios II IDE 提供了一个统一的开发平台,用于所有 Nios II 处理器系统。仅仅通过

一台 PC 机、一片 Altera 的 FPGA 以及一根 JTAG 下载电缆,软件开发人员就能够往 Nios II

处理器系统写入程序以及和 Nios II 处理器系统进行通讯。

Nios II IDE 基于开放式的、可扩展 Eclipse IDE project 工程以及 Eclipse C/C++ 开

发工具(CDT)工程。

Nios II IDE 为软件开发提供四个主要的功能:

(1)工程管理器

Nios II IDE 提供多个工程管理任务,加快嵌入式应用程序的开发进度。

新工程向导——Nios II IDE 推出了一个新工程向导,用于自动建立 C/C++应用程序工

程和系统库工程。采用新工程向导,能够轻松地在 Nios II IDE 中创建新工程。

软件工程模板——除了工程创建向导,Nios II IDE 还以工程模板的形式提供了软件代

码实例,帮助软件工程师尽可能快速地推出可运行的系统。

(2)编辑器和编译器

Altera Nios II IDE 提供了一个全功能的源代码编辑器和 C/C++编译器和文本编辑器

——Nios II IDE 文本编辑器是一个成熟的全功能源文件编辑器。这些功能包括:语法高亮

显示 - C/C++、代码辅助/代码协助完成、全面的搜索工具、文件管理、广泛的在线帮助主

题和教程、引入辅助、快速定位自动纠错、内置调试功能。

C/C++编译器——Nios II IDE 为 GCC 编译器提供了一个图形化用户界面,Nios II IDE

3

�

编译环境使设计 Altera 的 Nios II 处理器软件更容易,它提供了一个易用的按钮式流程,

同时允许开发人员手工设置高级编译选项。

Nios II IDE 编译环境自动地生成一个基于用户特定系统配置(SOPC Builder 生成的

PTF 文件)的 makefile。Nios II IDE 中编译/链接设置的任何改变都会自动映射到这个自

动生成的 makefile 中。这些设置可包括生成存储器初始化文件(MIF)的选项、闪存内容、

仿真器初始化文件(DAT/HEX)以及 profile 总结文件的相关选项。

(3)调试器

Nios II IDE 包含一个强大的、在 GNU 调试器基础之上的软件调试器-GDB。该调试器

提供了许多基本调试功能,以及一些在低成本处理器开发套件中不会经常用到的高级调试功

能。

基本调试功能——Nios II IDE 调试器包含如下的基本调试功能:运行控制、调用堆栈

查看、软件断点、反汇编代码查看、调试信息查看、指令集仿真器。

高级调试 ——除了上述基本调试功能之外,Nios II IDE 调试器还支持以下高级调试

功能:硬件断点调试 ROM 或闪存中的代码、数据触发、指令跟踪。

(4)闪存编程器

使用 Nios II 处理器的设计都在单板上采用了闪存,可以用来存储 FPGA 配置数据和/

或 Nios II 编程数据。Nios II IDE 提供了一个方便的闪存编程方法。任何连接到 FPGA 的

兼容通用闪存接口(CFI)的闪存器件都可以通过 Nios II IDE 闪存编程器来烧写。除 CFI

闪存之外,Nios II IDE 闪存编程器能够对连接到 FPGA 的任何 Altera 串行配置器件进行编

程。

四 实验内容

为了熟悉 SOPC 的基本开发流程,本实验要完成的任务就是设计一个最简单的系统,系

统中包括 Nios II CPU、作为标准输入/输出的 JTAG UART 以及存储执行代码 SRAM。通过 SOPC

Builder 对系统进行编译,然后通过 Quartus II 对系统进行二次编译,并把产生的 FPGA 配

置文件通过 USB 下载电缆下载到实验箱上,这时便完成了本实验中的硬件开发。接下来的工

作是软件协同开发——在 Nios II IDE 中编写一个最简单的 C 代码,对其编译后,通过 USB

下载电缆下载到 FPGA 中执行,执行的结果就是在 Nios II IDE 的 Console 窗口打印一条信

息——“Hello Nios II!”。

五 实验步骤

完成本实验的实验步骤为:

1.打开 Quartus II 17。

4

�

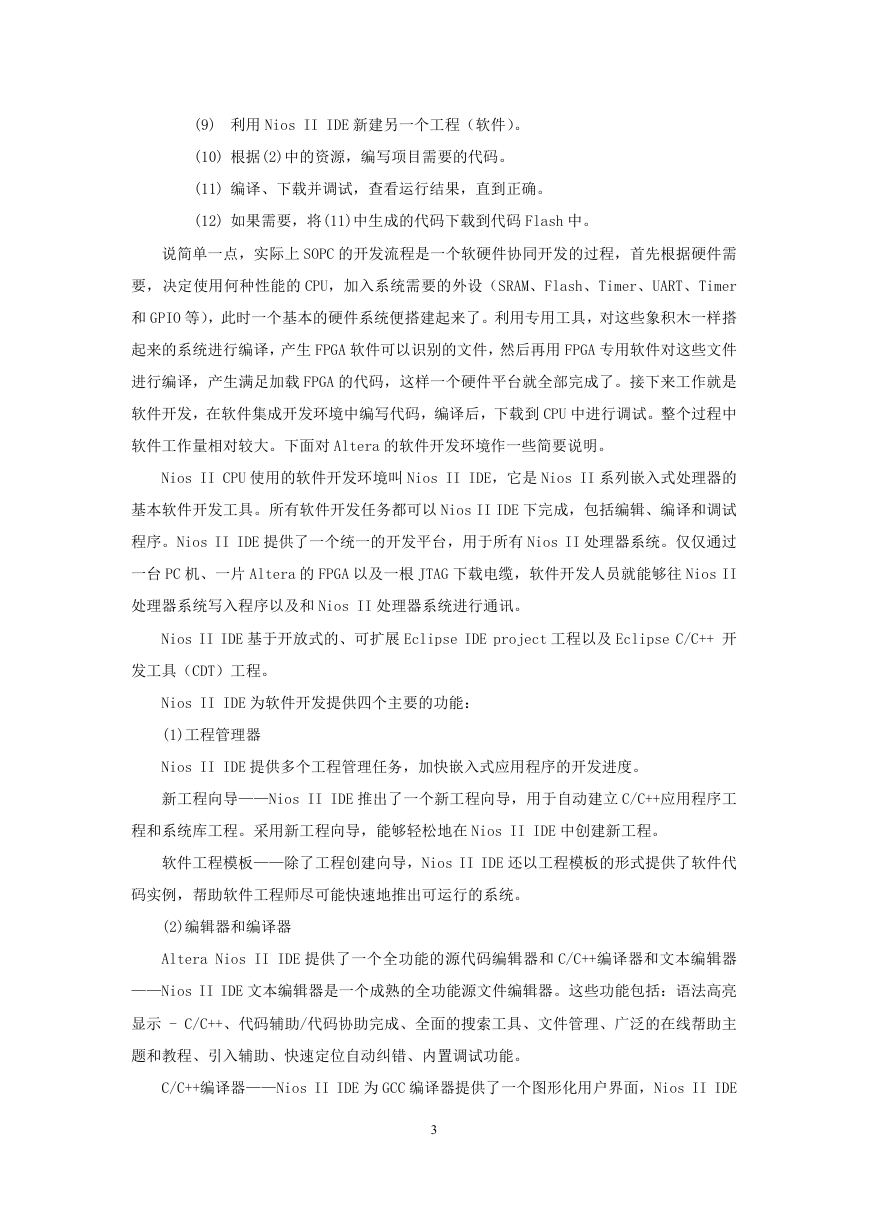

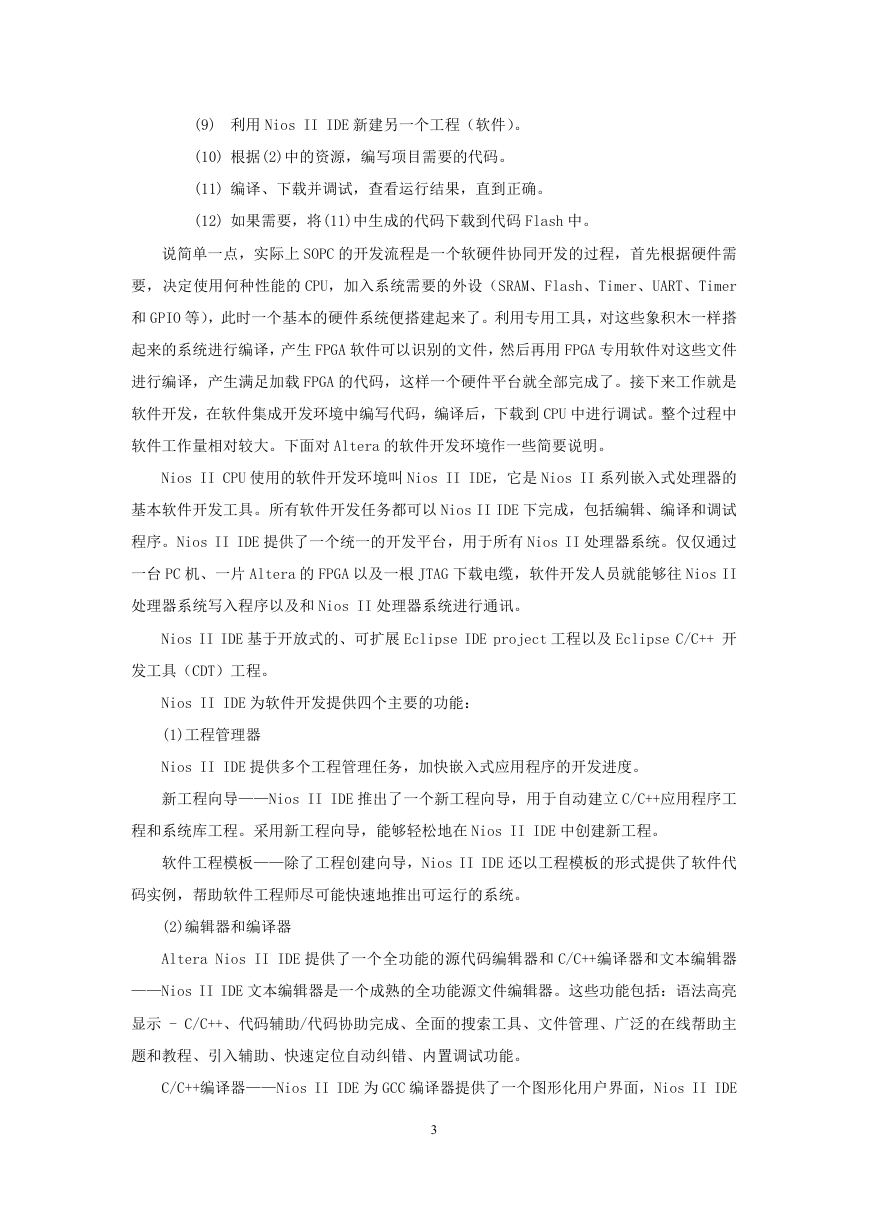

2 . 点 击 File 菜 单 中 的 New Project Wizard, 新 建 一 个 工 程 。 本 实 验 以

D:/Quartus17/projects/hello 文 件 夹 ( 文 件 夹 不 能 含 有 空 格 ) 为 例 , 工 程 名 称 为

hello_nios,如图 1-1 所示。

图 1-1 新建工程

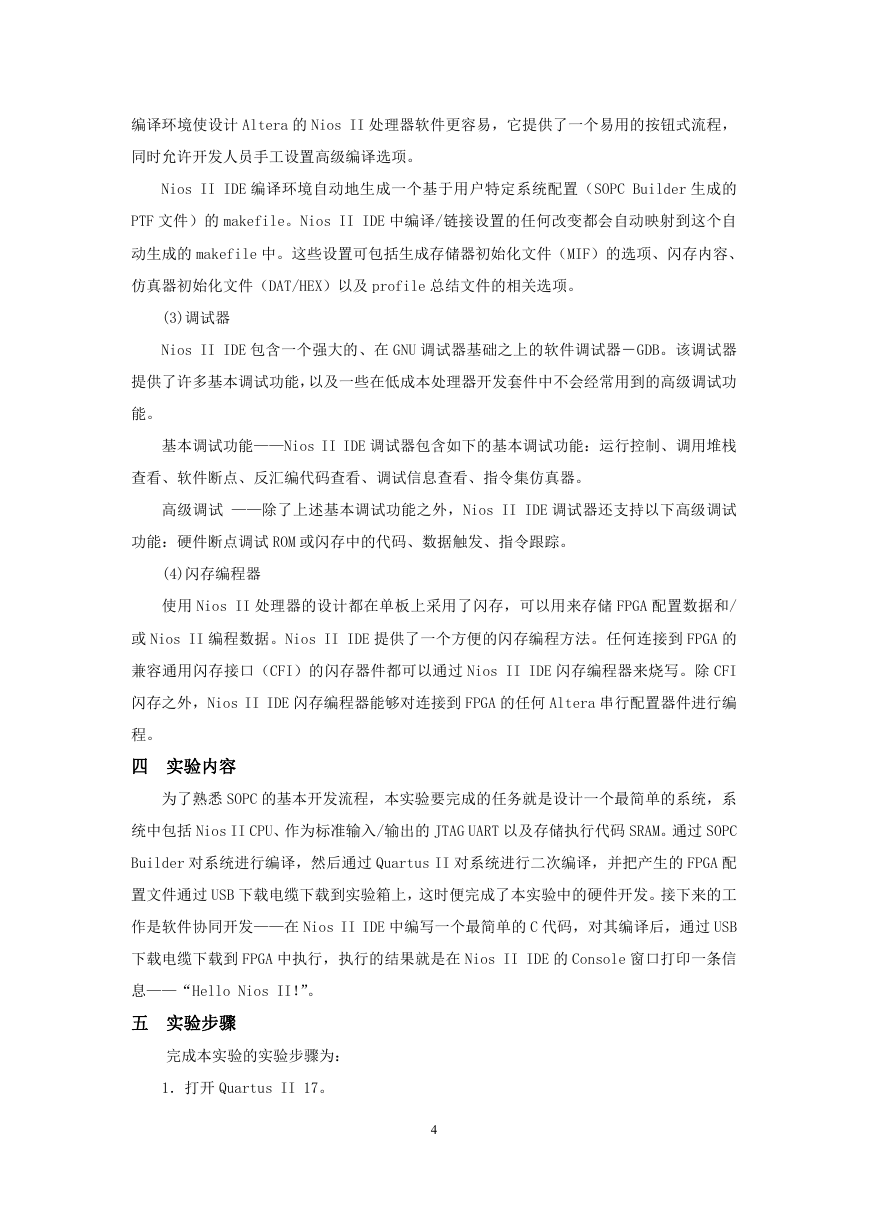

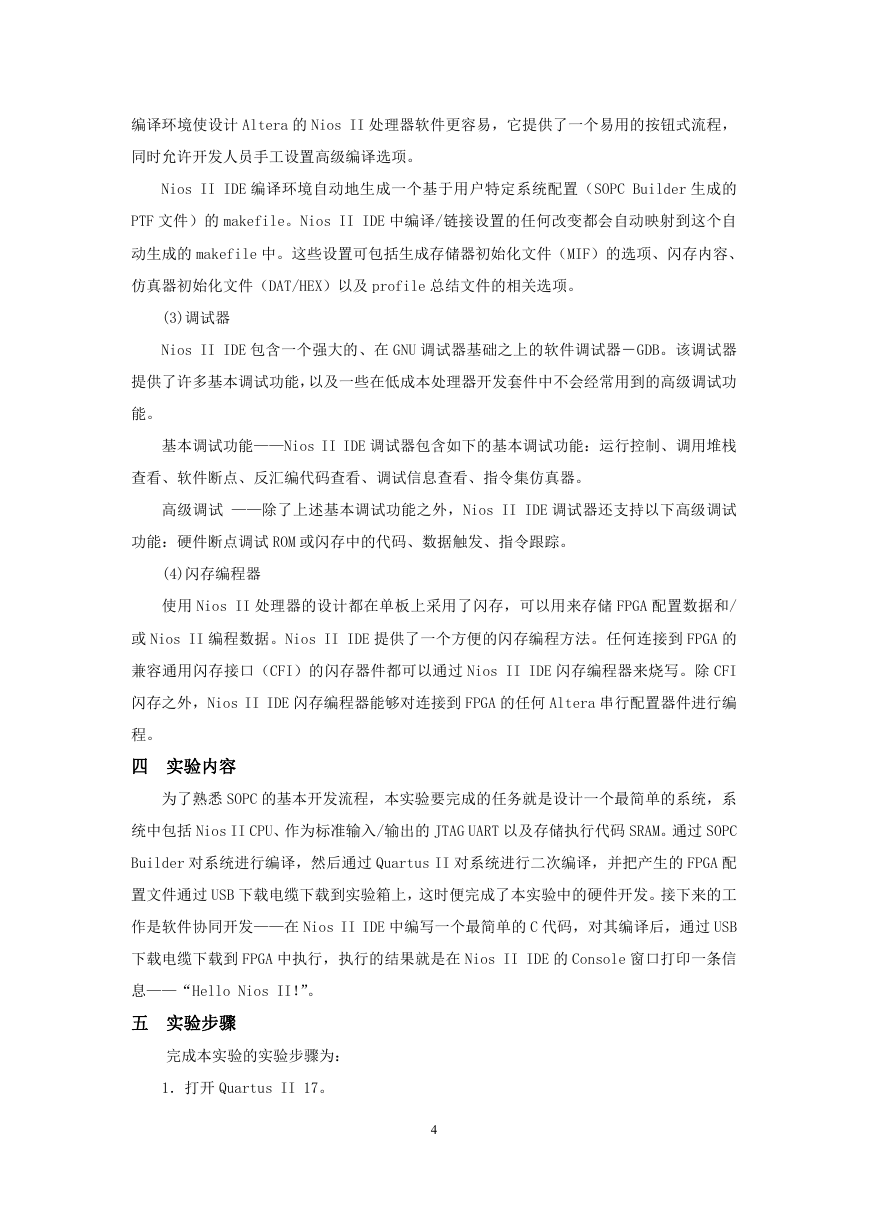

3.点击【Next】按钮,进入到添加工程文件步骤。由于工程全部为空,所以也没有文

件加入,因此直接点击【Next】进入到选择芯片步骤(在 Family 下拉菜单中选择 Cyclone IV

E;在 Filters 中的 Pin Count 下拉菜单中选择 144;在 Speed grade 下拉菜单中选择 8,然

后在 Available devices 中选择 EP4CE6E22C8),如图 1-2 所示。

4.FPGA 选好后,点击【Next】,进入到选择其它 EDA 工具窗口。本实验中需要任何 EDA

图 1-2 选择芯片

5

�

工具,所以直接点击【Next】按钮,然后再点击【Finish】按钮,完成新工程的创建。如图

1-3 所示。

图 1-3 新建的工程界面

5.点击 File菜单中的 New,选择 Block Diagram/Schematic File新建一个原理图文

件。本实验中需要创建的是一个原理图工程文件。如图 1-4 所示。

图 1-4 新建的原理图工程文件界面

6.点击 Tools菜单中的 Qsys(也可点击工具栏图标 ),启动 Qsys 软件。系统已经

默认添加了时钟模块,名称为 clk_0 ,这里选中 clk_0,右击,选择 Rename, 将其名称更

改为 clk。以下再添加任何模块,都要进行类似的名称更改,更改名称的方法类似,就不在

重复叙述了。如图 1-5 所示。

6

�

图 1-5

启动 Qsys 软件

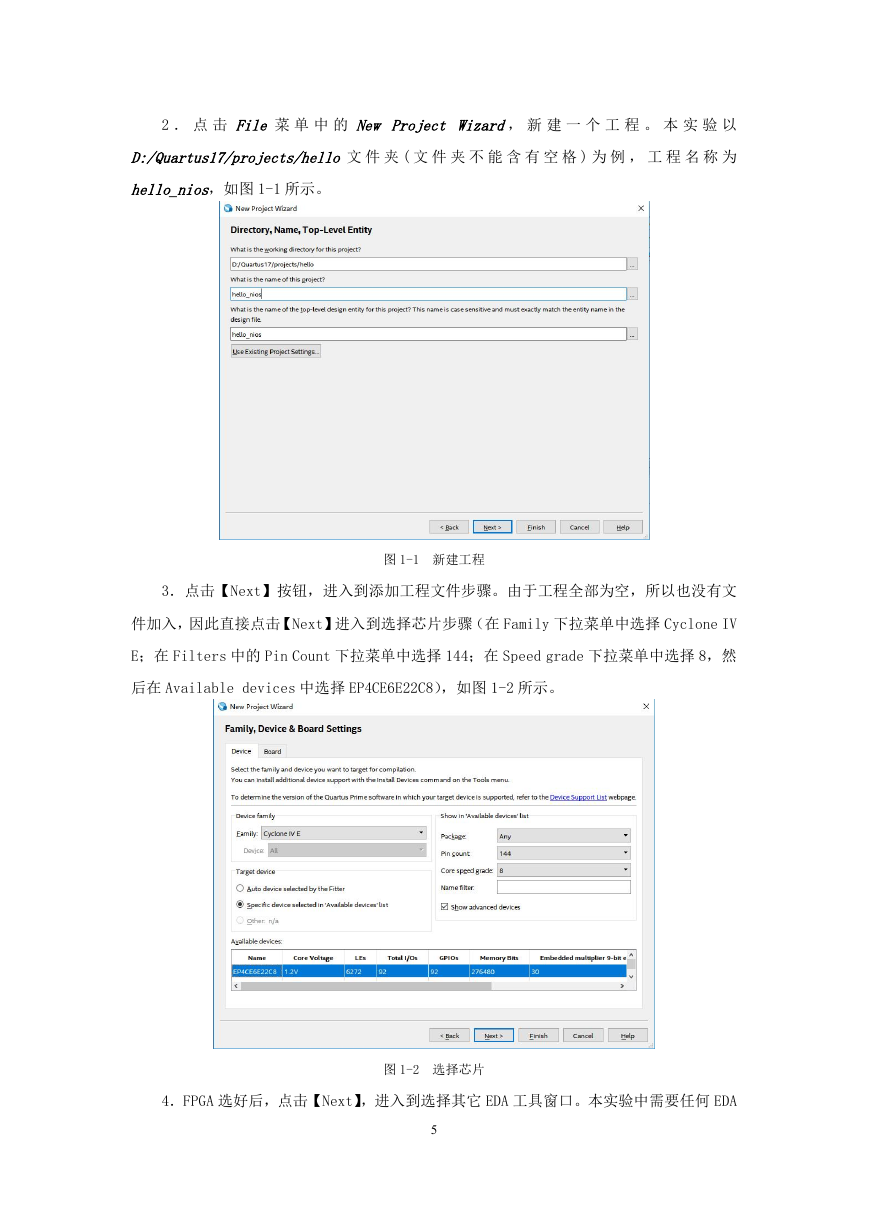

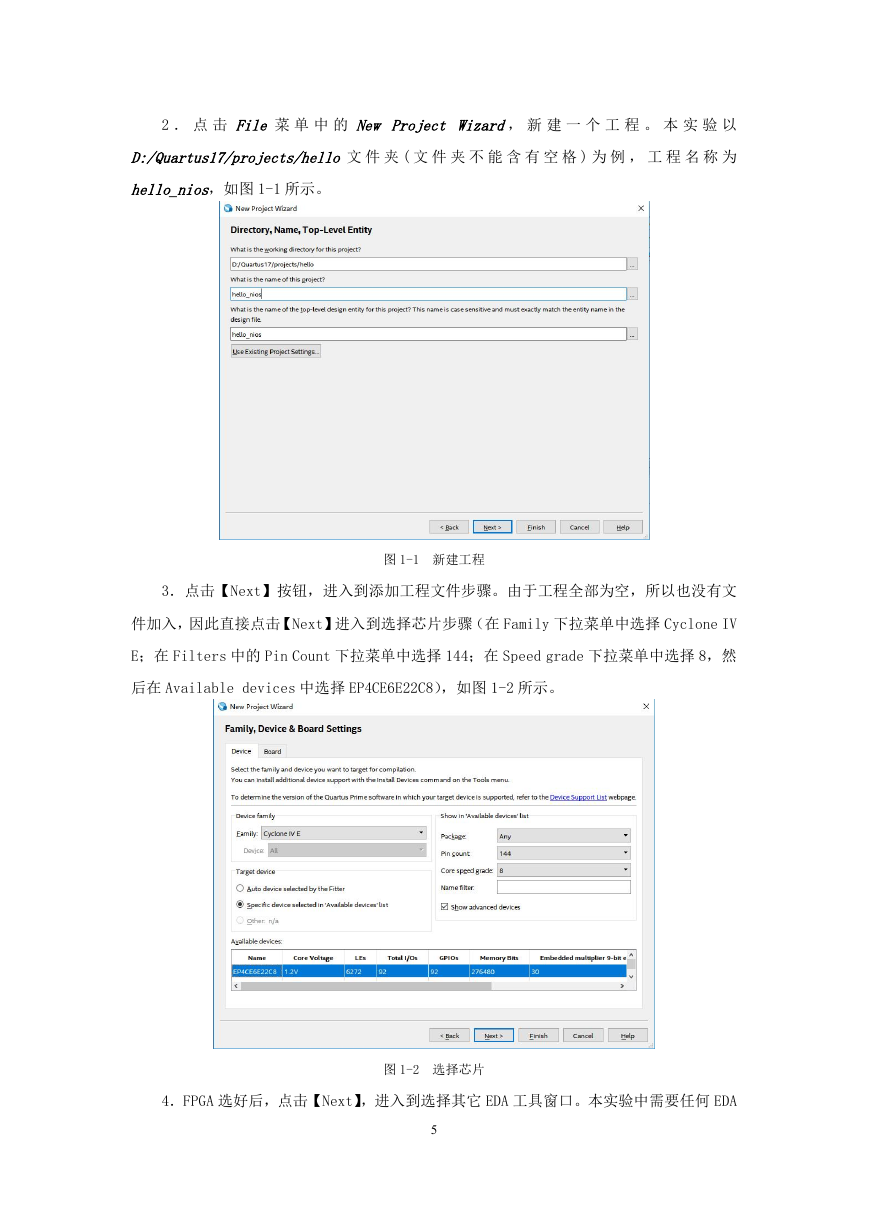

7.加入 Nios II CPU。首先熟悉一下 Qsys 的界面。左面 Component Library, 是系

统提供的元件库,里面有一些构成处理器的常用模块。右面是已经添加到系统的模块,也就

是说,Nios II 软核处理器是可以定制的,根据具体需要来。在 Component Library 中搜

索 Nios II Processor,双击即可进行配置。首先需要选择的是 Nios II 核心的类型。Nios

II 软核的核心共分成三种(quartus 17 中只有两种,省去了 s 型,添加 Nios II(Classic)

Processor 可以选则三种),为 e 型、s 型以及 f 型。e 型核占用的资源最少,功能也最简

单,速度最慢。s 型核占用资源其次,功能和速度较前者都有所提升,f 型核的功能最多,

速度最快,相应的占用资源也最多,选择的时候根据需求和芯片资源来决定,这里选择 e 核。

然后单击 Finish,结束当前配置。此时 SOPC Builder 底部窗口会出现一些红色错误信息,

先不用理会,等其它外设添加结束后,这些错误信息会自动消失。如图 1-6 所示。

图 1-6 设置 Nios II CPU

7

�

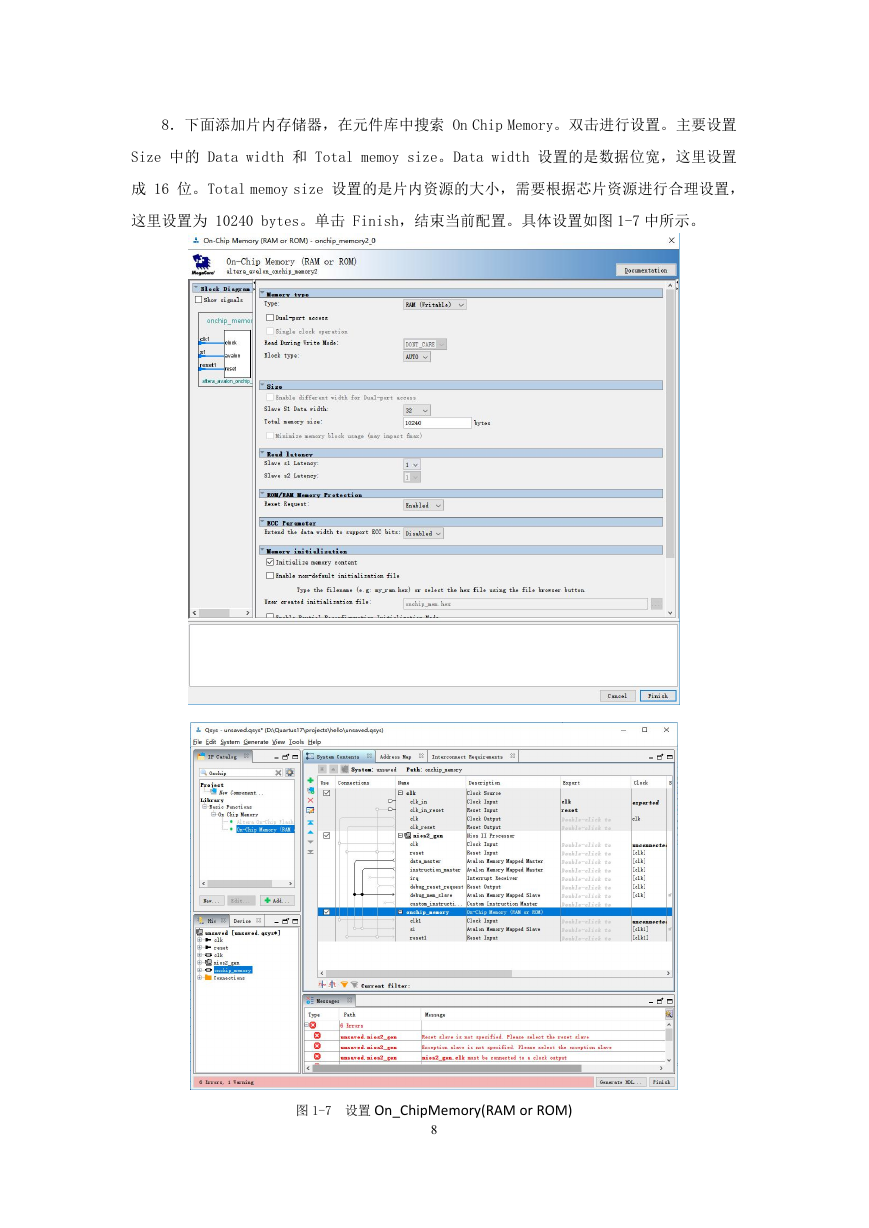

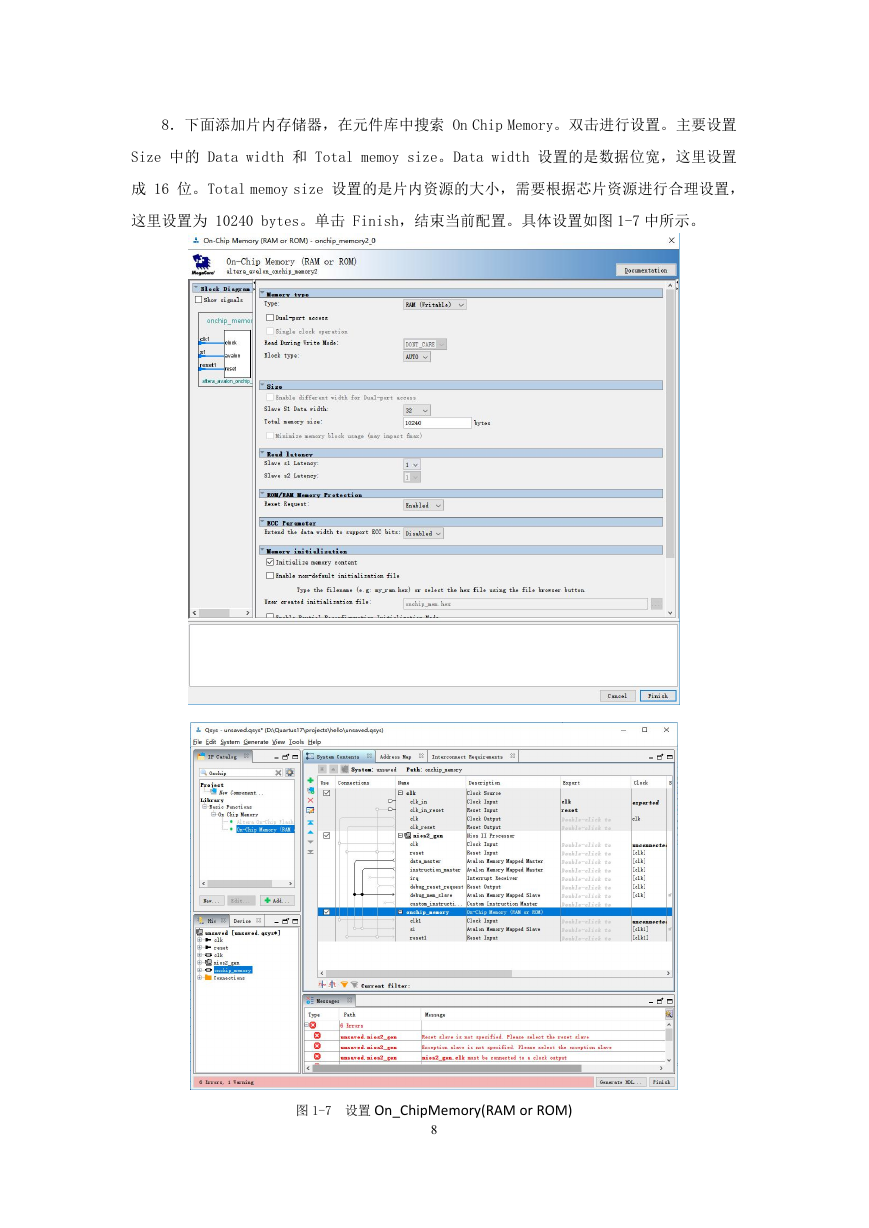

8.下面添加片内存储器,在元件库中搜索 On Chip Memory。双击进行设置。主要设置

Size 中的 Data width 和 Total memoy size。Data width 设置的是数据位宽,这里设置

成 16 位。Total memoy size 设置的是片内资源的大小,需要根据芯片资源进行合理设置,

这里设置为 10240 bytes。单击 Finish,结束当前配置。具体设置如图 1-7 中所示。

图 1-7 设置 On_ChipMemory(RAM or ROM)

8

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc