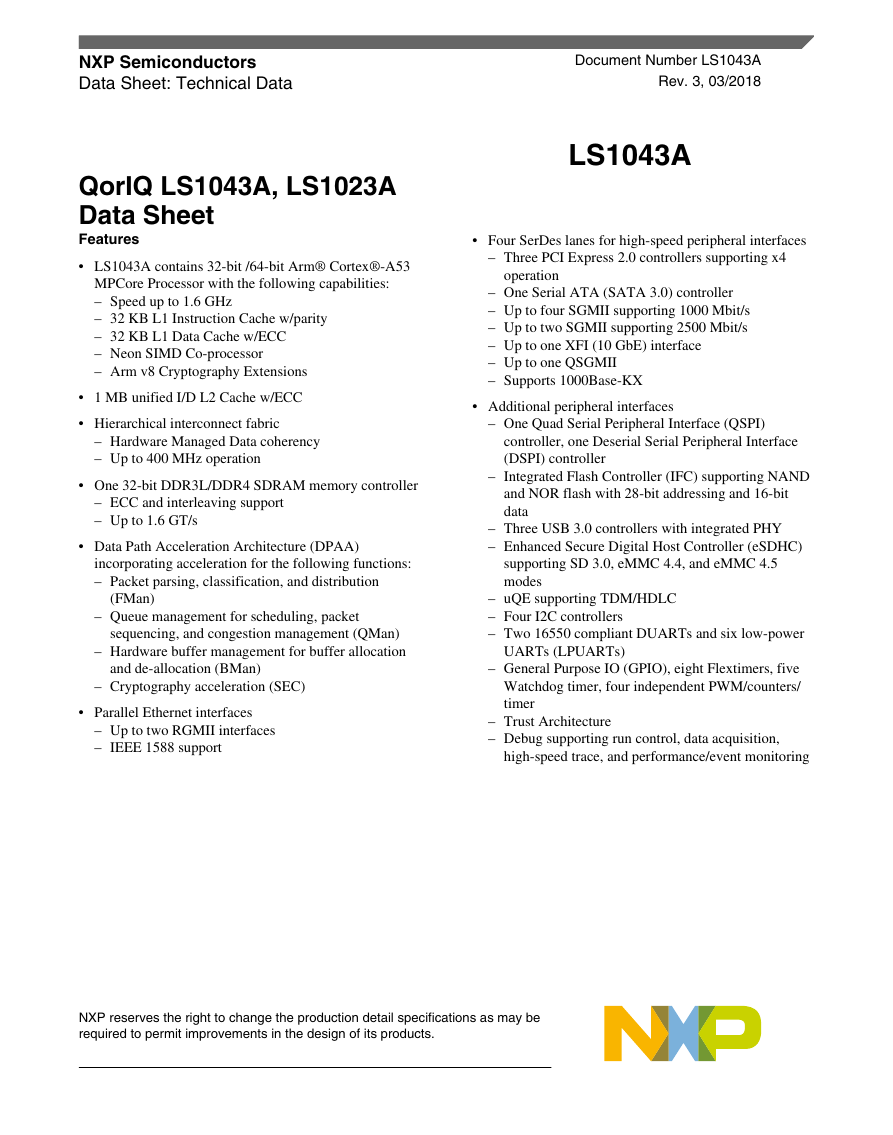

Features

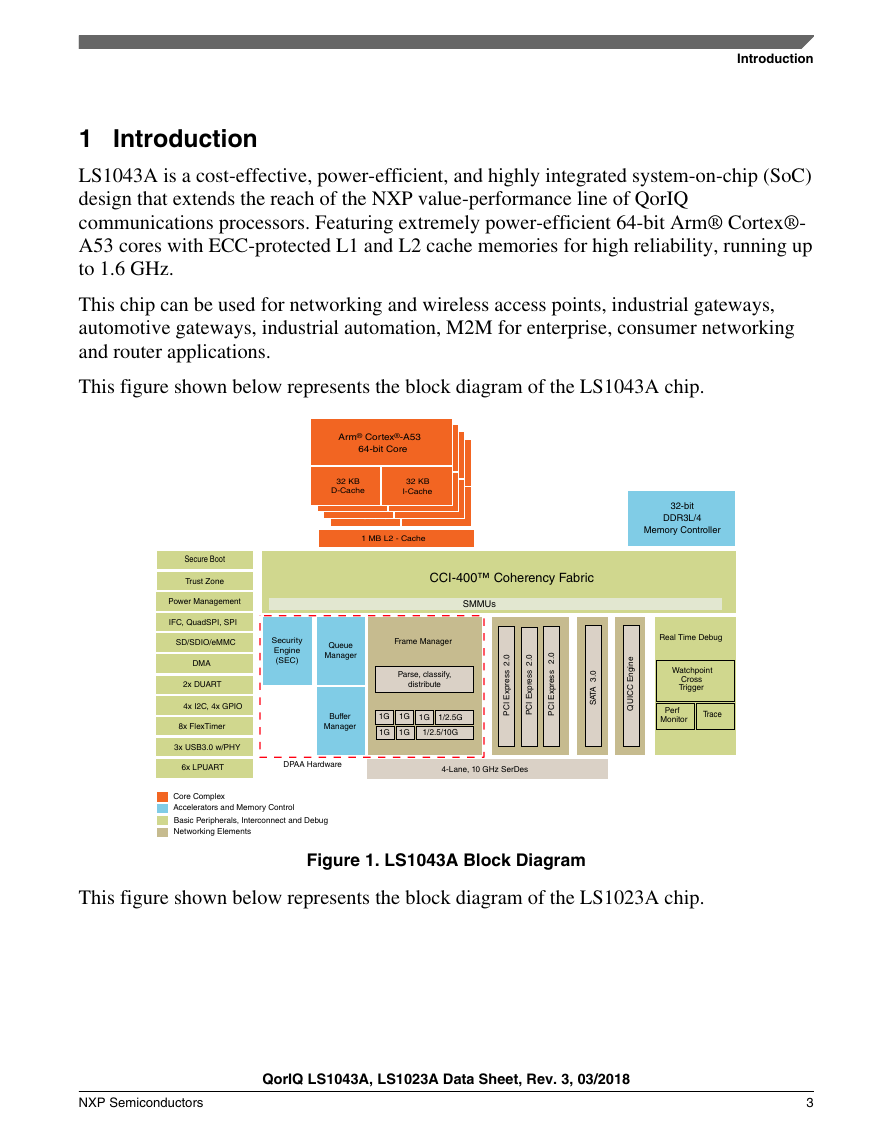

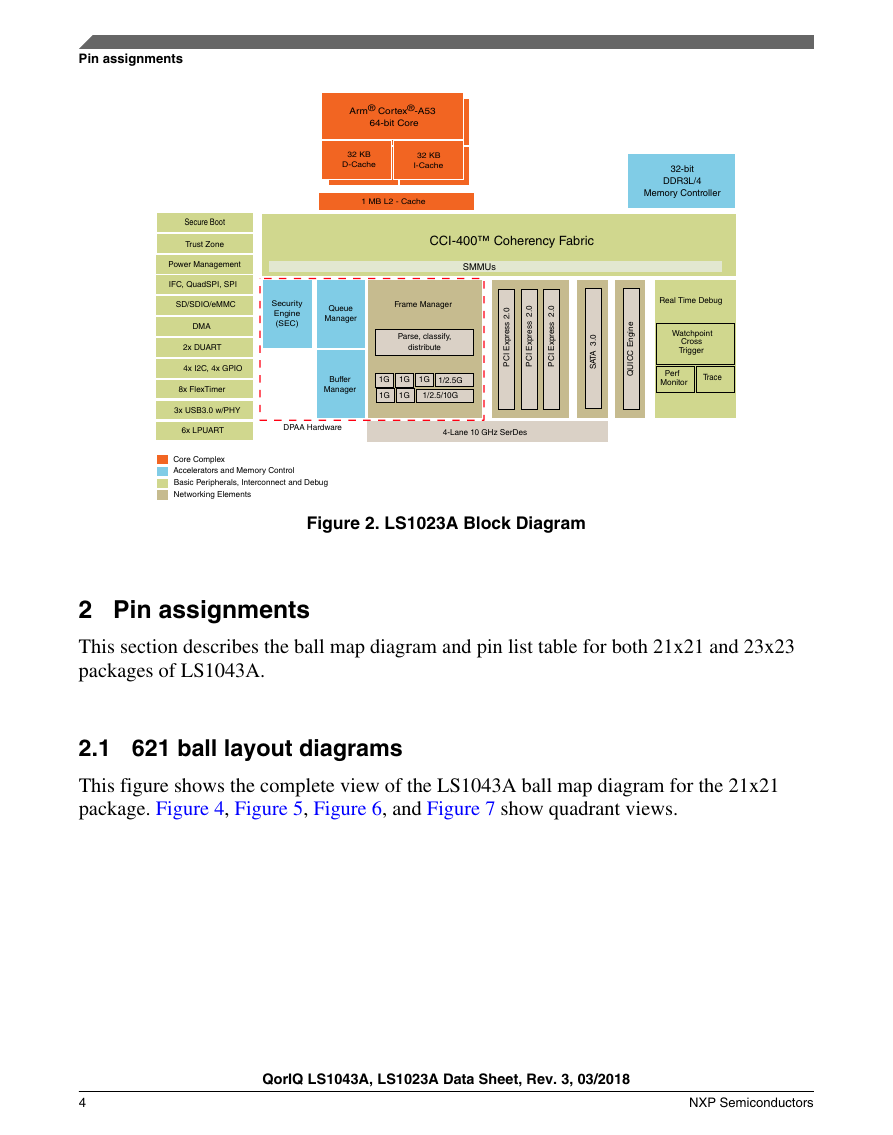

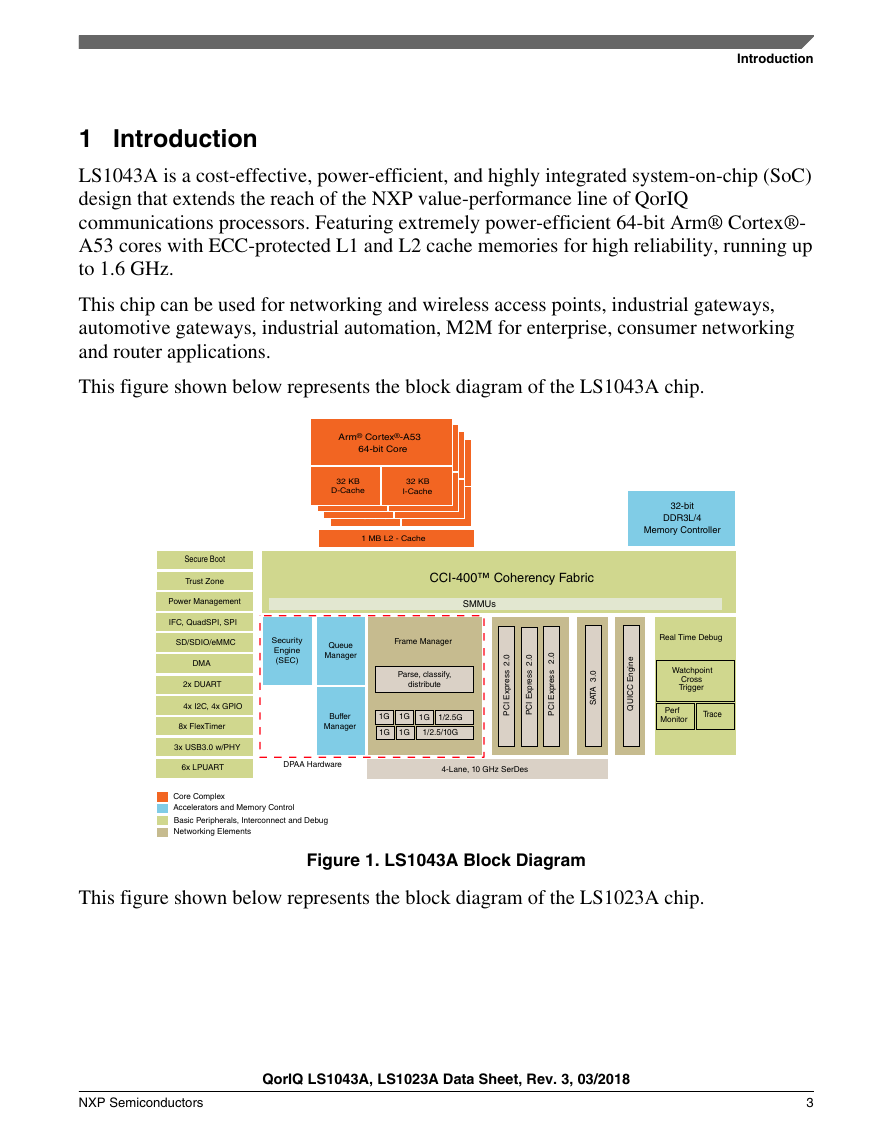

Introduction

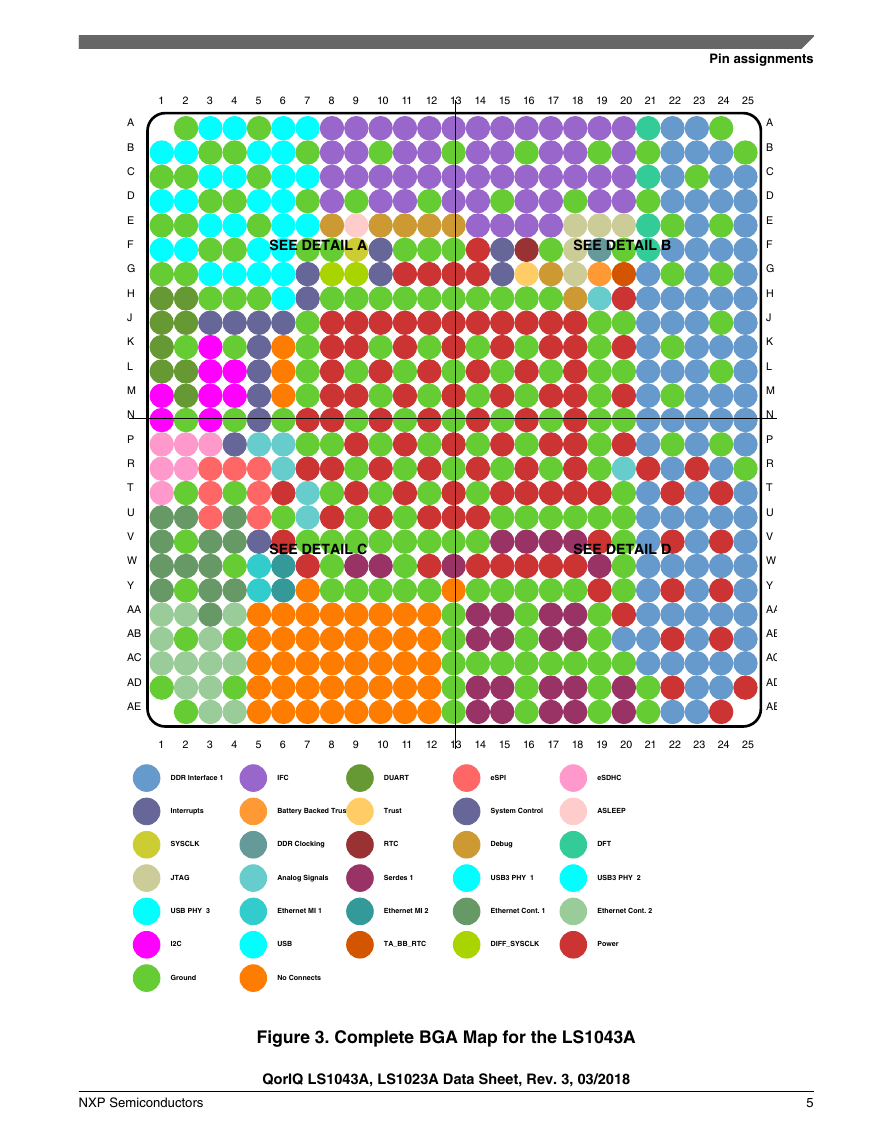

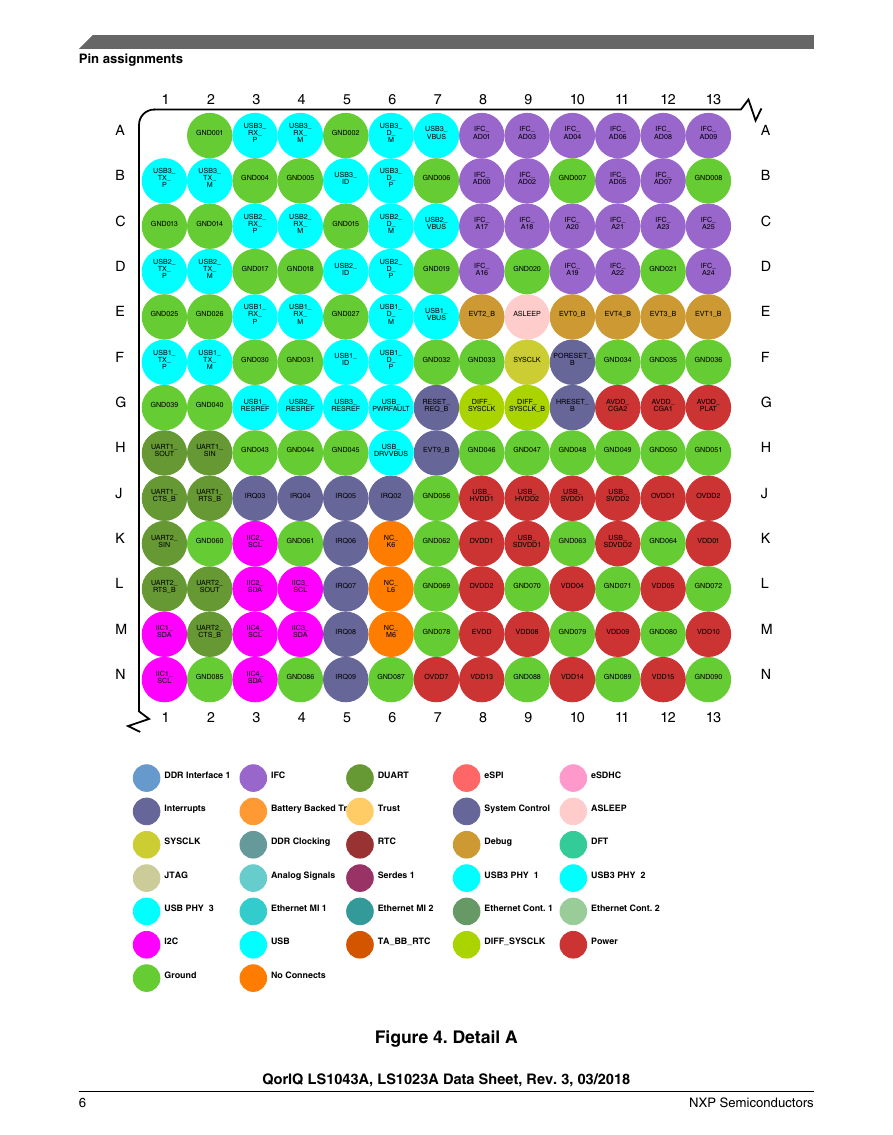

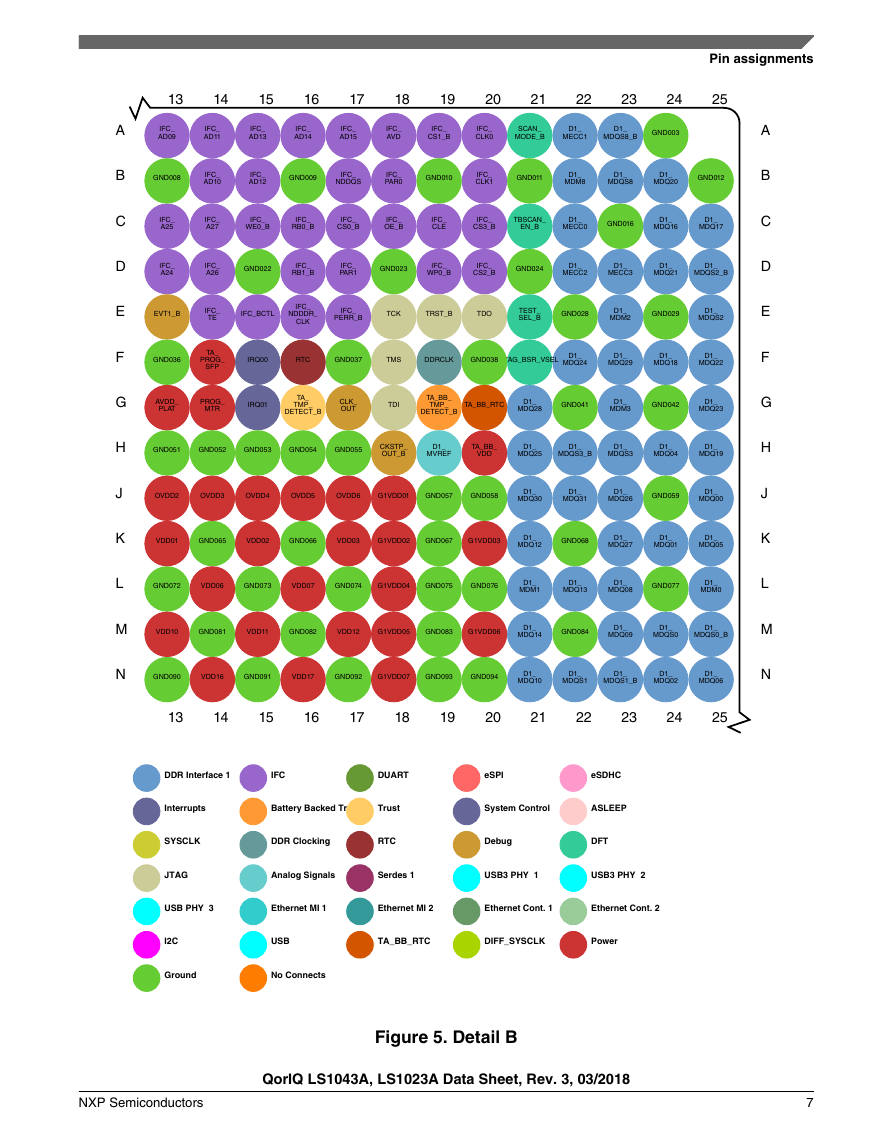

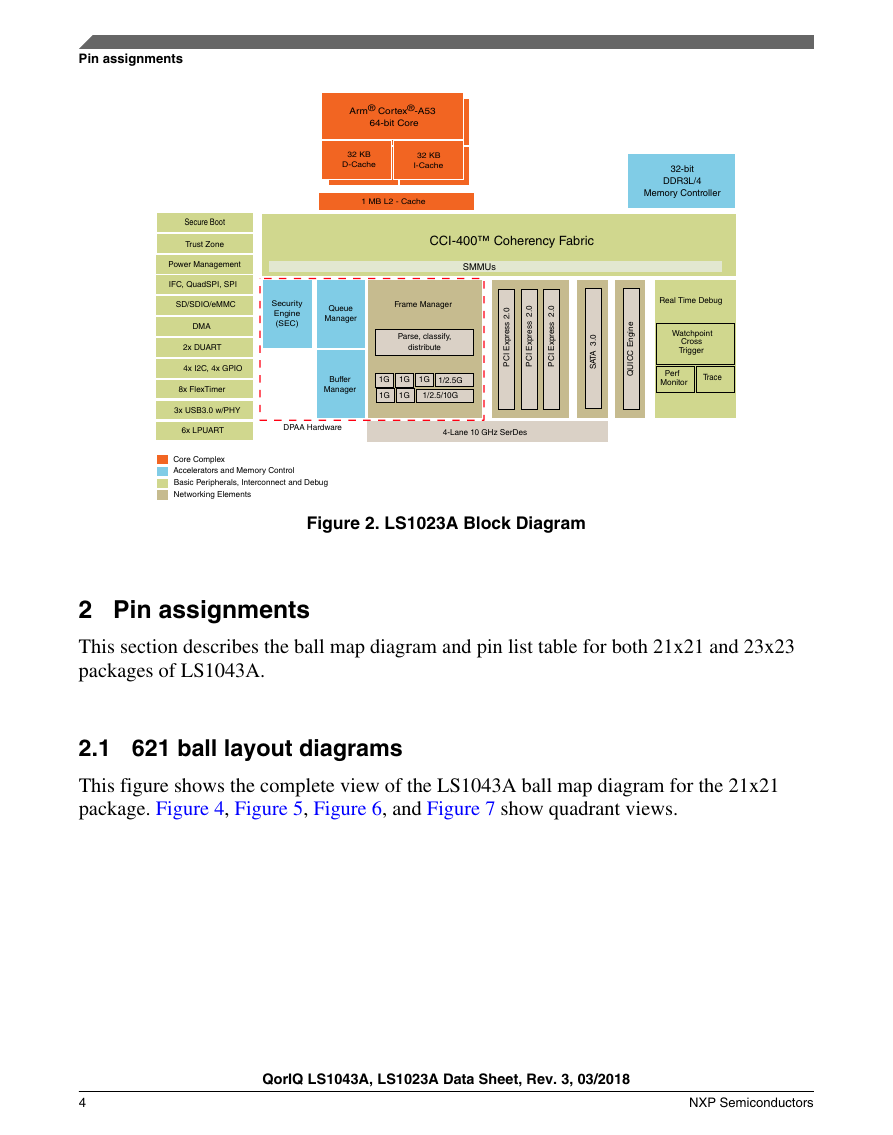

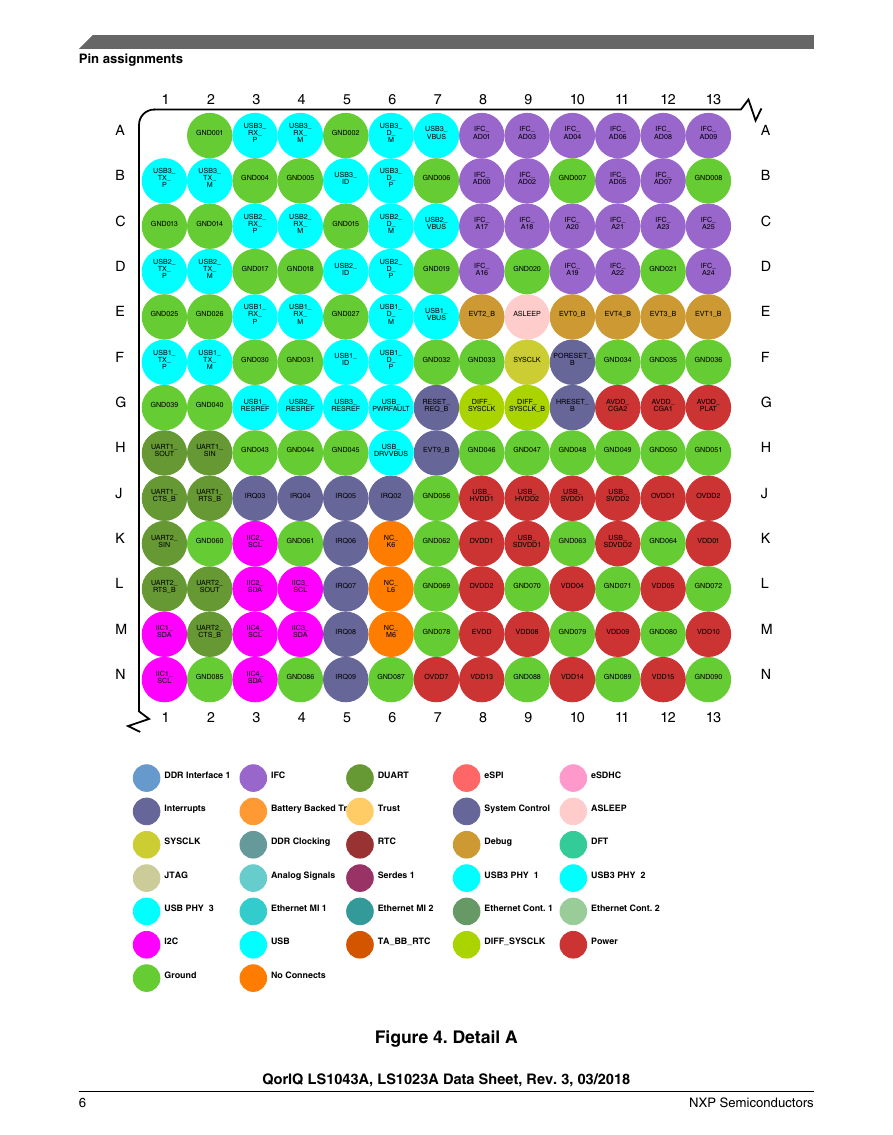

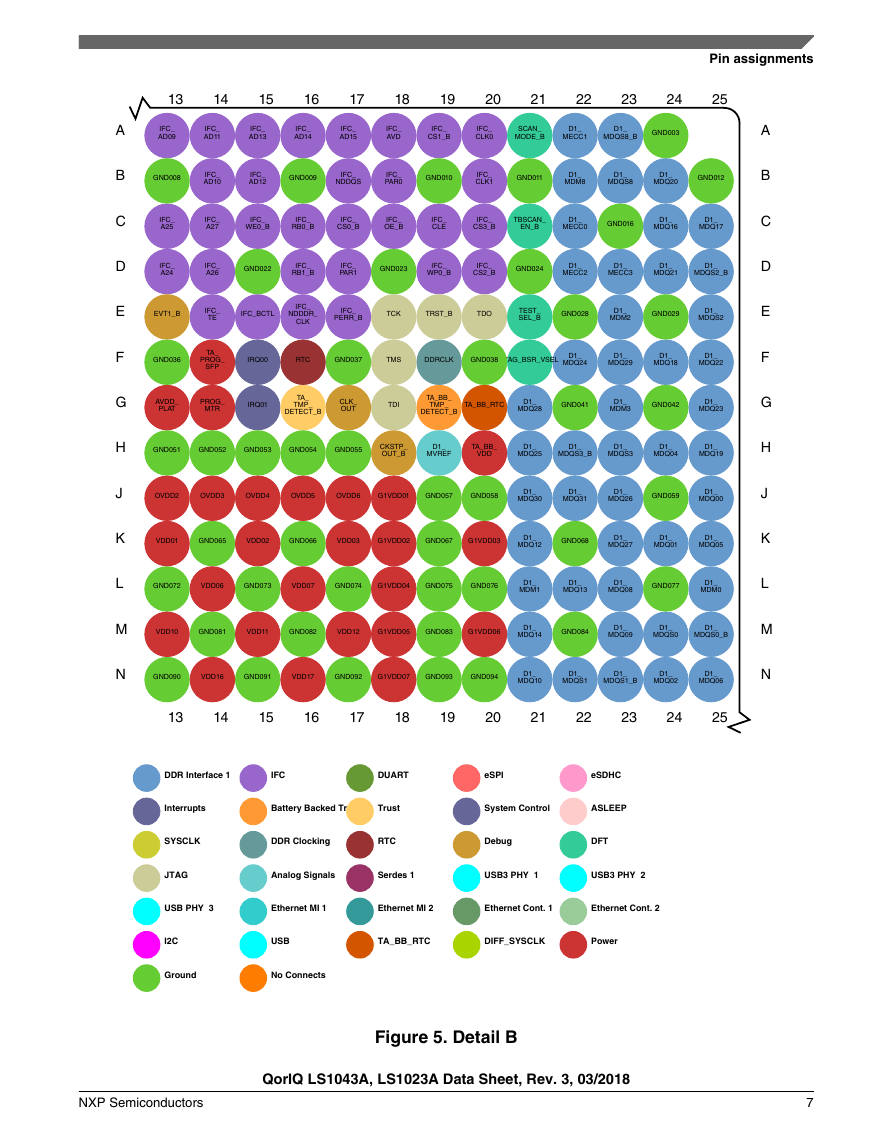

Pin assignments

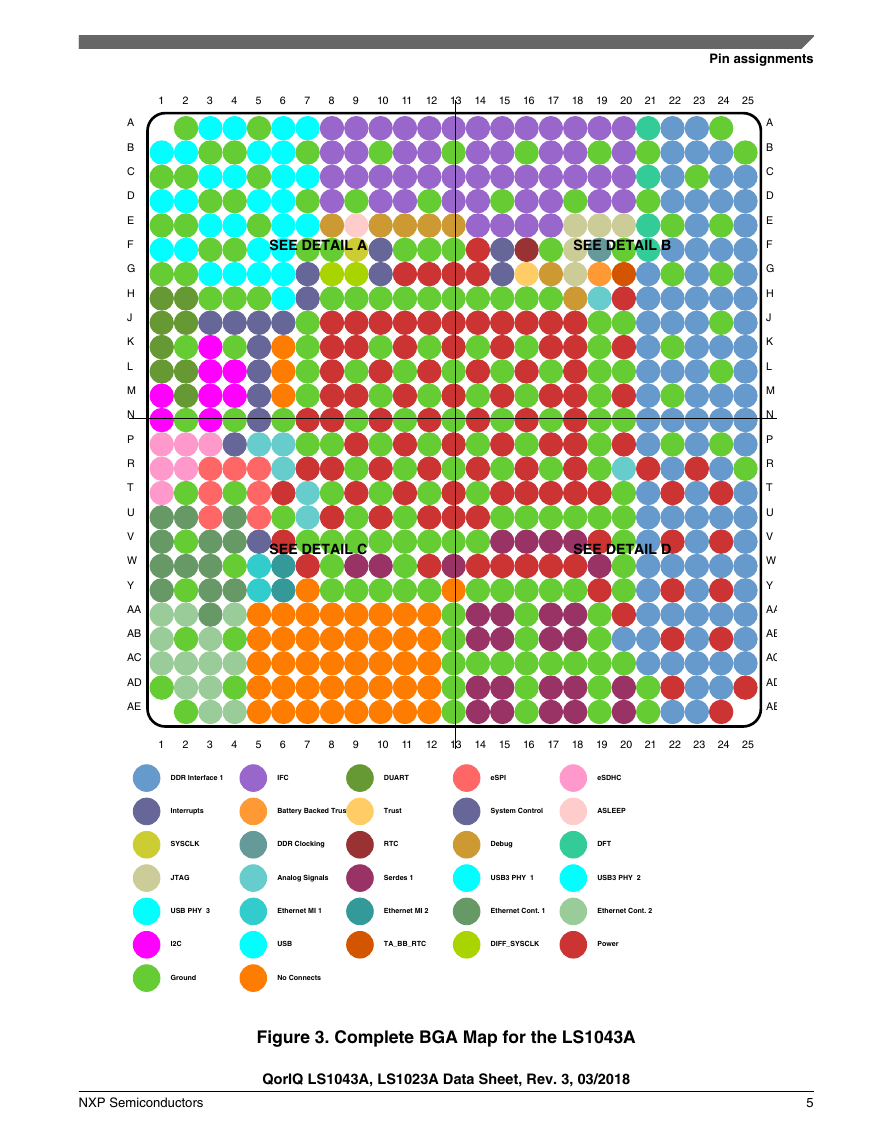

621 ball layout diagrams

Pinout list (21x21)

780 ball layout diagrams

Pinout list

Electrical characteristics

Overall DC electrical characteristics

Absolute maximum ratings

Recommended operating conditions

Output driver characteristics

General AC timing specifications

Power sequencing

Power down requirements

Power characteristics

Low power mode saving estimation

I/O power dissipation

Power-on ramp rate

Input clocks

System clock (SYSCLK)

SYSCLK DC electrical characteristics

SYSCLK AC timing specifications

Spread-spectrum sources

Real-time clock timing (RTC)

Gigabit Ethernet reference clock timing

DDR clock (DDRCLK)

DDRCLK DC electrical characteristics

DDRCLK AC timing specifications

Differential system clock (DIFF_SYSCLK/DIFF_SYSCLK_B) timing specifications

Differential system clock DC timing characteristics

Differential system clock AC timing specifications

Other input clocks

RESET initialization

DDR4 and DDR3L SDRAM controller

DDR4 and DDR3L SDRAM interface DC electrical characteristics

DDR4 and DDR3L SDRAM interface AC timing specifications

DDR4 and DDR3L SDRAM interface input AC timing specifications

DDR4 and DDR3L SDRAM interface output AC timing specifications

Ethernet interface, Ethernet management interface, IEEE Std 1588

SGMII interface

SGMII clocking requirements for SD1_REF_CLKn_P and SD1_REF_CLKn_N

SGMII DC electrical characteristics

SGMII and SGMII 2.5G transmit DC specifications

SGMII and SGMII 2.5G DC receiver electrical characteristics

SGMII AC timing specifications

SGMII and SGMII 2.5G transmit AC timing specifications

SGMII AC measurement details

SGMII and SGMII 2.5G receiver AC timing Specification

QSGMII interface

QSGMII clocking requirements for SD1_REF_CLKn_P and SD1_REF_CLKn_N

QSGMII DC electrical characteristics

QSGMII transmitter DC specifications

QSGMII DC receiver electrical characteristics

QSGMII AC timing specifications

QSGMII transmit AC timing specifications

QSGMII receiver AC timing Specification

XFI interface

XFI clocking requirements for SD1_REF_CLKn_P and SD1_REF_CLKn_N

XFI DC electrical characteristics

XFI transmitter DC electrical characteristics

XFI receiver DC electrical characteristics

XFI AC timing specifications

XFI transmitter AC timing specifications

XFI receiver AC timing specifications

1000Base-KX interface

1000Base-KX DC electrical characteristics

1000Base-KX Transmitter DC Specifications

1000Base-KX Receiver DC Specifications

1000Base-KX AC electrical characteristics

1000Base-KX Transmitter AC Specifications

1000Base-KX Receiver AC Specifications

RGMII electrical specifications

RGMII DC electrical characteristics

RGMII AC timing specifications

Ethernet management interface (EMI)

Ethernet management interface 1 (EMI1)

EMI1 DC electrical characteristics

EMI1 AC timing specifications

Ethernet management interface 2 (EMI2)

EMI2 DC electrical characteristics

EMI2 AC timing specifications

IEEE 1588 electrical specifications

IEEE 1588 DC electrical characteristics

IEEE 1588 AC timing specifications

QUICC engine specifications

HDLC interface

HDLC and Synchronous UART DC electrical characteristics

HDLC and Synchronous UART AC timing specifications

Time-division-multiplexed and serial interface (TDM/SI)

TDM/SI DC electrical characteristics

TDM/SI AC timing specifications

USB 3.0 interface

USB 3.0 PHY transceiver supply DC voltage

USB 3.0 DC electrical characteristics

USB 3.0 AC timing specifications

USB 3.0 reference clock requirements

USB 3.0 LFPS specifications

Integrated Flash Controller

IFC DC electrical characteristics

Integrated Flash Controller AC Timing Specifications

Test Condition

IFC AC Timing Specifications (GPCM/GASIC)

IFC AC Timing Specifications (NOR)

IFC AC Timing Specifications (NAND)

IFC-NAND SDR AC Timing Specifications

IFC-NAND NVDDR AC Timing Specification

LPUART interface

LPUART DC electrical characteristics

LPUART AC timing specifications

DUART interface

DUART DC electrical characteristics

DUART AC timing specifications

Flextimer interface

Flextimer DC electrical characteristics

Flextimer AC timing specifications

SPI interface

SPI DC electrical characteristics

SPI AC timing specifications

QuadSPI interface

QuadSPI DC electrical characteristics

QuadSPI AC timing specifications

QuadSPI timing SDR mode

Enhanced secure digital host controller (eSDHC)

eSDHC DC electrical characteristics

eSDHC AC timing specifications

JTAG controller

JTAG DC electrical characteristics

JTAG AC timing specifications

I2C interface

I2C DC electrical characteristics

I2C AC timing specifications

GPIO interface

GPIO DC electrical characteristics

GPIO AC timing specifications

GIC interface

GIC DC electrical characteristics

GIC AC timing specifications

High-speed serial interfaces (HSSI)

Signal terms definitions

SerDes reference clocks

SerDes spread-spectrum clock source recommendations

SerDes reference clock receiver characteristics

DC-level requirements for SerDes reference clocks

AC requirements for SerDes reference clocks

SerDes transmitter and receiver reference circuits

PCI Express

Clocking dependencies

PCI Express DC physical layer specifications

PCI Express DC physical layer transmitter specifications

PCI Express DC physical layer receiver specifications

PCI Express AC physical layer specifications

PCI Express AC physical layer transmitter specifications

PCI Express AC physical layer receiver specifications

Test and measurement load

Serial ATA (SATA) interface

SATA DC electrical characteristics

SATA DC transmitter output characteristics

SATA DC receiver input characteristics

SATA AC timing specifications

AC requirements for SATA REF_CLK

AC transmitter output characteristics

AC differential receiver input characteristics

Hardware design considerations

System clocking

PLL characteristics

Clock ranges

DDR clock ranges

Platform to SYSCLK PLL ratio

Core cluster to SYSCLK PLL ratio

Core complex PLL select

DDR controller PLL ratios

Valid reference clocks and PLL configurations for SerDes protocols

Frequency options

SYSCLK and core cluster frequency options

SYSCLK and platform frequency options

DDRCLK and DDR data rate frequency options

SYSCLK and eSDHC high speed modes frequency options

Minimum platform frequency requirements for high-speed interfaces

Connection recommendations

JTAG configuration signals

Termination of unused signals

Guidelines for high-speed interface termination

SerDes interface entirely unused

SerDes interface partly unused

Thermal

Recommended thermal model

Temperature diode

Thermal management information

Internal package conduction resistance

Thermal interface materials

Package information

Package parameters for the FC-PBGA

Mechanical dimensions of the FC-PBGA

Security fuse processor

Ordering information

Part numbering nomenclature

Part marking

Revision history

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc