版权所有,禁止未经授权的商业使用行为

高教社&XILINX SOC竞赛培训系列课程

何宾

何宾

Tel:

email:hebin@mail.buct.edu.cn

email:

Tel:13911127536

所有培训资料均可从网站

http://bucteda.eefocus.com下载

高等教育出版社

北京中教仪装备技术有限公司

北京中教仪装备技术有

限公司

�

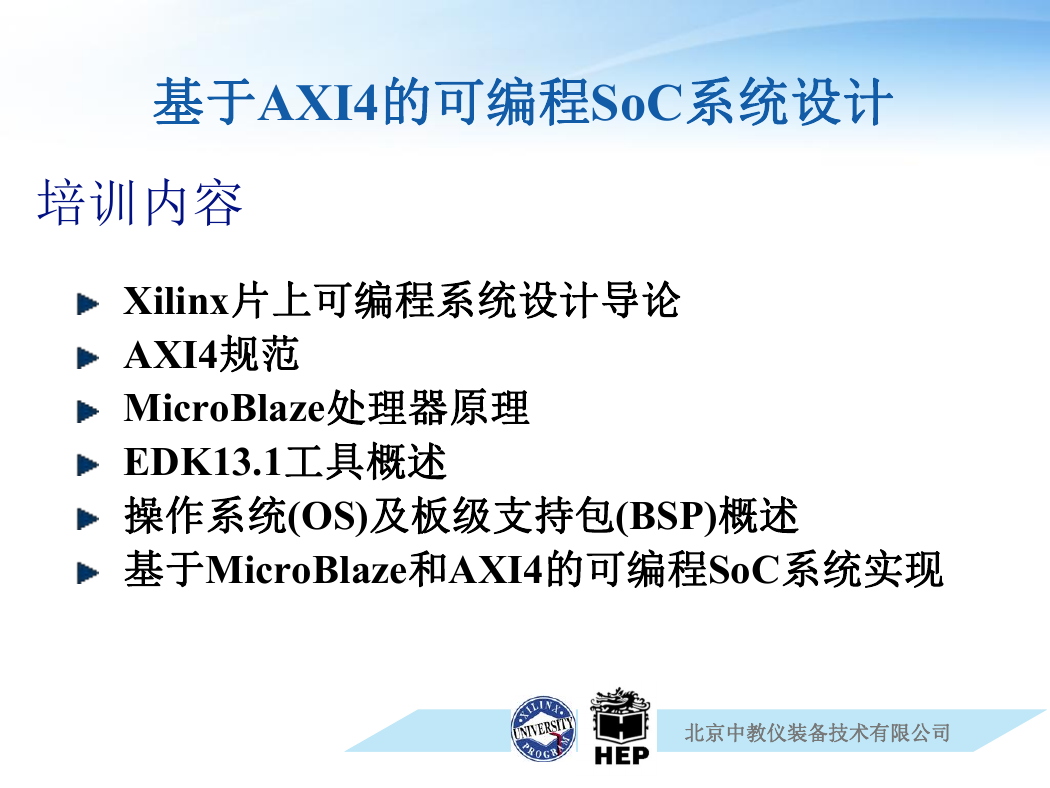

基于AXI4的可编程SoC系统设计

培训内容

Xilinx片上可编程系统设计导论

AXI4规范

MicroBlaze处理器原理

EDK13.1工具概述

操作系统(OS)及板级支持包(BSP)概述

基于MicroBlaze和AXI4的可编程SoC系统实现

北京中教仪装备技术有限公司

�

片上可编程系统设计导论

--基本概念

基于现场可编程门阵列(Field Programmable Gate

Array, FPGA)的可编程SoC系统(Programmable-System-

on-a-chip,P-SoC),包含嵌入式的软核或硬核处理器、

存储器和硬件加速器。

P-SoC的出现为设计者提供了设计高性能嵌入式系统

和优化系统的条件。

注:为了后面叙述方便,将Xilinx的可编程SoC系统,英文简述为P-SOC。

用于区分其它SOC的系统。

北京中教仪装备技术有限公司

�

片上可编程系统设计导论

--基本概念

P-SoC嵌入式处理器分为软核和硬核处理器两大类。

Xilinx提供了将物理的处理器核集成到FPGA硅片上的硬核

处理器产品。

一个处理器使用专门的硅片实现称为硬核处理器,比

如Xilinx:

ü 将PowerPC 405/440硬核集成到Virtex系列的FPGA芯片中;

ü 将ARM Cortex-A9 MP双核处理器集成在Zynq-7000系列的FPGA

芯片中。

北京中教仪装备技术有限公司

�

片上可编程系统设计导论

--基本概念

软核处理器是通过使用FPGA的通用逻辑实现的。软

核处理器通过HDL语言或网表进行描述的。软核处理器

必须进行综合才能使用。比如Xilinx:

ü 提供32位的软核处理器MicroBlaze;

ü 提供8位的软核控制器Picoblaze;

北京中教仪装备技术有限公司

�

片上可编程系统设计导论

--基本概念

在基于软核和硬核处理器的P-SoC系统中,本地存储

器、处理器总线、内部外设、外设控制器和存储器控制器

必须使用FPGA的通用逻辑实现。

下面给出Xilinx公司的软核和硬核处理器的性能。

北京中教仪装备技术有限公司

�

片上可编程系统设计导论

--Xilinx P-SoC类别

处理器种类

总线 IP核类型 总线 语言

ARM Cortex-A9 MP

(双核)

PowerPC

MicroBlaze

PicoBlaze

64位

32位

32位

8位

硬核

硬核

软核

软核

AXI

c/c++,

汇编

PLB c/c++,

汇编

c/c++,

PLB/

AXI

汇编

---- 汇编

开发环境

(Xilinx提供)

XPS&SDK

XPS&SDK

XPS&SDK

ISE&汇编器

北京中教仪装备技术有限公司

�

片上可编程系统设计导论

--基本概念

由于持续的要求嵌入式系统具有更多的功能、更好的

性能和灵活性,因此传统上的设计方法已经不适应这种要

求。当设计人员试图通过高性能的嵌入式处理器得到更高

的性能时,遇到了吞吐量和性能方面的限制,而这种限制

源于系统和结构的瓶颈,以及存储器带宽的限制。

现在解决问题的方法是“专用”,即对某个嵌入式系

统应用使用专门的解决方法。比如,数字信号处理器DSP

用于解决某一类专门的数字信号处理。对于一些高容量的

应用,设计人员可能还需要专门开发ASIC芯片。

北京中教仪装备技术有限公司

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc