Hi3536 H.265 解码处理器

用户指南

文档版本

00B05

发布日期

2015-03-23

部件编码

N/A

初稿,仅供参考!�

版权所有 © 深圳市海思半导体有限公司 2014—2015。保留一切权利。

非经本公司书面许可,任何单位和个人不得擅自摘抄、复制本文档内容的部分或全部,并不得以任何形

式传播。

商标声明

、

、海思和其他海思商标均为深圳市海思半导体有限公司的商标。

本文档提及的其他所有商标或注册商标,由各自的所有人拥有。

注意

您购买的产品、服务或特性等应受海思公司商业合同和条款的约束,本文档中描述的全部或部分产品、

服务或特性可能不在您的购买或使用范围之内。除非合同另有约定,海思公司对本文档内容不做任何明

示或默示的声明或保证。

由于产品版本升级或其他原因,本文档内容会不定期进行更新。除非另有约定,本文档仅作为使用指导,

本文档中的所有陈述、信息和建议不构成任何明示或暗示的担保。

深圳市海思半导体有限公司

地址:

深圳市龙岗区坂田华为基地华为电气生产中心 邮编:518129

网址:

http://www.hisilicon.com

客户服务电话:

+86-755-28788858

客户服务传真:

+86-755-28357515

客户服务邮箱:

support@hisilicon.com

初稿,仅供参考!�

Hi3536 H.265 解码处理器

用户指南

前 言

目 录

前 言 .................................................................................................................................................. 1

文档版本 00B05 (2015-03-23)

海思专有和保密信息

版权所有 © 深圳市海思半导体有限公司

i

初稿,仅供参考!�

Hi3536 H.265 解码处理器

用户指南

前 言

前 言

概述

本文档介绍了 Hi3536 芯片的特性、逻辑结构,详细描述各个模块的功能、工作方式、

相关寄存器定义,用图表的方式给出了接口时序关系和相关参数,并详细描述了芯片的

管脚定义和用途以及芯片的性能参数和封装尺寸。

产品版本

与本文档相对应的产品版本如下。

产品名称

Hi3536

产品版本

V100

读者对象

本文档主要适用于以下工程师:

电子产品设计维护人员

电子产品元器件市场销售人员

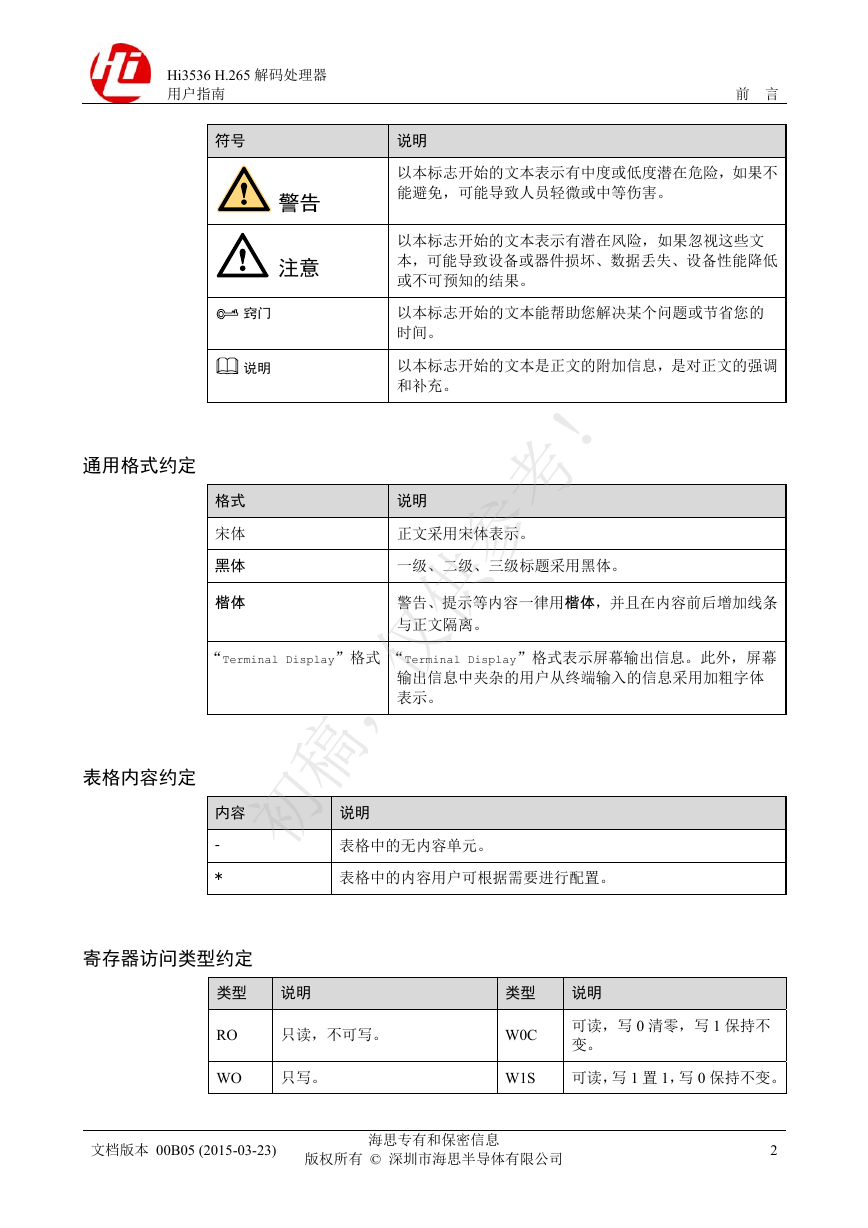

约定符号约定

在本文中可能出现下列标志,它们所代表的含义如下。

符号

说明

以本标志开始的文本表示有高度潜在危险,如果不能避

免,会导致人员死亡或严重伤害。

文档版本 00B05 (2015-03-23)

海思专有和保密信息

版权所有 © 深圳市海思半导体有限公司

1

初稿,仅供参考!�

Hi3536 H.265 解码处理器

用户指南

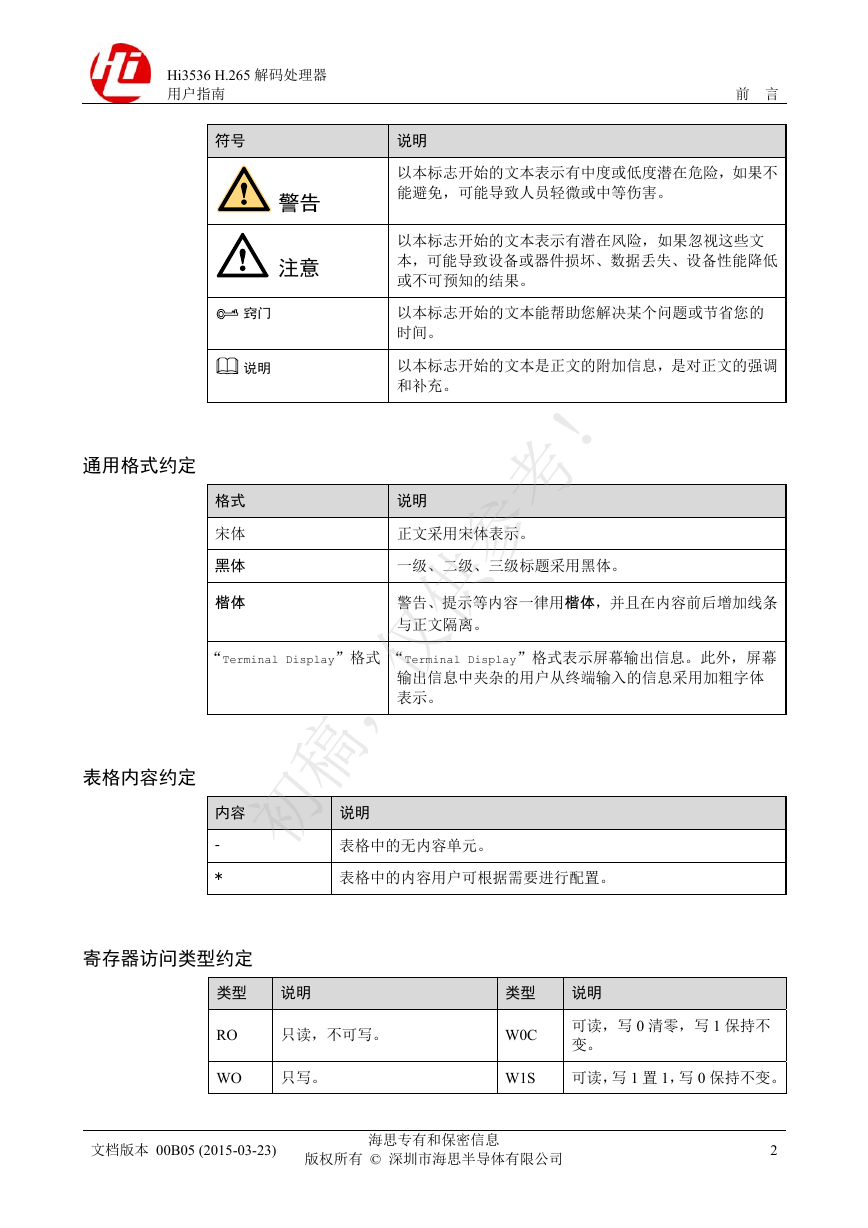

符号

说明

前 言

以本标志开始的文本表示有中度或低度潜在危险,如果不

能避免,可能导致人员轻微或中等伤害。

以本标志开始的文本表示有潜在风险,如果忽视这些文

本,可能导致设备或器件损坏、数据丢失、设备性能降低

或不可预知的结果。

以本标志开始的文本能帮助您解决某个问题或节省您的

时间。

以本标志开始的文本是正文的附加信息,是对正文的强调

和补充。

通用格式约定

格式

宋体

黑体

楷体

说明

正文采用宋体表示。

一级、二级、三级标题采用黑体。

警告、提示等内容一律用楷体,并且在内容前后增加线条

与正文隔离。

“Terminal Display”格式 “Terminal Display”格式表示屏幕输出信息。此外,屏幕

输出信息中夹杂的用户从终端输入的信息采用加粗字体

表示。

说明

表格中的无内容单元。

表格中的内容用户可根据需要进行配置。

表格内容约定

内容

-

*

寄存器访问类型约定

类型 说明

只读,不可写。

RO

WO

说明

类型

W0C 可读,写 0 清零,写 1 保持不

变。

只写。

W1S

可读,写 1 置 1,写 0 保持不变。

文档版本 00B05 (2015-03-23)

海思专有和保密信息

版权所有 © 深圳市海思半导体有限公司

2

初稿,仅供参考!�

Hi3536 H.265 解码处理器

用户指南

类型 说明

RW

RC

可读可写。

读清零。

W1C 可读,写 1 清零,写 0 保持不变。

前 言

类型

W0S

说明

可读,写 0 置 1,写 1 保持不变。

OSW 可读,写 1 后片内自清零,即

产生一个脉冲。

数值单位约定

数据容量、频率、数据速率等的表达方式说明如下。

类别

符号

1K

数据容量(如 RAM 容量)

1M

频率、数据速率等

1G

1k

1M

1G

地址、数据的表达方式说明如下。

对应的数值

1024

1,048,576

1,073,741,824

1000

1,000,000

1,000,000,000

举例

说明

0xFE04、0x18

用 16 进制表示的数据值、地址值。

0b000、0b00 00000000

表示 2 进制的数据值以及 2 进制序列(寄

存器描述中除外)。

符号

0x

0b

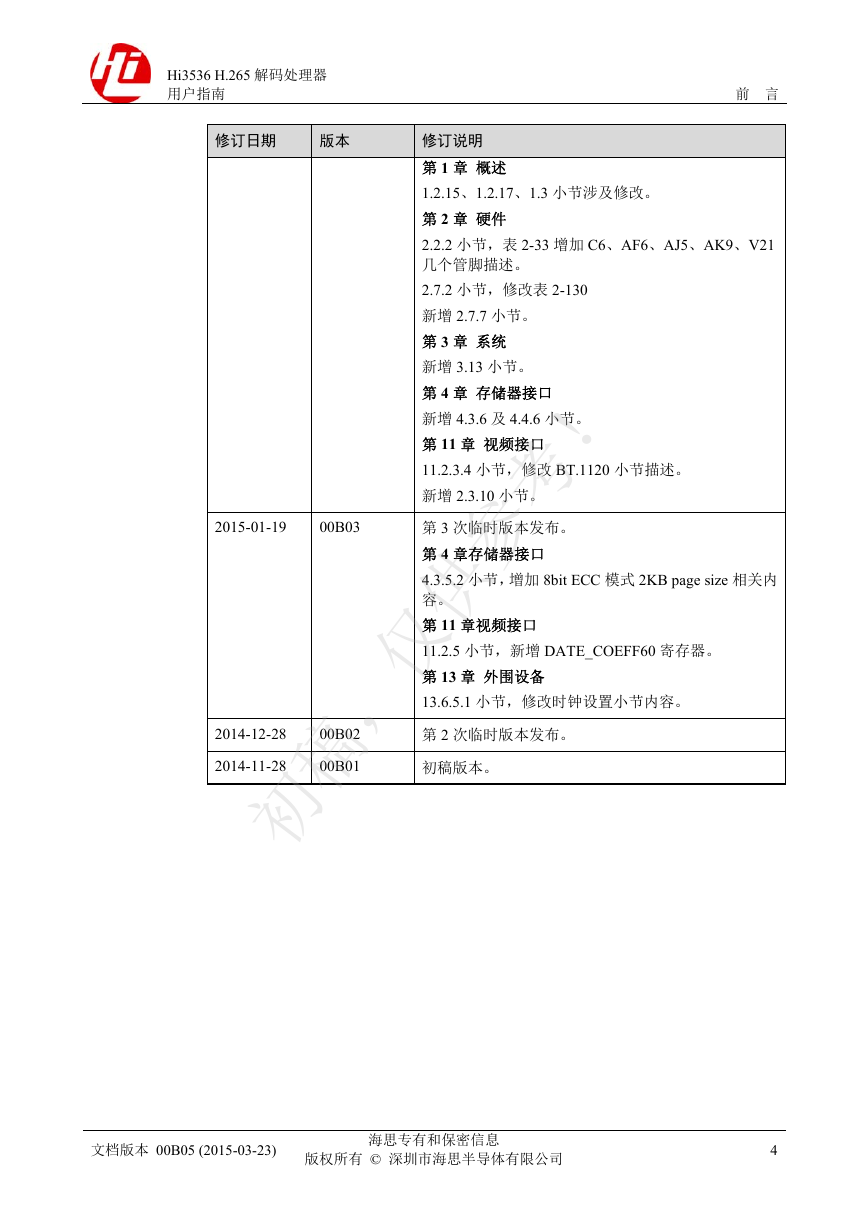

修订记录

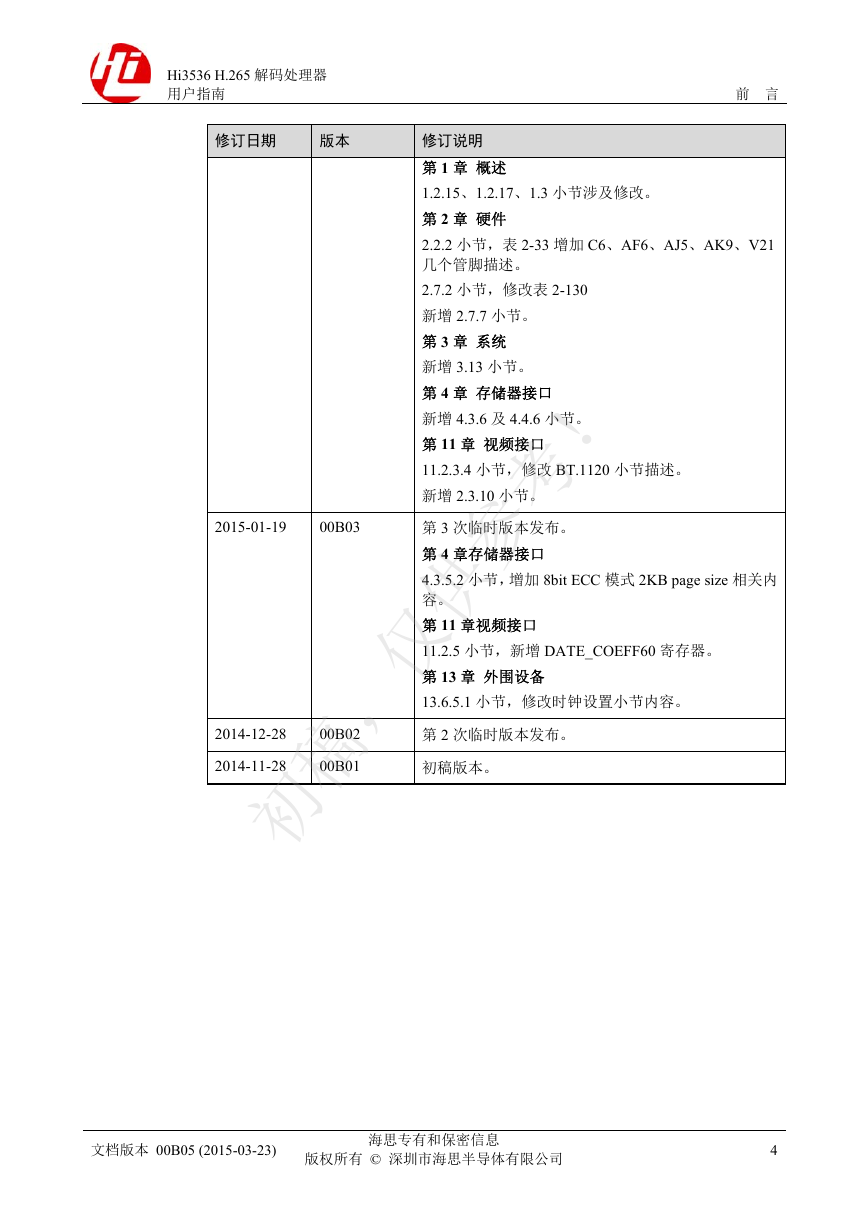

修订记录累积了每次文档更新的说明。最新版本的文档包含以前所有文档版本的更新内

容。

修订日期

2015-03-23

版本

00B05

修订说明

第 5 次临时版本发布。

第 2 章 硬件

2.2.9 小节涉及修改。

2015-03-02

00B04

第 4 次临时版本发布。

文档版本 00B05 (2015-03-23)

海思专有和保密信息

版权所有 © 深圳市海思半导体有限公司

3

初稿,仅供参考!�

Hi3536 H.265 解码处理器

用户指南

修订日期

版本

2015-01-19

00B03

前 言

修订说明

第 1 章 概述

1.2.15、1.2.17、1.3 小节涉及修改。

第 2 章 硬件

2.2.2 小节,表 2-33 增加 C6、AF6、AJ5、AK9、V21

几个管脚描述。

2.7.2 小节,修改表 2-130

新增 2.7.7 小节。

第 3 章 系统

新增 3.13 小节。

第 4 章 存储器接口

新增 4.3.6 及 4.4.6 小节。

第 11 章 视频接口

11.2.3.4 小节,修改 BT.1120 小节描述。

新增 2.3.10 小节。

第 3 次临时版本发布。

第 4 章存储器接口

4.3.5.2 小节,增加 8bit ECC 模式 2KB page size 相关内

容。

第 11 章视频接口

11.2.5 小节,新增 DATE_COEFF60 寄存器。

第 13 章 外围设备

13.6.5.1 小节,修改时钟设置小节内容。

2014-12-28

2014-11-28

00B02

00B01

第 2 次临时版本发布。

初稿版本。

文档版本 00B05 (2015-03-23)

海思专有和保密信息

版权所有 © 深圳市海思半导体有限公司

4

初稿,仅供参考!�

Hi3536 H.265 解码处理器

用户指南

目 录

目 录

1 产品概述 ....................................................................................................................................... 1-1

1.1 应用场景 ...................................................................................................................................................... 1-1

1.2 架构 .............................................................................................................................................................. 1-2

1.2.1 概述 .................................................................................................................................................... 1-2

1.2.2 处理器内核 ........................................................................................................................................ 1-3

1.2.3 视频解码标准..................................................................................................................................... 1-3

1.2.4 视频编码标准..................................................................................................................................... 1-4

1.2.5 视频编解码处理 ................................................................................................................................. 1-4

1.2.6 GPU ..................................................................................................................................................... 1-4

1.2.7 智能视频分析..................................................................................................................................... 1-4

1.2.8 视频与图形处理 ................................................................................................................................. 1-4

1.2.9 视频接口 ............................................................................................................................................ 1-5

1.2.10 音频接口 .......................................................................................................................................... 1-5

1.2.11 网络接口 ........................................................................................................................................... 1-5

1.2.12 安全引擎 .......................................................................................................................................... 1-6

1.2.13 RAID 加速引擎 ................................................................................................................................. 1-6

1.2.14 外围接口 .......................................................................................................................................... 1-6

1.2.15 存储器接口....................................................................................................................................... 1-6

1.2.16 独立供电 RTC .................................................................................................................................. 1-7

1.2.17 启动模式 .......................................................................................................................................... 1-7

1.2.18 SDK ................................................................................................................................................... 1-7

1.2.19 芯片物理规格 ................................................................................................................................... 1-7

1.3 启动模式 ...................................................................................................................................................... 1-8

文档版本 00B05 (2015-03-23)

版权所有 © 深圳市海思半导体有限公司

海思专有和保密信息

i

初稿,仅供参考!�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc