�

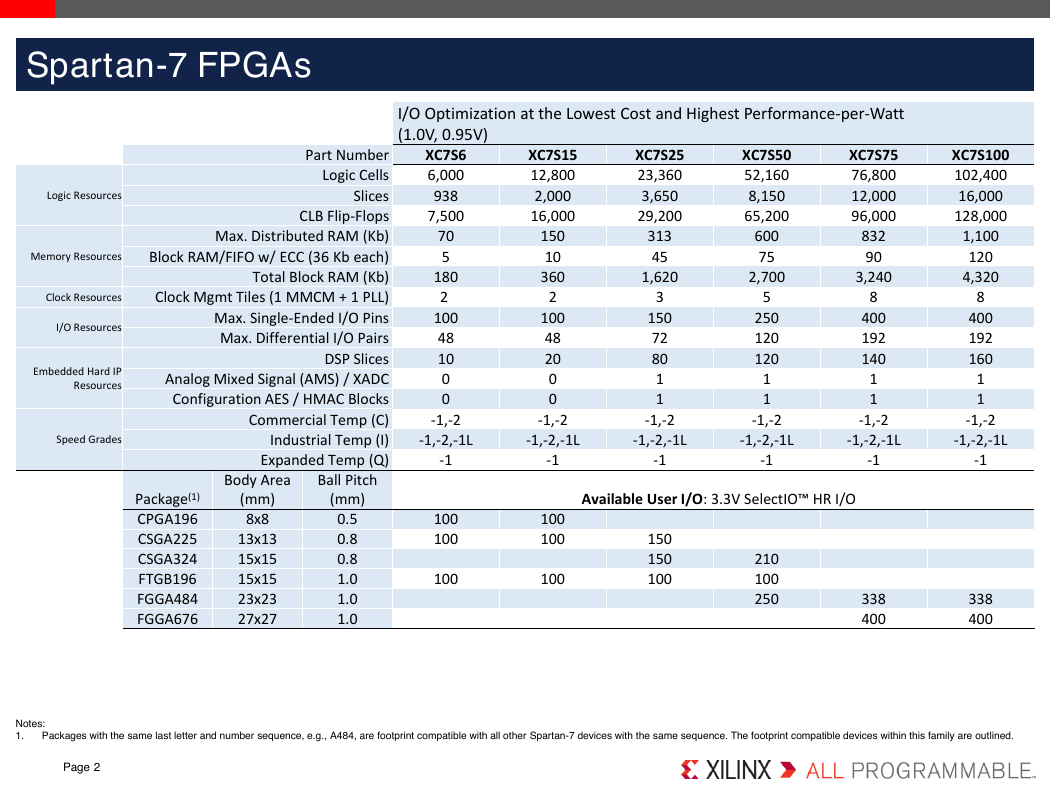

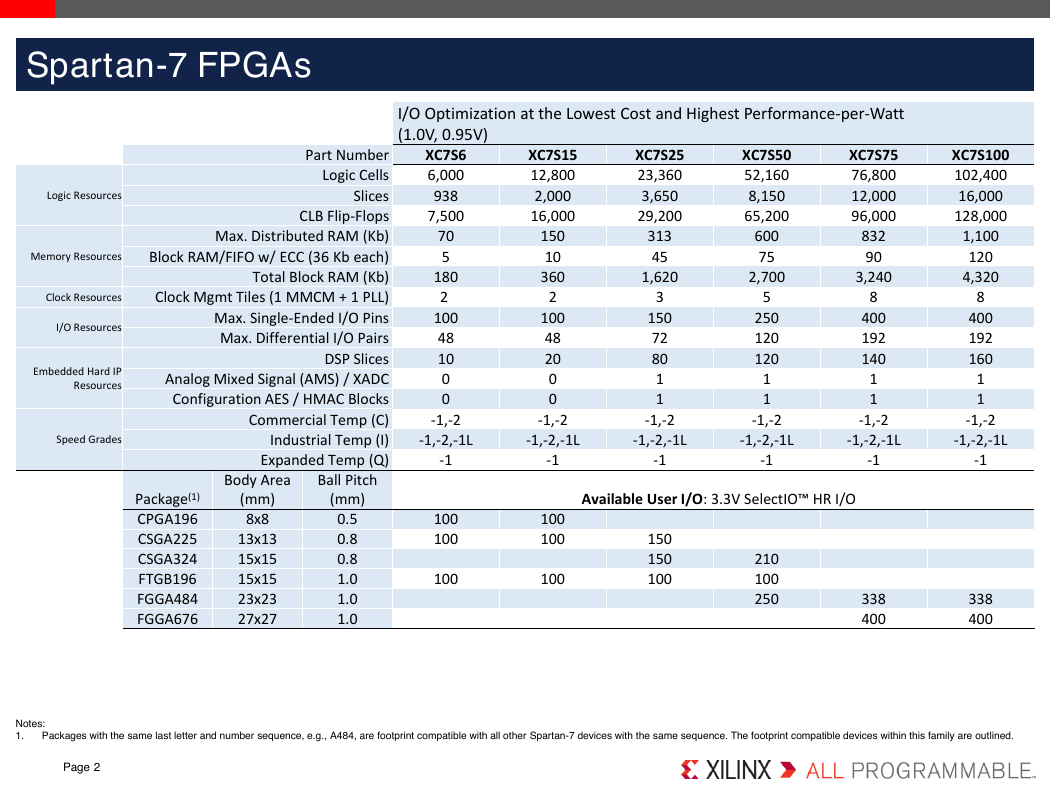

Spartan-7 FPGAs

Logic Resources

Memory Resources

Clock Resources

I/O Resources

Embedded Hard IP

Resources

Speed Grades

Part Number

Logic Cells

Slices

CLB Flip-Flops

Max. Distributed RAM (Kb)

Block RAM/FIFO w/ ECC (36 Kb each)

Total Block RAM (Kb)

Clock Mgmt Tiles (1 MMCM + 1 PLL)

Max. Single-Ended I/O Pins

Max. Differential I/O Pairs

DSP Slices

Analog Mixed Signal (AMS) / XADC

Configuration AES / HMAC Blocks

Commercial Temp (C)

Industrial Temp (I)

Expanded Temp (Q)

Body Area

Ball Pitch

Package(1)

CPGA196

CSGA225

CSGA324

FTGB196

FGGA484

FGGA676

(mm)

8x8

13x13

15x15

15x15

23x23

27x27

(mm)

0.5

0.8

0.8

1.0

1.0

1.0

I/O Optimization at the Lowest Cost and Highest Performance-per-Watt

(1.0V, 0.95V)

XC7S6

6,000

938

7,500

70

5

180

2

100

48

10

0

0

XC7S15

12,800

2,000

16,000

150

10

360

2

100

48

20

0

0

XC7S25

23,360

3,650

29,200

313

45

1,620

3

150

72

80

1

1

XC7S50

52,160

8,150

65,200

600

75

2,700

5

250

120

120

1

1

XC7S75

76,800

12,000

96,000

832

90

3,240

8

400

192

140

1

1

XC7S100

102,400

16,000

128,000

1,100

120

4,320

8

400

192

160

1

1

-1,-2

-1,-2,-1L

-1

-1,-2

-1,-2,-1L

-1

-1,-2

-1,-2,-1L

-1

-1,-2

-1,-2,-1L

-1

-1,-2

-1,-2,-1L

-1

-1,-2

-1,-2,-1L

-1

Available User I/O: 3.3V SelectIO™ HR I/O

100

100

100

100

100

100

150

150

100

210

100

250

338

400

338

400

Notes:

1.

Packages with the same last letter and number sequence, e.g., A484, are footprint compatible with all other Spartan-7 devices with the same sequence. The footprint compatible devices within this family are outlined.

Page 2

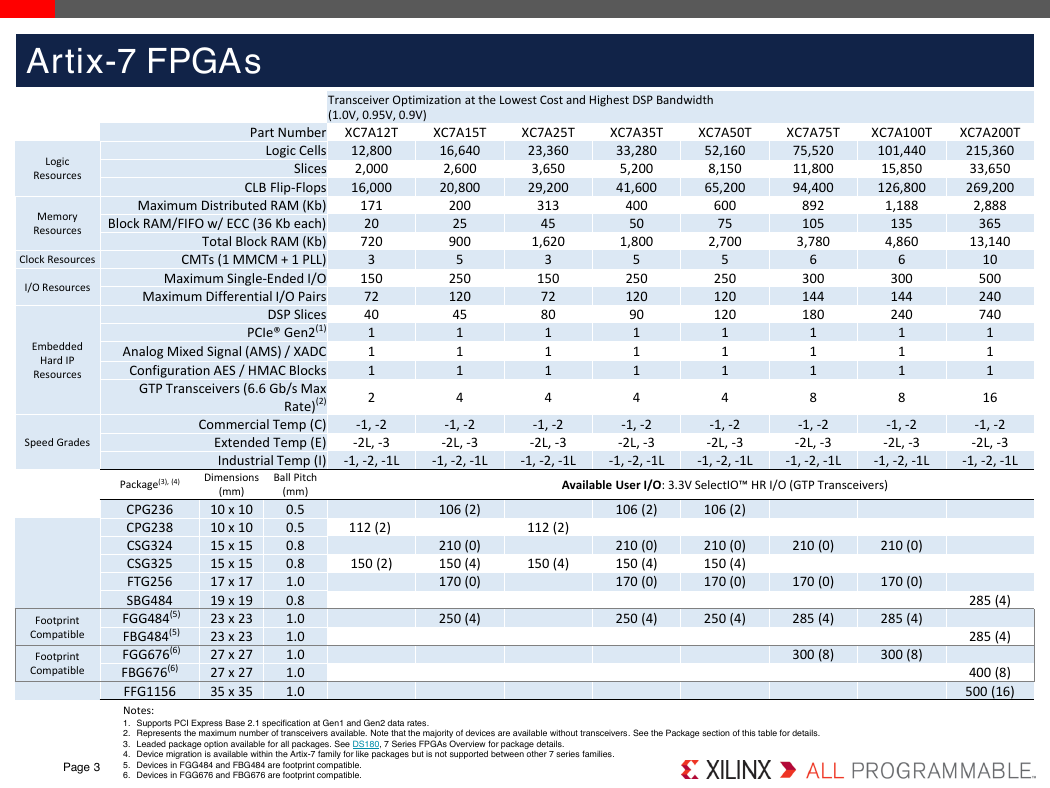

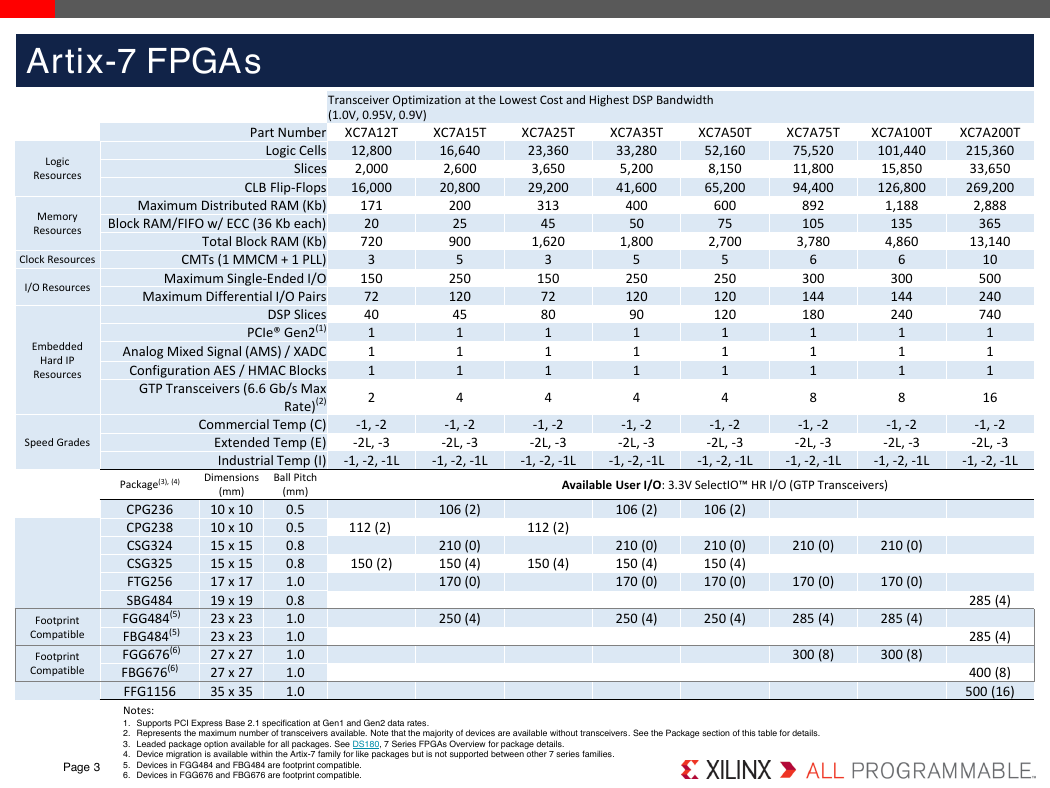

Artix-7 FPGAs

Transceiver Optimization at the Lowest Cost and Highest DSP Bandwidth

(1.0V, 0.95V, 0.9V)

Logic

Resources

Memory

Resources

Clock Resources

I/O Resources

Embedded

Hard IP

Resources

Speed Grades

Footprint

Compatible

Footprint

Compatible

Page 3

Part Number XC7A12T

12,800

2,000

16,000

Logic Cells

Slices

CLB Flip-Flops

Maximum Distributed RAM (Kb)

Block RAM/FIFO w/ ECC (36 Kb each)

Total Block RAM (Kb)

CMTs (1 MMCM + 1 PLL)

Maximum Single-Ended I/O

Maximum Differential I/O Pairs

DSP Slices

PCIe® Gen2(1)

Analog Mixed Signal (AMS) / XADC

Configuration AES / HMAC Blocks

GTP Transceivers (6.6 Gb/s Max

Rate)(2)

Commercial Temp (C)

Extended Temp (E)

Industrial Temp (I)

Package(3), (4)

Dimensions

Ball Pitch

(mm)

171

20

720

3

150

72

40

1

1

1

2

XC7A15T

16,640

2,600

20,800

200

25

900

5

250

120

45

1

1

1

4

XC7A25T

23,360

3,650

29,200

313

45

1,620

XC7A35T

33,280

5,200

41,600

400

50

1,800

3

150

72

80

1

1

1

4

5

250

120

90

1

1

1

4

XC7A50T

52,160

8,150

65,200

XC7A75T

75,520

11,800

94,400

XC7A100T

101,440

15,850

126,800

600

75

2,700

5

250

120

120

1

1

1

4

892

105

3,780

6

300

144

180

1

1

1

8

1,188

135

4,860

6

300

144

240

1

1

1

8

XC7A200T

215,360

33,650

269,200

2,888

365

13,140

10

500

240

740

1

1

1

16

-1, -2

-2L, -3

-1, -2

-2L, -3

-1, -2

-2L, -3

-1, -2

-2L, -3

-1, -2

-2L, -3

-1, -2

-2L, -3

-1, -2

-2L, -3

-1, -2

-2L, -3

-1, -2, -1L

-1, -2, -1L

-1, -2, -1L

-1, -2, -1L

-1, -2, -1L

-1, -2, -1L

-1, -2, -1L

-1, -2, -1L

Available User I/O: 3.3V SelectIO™ HR I/O (GTP Transceivers)

(mm)

0.5

0.5

0.8

0.8

1.0

0.8

1.0

1.0

1.0

1.0

1.0

106 (2)

112 (2)

150 (2)

112 (2)

150 (4)

106 (2)

106 (2)

210 (0)

150 (4)

170 (0)

10 x 10

10 x 10

15 x 15

15 x 15

17 x 17

19 x 19

23 x 23

23 x 23

27 x 27

27 x 27

35 x 35

CPG236

CPG238

CSG324

CSG325

FTG256

SBG484

FGG484(5)

FBG484(5)

FGG676(6)

FBG676(6)

FFG1156

Notes:

1. Supports PCI Express Base 2.1 specification at Gen1 and Gen2 data rates.

2. Represents the maximum number of transceivers available. Note that the majority of devices are available without transceivers. See the Package section of this table for details.

3. Leaded package option available for all packages. See DS180, 7 Series FPGAs Overview for package details.

4. Device migration is available within the Artix-7 family for like packages but is not supported between other 7 series families.

5. Devices in FGG484 and FBG484 are footprint compatible.

6. Devices in FGG676 and FBG676 are footprint compatible.

210 (0)

150 (4)

170 (0)

210 (0)

150 (4)

170 (0)

250 (4)

250 (4)

250 (4)

285 (4)

210 (0)

170 (0)

300 (8)

210 (0)

170 (0)

285 (4)

300 (8)

285 (4)

285 (4)

400 (8)

500 (16)

�

Kintex-7 FPGAs

Optimized for Best Price-Performance

(1.0V, 0.95V, 0.9V)

—

10,250

65,600

82,000

838

135

4,860

6

300

144

240

1

1

1

8

-1, -2

-2L, -3

-1, -2

Part Number

EasyPath™ Cost Reduction Solutions(1)

Slices

Logic Cells

CLB Flip-Flops

Maximum Distributed RAM (Kb)

Block RAM/FIFO w/ ECC (36 Kb each)

Total Block RAM (Kb)

CMTs (1 MMCM + 1 PLL)

Maximum Single-Ended I/O

Maximum Differential I/O Pairs

DSP48 Slices

PCIe® Gen2(2)

Analog Mixed Signal (AMS) / XADC

Configuration AES / HMAC Blocks

GTX Transceivers (12.5 Gb/s Max Rate)

Commercial Temp (C)

Extended Temp (E)

Industrial Temp (I)

Package(3)

FBG484(4)

FBG676(4)

FFG676

FBG900(4)

FFG900

FFG901

FFG1156

Dimensions

Ball Pitch

(mm)

23 x 23

27 x 27

27 x 27

31 x 31

31 x 31

31 x 31

35 x 35

(mm)

1.0

1.0

1.0

1.0

1.0

1.0

1.0

Logic Resources

Memory

Resources

Clock Resources

I/O Resources

Integrated IP

Resources

Speed Grades

Footprint

Compatible

Footprint

Compatible

Page 4

XC7K70T

XC7K160T

XC7K325T

XCE7K325T

XC7K355T

XCE7K355T

XC7K410T

XCE7K410T

XC7K420T

XCE7K420T

XC7K480T

XCE7K480T

—

25,350

162,240

202,800

2,188

325

11,700

8

400

192

600

1

1

1

8

50,950

326,080

407,600

4,000

445

16,020

10

500

240

840

1

1

1

16

-1, -2

-2L, -3

-1, -2

-2L, -3

55,650

356,160

445,200

5,088

715

25,740

6

300

144

1,440

1

1

1

24

-1, -2

-2L, -3

63,550

406,720

508,400

5,663

795

28,620

10

500

240

1,540

1

1

1

16

-1, -2

-2L, -3

65,150

416,960

521,200

5,938

835

30,060

8

400

192

1,680

1

1

1

32

-1, -2

-2L, -3

74,650

477,760

597,200

6,788

955

34,380

8

400

192

1,920

1

1

1

32

-1, -2

-2L, -3

-1, -2, -2L

-1, -2, -2L

-1, -2, -2L

-1, -2, -2L

-1, -2, -2L

-1, -2, -2L

185, 100 (4)

200, 100 (8)

185, 100 (4)

250, 150 (8)

250, 150 (8)

Available User I/O: 3.3V HR I/O, 1.8V HP I/Os (GTX)

250, 150 (8)

250, 150 (8)

350, 150 (16)

350, 150 (16)

250, 150 (8)

250, 150 (8)

350, 150 (16)

350, 150 (16)

300, 0 (24)

380, 0 (28)

400, 0 (32)

380, 0 (28)

400, 0 (32)

Notes:

1.

2.

3.

4.

EasyPath™ solutions provide a fast and conversion-free path for cost reduction.

Hard block supports PCI Express Base 2.1 specification at Gen1 and Gen2 data rates. Gen3 supported with soft IP.

See DS180, 7 Series FPGAs Overview, for package details.

GTX transceivers in FB packages support the following maximum data rates: 10.3Gb/s in FBG484; 6.6Gb/s in FBG676 and FBG900. See DS182, Kintex-7 FPGAs Data Sheet: DC and AC

Switching Characteristics, for details.

�

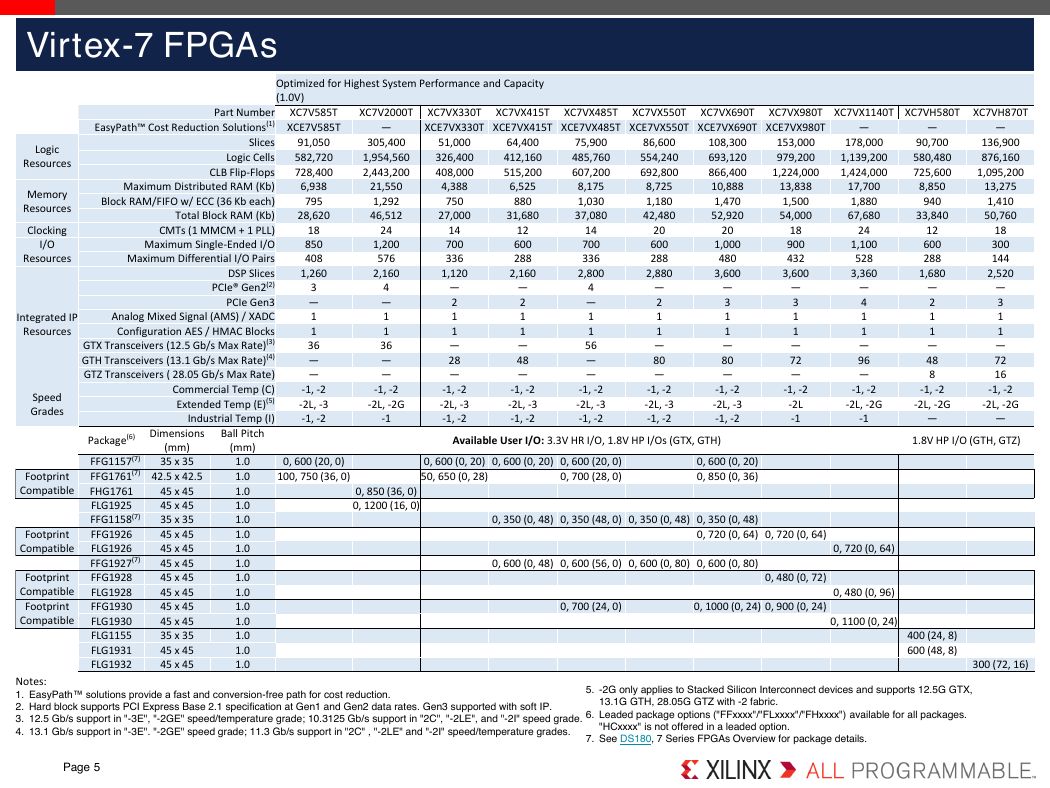

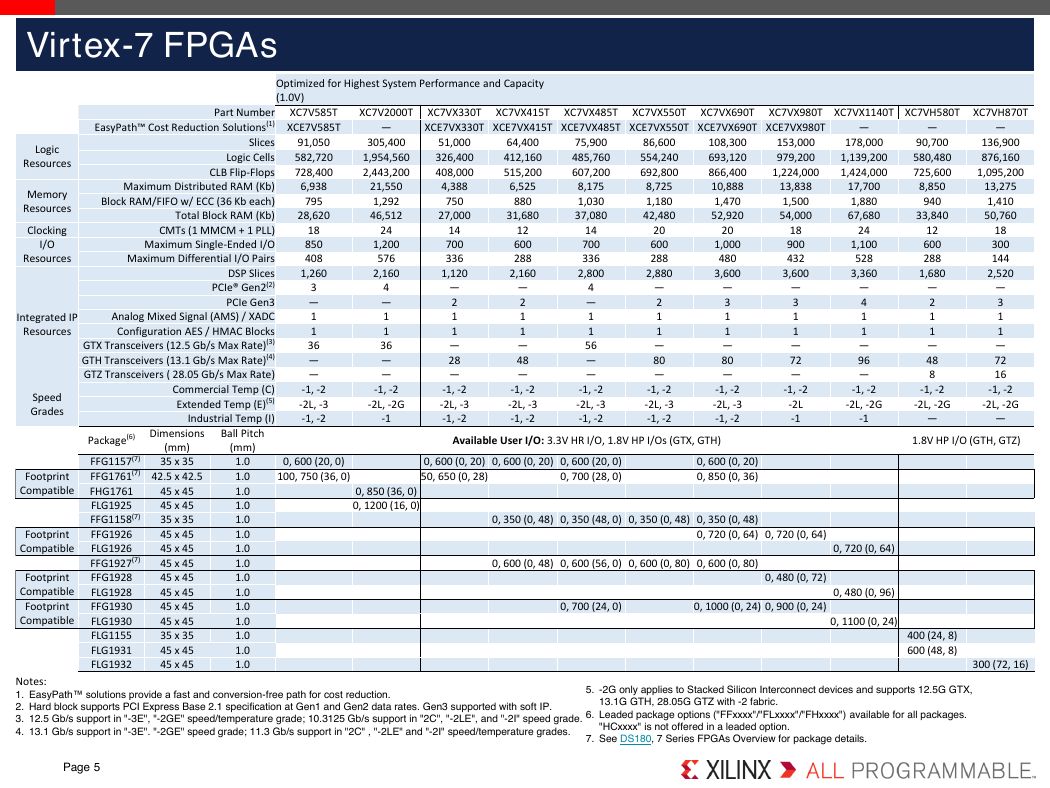

Virtex-7 FPGAs

Optimized for Highest System Performance and Capacity

(1.0V)

XC7V585T

EasyPath™ Cost Reduction Solutions(1) XCE7V585T

Part Number

XC7VX330T

XCE7VX330T XCE7VX415T XCE7VX485T XCE7VX550T XCE7VX690T XCE7VX980T

XC7VX415T

XC7VX690T

XC7VX485T

XC7VX550T

XC7VX980T XC7VX1140T XC7VH580T

XC7V2000T

—

305,400

1,954,560

2,443,200

21,550

1,292

46,512

24

1,200

576

2,160

4

—

1

1

36

—

—

91,050

582,720

728,400

6,938

795

28,620

18

850

408

1,260

3

—

1

1

36

—

—

51,000

326,400

408,000

4,388

750

27,000

14

700

336

1,120

—

2

1

1

—

28

—

64,400

412,160

515,200

6,525

880

31,680

12

600

288

2,160

—

2

1

1

—

48

—

75,900

485,760

607,200

8,175

1,030

37,080

14

700

336

2,800

4

—

1

1

56

—

—

86,600

554,240

692,800

8,725

1,180

42,480

20

600

288

2,880

—

2

1

1

—

80

—

108,300

693,120

866,400

10,888

1,470

52,920

20

1,000

480

3,600

—

3

1

1

—

80

—

153,000

979,200

1,224,000

13,838

1,500

54,000

18

900

432

3,600

—

3

1

1

—

72

—

-1, -2

-2L

-1

—

178,000

1,139,200

1,424,000

17,700

1,880

67,680

24

1,100

528

3,360

—

4

1

1

—

96

—

-1, -2

-2L, -2G

-1

—

90,700

580,480

725,600

8,850

940

33,840

12

600

288

1,680

—

2

1

1

—

48

8

XC7VH870T

—

136,900

876,160

1,095,200

13,275

1,410

50,760

18

300

144

2,520

—

3

1

1

—

72

16

-1, -2

-2L, -2G

—

-1, -2

-2L, -2G

—

1.8V HP I/O (GTH, GTZ)

400 (24, 8)

600 (48, 8)

300 (72, 16)

Logic

Resources

Memory

Resources

Clocking

I/O

Resources

Integrated IP

Resources

Speed

Grades

Footprint

Compatible

Footprint

Compatible

Footprint

Compatible

Footprint

Compatible

Slices

Logic Cells

CLB Flip-Flops

Maximum Distributed RAM (Kb)

Block RAM/FIFO w/ ECC (36 Kb each)

Total Block RAM (Kb)

CMTs (1 MMCM + 1 PLL)

Maximum Single-Ended I/O

Maximum Differential I/O Pairs

DSP Slices

PCIe® Gen2(2)

PCIe Gen3

Analog Mixed Signal (AMS) / XADC

Configuration AES / HMAC Blocks

GTX Transceivers (12.5 Gb/s Max Rate)(3)

GTH Transceivers (13.1 Gb/s Max Rate)(4)

GTZ Transceivers ( 28.05 Gb/s Max Rate)

Commercial Temp (C)

Extended Temp (E)(5)

Industrial Temp (I)

Dimensions

Ball Pitch

Package(6)

(mm)

35 x 35

FFG1157(7)

FFG1761(7) 42.5 x 42.5

FHG1761

FLG1925

FFG1158(7)

FFG1926

FLG1926

FFG1927(7)

FFG1928

FLG1928

FFG1930

FLG1930

FLG1155

FLG1931

FLG1932

45 x 45

45 x 45

35 x 35

45 x 45

45 x 45

45 x 45

45 x 45

45 x 45

45 x 45

45 x 45

35 x 35

45 x 45

45 x 45

(mm)

1.0

1.0

1.0

1.0

1.0

1.0

1.0

1.0

1.0

1.0

1.0

1.0

1.0

1.0

1.0

-1, -2

-2L, -3

-1, -2

-1, -2

-2L, -2G

-1

-1, -2

-2L, -3

-1, -2

-1, -2

-2L, -3

-1, -2

-1, -2

-2L, -3

-1, -2

-1, -2

-2L, -3

-1, -2

-1, -2

-2L, -3

-1, -2

Available User I/O: 3.3V HR I/O, 1.8V HP I/Os (GTX, GTH)

0, 600 (20, 0)

100, 750 (36, 0)

0, 600 (0, 20) 0, 600 (0, 20) 0, 600 (20, 0)

50, 650 (0, 28)

0, 700 (28, 0)

0, 600 (0, 20)

0, 850 (0, 36)

0, 850 (36, 0)

0, 1200 (16, 0)

0, 350 (0, 48) 0, 350 (48, 0) 0, 350 (0, 48) 0, 350 (0, 48)

0, 720 (0, 64) 0, 720 (0, 64)

0, 600 (0, 48) 0, 600 (56, 0) 0, 600 (0, 80) 0, 600 (0, 80)

0, 480 (0, 72)

0, 700 (24, 0)

0, 1000 (0, 24) 0, 900 (0, 24)

0, 720 (0, 64)

0, 480 (0, 96)

0, 1100 (0, 24)

Notes:

1. EasyPath™ solutions provide a fast and conversion-free path for cost reduction.

2. Hard block supports PCI Express Base 2.1 specification at Gen1 and Gen2 data rates. Gen3 supported with soft IP.

3. 12.5 Gb/s support in "-3E", "-2GE" speed/temperature grade; 10.3125 Gb/s support in "2C", "-2LE", and "-2I" speed grade.

4. 13.1 Gb/s support in "-3E". "-2GE" speed grade; 11.3 Gb/s support in "2C" , "-2LE" and "-2I" speed/temperature grades.

5. -2G only applies to Stacked Silicon Interconnect devices and supports 12.5G GTX,

13.1G GTH, 28.05G GTZ with -2 fabric.

6. Leaded package options ("FFxxxx"/"FLxxxx"/"FHxxxx") available for all packages.

"HCxxxx" is not offered in a leaded option.

7. See DS180, 7 Series FPGAs Overview for package details.

Page 5

�

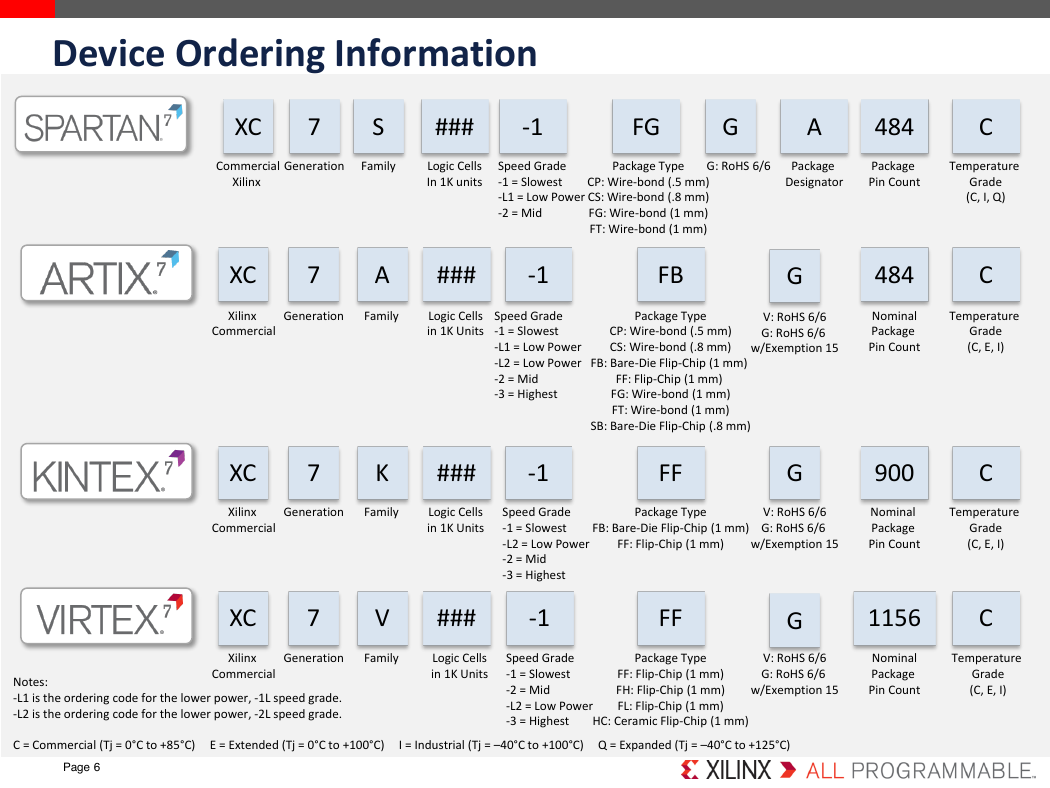

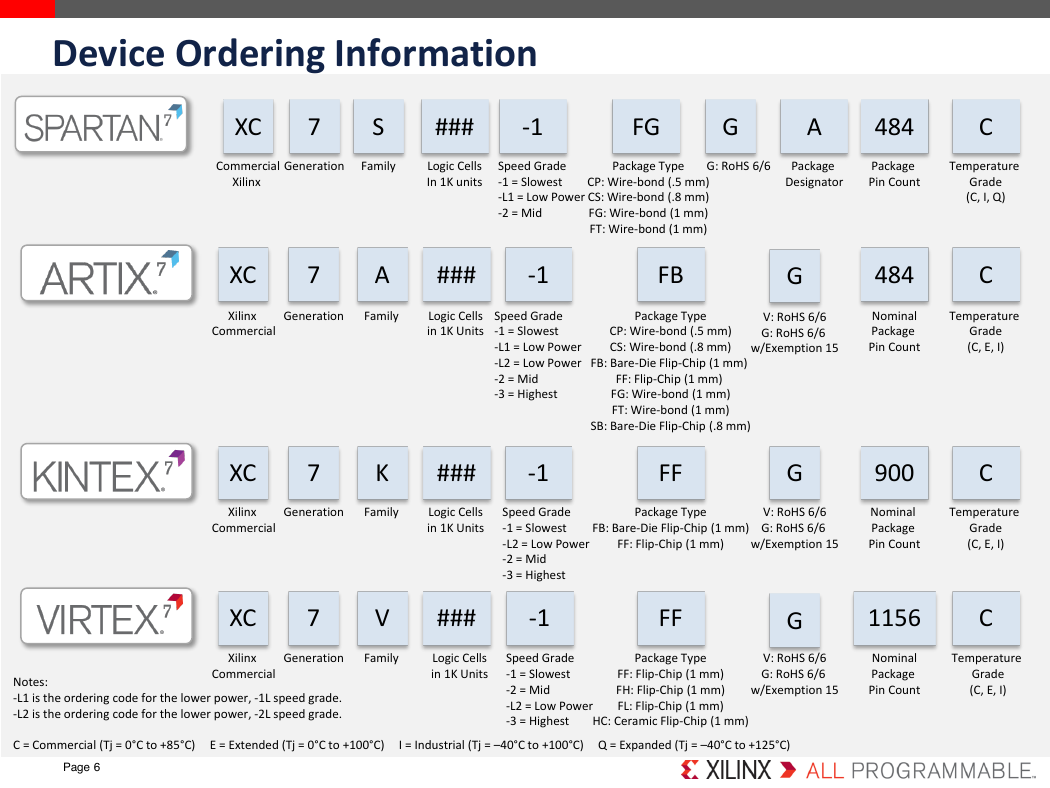

Device Ordering Information

XC

7

S

###

-1

FG

G

A

484

C

Commercial

Generation

Family

Xilinx

Logic Cells

In 1K units

Speed Grade

-1 = Slowest

-L1 = Low Power

-2 = Mid

Package Type

G: RoHS 6/6

CP: Wire-bond (.5 mm)

CS: Wire-bond (.8 mm)

FG: Wire-bond (1 mm)

FT: Wire-bond (1 mm)

Package

Designator

Package

Pin Count

Temperature

Grade

(C, I, Q)

XC

7

A

###

-1

FB

G

484

C

Xilinx

Generation

Family

Commercial

Logic Cells

in 1K Units

Speed Grade

-1 = Slowest

-L1 = Low Power

-L2 = Low Power

-2 = Mid

-3 = Highest

Package Type

CP: Wire-bond (.5 mm)

CS: Wire-bond (.8 mm)

V: RoHS 6/6

G: RoHS 6/6

w/Exemption 15

Nominal

Package

Pin Count

Temperature

Grade

(C, E, I)

FB: Bare-Die Flip-Chip (1 mm)

FF: Flip-Chip (1 mm)

FG: Wire-bond (1 mm)

FT: Wire-bond (1 mm)

SB: Bare-Die Flip-Chip (.8 mm)

XC

7

K

###

-1

FF

G

Xilinx

Generation

Family

Commercial

Logic Cells

in 1K Units

Package Type

FB: Bare-Die Flip-Chip (1 mm)

V: RoHS 6/6

G: RoHS 6/6

FF: Flip-Chip (1 mm)

w/Exemption 15

Speed Grade

-1 = Slowest

-L2 = Low Power

-2 = Mid

-3 = Highest

XC

7

V

###

-1

FF

G

Notes:

-L1 is the ordering code for the lower power, -1L speed grade.

-L2 is the ordering code for the lower power, -2L speed grade.

Commercial

Xilinx

Generation

Family

Logic Cells

in 1K Units

Speed Grade

-1 = Slowest

-2 = Mid

-L2 = Low Power

-3 = Highest

Package Type

FF: Flip-Chip (1 mm)

FH: Flip-Chip (1 mm)

FL: Flip-Chip (1 mm)

V: RoHS 6/6

G: RoHS 6/6

w/Exemption 15

HC: Ceramic Flip-Chip (1 mm)

C = Commercial (Tj = 0°C to +85°C) E = Extended (Tj = 0°C to +100°C) I = Industrial (Tj = –40°C to +100°C) Q = Expanded (Tj = –40°C to +125°C)

Page 6

900

Nominal

Package

Pin Count

C

Temperature

Grade

(C, E, I)

1156

Nominal

Package

Pin Count

C

Temperature

Grade

(C, E, I)

�

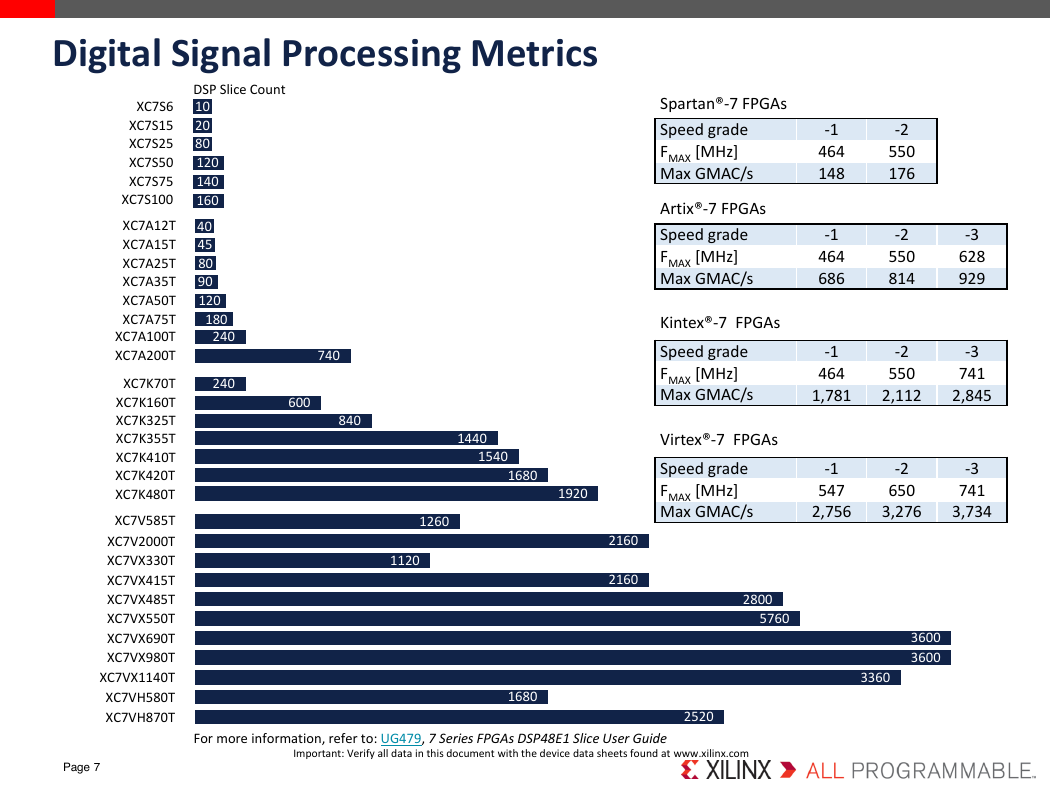

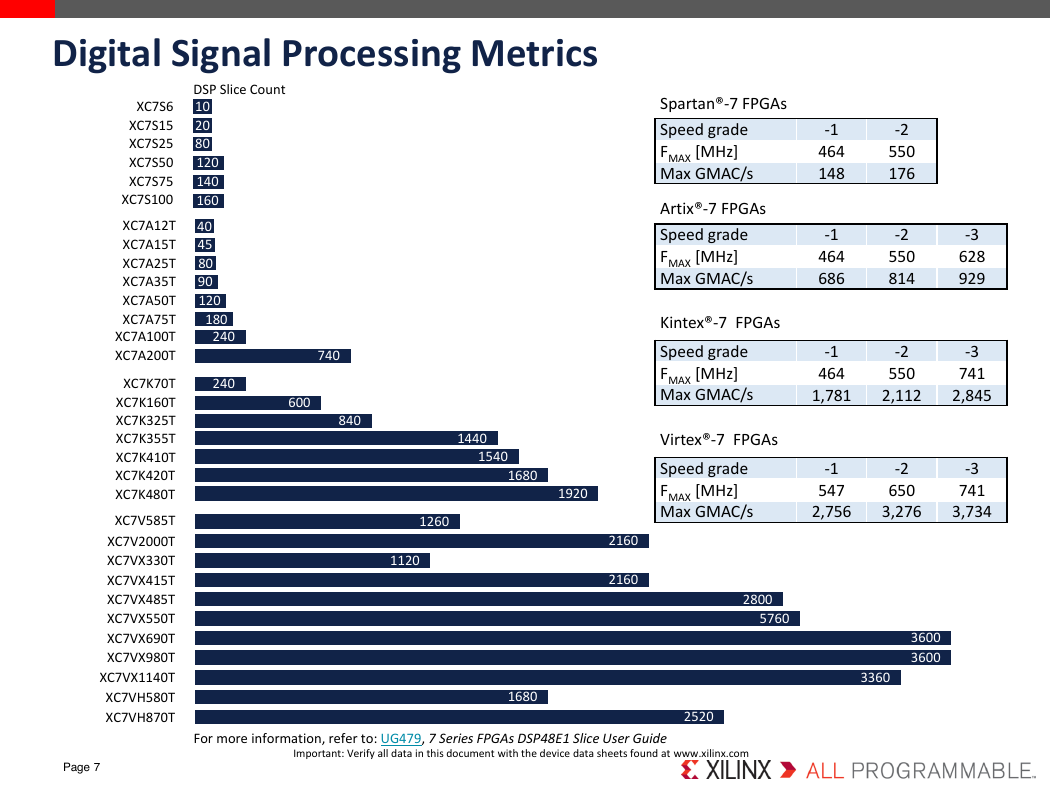

Digital Signal Processing Metrics

DSP Slice Count

10

20

80

120

140

160

40

45

80

90

120

180

240

240

740

600

840

XC7S6

XC7S15

XC7S25

XC7S50

XC7S75

XC7S100

XC7A12T

XC7A15T

XC7A25T

XC7A35T

XC7A50T

XC7A75T

XC7A100T

XC7A200T

XC7K70T

XC7K160T

XC7K325T

XC7K355T

XC7K410T

XC7K420T

XC7K480T

XC7V585T

XC7V2000T

XC7VX330T

XC7VX415T

XC7VX485T

XC7VX550T

XC7VX690T

XC7VX980T

XC7VX1140T

XC7VH580T

XC7VH870T

Spartan®-7 FPGAs

Speed grade

FMAX [MHz]

Max GMAC/s

Artix®-7 FPGAs

Speed grade

FMAX [MHz]

Max GMAC/s

Kintex®-7 FPGAs

Speed grade

FMAX [MHz]

Max GMAC/s

Virtex®-7 FPGAs

Speed grade

FMAX [MHz]

Max GMAC/s

-1

464

148

-1

464

686

-2

550

176

-2

550

814

-3

628

929

-1

464

1,781

-2

550

2,112

-3

741

2,845

-1

547

2,756

-2

650

3,276

-3

741

3,734

1440

1540

1680

1920

1260

1120

2160

2160

2800

5760

3600

3600

3360

1680

2520

For more information, refer to: UG479, 7 Series FPGAs DSP48E1 Slice User Guide

Important: Verify all data in this document with the device data sheets found at www.xilinx.com

Page 7

�

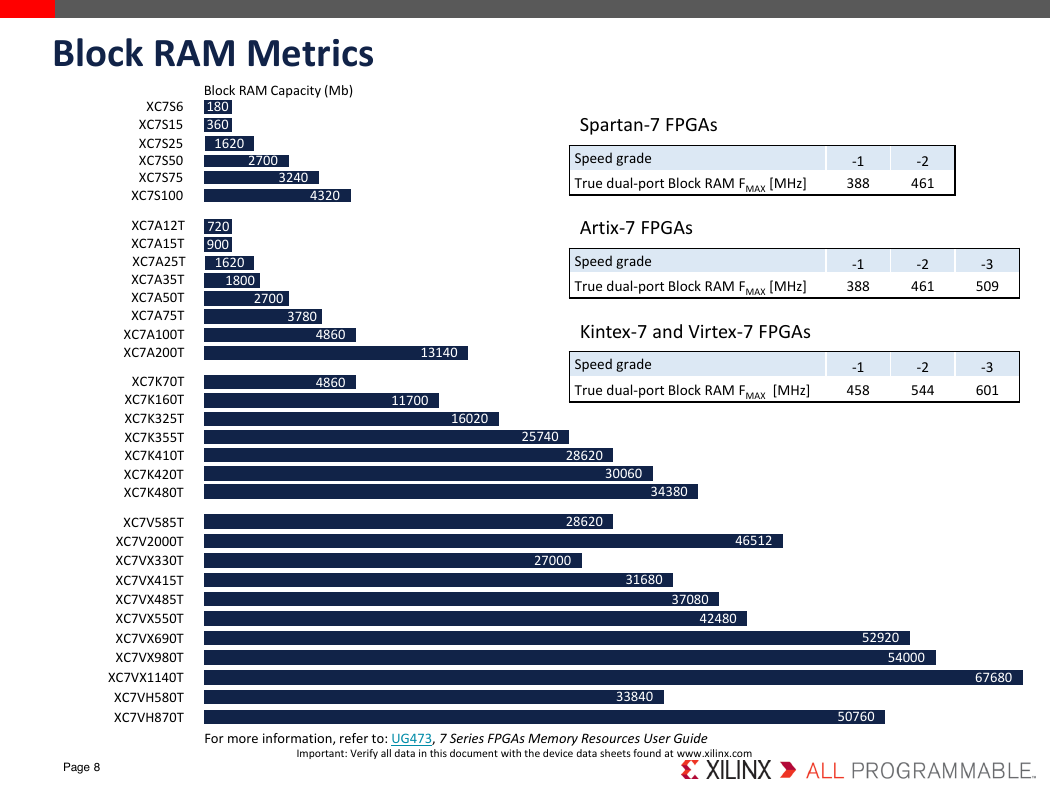

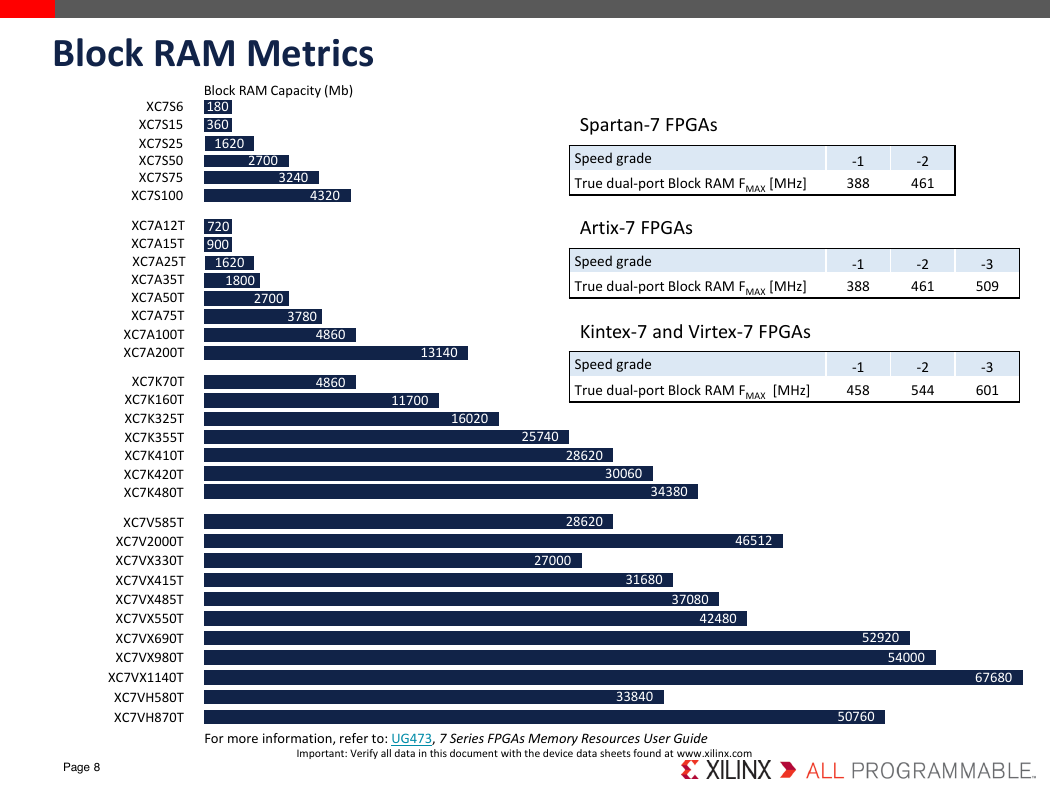

Block RAM Metrics

XC7S6

XC7S15

XC7S25

XC7S50

XC7S75

XC7S100

XC7A12T

XC7A15T

XC7A25T

XC7A35T

XC7A50T

XC7A75T

XC7A100T

XC7A200T

XC7K70T

XC7K160T

XC7K325T

XC7K355T

XC7K410T

XC7K420T

XC7K480T

XC7V585T

XC7V2000T

XC7VX330T

XC7VX415T

XC7VX485T

XC7VX550T

XC7VX690T

XC7VX980T

XC7VX1140T

XC7VH580T

XC7VH870T

Block RAM Capacity (Mb)

180

360

1620

2700

3240

4320

720

900

1620

1800

2700

3780

4860

4860

13140

11700

16020

Spartan-7 FPGAs

Speed grade

True dual-port Block RAM FMAX [MHz]

Artix-7 FPGAs

Speed grade

True dual-port Block RAM FMAX [MHz]

Kintex-7 and Virtex-7 FPGAs

-1

388

-1

388

-2

461

-2

461

-3

509

Speed grade

True dual-port Block RAM FMAX [MHz]

-1

458

-2

544

-3

601

25740

28620

30060

34380

28620

27000

46512

31680

37080

42480

33840

52920

54000

67680

50760

Page 8

For more information, refer to: UG473, 7 Series FPGAs Memory Resources User Guide

Important: Verify all data in this document with the device data sheets found at www.xilinx.com

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc