The Art of Multiprocessor Programming

Copyright Page

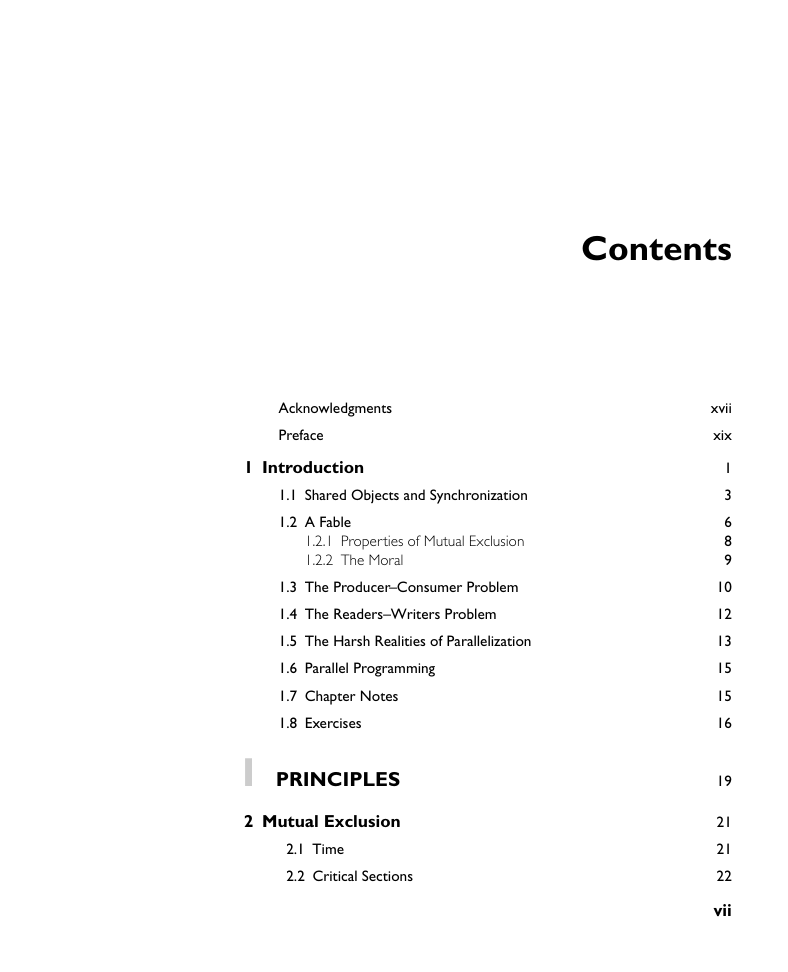

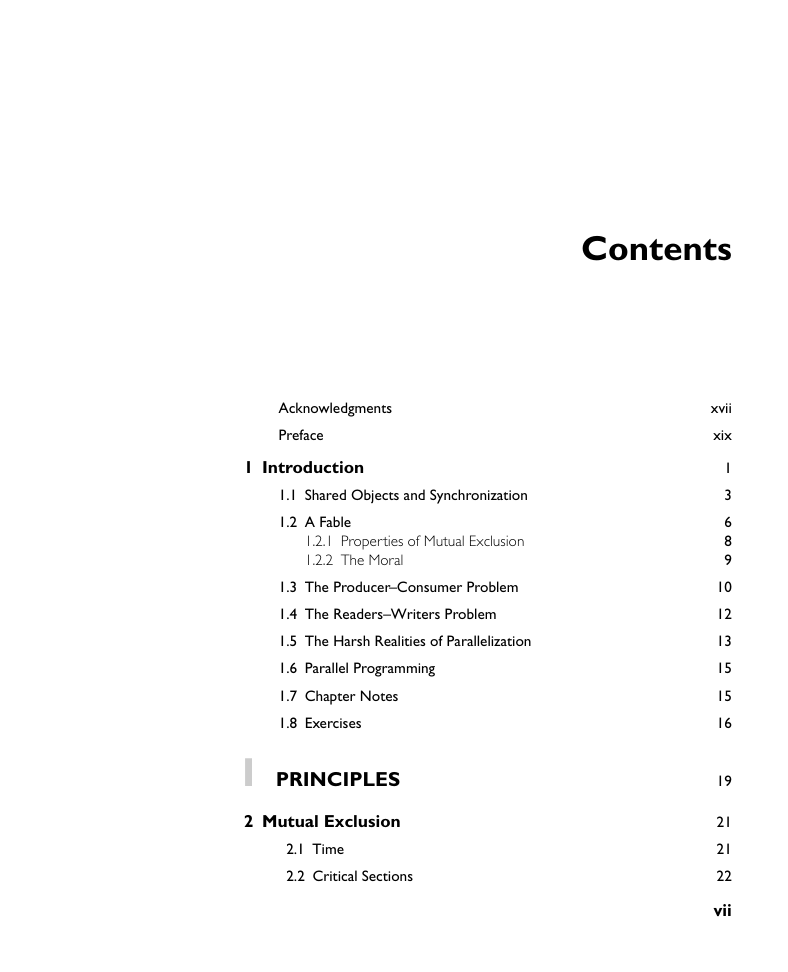

Table of Contents

Acknowledgments

Preface

Chapter 1. Introduction

1.1 Shared Objects and Synchronization

1.2 A Fable

1.3 The Producer–Consumer Problem

1.4 The Readers–Writers Problem

1.5 The Harsh Realities of Parallelization

1.6 Parallel Programming

1.7 Chapter Notes

1.8 Exercises

Part I: Principles

Chapter 2. Mutual Exclusion

2.1 Time

2.2 Critical Sections

2.3 2-Thread Solutions

2.4 The Filter Lock

2.5 Fairness

2.6 Lamport’s Bakery Algorithm

2.7 Bounded Timestamps

2.8 Lower Bounds on the Number of Locations

2.9 Chapter Notes

2.10 Exercises

Chapter 3. Concurrent Objects

3.1 Concurrency and Correctness

3.2 Sequential Objects

3.3 Quiescent Consistency

3.4 Sequential Consistency

3.5 Linearizability

3.6 Formal Definitions

3.7 Progress Conditions

3.8 The Java Memory Model

3.9 Remarks

3.10 Chapter Notes

3.11 Exercises

Chapter 4. Foundations of Shared Memory

4.1 The Space of Registers

4.2 Register Constructions

4.3 Atomic Snapshots

4.4 Chapter Notes

4.5 Exercises

Chapter 5. The Relative Power of Primitive Synchronization Operations

5.1 Consensus Numbers

5.2 Atomic Registers

5.3 Consensus Protocols

5.4 FIFO Queues

5.5 Multiple Assignment Objects

5.6 Read–Modify–Write Operations

5.7 Common2 RMW Operations

5.8 The compareAndSet() Operation

5.9 Chapter Notes

5.10 Exercises

Chapter 6. Universality of Consensus

6.1 Introduction

6.2 Universality

6.3 A Lock-Free Universal Construction

6.4 A Wait-Free Universal Construction

6.5 Chapter Notes

6.6 Exercises

Part II: Practice

Chapter 7. Spin Locks and Contention

7.1 Welcome to the Real World

7.2 Test-And-Set Locks

7.3 TAS-Based Spin Locks Revisited

7.4 Exponential Backoff

7.5 Queue Locks

7.6 A Queue Lock with Timeouts

7.7 A Composite Lock

7.8 Hierarchical Locks

7.9 One Lock To Rule Them All

7.10 Chapter Notes

7.11 Exercises

Chapter 8. Monitors and Blocking Synchronization

8.1 Introduction

8.2 Monitor Locks and Conditions

8.3 Readers–Writers Locks

8.4 Our Own Reentrant Lock

8.5 Semaphores

8.6 Chapter Notes

8.7 Exercises

Chapter 9. Linked Lists: The Role of Locking

9.1 Introduction

9.2 List-Based Sets

9.3 Concurrent Reasoning

9.4 Coarse-Grained Synchronization

9.5 Fine-Grained Synchronization

9.6 Optimistic Synchronization

9.7 Lazy Synchronization

9.8 Non-Blocking Synchronization

9.9 Discussion

9.10 Chapter Notes

9.11 Exercises

Chapter 10. Concurrent Queues and the ABA Problem

10.1 Introduction

10.2 Queues

10.3 A Bounded Partial Queue

10.4 An Unbounded Total Queue

10.5 An Unbounded Lock-Free Queue

10.6 Memory Reclamation and the ABA Problem

10.7 Dual Data Structures

10.8 Chapter Notes

10.9 Exercises

Chapter 11. Concurrent Stacks and Elimination

11.1 Introduction

11.2 An Unbounded Lock-Free Stack

11.3 Elimination

11.4 The Elimination Backoff Stack

11.5 Chapter Notes

11.6 Exercises

Chapter 12. Counting, Sorting, and Distributed Coordination

12.1 Introduction

12.2 Shared Counting

12.3 Software Combining

12.4 Quiescently Consistent Pools and Counters

12.5 Counting Networks

12.6 Diffracting Trees

12.7 Parallel Sorting

12.8 Sorting Networks

12.9 Sample Sorting

12.10 Distributed Coordination

12.11 Chapter Notes

12.12 Exercises

Chapter 13. Concurrent Hashing and Natural Parallelism

13.1 Introduction

13.2 Closed-Address Hash Sets

13.3 A Lock-Free Hash Set

13.4 An Open-Addressed Hash Set

13.5 Chapter Notes

13.6 Exercises

Chapter 14. Skiplists and Balanced Search

14.1 Introduction

14.2 Sequential Skiplists

14.3 A Lock-Based Concurrent Skiplist

14.4 A Lock-Free Concurrent Skiplist

14.5 Concurrent Skiplists

14.6 Chapter Notes

14.7 Exercises

Chapter 15. Priority Queues

15.1 Introduction

15.2 An Array-Based Bounded Priority Queue

15.3 A Tree-Based Bounded Priority Queue

15.4 An Unbounded Heap-Based Priority Queue

15.5 A Skiplist-Based Unbounded Priority Queue

15.6 Chapter Notes

15.7 Exercises

Chapter 16. Futures, Scheduling, and Work Distribution

16.1 Introduction

16.2 Analyzing Parallelism

16.3 Realistic Multiprocessor Scheduling

16.4 Work Distribution

16.5 Work-Stealing Dequeues

16.6 Chapter Notes

16.7 Exercises

Chapter 17. Barriers

17.1 Introduction

17.2 Barrier Implementations

17.3 Sense-Reversing Barrier

17.4 Combining Tree Barrier

17.5 Static Tree Barrier

17.6 Termination Detecting Barriers

17.7 Chapter Notes

17.8 Exercises

Chapter 18. Transactional Memory

18.1 Introduction

18.2 Transactions and Atomicity

18.3 Software Transactional Memory

18.4 Hardware Transactional Memory

18.5 Chapter Notes

18.6 Exercises

Part III: Appendix

Appendix A. Software Basics

A.1 Introduction

A.2 Java

A.3 C#

A.4 Pthreads

A.5 Chapter Notes

Appendix B. Hardware Basics

B.1 Introduction (and a Puzzle)

B.2 Processors and Threads

B.3 Interconnect

B.4 Memory

B.5 Caches

B.6 Cache-Conscious Programming, or the Puzzle Solved

B.7 Multi-Core and Multi-Threaded Architectures

B.8 Hardware Synchronization Instructions

B.9 Chapter Notes

B.10 Exercises

Bibliography

Index

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc