数字电子技术基础试卷(本科)及参考答案

试卷七

一、选择题(每小题 2 分,共 16 分)

6.TTL 与非门在电路中使用时,多余输入端的处理一般是(

)。

a. 悬空

b. 通过一合适电阻接地

c. 通过一合适电阻接电源

7.欲用两输入与非门构成一个二—十进制译码器,最少要用(

)两输入与非门。

a. 16

b. 20

c. 28

d. 44

8.用六管静态存储单元构成 1024bit 的 RAM,如果输出为 Y1Y2,则地址为(

),

MOS 管的个数为(

a. A0~ A7

)。

b. A0~ A8

c. A0~ A9

d. 4096

e. 6144

f. 8192

七、(15 分)设计一个将余 3BCD 码转换为余 3 循环 BCD 码(修改的格雷码,“0”的

码组为“0010”)的码制变换电路。画出用与非门组成的逻辑电路图。

八、(15 分)试用 74161 和尽量少的门电路设计一个秒计数器,(在 60 秒时产生分进位

信号)。

试卷七参考答案

一、

6. c

7.d

8.b,e

七、

1.设输入为 A、B、C、D,输出为 W、X、Y、Z,余 3 BCD 码转换为余 3 循环 BCD

码如表 A7 所示。

表 A7

输 入

余 3 码

A B C D

0 0 1 1

0 1 0 0

0 1 0 1

0 1 1 0

0 1 1 1

1 0 0 0

1 0 0 1

1 0 1 0

1 0 1 1

1 1 0 0

十进制数

0

1

2

3

4

5

6

7

8

9

输 出

余 3 循环码

W X Y Z

0 0 1 0

0 1 1 0

0 1 1 1

0 1 0 1

0 1 0 0

1 1 0 0

1 1 0 1

1 1 1 1

1 1 1 0

1 0 1 0

�

用卡诺图化简得输出的逻辑函数表达式分别为

X

AW ,

BABA

2.逻辑电路图(略)

CBCBY

DCDCZ

,

,

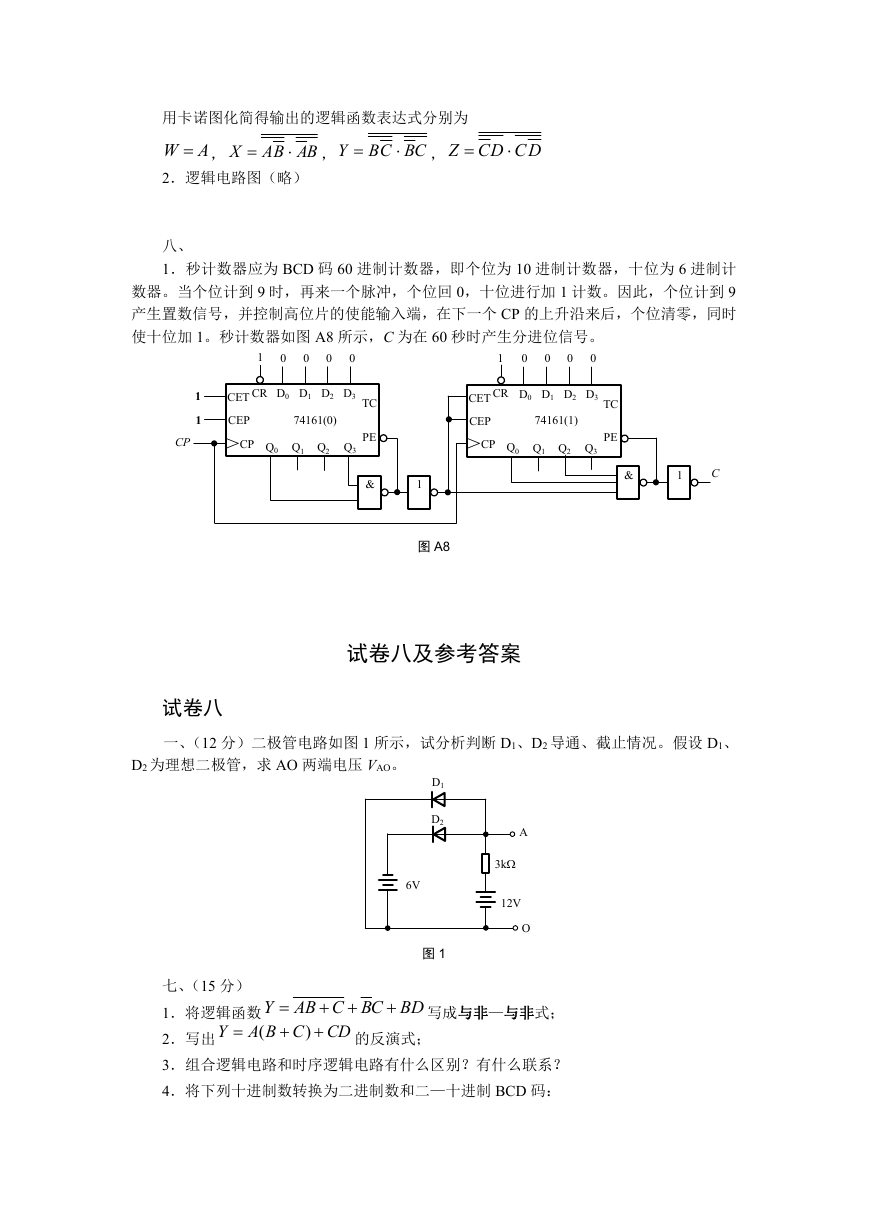

八、

1.秒计数器应为 BCD 码 60 进制计数器,即个位为 10 进制计数器,十位为 6 进制计

数器。当个位计到 9 时,再来一个脉冲,个位回 0,十位进行加 1 计数。因此,个位计到 9

产生置数信号,并控制高位片的使能输入端,在下一个 CP 的上升沿来后,个位清零,同时

使十位加 1。秒计数器如图 A8 所示,C 为在 60 秒时产生分进位信号。

0

D3

0

D0

D0

D3

CR

CR

TC

1

0

1

0

0

0

0

D1

74161(1)

0

D2

D1

74161(0)

D2

1

1

CP

CET

CEP

>

CP

&

1

C

CET

CEP

>

CP

TC

PE

Q0 Q1 Q2 Q3

Q0 Q1 Q2 Q3

PE

&

1

图 A8

试卷八及参考答案

试卷八

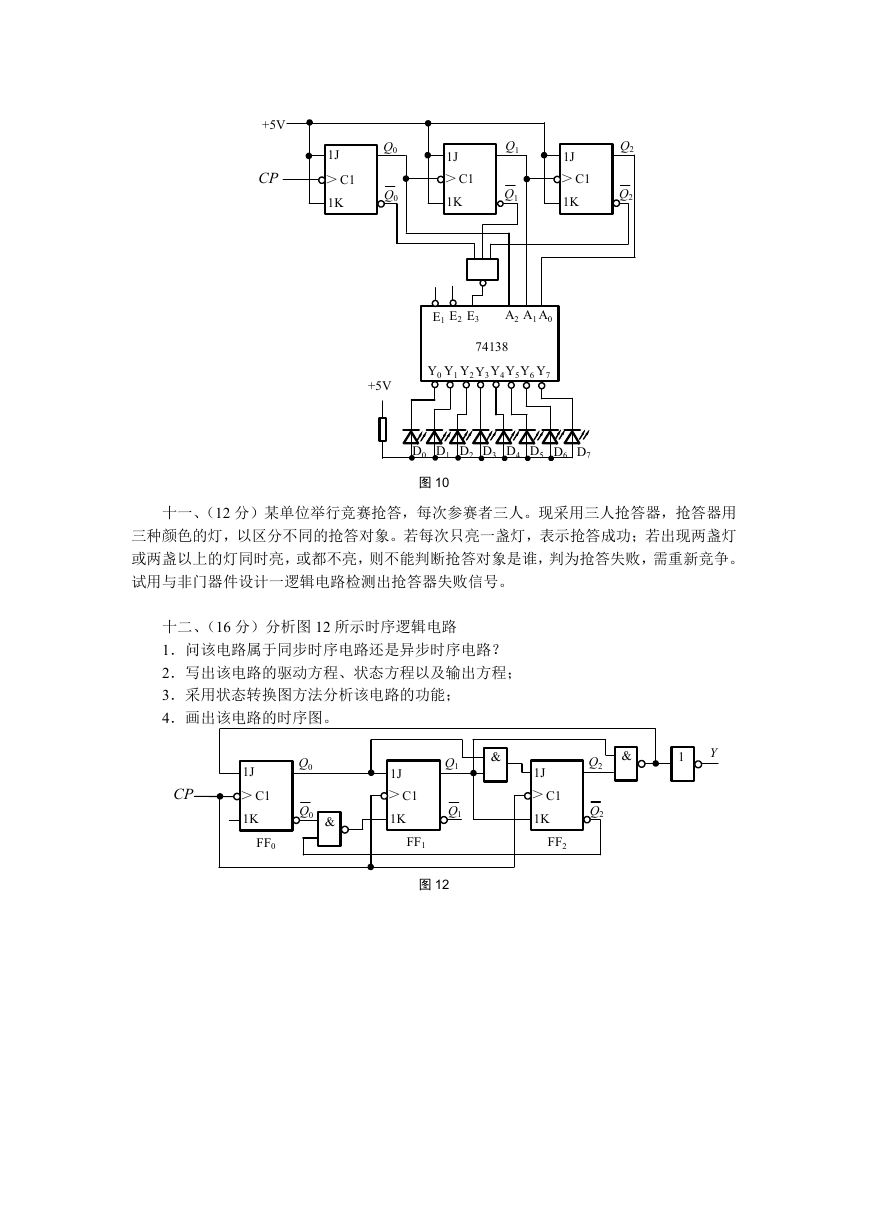

一、(12 分)二极管电路如图 1 所示,试分析判断 D1、D2 导通、截止情况。假设 D1、

D2 为理想二极管,求 AO 两端电压 VAO。

D1

D2

6V

图 1

A

3k

V

O

七、(15 分)

Y

1.将逻辑函数

(

CBA

2.写出

3.组合逻辑电路和时序逻辑电路有什么区别?有什么联系?

4.将下列十进制数转换为二进制数和二—十进制 BCD 码:

AB

CBC

)

CD

写成与非—与非式;

的反演式;

BD

Y

�

(1)10

(2)598

5.一个 n 位 D/A 转换器,可以达到的精度为多少?若一 D/A 转换器满刻度输出电压为

10V,当要求 1mV 的分辨率时,输入数字量的位数 n 至少应为多少?

八、(12 分)图 8 所示是一双相时钟发生器。设触发器的初始状态 Q=0。

1.分析该电路中 555 电路及周围元件构成什么电路;

2.画出 555 电路v3、v1 及v2 的波形;

3.计算该电路时钟频率。

R1

14.7k

R2

7.3k

vC

7

6

2

C

100pF

VCC

8

4

3

5

555

1

v3

1

1J

C1

>

1K

Q

Q

≥1

≥1

v1

v2

0.01F

图 8

九、(10 分)图 9 所示是用两个二进制计数器 74161 和一个 D 触发器 7474 组成的电路,

试分析该电路的功能。触发器输出信号 Q 与 CP 信号满足什么关系?

1

1

CP

1

0

0

0

0

CET

CEP

>

CP

CR

D0

D1

74161(0)

D2

D3

Q0 Q1 Q2 Q3

TC

PE

1

CET

CEP

>

CP

1

CR

0

D0

0

D1

74161(1)

0

D2

0

D3

Q0 Q1 Q2 Q3

TC

PE

1

Q

1D

C1 >

7474

图 9

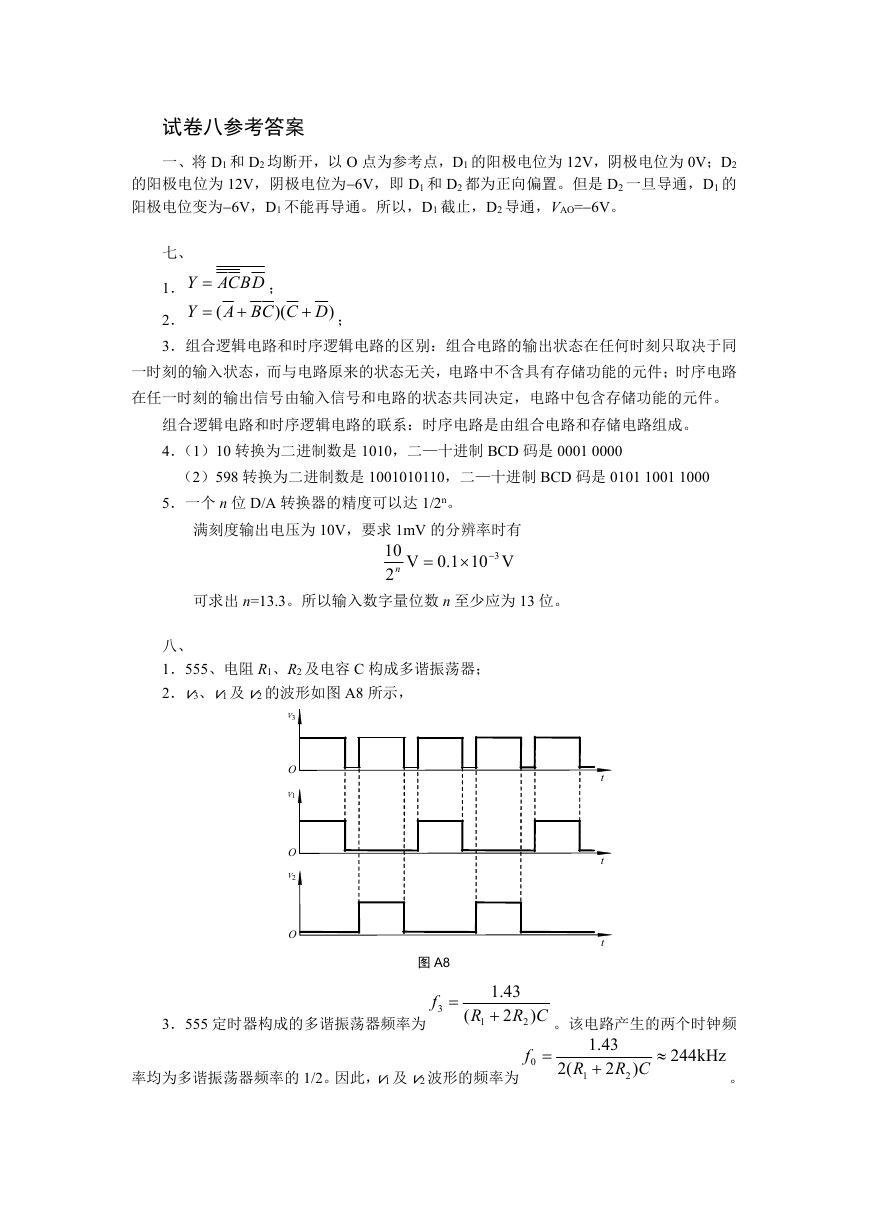

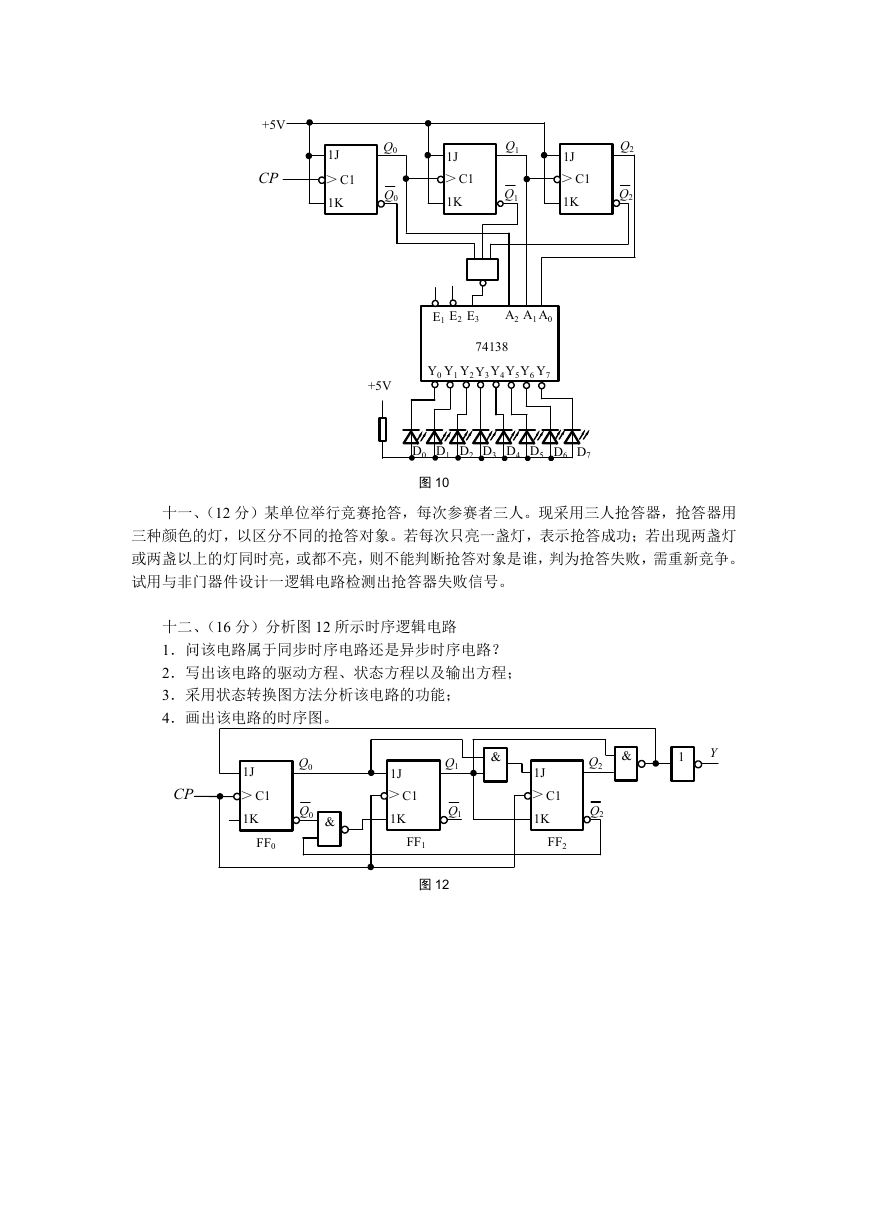

十、(10 分)用 74138 和 JK 触发器构成图 10 所示电路。

1.要使电路正常工作,请连接电路未完成部分;

2.当 CP 时钟端加时钟信号,JK 触发器组成的电路具有什么功能;

3. 电路 中的 LED 能 否发 光?D0~D7 闪 亮次 序如 何? 试加 以分 析。( 设初 始状 态

Q0=Q1=Q2=0)

�

+5V

CP

1J

>

1K

C1

Q0

Q0

1J

>

1K

C1

Q1

Q1

1J

>

1K

C1

Q2

Q2

E1 E2 E3

A2

A1

A0

74138

Y4

Y3

Y5

Y6

Y7

Y0

+5V

Y1

Y2

D0 D1 D2 D3 D4 D5 D6 D7

图 10

十一、(12 分)某单位举行竞赛抢答,每次参赛者三人。现采用三人抢答器,抢答器用

三种颜色的灯,以区分不同的抢答对象。若每次只亮一盏灯,表示抢答成功;若出现两盏灯

或两盏以上的灯同时亮,或都不亮,则不能判断抢答对象是谁,判为抢答失败,需重新竞争。

试用与非门器件设计一逻辑电路检测出抢答器失败信号。

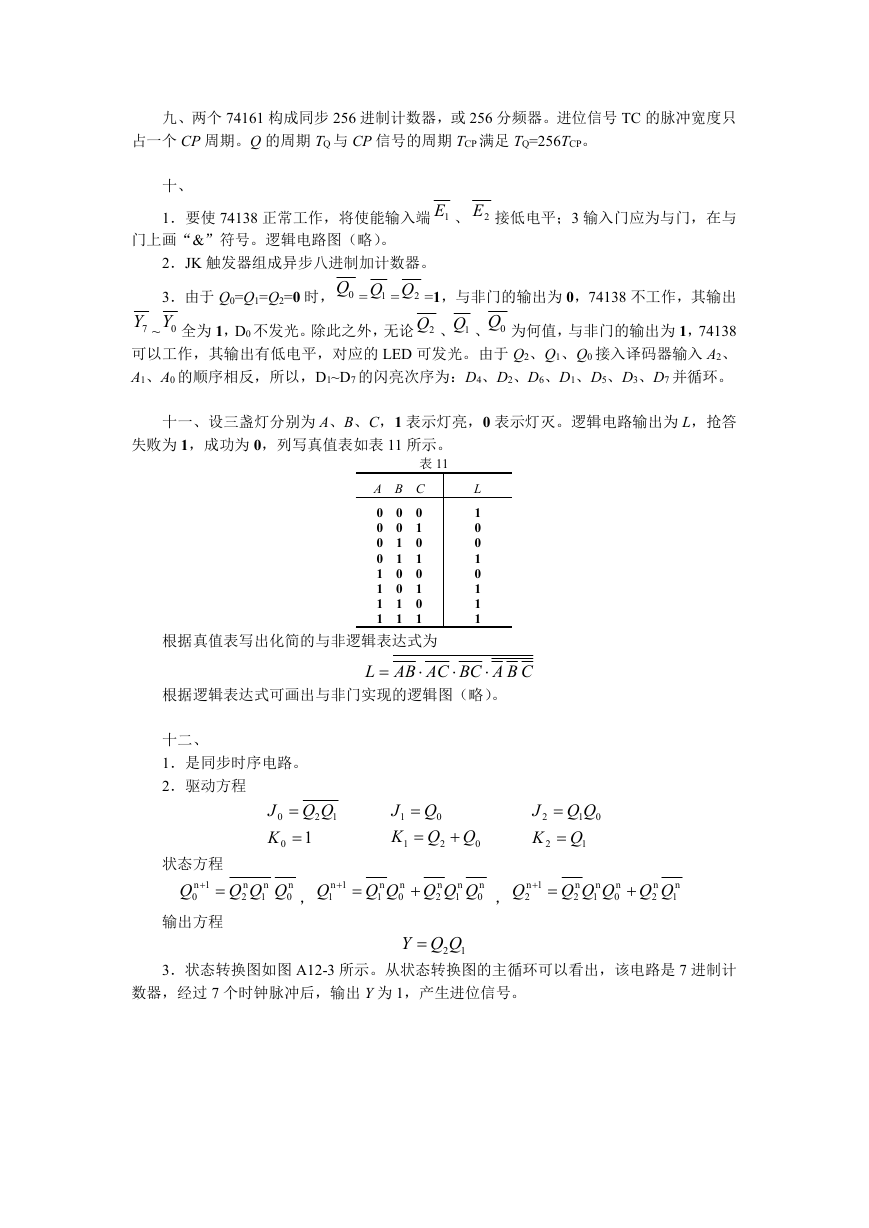

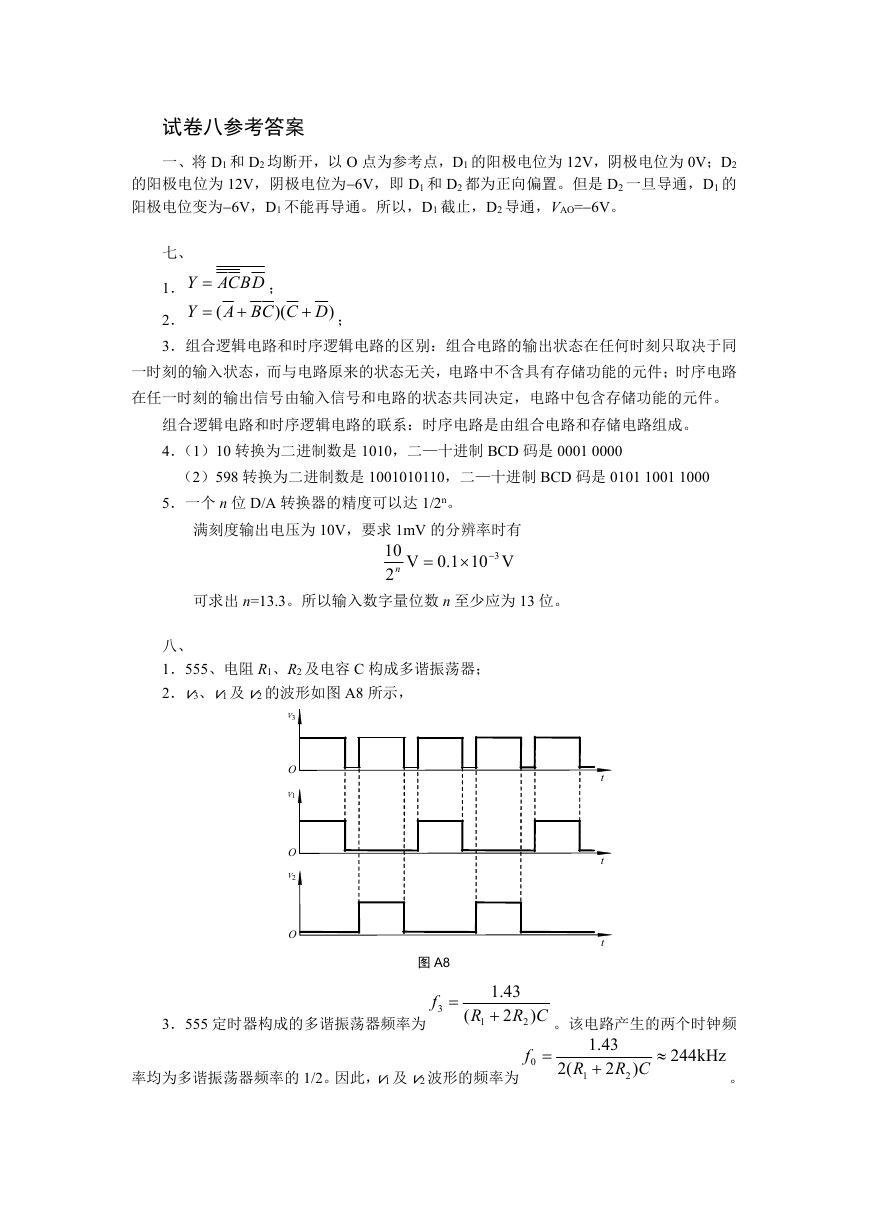

十二、(16 分)分析图 12 所示时序逻辑电路

1.问该电路属于同步时序电路还是异步时序电路?

2.写出该电路的驱动方程、状态方程以及输出方程;

3.采用状态转换图方法分析该电路的功能;

4.画出该电路的时序图。

CP

Q0

Q0

&

1J

>

1K

C1

FF0

Q1

Q1

1J

>

1K

C1

FF1

图 12

&

&

1

Y

Q2

Q2

1J

>

1K

C1

FF2

�

试卷八参考答案

一、将 D1 和 D2 均断开,以 O 点为参考点,D1 的阳极电位为 12V,阴极电位为 0V;D2

的阳极电位为 12V,阴极电位为6V,即 D1 和 D2 都为正向偏置。但是 D2 一旦导通,D1 的

阳极电位变为6V,D1 不能再导通。所以,D1 截止,D2 导通,VAO=6V。

七、

1.

Y

Y

DBCA

(

DCCBA

;

)(

)

2.

3.组合逻辑电路和时序逻辑电路的区别:组合电路的输出状态在任何时刻只取决于同

一时刻的输入状态,而与电路原来的状态无关,电路中不含具有存储功能的元件;时序电路

;

在任一时刻的输出信号由输入信号和电路的状态共同决定,电路中包含存储功能的元件。

组合逻辑电路和时序逻辑电路的联系:时序电路是由组合电路和存储电路组成。

4.(1)10 转换为二进制数是 1010,二—十进制 BCD 码是 0001 0000

(2)598 转换为二进制数是 1001010110,二—十进制 BCD 码是 0101 1001 1000

5.一个 n 位 D/A 转换器的精度可以达 1/2n。

满刻度输出电压为 10V,要求 1mV 的分辨率时有

V10

1.0V

3

10

n

2

可求出 n=13.3。所以输入数字量位数 n 至少应为 13 位。

八、

1.555、电阻 R1、R2 及电容 C 构成多谐振荡器;

2.v3、v1 及v2 的波形如图 A8 所示,

v3

O

v1

O

v2

O

t

t

t

图 A8

3.555 定时器构成的多谐振荡器频率为

率均为多谐振荡器频率的 1/2。因此,v1 及v2 波形的频率为

f

3

43.1

2

)

CR

2

(

R

1

。该电路产生的两个时钟频

f

0

43.1

2

)

CR

2

(2

R

1

244

kHz

。

�

九、两个 74161 构成同步 256 进制计数器,或 256 分频器。进位信号 TC 的脉冲宽度只

占一个 CP 周期。Q 的周期 TQ 与 CP 信号的周期 TCP 满足 TQ=256TCP。

十、

1.要使 74138 正常工作,将使能输入端 1E 、 2E 接低电平;3 输入门应为与门,在与

门上画“&”符号。逻辑电路图(略)。

2.JK 触发器组成异步八进制加计数器。

3.由于 Q0=Q1=Q2=0 时, 0Q = 1Q = 2Q =1,与非门的输出为 0,74138 不工作,其输出

7Y ~ 0Y 全为 1,D0 不发光。除此之外,无论 2Q 、 1Q 、 0Q 为何值,与非门的输出为 1,74138

可以工作,其输出有低电平,对应的 LED 可发光。由于 Q2、Q1、Q0 接入译码器输入 A2、

A1、A0 的顺序相反,所以,D1~D7 的闪亮次序为:D4、D2、D6、D1、D5、D3、D7 并循环。

十一、设三盏灯分别为 A、B、C,1 表示灯亮,0 表示灯灭。逻辑电路输出为 L,抢答

失败为 1,成功为 0,列写真值表如表 11 所示。

表 11

A B C

0

0 0

1

0 0

0

0 1

0 1

1

0

1 0

1

1 0

0

1 1

1 1

1

L

1

0

0

1

0

1

1

1

根据真值表写出化简的与非逻辑表达式为

AC

CBA

根据逻辑表达式可画出与非门实现的逻辑图(略)。

BC

AB

L

十二、

1.是同步时序电路。

2.驱动方程

J

0

K

0

2

QQ

1

1

状态方程

Q

1n

0

输出方程

n

QQQ

0

n

1

n

2

1n

Q

1

,

QJ

0

1

QQK

0

2

1

J

2

K

2

QQ

1

0

Q

1

n

n

QQQQQ

1

0

n

1

n

0

n

2

Q

1n

2

,

n

QQQQQ

1

n

1

n

0

n

2

n

2

3.状态转换图如图 A12-3 所示。从状态转换图的主循环可以看出,该电路是 7 进制计

数器,经过 7 个时钟脉冲后,输出 Y 为 1,产生进位信号。

2QQY

1

�

Q2Q1Q0

/Y

000

/1

/1

111

/0

/0

001

/0

010

011

/0

101

/0

100

110

/0

图 A12-3

4.画出时序图

设电路的初始状态为 Q0=Q1=Q2=0,根据状态图可画出时序图如图 A12-4 所示。

CP

Q0

Q1

Q2

图 A12-4

试卷一及其参考答案

试卷一

一、(20 分)选择填空。从每个小题的四个选项中选出一个正确答案,并将其编号填入

该题后的括号中。

1.十进制数 3.625 的二进制数和 8421BCD 码分别为(

)

A. 11.11 和 11.001

C.11.01 和 11.011000100101

B.11.101 和 0011.011000100101

D.11.101 和 11.101

2.下列几种说法中错误的是(

)

A.任何逻辑函数都可以用卡诺图表示。

C.同一个卡诺图化简结果可能不是唯一的。 D.卡诺图中 1 的个数和 0 的个数相同。

B.逻辑函数的卡诺图是唯一的。

3.和 TTL 电路相比,CMOS 电路最突出的优点在于(

)

4.为了把串行输入的数据转换为并行输出的数据,可以使用(

A.可靠性高

C.速度快

A.寄存器

C.计数器

B.抗干扰能力强

D.功耗低

B.移位寄存器

D.存储器

5.单稳态触发器的输出脉冲的宽度取决于(

)

A.触发脉冲的宽度

C.电路本身的电容、电阻的参数

B.触发脉冲的幅度

D.电源电压的数值

6.为了提高多谐振荡器频率的稳定性,最有效的方法是(

)

A.提高电容、电阻的精度

C.采用石英晶体振荡器

B.提高电源的稳定度

C.保持环境温度不变

7.已知时钟脉冲频率为 fcp,欲得到频率为 0.2fcp 的矩形波应采用(

B.五位二进制计数器

C.多谐振荡器

A.五进制计数器

C.单稳态触发器

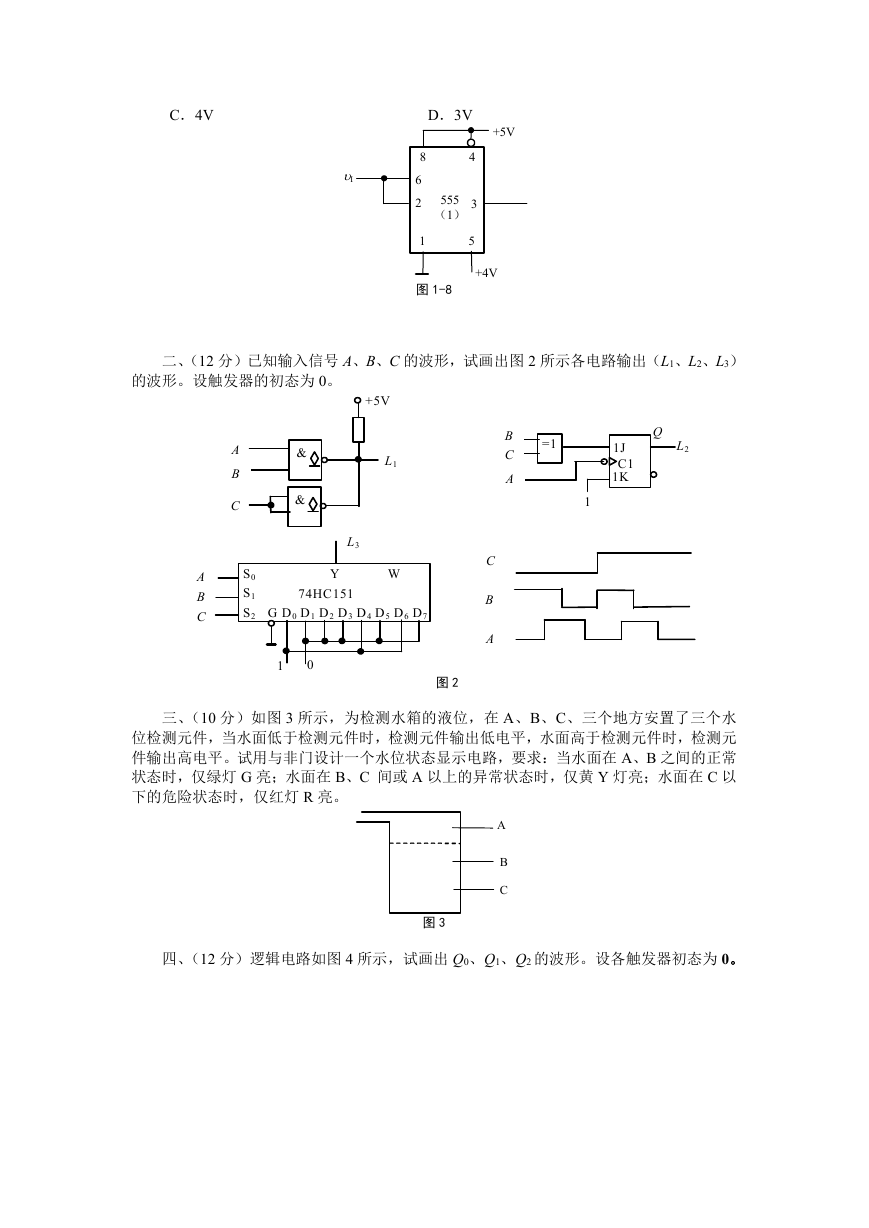

8.在图 1-8 用 555 定时器组成的施密特触发电路中,它的回差电压等于(

)

A.5V

B.2V

)

)

�

C.4V

I

D.3V

+5V

8 4

6

2

555

(1)

3

1 5

+4V

图 1-8

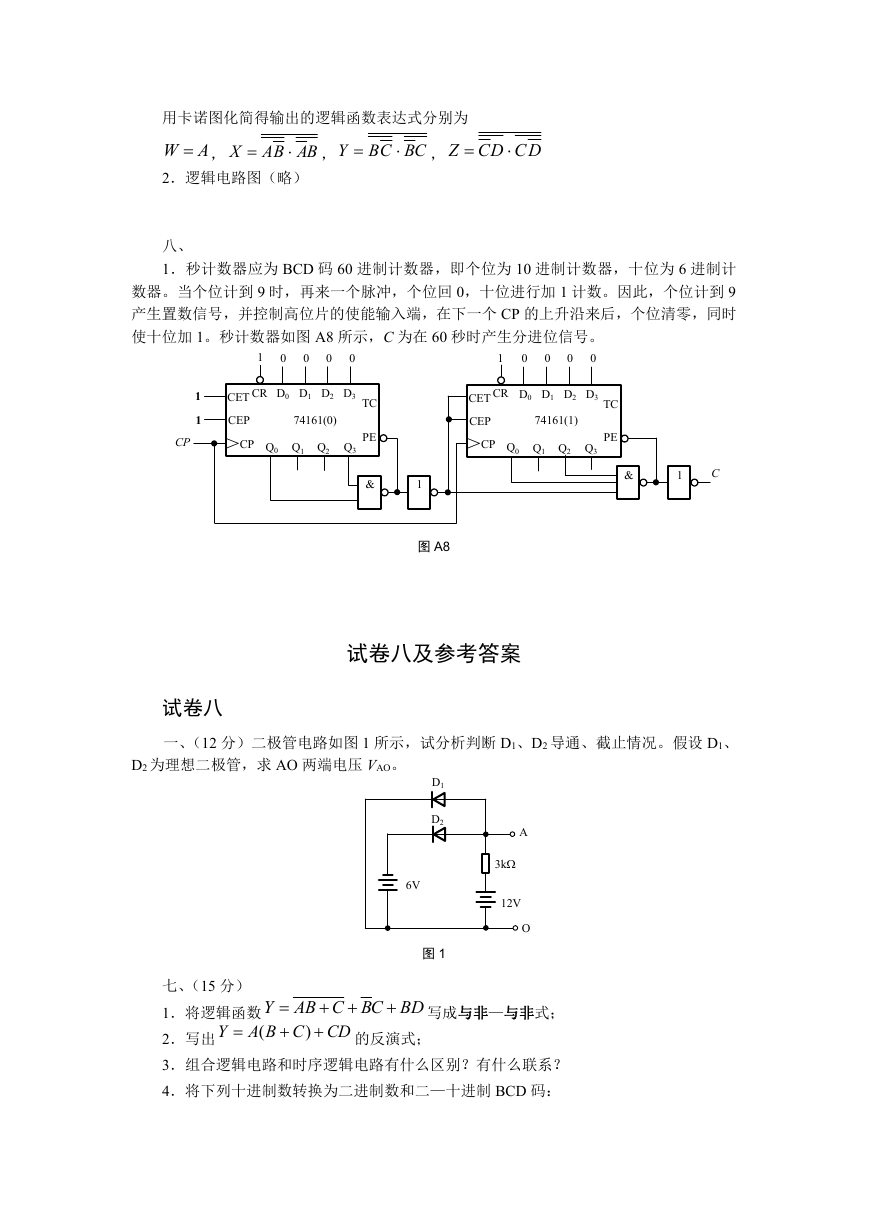

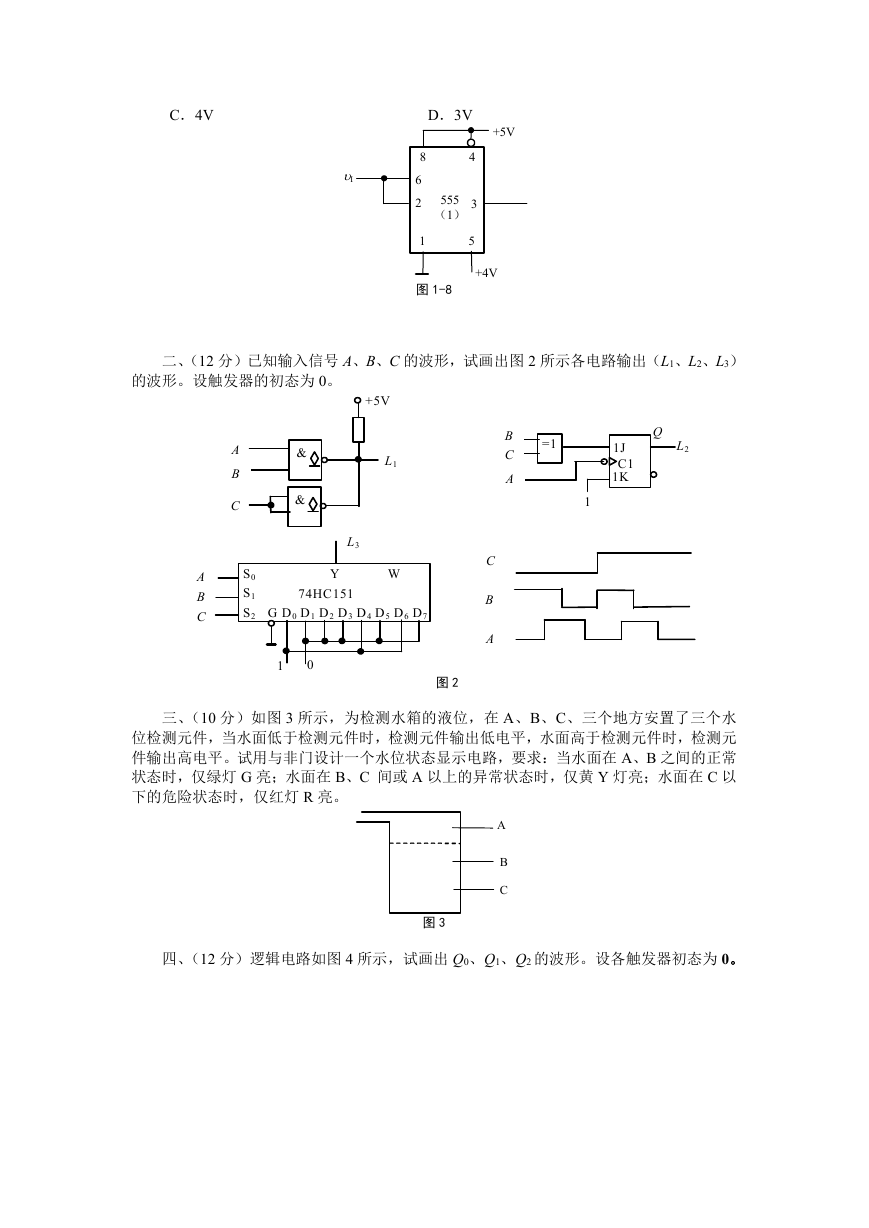

二、(12 分)已知输入信号 A、B、C 的波形,试画出图 2 所示各电路输出(L1、L2、L3)

的波形。设触发器的初态为 0。

A

B

C

A

B

C

&

&

+5V

L1

L3

Y

W

74HC151

S0

S1

S2 G D0 D1 D2 D3 D4 D5 D6 D7

Q

L2

=1

B

C

A

1J

C1

1K

1

C

B

A

1

0

图 2

三、(10 分)如图 3 所示,为检测水箱的液位,在 A、B、C、三个地方安置了三个水

位检测元件,当水面低于检测元件时,检测元件输出低电平,水面高于检测元件时,检测元

件输出高电平。试用与非门设计一个水位状态显示电路,要求:当水面在 A、B 之间的正常

状态时,仅绿灯 G 亮;水面在 B、C 间或 A 以上的异常状态时,仅黄 Y 灯亮;水面在 C 以

下的危险状态时,仅红灯 R 亮。

A

B

C

图 3

四、(12 分)逻辑电路如图 4 所示,试画出 Q0、Q1、Q2 的波形。设各触发器初态为 0。

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc