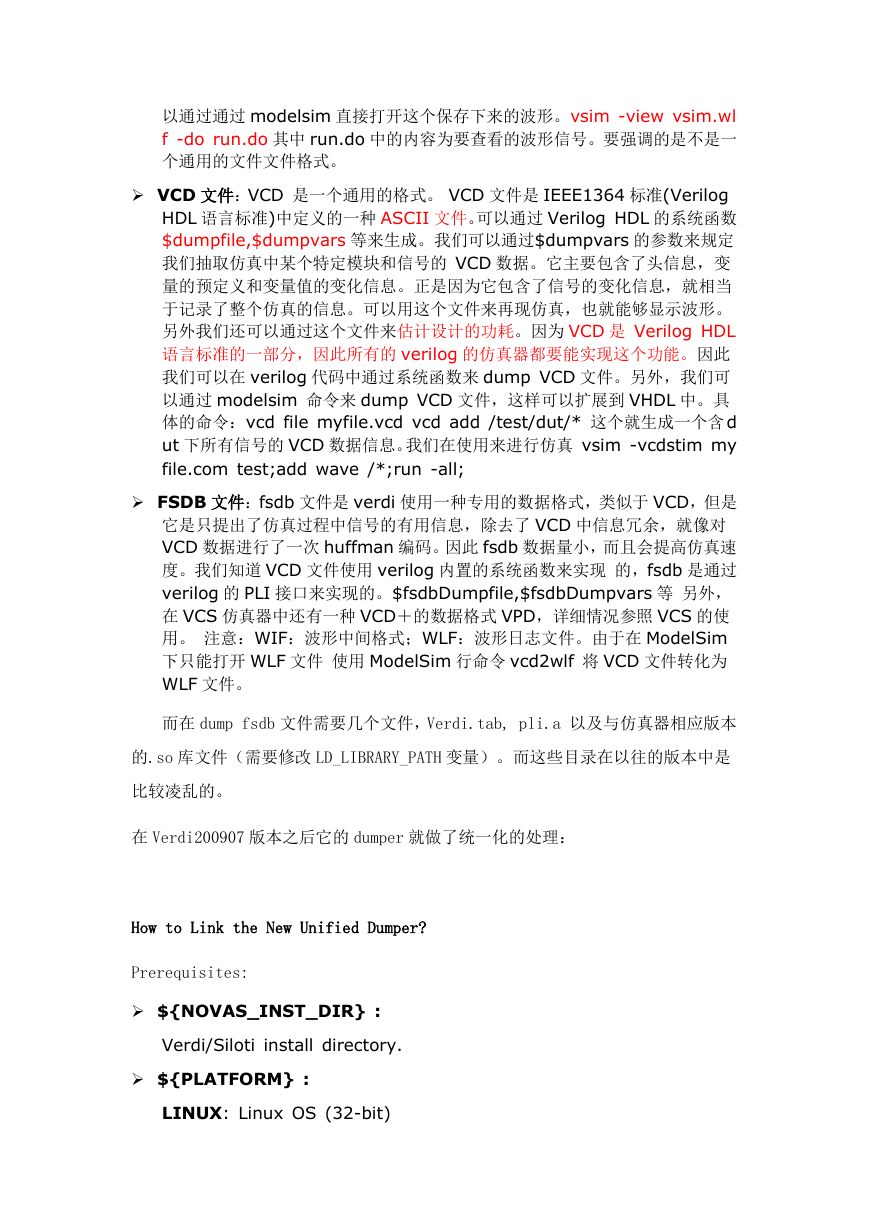

(笔记)vcs 和 verdi 的联合仿真

环境配置

首先搭建好 vcs 和 Verdi 都能工作的环境,主要有 license 问题,环境变量的设置。

在 220 实验室的服务器上所有软件的运行环境都是 csh。所以,所写的脚本也都是 c

sh 的语法。

生成波形文件

Testbench 的编写

若想用 Verdi 观察波形,需要在仿真时生成 fsdb 文件,而 fsdb 在 vcs 或者 models

im 中的生成是通过两个系统调用$fsdbDumpfile $fsdbDumpvars 来实现的。而这两

个系统调用并不是 Verilog 中规定的,是 Verdi 以 pli(Programming Language Int

erface)的方式实现的。这就需要让 vcs 编译时能找到相应的库。

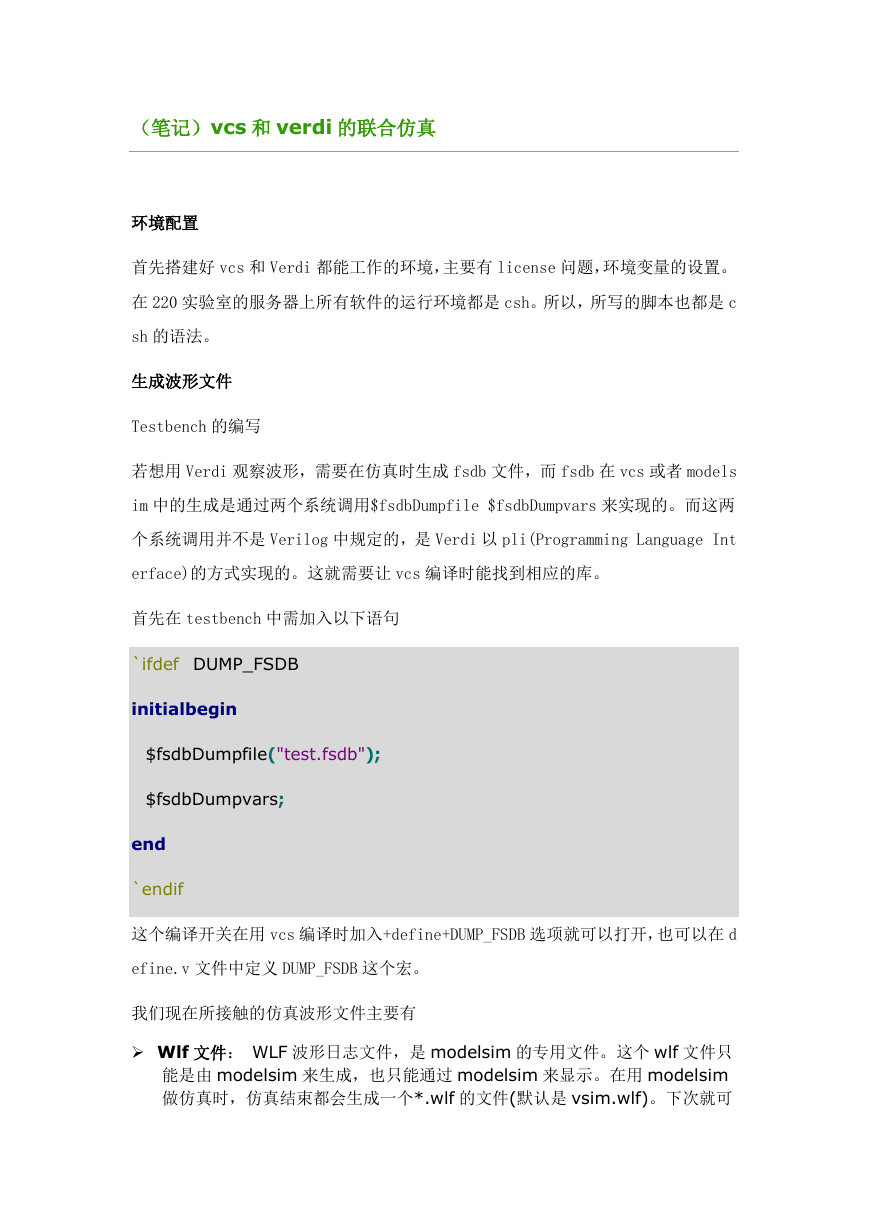

首先在 testbench 中需加入以下语句

`ifdef DUMP_FSDB

initialbegin

$fsdbDumpfile("test.fsdb");

$fsdbDumpvars;

end

`endif

这个编译开关在用 vcs 编译时加入+define+DUMP_FSDB 选项就可以打开,也可以在 d

efine.v 文件中定义 DUMP_FSDB 这个宏。

我们现在所接触的仿真波形文件主要有

Wlf 文件: WLF 波形日志文件,是 modelsim 的专用文件。这个 wlf 文件只

能是由 modelsim 来生成,也只能通过 modelsim 来显示。在用 modelsim

做仿真时,仿真结束都会生成一个*.wlf 的文件(默认是 vsim.wlf)。下次就可

�

以通过通过 modelsim 直接打开这个保存下来的波形。vsim -view vsim.wl

f -do run.do 其中 run.do 中的内容为要查看的波形信号。要强调的是不是一

个通用的文件文件格式。

VCD 文件:VCD 是一个通用的格式。 VCD 文件是 IEEE1364 标准(Verilog

HDL 语言标准)中定义的一种 ASCII 文件。可以通过 Verilog HDL 的系统函数

$dumpfile,$dumpvars 等来生成。我们可以通过$dumpvars 的参数来规定

我们抽取仿真中某个特定模块和信号的 VCD 数据。它主要包含了头信息,变

量的预定义和变量值的变化信息。正是因为它包含了信号的变化信息,就相当

于记录了整个仿真的信息。可以用这个文件来再现仿真,也就能够显示波形。

另外我们还可以通过这个文件来估计设计的功耗。因为 VCD 是 Verilog HDL

语言标准的一部分,因此所有的 verilog 的仿真器都要能实现这个功能。因此

我们可以在 verilog 代码中通过系统函数来 dump VCD 文件。另外,我们可

以通过 modelsim 命令来 dump VCD 文件,这样可以扩展到 VHDL 中。具

体的命令: vcd file myfile.vcd vcd add /test/dut/* 这个就生成一个含 d

ut 下所有信号的 VCD 数据信息。我们在使用来进行仿真 vsim -vcdstim my

file.com test;add wave /*;run -all;

FSDB 文件:fsdb 文件是 verdi 使用一种专用的数据格式,类似于 VCD,但是

它是只提出了仿真过程中信号的有用信息,除去了 VCD 中信息冗余,就像对

VCD 数据进行了一次 huffman 编码。因此 fsdb 数据量小,而且会提高仿真速

度。我们知道 VCD 文件使用 verilog 内置的系统函数来实现 的,fsdb 是通过

verilog 的 PLI 接口来实现的。$fsdbDumpfile,$fsdbDumpvars 等 另外,

在 VCS 仿真器中还有一种 VCD+的数据格式 VPD,详细情况参照 VCS 的使

用。 注意:WIF:波形中间格式;WLF:波形日志文件。由于在 ModelSim

下只能打开 WLF 文件 使用 ModelSim 行命令 vcd2wlf 将 VCD 文件转化为

WLF 文件。

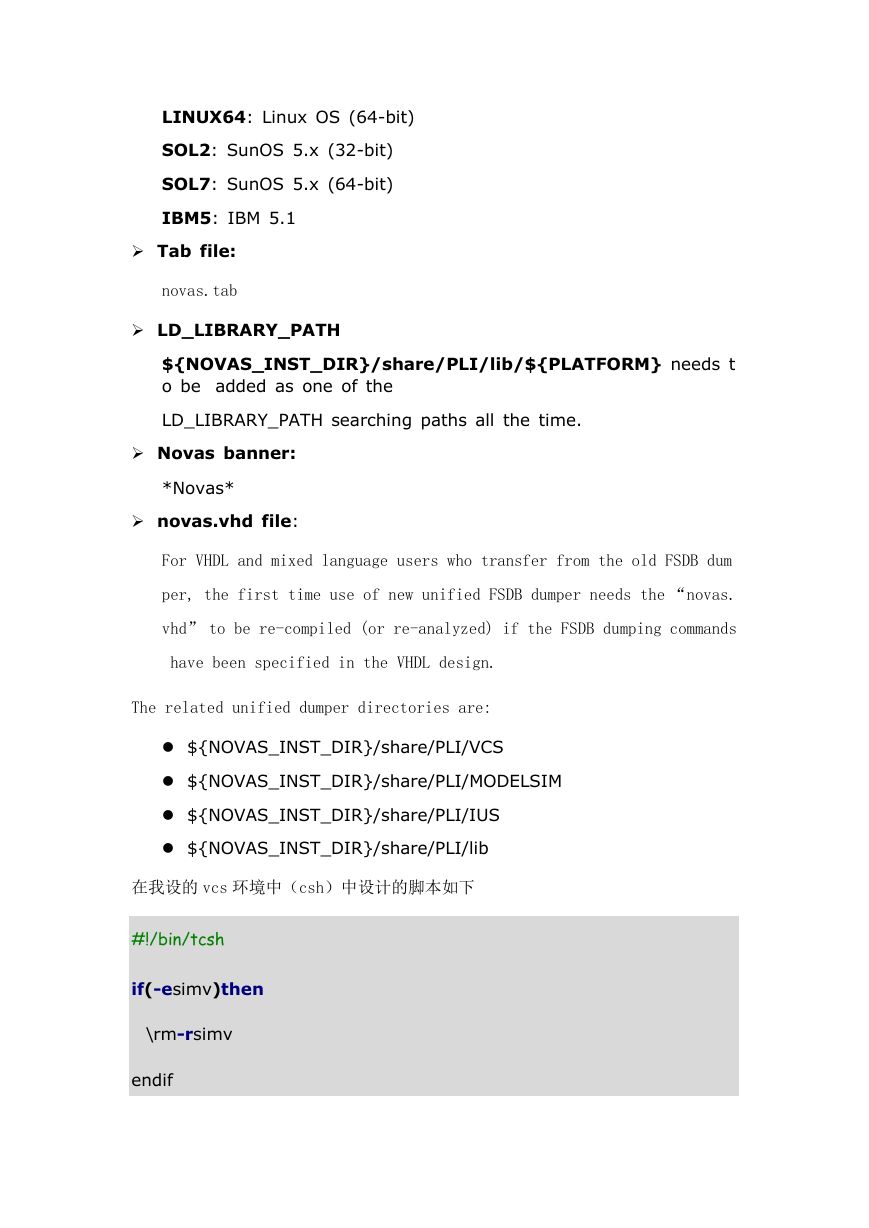

而在 dump fsdb 文件需要几个文件,Verdi.tab, pli.a 以及与仿真器相应版本

的.so 库文件(需要修改 LD_LIBRARY_PATH 变量)。而这些目录在以往的版本中是

比较凌乱的。

在 Verdi200907 版本之后它的 dumper 就做了统一化的处理:

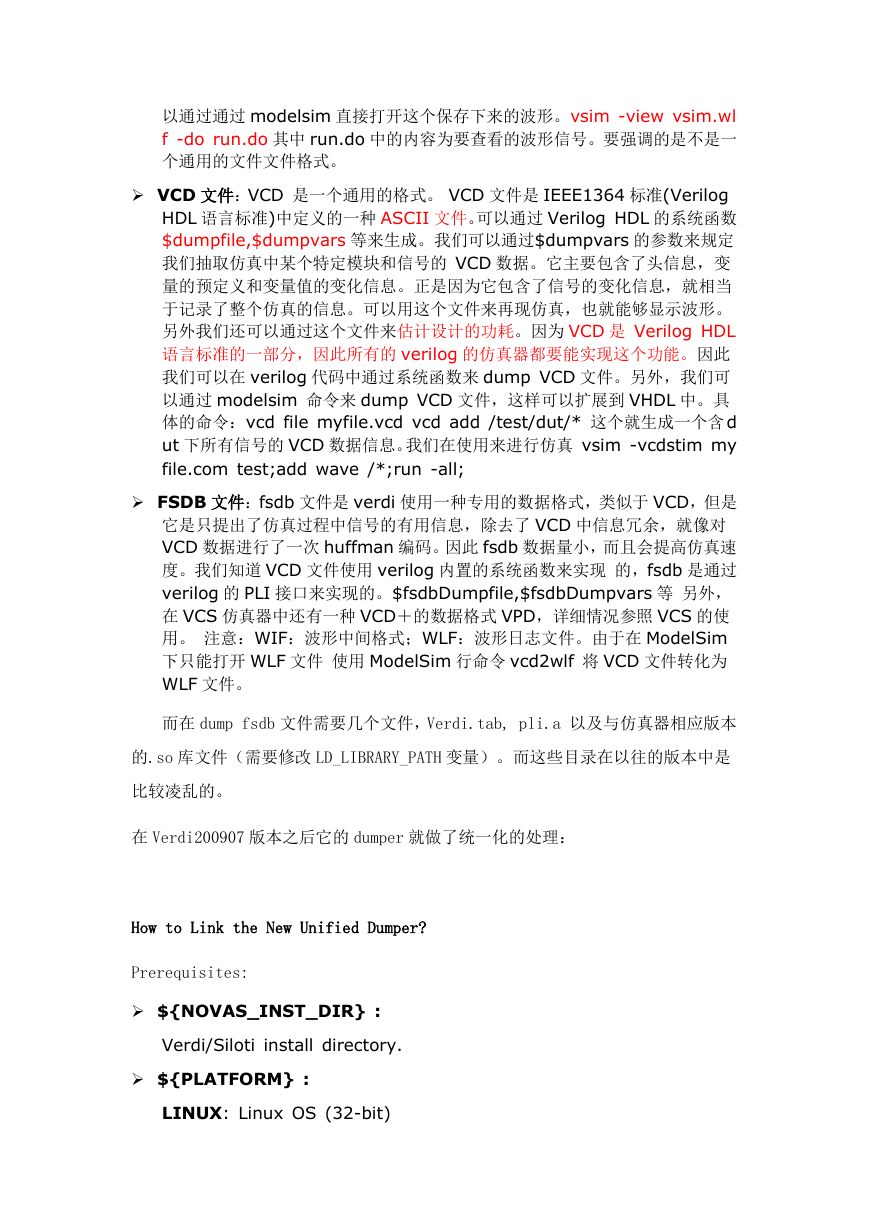

How to Link the New Unified Dumper?

Prerequisites:

${NOVAS_INST_DIR} :

Verdi/Siloti install directory.

${PLATFORM} :

LINUX: Linux OS (32-bit)

�

LINUX64: Linux OS (64-bit)

SOL2: SunOS 5.x (32-bit)

SOL7: SunOS 5.x (64-bit)

IBM5: IBM 5.1

Tab file:

novas.tab

LD_LIBRARY_PATH

${NOVAS_INST_DIR}/share/PLI/lib/${PLATFORM} needs t

o be added as one of the

LD_LIBRARY_PATH searching paths all the time.

Novas banner:

*Novas*

novas.vhd file:

For VHDL and mixed language users who transfer from the old FSDB dum

per, the first time use of new unified FSDB dumper needs the “novas.

vhd” to be re-compiled (or re-analyzed) if the FSDB dumping commands

have been specified in the VHDL design.

The related unified dumper directories are:

${NOVAS_INST_DIR}/share/PLI/VCS

${NOVAS_INST_DIR}/share/PLI/MODELSIM

${NOVAS_INST_DIR}/share/PLI/IUS

${NOVAS_INST_DIR}/share/PLI/lib

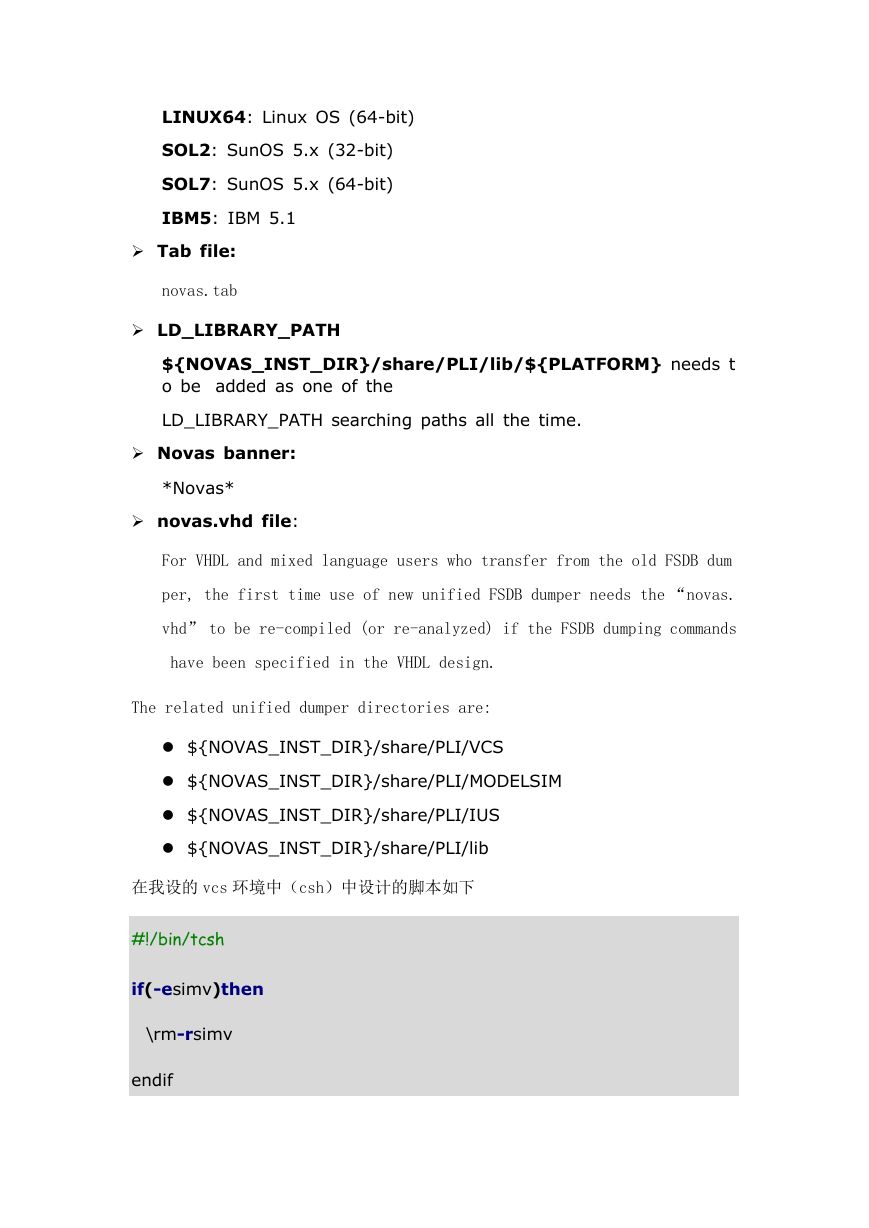

在我设的 vcs 环境中(csh)中设计的脚本如下

#!/bin/tcsh

if(-esimv)then

\rm-rsimv

endif

�

if(-esimv.daidir)then

\rm-rfsimv.daidir

endif

if(-ecsrc*)then

\rm-rfcsrc

endif

vcs0809

#verdi env setting

setPLATFORM=LINUX

setNOVAS_INST_DIR=/opt/spring/verdi201004

setenvLD_LIBRARY_PATH${NOVAS_INST_DIR}/share/PLI/lib/${PL

ATFORM}:${LD_LIBRARY_PATH}

vcs -l vcs.log \

-notice \

-line -debug_all \

-P $NOVAS_INST_DIR/share/PLI/VCS/$PLATFORM/novas.tab \

$NOVAS_INST_DIR/share/PLI/VCS/$PLATFORM/pli.a \

�

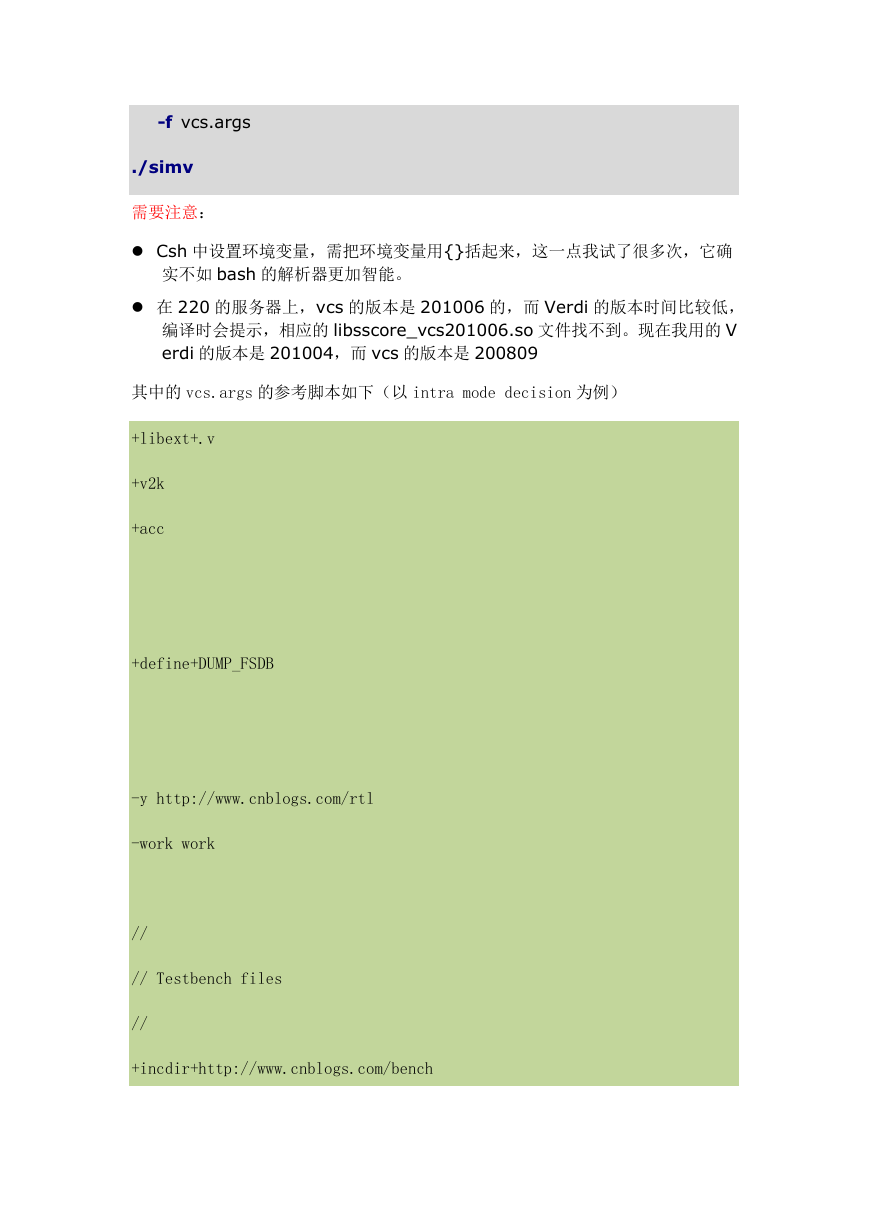

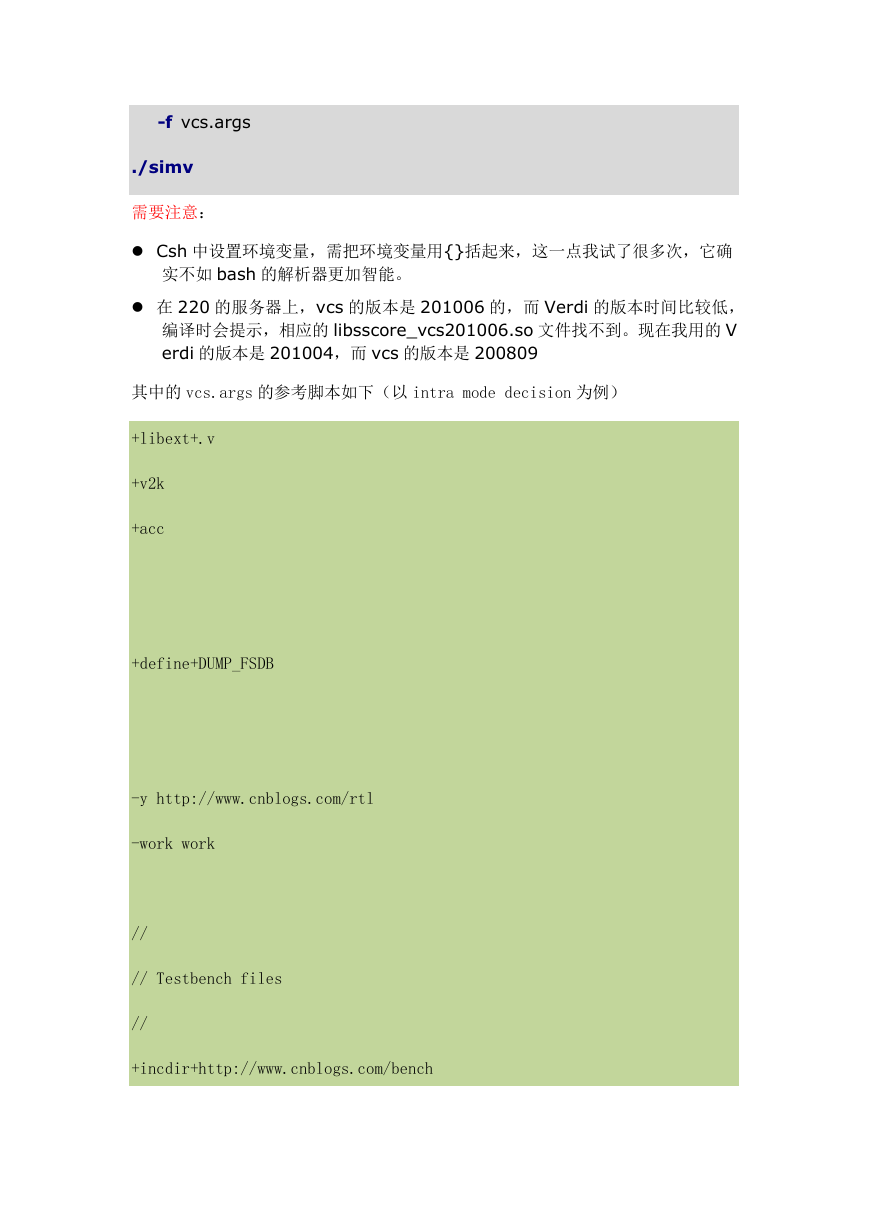

-f vcs.args

./simv

需要注意:

Csh 中设置环境变量,需把环境变量用{}括起来,这一点我试了很多次,它确

实不如 bash 的解析器更加智能。

在 220 的服务器上,vcs 的版本是 201006 的,而 Verdi 的版本时间比较低,

编译时会提示,相应的 libsscore_vcs201006.so 文件找不到。现在我用的 V

erdi 的版本是 201004,而 vcs 的版本是 200809

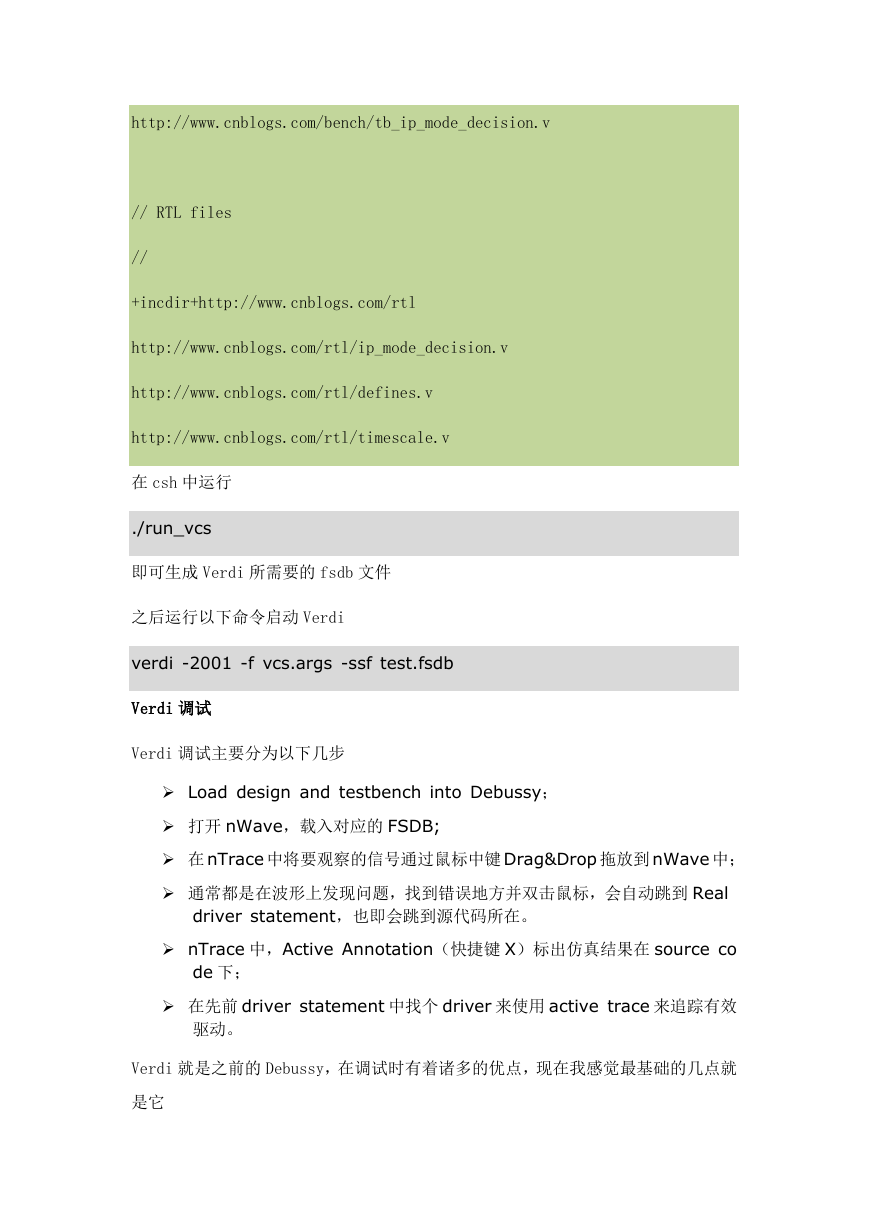

其中的 vcs.args 的参考脚本如下(以 intra mode decision 为例)

+libext+.v

+v2k

+acc

+define+DUMP_FSDB

-y http://www.cnblogs.com/rtl

-work work

//

// Testbench files

//

+incdir+http://www.cnblogs.com/bench

�

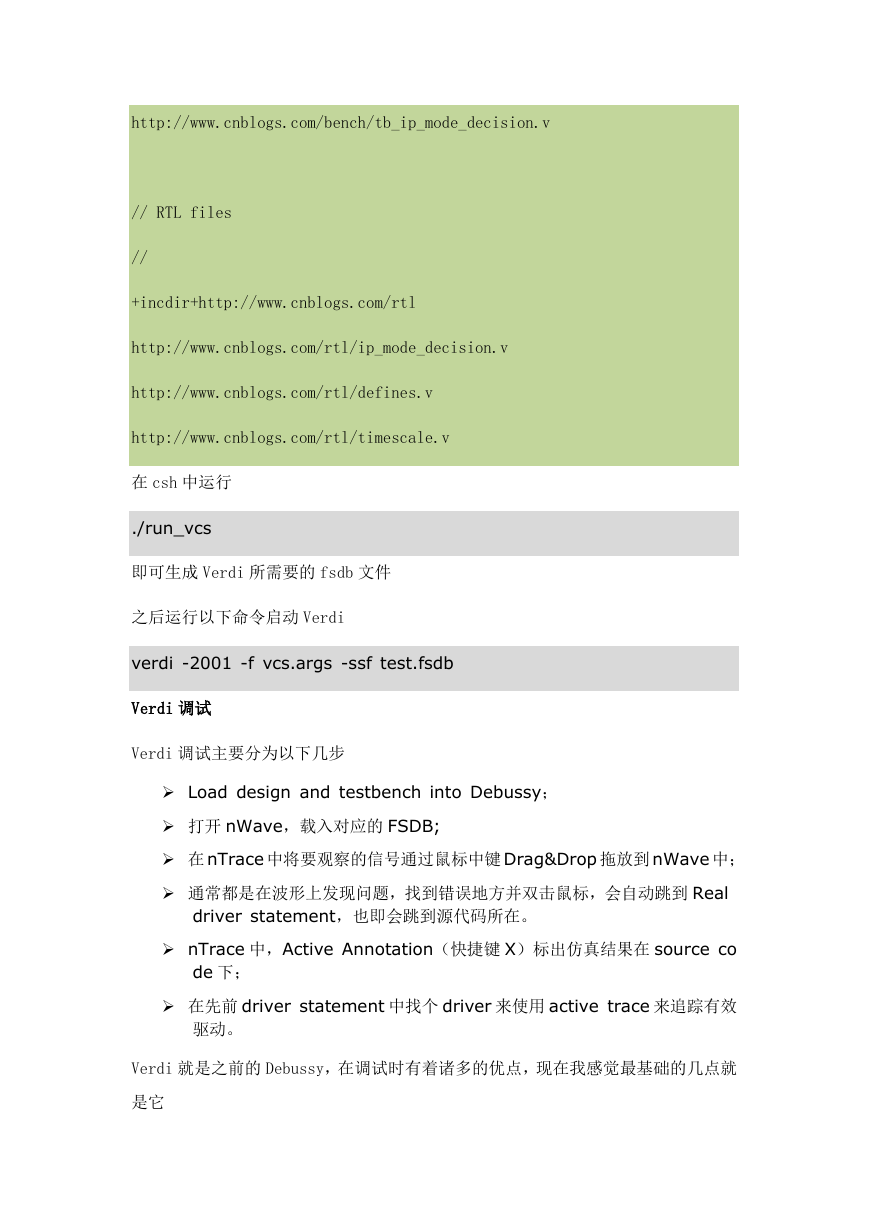

http://www.cnblogs.com/bench/tb_ip_mode_decision.v

// RTL files

//

+incdir+http://www.cnblogs.com/rtl

http://www.cnblogs.com/rtl/ip_mode_decision.v

http://www.cnblogs.com/rtl/defines.v

http://www.cnblogs.com/rtl/timescale.v

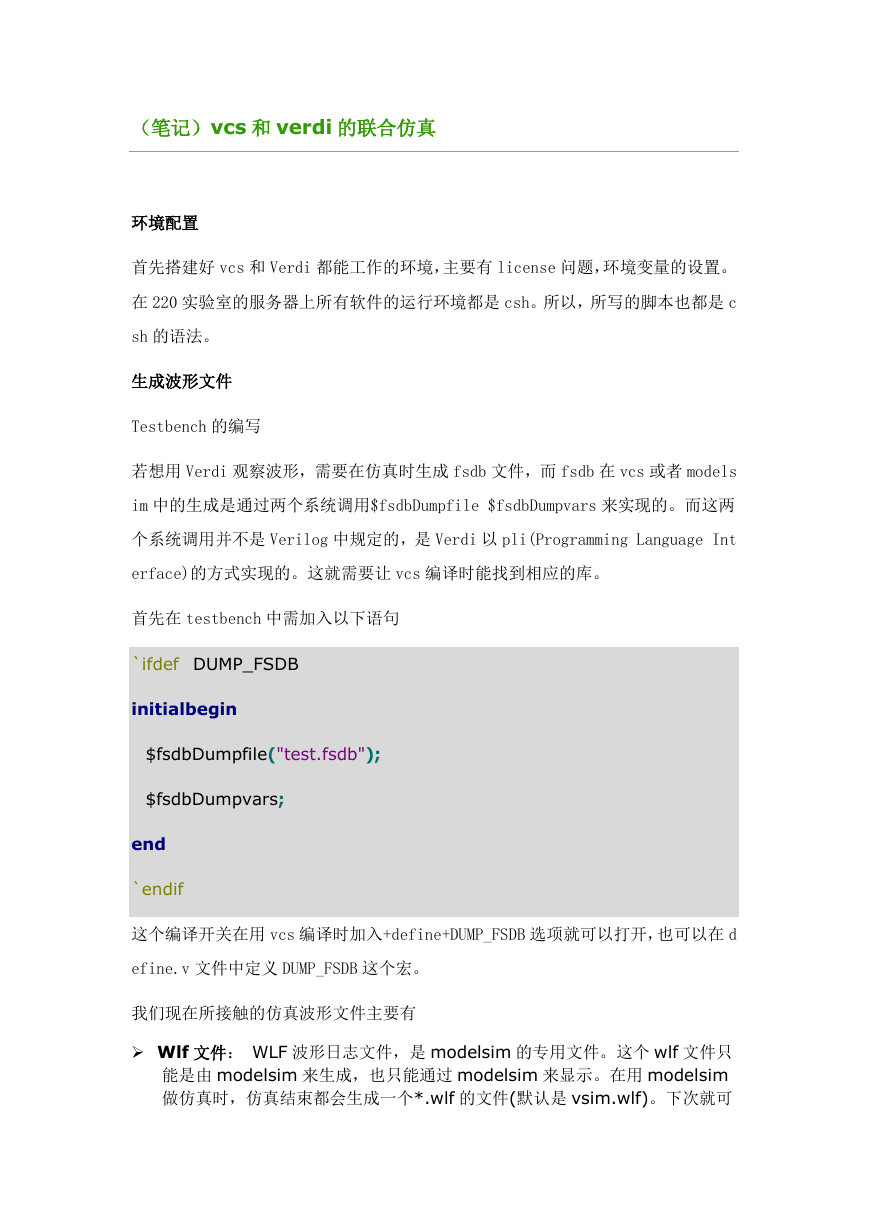

在 csh 中运行

./run_vcs

即可生成 Verdi 所需要的 fsdb 文件

之后运行以下命令启动 Verdi

verdi -2001 -f vcs.args -ssf test.fsdb

Verdi 调试

Verdi 调试主要分为以下几步

Load design and testbench into Debussy;

打开 nWave,载入对应的 FSDB;

在 nTrace 中将要观察的信号通过鼠标中键 Drag&Drop 拖放到 nWave 中;

通常都是在波形上发现问题,找到错误地方并双击鼠标,会自动跳到 Real

driver statement,也即会跳到源代码所在。

nTrace 中,Active Annotation(快捷键 X)标出仿真结果在 source co

de 下;

在先前 driver statement 中找个 driver 来使用 active trace 来追踪有效

驱动。

Verdi 就是之前的 Debussy,在调试时有着诸多的优点,现在我感觉最基础的几点就

是它

�

只需执行一遍仿真就可以查看所有的波形,而在 modelsim 中则需要反复

运行 add wave 命令,每一次都要重新仿真。

可以查看设计的原理图 schematic,这非常方便查看每一个 module 和 wi

re 的所对应的硬件结构,modelsim 现在还没有这个功能。

在仿真时可以很轻易地追踪每个信号所对应的源码。

Modelsim 脚本自动仿真

1、创建文件 run.do,“#”为注释符号

quit -sim #退出上次仿真

.main clear #清除上次仿真所有文件以

及打印信息

vlib work.veloce #创建veloce 的工作环境

#----------------------------------------------------------------------------------

---------------------

vlog ./tb_XXXXXXX.v #testbench 文件

vlog ./../src/*.v #代码源文件

vlog ./../ip_core/*.v #IP 核

#----------------------------------------------------------------------------------

---------------------

#Alrera

vlog /opt/Quartus/13.1/quartus/eda/sim_lib/altera_mf.v #IP 核仿真模型

vlog /opt/Quartus/13.1/quartus/eda/sim_lib/220model.v #IP 核仿真模型

#----------------------------------------------------------------------------------

---------------------

#Xilinx

vlog /opt/Xilinx/Vivado/2015.4/data/verilog/src/unimacro/*.v #IP 核仿真模型

vlog /opt/Xilinx/Vivado/2015.4/data/verilog/src/unisims/*.v #IP 核仿真模型

vlog /opt/Xilinx/Vivado/2015.4/data/verilog/src/unisims_dr/*.v #IP 核仿真模型

�

vlog /opt/Xilinx/Vivado/2015.4/data/verilog/src/xeclib/*.v #IP 核仿真模型

vlog /opt/Xilinx/Vivado/2015.4/data/verilog/src/glbl.v #IP 核仿真模型

#----------------------------------------------------------------------------------

---------------------

#LATTICE

vlog ./lattice/verilog/ecp3 #IP 核仿真模型

vlog ./lattice/verilog/pmi #IP 核仿真模型

#----------------------------------------------------------------------------------

---------------------

vsim -voptargs=+acc work.tb_XXXXXXXX

#----------------------------------------------------------------------------------

---------------------

add wave /tb_XXXX/i2s_XXX_inst/* #添加例化模块所有信号

波形

do wave.do #若保存有新模型,用此语句

可以复现已保存的波形

run 500000 ns #仿真运行时间

2、写完以上 run.do 文件后,在「 terminal 」中执行以下语句,则可以

自动跑完仿真

[redhat@fpga marin]$ vsim -do run.do

Vcs+Verdi 脚本自动仿真

0、定义环境变量,在.bashrc 或者.cshrc 文件中加入

##VCS

setenv VCS_HOME /work/tools/synopsys2015/vcs

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc