QCA9531 v2.0 802.11n 2x2 2.4 GHz

Premium SOC for WLAN Platforms

Data Sheet

80-Y7991-1 Rev. C

October 2014

Confidential and Proprietary – Qualcomm Atheros Inc.

NO PUBLIC DISCLOSURE PERMITTED: Please report postings of this document on public servers or websites

to: DocCtrlAgent@qualcomm.com.

Restricted Distribution: Not to be distributed to anyone who is not an employee of either Qualcomm or its

subsidiaries without the express approval of Qualcomm’s Configuration Management.

Not to be used, copied, reproduced, or modified in whole or in part, nor its contents revealed in any manner to others

without the express written permission of Qualcomm Atheros, Inc.

Qualcomm is a registered trademark of QUALCOMM Incorporated. Atheros is a registered trademark of Qualcomm Atheros, Inc.

All other registered and unregistered trademarks are the property of QUALCOMM Incorporated, Qualcomm Atheros, Inc., or their

respective owners and used with permission. Registered marks owned by QUALCOMM Incorporated and Qualcomm Atheros, Inc.

are registered in the United States and may be registered in other countries.

This technical data may be subject to U.S. and international export, re-export, or transfer (“export”) laws. Diversion

contrary to U.S. and international law is strictly prohibited.

Qualcomm Atheros, Inc.

1700 Technology Drive

San Jose, CA 95110

U.S.A.

© 2014 Qualcomm Atheros, Inc.

�

###E###

Contents

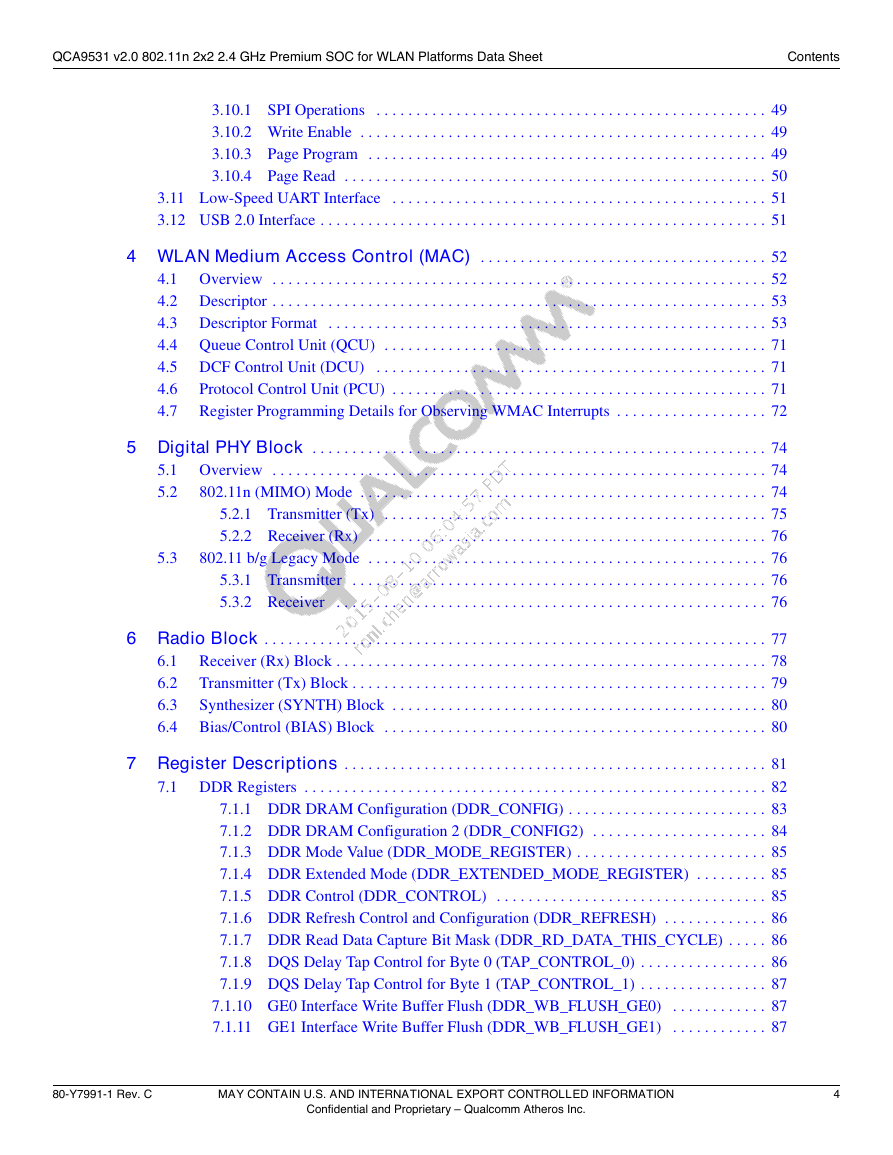

1 General Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

1.1

1.2 QCA9531 System Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

2 Pin Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

3.1

3.2

3.3

3.4

3 Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

Functional Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

Bootstrap Options . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31

Reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32

PLL and Clock Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 33

3.4.1 Full Chip Clocking Structure . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 33

3.4.2 PLL . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 34

3.4.3 DDR PLL . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 34

3.4.4 Ethernet PLL . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 35

3.5 MIPS Processor . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 35

3.6 Address Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 35

3.7 DDR Memory Controller . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 36

3.7.1 DDR Configurations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 36

3.7.2 DDR Initialization Sequences . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 37

3.7.3 DDR Memory Initialization . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 41

3.7.4 CPU DDR Address Mapping . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 42

3.7.5 Refresh . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 42

3.7.6 Self Refresh . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 42

PCIE RC . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 43

3.8.1 Power Management . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 44

3.8.2 Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 44

3.8.3 Error Reporting Capability and Status Checking . . . . . . . . . . . . . . . . . . . . . . . 44

3.8.4 Byte-Swap Option . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 44

3.8.5 Request Sizes and Payloads . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 44

3.9 GPIO . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 45

3.9.1 GPIO Output . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 46

3.9.2 GPIO Input . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 48

3.10 Serial Flash SPI/ROM . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 49

3.8

80-Y7991-1 Rev. C

MAY CONTAIN U.S. AND INTERNATIONAL EXPORT CONTROLLED INFORMATION

3

Confidential and Proprietary – Qualcomm Atheros Inc.

�

QCA9531 v2.0 802.11n 2x2 2.4 GHz Premium SOC for WLAN Platforms Data Sheet

Contents

3.10.1 SPI Operations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 49

3.10.2 Write Enable . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 49

3.10.3 Page Program . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 49

3.10.4 Page Read . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 50

3.11 Low-Speed UART Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 51

3.12 USB 2.0 Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 51

4 WLAN Medium Access Control (MAC) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 52

4.1 Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 52

4.2 Descriptor . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 53

4.3 Descriptor Format . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 53

4.4 Queue Control Unit (QCU) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 71

4.5 DCF Control Unit (DCU) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 71

Protocol Control Unit (PCU) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 71

4.6

4.7

Register Programming Details for Observing WMAC Interrupts . . . . . . . . . . . . . . . . . . . 72

5 Digital PHY Block . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 74

5.1 Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 74

802.11n (MIMO) Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 74

5.2

5.2.1 Transmitter (Tx) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 75

5.2.2 Receiver (Rx) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 76

802.11 b/g Legacy Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 76

5.3.1 Transmitter . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 76

5.3.2 Receiver . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 76

5.3

6 Radio Block . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 77

Receiver (Rx) Block . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 78

Transmitter (Tx) Block . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 79

Synthesizer (SYNTH) Block . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 80

Bias/Control (BIAS) Block . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 80

6.1

6.2

6.3

6.4

7 Register Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 81

7.1 DDR Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 82

7.1.1 DDR DRAM Configuration (DDR_CONFIG) . . . . . . . . . . . . . . . . . . . . . . . . . 83

7.1.2 DDR DRAM Configuration 2 (DDR_CONFIG2) . . . . . . . . . . . . . . . . . . . . . . 84

7.1.3 DDR Mode Value (DDR_MODE_REGISTER) . . . . . . . . . . . . . . . . . . . . . . . . 85

7.1.4 DDR Extended Mode (DDR_EXTENDED_MODE_REGISTER) . . . . . . . . . 85

7.1.5 DDR Control (DDR_CONTROL) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 85

7.1.6 DDR Refresh Control and Configuration (DDR_REFRESH) . . . . . . . . . . . . . 86

7.1.7 DDR Read Data Capture Bit Mask (DDR_RD_DATA_THIS_CYCLE) . . . . . 86

7.1.8 DQS Delay Tap Control for Byte 0 (TAP_CONTROL_0) . . . . . . . . . . . . . . . . 86

7.1.9 DQS Delay Tap Control for Byte 1 (TAP_CONTROL_1) . . . . . . . . . . . . . . . . 87

7.1.10 GE0 Interface Write Buffer Flush (DDR_WB_FLUSH_GE0) . . . . . . . . . . . . 87

7.1.11 GE1 Interface Write Buffer Flush (DDR_WB_FLUSH_GE1) . . . . . . . . . . . . 87

80-Y7991-1 Rev. C

MAY CONTAIN U.S. AND INTERNATIONAL EXPORT CONTROLLED INFORMATION

4

Confidential and Proprietary – Qualcomm Atheros Inc.

�

QCA9531 v2.0 802.11n 2x2 2.4 GHz Premium SOC for WLAN Platforms Data Sheet

Contents

7.1.12 USB Interface Write Buffer Flush (DDR_WB_FLUSH_USB) . . . . . . . . . . . . 88

7.1.13 PCIE Interface Write Buffer Flush (DDR_WB_FLUSH_PCIE) . . . . . . . . . . . 88

7.1.14 WMAC Interface Write Buffer Flush (DDR_WB_FLUSH_WMAC) . . . . . . . 88

7.1.15 DDR2 Configuration (DDR_DDR2_CONFIG) . . . . . . . . . . . . . . . . . . . . . . . . 89

7.1.16 DDR EMR2 (DDR_EMR2) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 89

7.1.17 DDR EMR3 (DDR_EMR3) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 89

7.1.18 DDR Bank Arbiter Per Client Burst Size (DDR_BURST) . . . . . . . . . . . . . . . . 90

7.1.19 DDR Bank Arbiter Per Client Burst Size 2 (DDR_BURST2) . . . . . . . . . . . . . 90

7.1.20 DDR AHB Master Timeout Control (DDR_AHB_MASTER_TIMEOUT_MAX)

91

7.1.21 DDR AHB Timeout Current Count (DDR_AHB_MASTER_TIMEOUT_

CURNT) 91

7.1.22 Timeout Slave Address (AHB_MASTER_TIMEOUT_SLV_ADDR) . . . . . . 91

7.1.23 DDR Controller Configuration (DDR_CTL_CONFIG) . . . . . . . . . . . . . . . . . . 92

7.1.24 DDR Self Refresh Control . . . . . . . . . . . . . . . . . . . . . . . . . . (DDR_SF_CTL) 93

7.1.25 Self Refresh Timer (SF_TIMER) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 94

7.1.26 WMAC Flush (WMAC_FLUSH) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 94

7.1.27 DDR3 Configuration Register (DDR3_CONFIG) . . . . . . . . . . . . . . . . . . . . . . 95

7.2 UART0 (Low-Speed) Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 96

7.2.1 Receive Buffer (RBR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 96

7.2.2 Transmit Holding (THR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 97

7.2.3 Divisor Latch Low (DLL) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 97

7.2.4 Divisor Latch High (DLH) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 98

7.2.5 Interrupt Enable (IER) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 98

7.2.6 Interrupt Identity (IIR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 99

7.2.7 FIFO Control (FCR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 100

7.2.8 Line Control (LCR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 101

7.2.9 Modem Control (MCR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 102

7.2.10 Line Status (LSR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 103

7.2.11 Modem Status (MSR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 104

7.3 USB Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 105

7.3.1 USB Configuration Control (USB_CONFIG) . . . . . . . . . . . . . . . . . . . . . . . . 105

7.4 GPIO Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 106

7.4.1 GPIO Output Enable (GPIO_OE) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 106

7.4.2 GPIO Input Value (GPIO_IN) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 107

7.4.3 GPIO Output Value (GPIO_OUT) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 107

7.4.4 GPIO Per Bit Set (GPIO_SET) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 107

7.4.5 GPIO Per Bit Clear (GPIO_CLEAR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 107

7.4.6 GPIO Interrupt Enable (GPIO_INT) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 108

7.4.7 GPIO Interrupt Type (GPIO_INT_TYPE) . . . . . . . . . . . . . . . . . . . . . . . . . . . 108

7.4.8 GPIO Interrupt Polarity (GPIO_INT_POLARITY) . . . . . . . . . . . . . . . . . . . . 108

7.4.9 GPIO Interrupt Pending (GPIO_INT_PENDING) . . . . . . . . . . . . . . . . . . . . . 108

7.4.10 GPIO Interrupt Mask (GPIO_INT_MASK) . . . . . . . . . . . . . . . . . . . . . . . . . . 109

80-Y7991-1 Rev. C

MAY CONTAIN U.S. AND INTERNATIONAL EXPORT CONTROLLED INFORMATION

5

Confidential and Proprietary – Qualcomm Atheros Inc.

�

QCA9531 v2.0 802.11n 2x2 2.4 GHz Premium SOC for WLAN Platforms Data Sheet

Contents

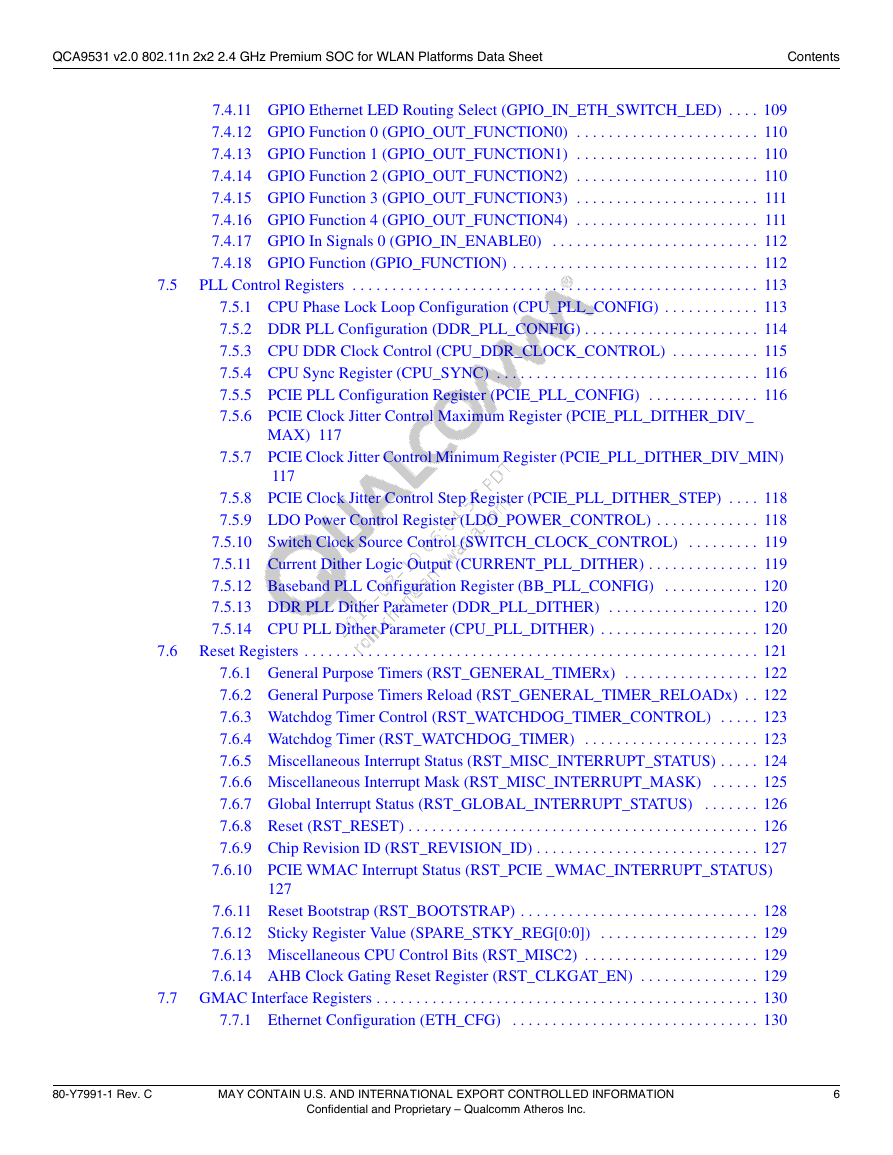

7.5

7.6

7.4.11 GPIO Ethernet LED Routing Select (GPIO_IN_ETH_SWITCH_LED) . . . . 109

7.4.12 GPIO Function 0 (GPIO_OUT_FUNCTION0) . . . . . . . . . . . . . . . . . . . . . . . 110

7.4.13 GPIO Function 1 (GPIO_OUT_FUNCTION1) . . . . . . . . . . . . . . . . . . . . . . . 110

7.4.14 GPIO Function 2 (GPIO_OUT_FUNCTION2) . . . . . . . . . . . . . . . . . . . . . . . 110

7.4.15 GPIO Function 3 (GPIO_OUT_FUNCTION3) . . . . . . . . . . . . . . . . . . . . . . . 111

7.4.16 GPIO Function 4 (GPIO_OUT_FUNCTION4) . . . . . . . . . . . . . . . . . . . . . . . 111

7.4.17 GPIO In Signals 0 (GPIO_IN_ENABLE0) . . . . . . . . . . . . . . . . . . . . . . . . . . 112

7.4.18 GPIO Function (GPIO_FUNCTION) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 112

PLL Control Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 113

7.5.1 CPU Phase Lock Loop Configuration (CPU_PLL_CONFIG) . . . . . . . . . . . . 113

7.5.2 DDR PLL Configuration (DDR_PLL_CONFIG) . . . . . . . . . . . . . . . . . . . . . . 114

7.5.3 CPU DDR Clock Control (CPU_DDR_CLOCK_CONTROL) . . . . . . . . . . . 115

7.5.4 CPU Sync Register (CPU_SYNC) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 116

7.5.5 PCIE PLL Configuration Register (PCIE_PLL_CONFIG) . . . . . . . . . . . . . . 116

7.5.6 PCIE Clock Jitter Control Maximum Register (PCIE_PLL_DITHER_DIV_

MAX) 117

7.5.7 PCIE Clock Jitter Control Minimum Register (PCIE_PLL_DITHER_DIV_MIN)

117

7.5.8 PCIE Clock Jitter Control Step Register (PCIE_PLL_DITHER_STEP) . . . . 118

7.5.9 LDO Power Control Register (LDO_POWER_CONTROL) . . . . . . . . . . . . . 118

7.5.10 Switch Clock Source Control (SWITCH_CLOCK_CONTROL) . . . . . . . . . 119

7.5.11 Current Dither Logic Output (CURRENT_PLL_DITHER) . . . . . . . . . . . . . . 119

7.5.12 Baseband PLL Configuration Register (BB_PLL_CONFIG) . . . . . . . . . . . . 120

7.5.13 DDR PLL Dither Parameter (DDR_PLL_DITHER) . . . . . . . . . . . . . . . . . . . 120

7.5.14 CPU PLL Dither Parameter (CPU_PLL_DITHER) . . . . . . . . . . . . . . . . . . . . 120

Reset Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 121

7.6.1 General Purpose Timers (RST_GENERAL_TIMERx) . . . . . . . . . . . . . . . . . 122

7.6.2 General Purpose Timers Reload (RST_GENERAL_TIMER_RELOADx) . . 122

7.6.3 Watchdog Timer Control (RST_WATCHDOG_TIMER_CONTROL) . . . . . 123

7.6.4 Watchdog Timer (RST_WATCHDOG_TIMER) . . . . . . . . . . . . . . . . . . . . . . 123

7.6.5 Miscellaneous Interrupt Status (RST_MISC_INTERRUPT_STATUS) . . . . . 124

7.6.6 Miscellaneous Interrupt Mask (RST_MISC_INTERRUPT_MASK) . . . . . . 125

7.6.7 Global Interrupt Status (RST_GLOBAL_INTERRUPT_STATUS) . . . . . . . 126

7.6.8 Reset (RST_RESET) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 126

7.6.9 Chip Revision ID (RST_REVISION_ID) . . . . . . . . . . . . . . . . . . . . . . . . . . . . 127

7.6.10 PCIE WMAC Interrupt Status (RST_PCIE _WMAC_INTERRUPT_STATUS)

127

7.6.11 Reset Bootstrap (RST_BOOTSTRAP) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 128

7.6.12 Sticky Register Value (SPARE_STKY_REG[0:0]) . . . . . . . . . . . . . . . . . . . . 129

7.6.13 Miscellaneous CPU Control Bits (RST_MISC2) . . . . . . . . . . . . . . . . . . . . . . 129

7.6.14 AHB Clock Gating Reset Register (RST_CLKGAT_EN) . . . . . . . . . . . . . . . 129

7.7 GMAC Interface Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 130

7.7.1 Ethernet Configuration (ETH_CFG) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 130

80-Y7991-1 Rev. C

MAY CONTAIN U.S. AND INTERNATIONAL EXPORT CONTROLLED INFORMATION

6

Confidential and Proprietary – Qualcomm Atheros Inc.

�

QCA9531 v2.0 802.11n 2x2 2.4 GHz Premium SOC for WLAN Platforms Data Sheet

Contents

7.8

PCIE RC Control Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 131

7.8.1 PCIE Application Control (PCIE_APP) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 132

7.8.2 PCIE Interrupt and Error (PCIE_AER) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 133

7.8.3 PCIE Power Management (PCIE_PWR_MGMT) . . . . . . . . . . . . . . . . . . . . . 133

7.8.4 PCIE Electromechanical (PCIE_ELEC) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 134

7.8.5 PCIE Configuration (PCIE_CFG) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 134

7.8.6 PCIE Receive Completion (PCIE_RX_CNTL) . . . . . . . . . . . . . . . . . . . . . . . 135

7.8.7 PCIE Reset (PCIE_RESET) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 135

7.8.8 PCIE Debug and Control (PCIE_DEBUG) . . . . . . . . . . . . . . . . . . . . . . . . . . 136

7.8.9 PCIE PHY Read/Write Data (PCIE_PHY_RW_DATA) . . . . . . . . . . . . . . . . 136

7.8.10 PCIE PHY Serial Interface Load/Read Trigger (PCIE_PHY_TRG_RD_LOAD)

137

7.8.11 PCIE PHY Configuration Data (PCIE_PHY_CFG_DATA) . . . . . . . . . . . . . . 137

7.8.12 PCIE MAC-PHY Interface Signals (PCIE_MAC_PHY) . . . . . . . . . . . . . . . . 137

7.8.13 PCIE PHY-MAC Interface Signals (PCIE_PHY_MAC) . . . . . . . . . . . . . . . . 138

7.8.14 PCIE Sideband Bus1 (PCIE_SIDEBAND1) . . . . . . . . . . . . . . . . . . . . . . . . . 138

7.8.15 PCIE Sideband Bus2 (PCIE_SIDEBAND2) . . . . . . . . . . . . . . . . . . . . . . . . . 138

7.8.16 PCIE Spare (PCIE_SPARE) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 139

7.8.17 PCIE MSI Lower Address (PCIE_MSI_ADDR) . . . . . . . . . . . . . . . . . . . . . . 139

7.8.18 PCIE MSI Data Value (PCIE_MSI_DATA) . . . . . . . . . . . . . . . . . . . . . . . . . . 139

7.8.19 PCIE Interrupt Status (PCIE_INT_STATUS) . . . . . . . . . . . . . . . . . . . . . . . . . 139

7.8.20 PCIE Interrupt Mask (PCIE_INT_MASK) . . . . . . . . . . . . . . . . . . . . . . . . . . . 141

7.8.21 PCIE Error Counter (PCIE_ERR_CNT) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 142

7.8.22 PCIE AHB Latency Interrupt Counter (PCIE_REQ_LATENCY_W_INT) . . 142

7.8.23 Miscellaneous PCIE Bits (PCIE_MISC) . . . . . . . . . . . . . . . . . . . . . . . . . . . . 142

7.9 WDMA Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 143

7.9.1 Command (CR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 144

7.9.2 Configuration and Status (CFG) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 144

7.9.3 Rx DMA Data Buffer Pointer Threshold (RXBUFPTR_THRESH) . . . . . . . 145

7.9.4 Tx DMA Descriptor Pointer Threshold (TXDPPTR_THRESH) . . . . . . . . . . 145

7.9.5 Maximum Interrupt Rate Threshold (MIRT) . . . . . . . . . . . . . . . . . . . . . . . . . 145

7.9.6 Interrupt Global Enable (IER) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 146

7.9.7 Tx Interrupt Mitigation Thresholds (TIMT) . . . . . . . . . . . . . . . . . . . . . . . . . . 146

7.9.8 Rx Interrupt Mitigation Thresholds (RIMT) . . . . . . . . . . . . . . . . . . . . . . . . . . 146

7.9.9 Tx Configuration (TXCFG) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 147

7.9.10 Rx Configuration (RXCFG) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 148

7.9.11 MIB Control (MIBC) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 148

7.9.12 Data Buffer Length (DATABUF) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 149

7.9.13 Global Tx Timeout (GTT) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 149

7.9.14 Global Tx Timeout Mode (GTTM) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 149

7.9.15 Carrier Sense Timeout (CST) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 150

7.9.16 Size of High and Low Priority (RXDP_SIZE) . . . . . . . . . . . . . . . . . . . . . . . . 150

7.9.17 MAC Rx High Priority Queue RXDP Pointer (RX_QUEUE_HP_RXDP) . . 150

80-Y7991-1 Rev. C

MAY CONTAIN U.S. AND INTERNATIONAL EXPORT CONTROLLED INFORMATION

7

Confidential and Proprietary – Qualcomm Atheros Inc.

�

QCA9531 v2.0 802.11n 2x2 2.4 GHz Premium SOC for WLAN Platforms Data Sheet

Contents

7.9.18 MAC Rx Low Priority Queue RXDP Pointer (RX_QUEUE_LP_RXDP) . . . 150

7.9.19 Primary Interrupt Status (ISR_P) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 151

7.9.20 Secondary Interrupt Status 0 (ISR_S0) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 152

7.9.21 Secondary Interrupt Status 1 (ISR_S1) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 153

7.9.22 Secondary Interrupt Status 2 (ISR_S2) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 153

7.9.23 Secondary Interrupt Status 3 (ISR_S3) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 154

7.9.24 Secondary Interrupt Status 4 (ISR_S4) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 154

7.9.25 Secondary Interrupt Status 5 (ISR_S5) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 155

7.9.26 Primary Interrupt Mask (IMR_P) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 156

7.9.27 Secondary Interrupt Mask 0 (IMR_S0) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 157

7.9.28 Secondary Interrupt Mask 1 (IMR_S1) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 157

7.9.29 Secondary Interrupt Mask 2 (IMR_S2) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 158

7.9.30 Secondary Interrupt Mask 3 (IMR_S3) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 158

7.9.31 Secondary Interrupt Mask 4 (IMR_S4) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 159

7.9.32 Secondary Interrupt Mask 5 (IMR_S5) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 159

7.9.33 Primary Interrupt Status Read and Clear (ISR_P_RAC) . . . . . . . . . . . . . . . . 160

7.9.34 Secondary Interrupt Status 0 (ISR_S0_S) . . . . . . . . . . . . . . . . . . . . . . . . . . . . 160

7.9.35 Secondary Interrupt Status 1 (ISR_S1_S) . . . . . . . . . . . . . . . . . . . . . . . . . . . . 160

7.9.36 Secondary Interrupt Status 2 (ISR_S2_S) . . . . . . . . . . . . . . . . . . . . . . . . . . . . 160

7.9.37 Secondary Interrupt Status 3 (ISR_S3_S) . . . . . . . . . . . . . . . . . . . . . . . . . . . . 161

7.9.38 Secondary Interrupt Status 4 (ISR_S4_S) . . . . . . . . . . . . . . . . . . . . . . . . . . . . 161

7.9.39 Secondary Interrupt Status 5 (ISR_S5_S) . . . . . . . . . . . . . . . . . . . . . . . . . . . . 161

7.10 WQCU Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 162

7.10.1 Tx Queue Descriptor (Q_TXDP) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 162

7.10.2 QCU_STATUS_RING_START_ADDRESS Lower 32 bits of Address (Q_

STATUS_RING_START) 163

7.10.3 QCU_STATUS_RING_END_ADDR Lower 32 Bits of Address (Q_STATUS_

RING_END) 163

7.10.4 QCU_STATUS_RING_CURRENT Address (Q_STATUS_RING_CURRENT)

163

7.10.5 Tx Queue Enable (Q_TXE) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 163

7.10.6 Tx Queue Disable (Q_TXD) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 164

7.10.7 CBR Configuration (Q_CBRCFG) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 164

7.10.8 ReadyTime Configuration (Q_RDYTIMECFG) . . . . . . . . . . . . . . . . . . . . . . 164

7.10.9 OneShotArm Set Control (Q_ONESHOTARM_SC) . . . . . . . . . . . . . . . . . . . 165

7.10.10 OneShotArm Clear Control (Q_ONESHOTARM_CC) . . . . . . . . . . . . . . . . . 165

7.10.11 Misc. QCU Settings (Q_MISC) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 166

7.10.12 Misc. QCU Status (Q_STS) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 167

7.10.13 ReadyTimeShutdown Status (Q_RDYTIMESHDN) . . . . . . . . . . . . . . . . . . . 167

7.10.14 Descriptor CRC Check (MAC_QCU_DESC_CRC_CHK) . . . . . . . . . . . . . . 168

7.11 WDCU Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 169

7.11.1 QCU Mask (D_QCUMASK) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 169

7.11.2 DCU-Global SIFS (D_GBL_IFS_SIFS) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 170

80-Y7991-1 Rev. C

MAY CONTAIN U.S. AND INTERNATIONAL EXPORT CONTROLLED INFORMATION

8

Confidential and Proprietary – Qualcomm Atheros Inc.

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc