TMS320C645x DSPSerial RapidIO (SRIO)

Table of Contents

Preface

1 Overview

1.1 General RapidIO System

1.1.1 RapidIO Architectural Hierarchy

1.1.2 RapidIO Interconnect Architecture

1.1.3 Physical Layer 1x/4x LP-Serial Specification

1.2 RapidIO Feature Support in SRIO

1.3 Standards

1.4 External Devices Requirements

1.5 TI Devices Supported By This Document

2 SRIO Functional Description

2.1 Overview

2.1.1 Peripheral Data Flow

2.1.2 SRIO Packets

2.1.2.1 Operation Sequence

2.1.2.2 Example Packet - Streaming Write

2.1.2.3 Control Symbols

2.1.2.4 SRIO Packet Type

2.2 SRIO Pins

2.3 Functional Operation

2.3.1 Component Block Diagram

2.3.2 SERDES Macro and Its Configurations

2.3.2.1 Enabling the PLL

2.3.2.2 Enabling the Receiver

2.3.2.3 Enabling the Transmitter

2.3.2.4 SERDES Configuration Example

2.3.3 Direct I/O Operation

2.3.3.1 Detailed Data Path Description

2.3.3.2 Direct I/O TX Operation

2.3.3.3 Direct I/O RX Operation

2.3.3.4 Reset and Power Down State

2.3.4 Message Passing

2.3.4.1 RX Operation

2.3.4.2 TX Operation

2.3.4.3 Reset and Power Down State

2.3.4.4 Message Passing Software Requirements

2.3.5 Maintenance

2.3.6 Doorbell Operation

2.3.7 Atomic Operations

2.3.8 Congestion Control

2.3.8.1 Detailed Description

2.3.9 Endianness

2.3.9.1 Translation for MMR space

2.3.9.2 Endian Conversion

2.3.10 Reset and Power Down

2.3.10.1 Reset and Power Down Summary

2.3.10.2 Enable and Enable Status Registers

2.3.10.3 Software Shutdown Details

2.3.11 Emulation

2.3.12 TX Buffers, Credit, and Packet Reordering

2.3.12.1 Multiple Ports With 1x Operation

2.3.12.2 Single Port With 1x or 4x Operation

2.3.12.3 Unavailable Outbound Credit

2.3.13 Initialization Example

2.3.13.1 Enabling the SRIO Peripheral

2.3.13.2 PLL, Ports, and Data Rate Initializations

2.3.13.3 Peripheral Initializations

2.3.14 Bootload Capability

2.3.14.1 Configuration and Operation

2.3.14.2 Bootload Data Movement

2.3.14.3 Device Wakeup

2.3.15 RX Multicast and Multiple DESTID Support

2.3.15.1 Discrete Multicast ID Support

2.3.15.2 Unlimited Multicast and DESTID Support

2.3.15.3 Daisy Chain Operation and Packet Forwarding

3 Logical/Transport Error Handling and Logging

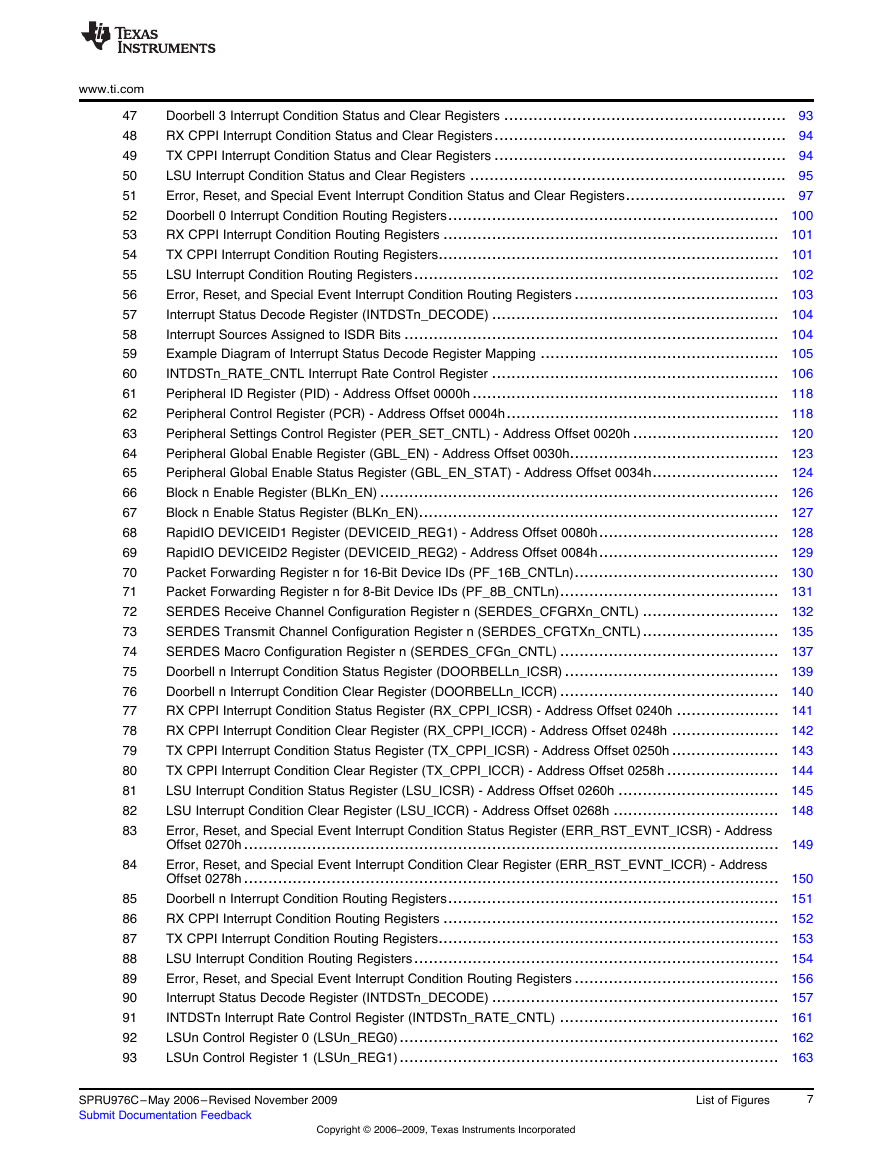

4 Interrupt Conditions

4.1 CPU Interrupts

4.2 General Description

4.3 Interrupt Condition Status and Clear Registers

4.3.1 Doorbell Interrupt Condition Status and Clear Registers

4.3.2 CPPI Interrupt Condition Status and Clear Registers

4.3.3 LSU Interrupt Condition Status and Clear Registers

4.3.4 Error, Reset, and Special Event Interrupt Condition Status and Clear Registers

4.4 Interrupt Condition Routing Registers

4.4.1 Doorbell Interrupt Condition Routing Registers

4.4.1.1 CPPI Interrupt Condition Routing Registers

4.4.1.2 LSU Interrupt Condition Routing Registers

4.4.1.3 Error, Reset, and Special Event Interrupt Condition Routing Registers

4.5 Interrupt Status Decode Registers

4.6 Interrupt Generation

4.7 Interrupt Pacing

4.8 Interrupt Handling

5 SRIO Registers

5.1 Peripheral Identification Register (PID)

5.2 Peripheral Control Register (PCR)

5.3 Peripheral Settings Control Register (PER_SET_CNTL)

5.4 Peripheral Global Enable Register (GBL_EN)

5.5 Peripheral Global Enable Status Register (GBL_EN_STAT)

5.6 Block n Enable Register (BLKn_EN)

5.7 Block n Enable Status Register (BLKn_EN_STAT)

5.8 RapidIO DEVICEID1 Register (DEVICEID_REG1)

5.9 RapidIO DEVICEID2 Register (DEVICEID_REG2)

5.10 Packet Forwarding Register n for 16-Bit Device IDs (PF_16B_CNTLn)

5.11 Packet Forwarding Register n for 8-Bit Device IDs (PF_8B_CNTLn)

5.12 SERDES Receive Channel Configuration Register n (SERDES_CFGRXn_CNTL)

5.13 SERDES Transmit Channel Configuration Register n (SERDES_CFGTXn_CNTL)

5.14 SERDES Macro Configuration Register n (SERDES_CFGn_CNTL)

5.15 DOORBELLn Interrupt Condition Status Register (DOORBELLn_ICSR)

5.16 DOORBELLn Interrupt Condition Clear Register (DOORBELLn_ICCR)

5.17 RX CPPI Interrupt Status Register (RX_CPPI_ICSR)

5.18 RX CPPI Interrupt Clear Register (RX_CPPI_ICCR)

5.19 TX CPPI Interrupt Status Register (TX_CPPI_ICSR)

5.20 TX CPPI Interrupt Clear Register (TX_CPPI_ICCR)

5.21 LSU Interrupt Condition Status Register (LSU_ICSR)

5.22 LSU Interrupt Condition Clear Register (LSU_ICCR)

5.23 Error, Reset, and Special Event Interrupt Condition Status Register (ERR_RST_EVNT_ICSR)

5.24 Error, Reset, and Special Event Interrupt Condition Clear Register (ERR_RST_EVNT_ICCR)

5.25 DOORBELLn Interrupt Condition Routing Registers (DOORBELLn_ICRR and DOORBELLn_ICRR2)

5.26 RX CPPI Interrupt Condition Routing Registers (RX_CPPI_ICRR and RX_CPPI_ICRR2)

5.27 TX CPPI Interrupt Condition Routing Registers (TX_CPPI_ICRR and TX_CPPI_ICRR2)

5.28 LSU Interrupt Condition Routing Registers (LSU_ICRR0-LSU_ICRR3)

5.29 Error, Reset, and Special Event Interrupt Condition Routing Registers (ERR_RST_EVNT_ICRR, ERR_RST_EVNT_ICRR2, and ERR_RST_EVNT_ICRR3)

5.30 Interrupt Status Decode Register (INTDSTn_DECODE)

5.31 INTDSTn Interrupt Rate Control Register (INTDSTn_RATE_CNTL)

5.32 LSUn Control Register 0 (LSUn_REG0)

5.33 LSUn Control Register 1 (LSUn_REG1)

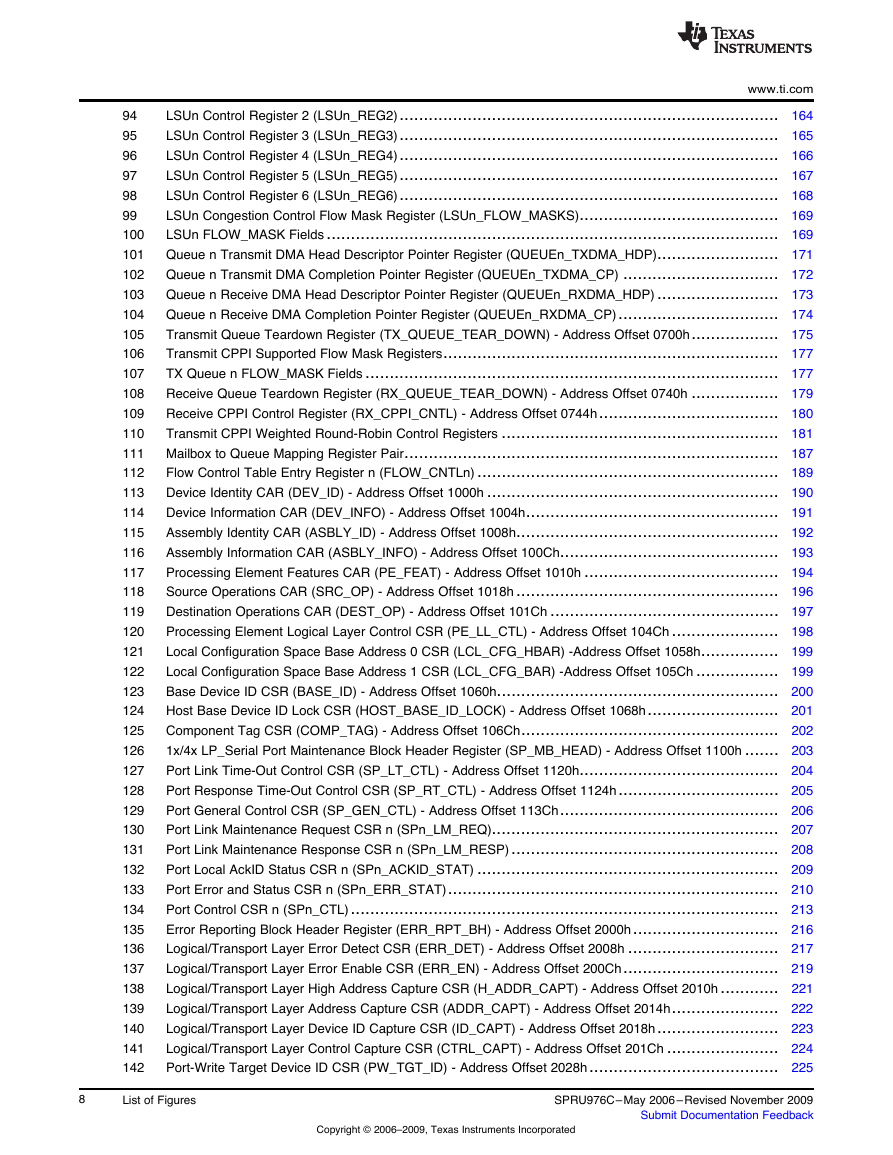

5.34 LSUn Control Register 2 (LSUn_REG2)

5.35 LSUn Control Register 3 (LSUn_REG3)

5.36 LSUn Control Register 4 (LSUn_REG4)

5.37 LSUn Control Register 5 (LSUn_REG5)

5.38 LSUn Control Register 6 (LSUn_REG6)

5.39 LSUn Congestion Control Flow Mask Register (LSUn_FLOW_MASKS)

5.40 Queue n Transmit DMA Head Descriptor Pointer Register (QUEUEn_TXDMA_HDP)

5.41 Queue n Transmit DMA Completion Pointer Register (QUEUEn_TXDMA_CP)

5.42 Queue n Receive DMA Head Descriptor Pointer Register (QUEUEn_RXDMA_HDP)

5.43 Queue n Receive DMA Completion Pointer Register (QUEUEn_RXDMA_CP)

5.44 Transmit Queue Teardown Register (TX_QUEUE_TEAR_DOWN)

5.45 Transmit CPPI Supported Flow Mask Registers (TX_CPPI_FLOW_MASKS[0-7])

5.46 Receive Queue Teardown Register (RX_QUEUE_TEAR_DOWN)

5.47 Receive CPPI Control Register (RX_CPPI_CNTL)

5.48 Transmit CPPI Weighted Round-Robin Control Registers (TX_QUEUE_CNTL[0-3])

5.49 Mailbox to Queue Mapping Registers (RXU_MAP_Ln and RXU_MAP_Hn)

5.50 Flow Control Table Entry Register n (FLOW_CNTLn)

5.51 Device Identity CAR (DEV_ID)

5.52 Device Information CAR (DEV_INFO)

5.53 Assembly Identity CAR (ASBLY_ID)

5.54 Assembly Information CAR (ASBLY_INFO)

5.55 Processing Element Features CAR (PE_FEAT)

5.56 Source Operations CAR (SRC_OP)

5.57 Destination Operations CAR (DEST_OP)

5.58 Processing Element Logical Layer Control CSR (PE_LL_CTL)

5.59 Local Configuration Space Base Address 0 CSR (LCL_CFG_HBAR)

5.60 Local Configuration Space Base Address 1 CSR (LCL_CFG_BAR)

5.61 Base Device ID CSR (BASE_ID)

5.62 Host Base Device ID Lock CSR (HOST_BASE_ID_LOCK)

5.63 Component Tag CSR (COMP_TAG)

5.64 1x/4x LP Serial Port Maintenance Block Header Register (SP_MB_HEAD)

5.65 Port Link Time-Out Control CSR (SP_LT_CTL)

5.66 Port Response Time-Out Control CSR (SP_RT_CTL)

5.67 Port General Control CSR (SP_GEN_CTL)

5.68 Port Link Maintenance Request CSR n (SPn_LM_REQ)

5.69 Port Link Maintenance Response CSR n (SPn_LM_RESP)

5.70 Port Local AckID Status CSR n (SPn_ACKID_STAT)

5.71 Port Error and Status CSR n (SPn_ERR_STAT)

5.72 Port Control CSR n (SPn_CTL)

5.73 Error Reporting Block Header Register (ERR_RPT_BH)

5.74 Logical/Transport Layer Error Detect CSR (ERR_DET)

5.75 Logical/Transport Layer Error Enable CSR (ERR_EN)

5.76 Logical/Transport Layer High Address Capture CSR (H_ADDR_CAPT)

5.77 Logical/Transport Layer Address Capture CSR (ADDR_CAPT)

5.78 Logical/Transport Layer Device ID Capture CSR (ID_CAPT)

5.79 Logical/Transport Layer Control Capture CSR (CTRL_CAPT)

5.80 Port-Write Target Device ID CSR (PW_TGT_ID)

5.81 Port Error Detect CSR n (SPn_ERR_DET)

5.82 Port Error Rate Enable CSR n (SPn_RATE_EN)

5.83 Port n Attributes Error Capture CSR 0 (SPn_ERR_ATTR_CAPT_DBG0)

5.84 Port n Error Capture CSR 1 (SPn_ERR_CAPT_DBG1)

5.85 Port n Error Capture CSR 2 (SPn_ERR_CAPT_DBG2)

5.86 Port n Error Capture CSR 3 (SPn_ERR_CAPT_DBG3)

5.87 Port n Error Capture CSR 4 (SPn_ERR_CAPT_DBG4)

5.88 Port Error Rate CSR n (SPn_ERR_RATE)

5.89 Port Error Rate Threshold CSR n (SPn_ERR_THRESH)

5.90 Port IP Discovery Timer for 4x Mode Register (SP_IP_DISCOVERY_TIMER)

5.91 Port IP Mode CSR (SP_IP_MODE)

5.92 Port IP Prescaler Register (IP_PRESCAL)

5.93 Port-Write-In Capture CSRs (SP_IP_PW_IN_CAPT[0-3])

5.94 Port Reset Option CSR n (SPn_RST_OPT)

5.95 Port Control Independent Register n (SPn_CTL_INDEP)

5.96 Port Silence Timer n Register (SPn_SILENCE_TIMER)

5.97 Port Multicast-Event Control Symbol Request Register n (SPn_MULT_EVNT_CS)

5.98 Port Control Symbol Transmit n Register (SPn_CS_TX)

Appendix A Examples

A.1 SRIO Initialization Example

A.2 LSU Programming Example

A.3 Message Passing Software

A.3.1 Initialization Example

A.3.2 Queue Mapping

A.3.3 RX Buffer Descriptor

A.3.4 TX Buffer Description

A.3.5 Start Message Passing

A.4 Interrupt Handling

Appendix B Software-Assisted Error Recovery

Appendix C Revision History

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc